## RÉPUBLIQUE ALGERIENNE DÉMOCRATIQUE ET POPULAIRE MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR ET DE LA RECHERCHE SCIENTIFIQUE ECOLE NATIONALE POLYTECHNIQUE Option: TÉLÉCOMMUNICATIONS المدرسة الوطنية المتعددة التقنيات Département : ELÉCTRONIQUE HELICTHEOUP O « Ecolo Nationalo Pelytechnique THESE DE MAGISTER — THEME -CONCEPTION D'ARCHITECTURES DIGITALES UNIFIÉES TCD / TCDI 2-D: ETUDE COMPARATIVE DU MODE DE CALCUL HALF-LINE ET DE L'ARITHMÉTIQUE DISTRIBUÉE Présentée par : Mr M. TOUNSI Ingénieur d'état en Electronique, ENP. Devant le Jury:

| Mr D. BERKANI, Professeur à l'E.N.P                       | Président   |

|-----------------------------------------------------------|-------------|

| Mr A. FARAH, Professeur à l'E.N.P                         | Rapporteur  |

| Mr A. BEL OUCHRANI, Docteur d'état à l'E.N.P              | Examinateur |

| Mr R. SADOUN, Chargé de cours à l'E.N.P                   | Examinateur |

| Mr Z. TERRA, Docteur-Ingénieur, Chargé de cours à l'E.N.P | Examinateur |

## REMERCIEMENTS

المدرسة الوطنية المتددمة التقنيبات المحكمتيسة — DIDLIOTHEQUE المحكمتيسة المحكمة التقنيبات

De prime abord, je tiens à remercier vivement mon directeur de thèse, le Professeur A. FARAH de l'E.N.P, pour toute son assistance, ses orientations clairvoyantes et ses encouragements répétés qu'il m'a prodigués tout au long de la préparation de cette thèse. Qu'il trouve ici, l'expression de ma grande reconnaissance et l'assurance de ma parfaite considération pour ses multiples enseignements.

Je remercie Mr D. BERKANI, Professeur à l'E.N.P, de me faire l'honneur de présider mon jury. Qu'il trouve ici, l'expression et l'assurance de ma parfaite reconnaissance à ses précieux encouragements et ses riches enseignements.

Mes plus vifs remerciements vont à Mr A. BELLOUCHRANI, Docteur d'état à l'E.N.P, Mr Z. TERRA, Docteur-Ingénieur chargé de cours à l'E.N.P, et Mr R. SADOUN, chargé de cours à l'E.N.P, d'avoir bien voulu accepter d'examiner mon travail de thèse et pour tout l'intérêt qu'ils lui ont accordé.

Mes vifs remerciements vont également à Mr E.M AIT NOURI, du centre de développement des Techniques Avancées (C.D.T.A) pour son aide précieuse et tous ses encouragements à mener à bien mon travail.

Je remercie aussi toute ma famille, particulièrement ma Mère, mes frères, neveux et nièces, mon Oncle Hachemi, sa femme et ses adorables enfants, tous mes amis (ies) ainsi que tous mes collègues et responsables de la direction « Recherches-Développement » de SONELGAZ pour leurs encouragements et leur soutien.

المدرسة الوطنية المتعددة التقنيسات المحكنبية -- BIBLIOTHEQUE المحكنبية --- Ecolo Nationale Polytechnique

## DÉDICACE

JE DÉDIE CE PRÉSENT TRAVAIL À LA MÉMOIRE DE MON PÈRE

ET À LA MÉMOIRE DE CELUI QUI M'A INITIÉ AUX ÉTUDES

ET QUI AURAIT VOULU QUE JE SOIS DOCTEUR,

MON FRÈRE AÎNÉ ABDELKADER.

المدرسة الرطنية المتعددة التقنيات المحكتبة — BIBLIOTHEQUE المحكتبة المحكتبة المحكة ال

## ملخص

إن استعمال محولة تحب المنفصلة (TCD) بشفرة الصور الرقمية في وقتنا الحاضر, مقرر في مختلف القواعد الدولية . الهدف هو ايجاد تطبيقات و حدمات مثل المحاضرة-البصرية و HDTV بحيث لا يمكن تحقيق ذلك إلا بزرع TCD و محولتها العكسية في الدارات المتكاملية (ASICs) نظرا لاحتلالها الطبقات الأكثر عملا. بالرغم من أن معظم حساباتهما تستنتج بالدمج التسلسلي, فإن دبحهما الحسي أصبح هستو العنصر المفتاح في VLSI لضغط الصور.

سنبين في هذا البحث أن هناك خفة عالية في التوافق بين الحسابات و الأشكال بحيث تبقى دائمة باستعمال دراسة مقارنـــة و أدوات حسابية فعالة كالحساب الهوزع و طريقة الحساب بالخط "ON LINE" التي تسمح باشتقاق الحساب الهجين من أحل تكوين شكل موحد

## **RÉSUMÉ**

L'utilisation de la transformée cosinus discrète (T.C.D) en codage d'images numériques, est de nos jours adoptée par les diverses normes internationales. L'objectif d'offrir des applications et des services tels que la visioconférence et la HDTV, reporté sur le codec, ne pourrait être atteint que par l'implantation de la TCD et sa transformée inverse sur des circuits intégrés dédiés (ASICs), vu qu'elles occupent les blocs les plus opérationnels. Quoique la majorité de leurs algorithmes, sont dédiés à une implémentation software, leur implémentation hardware est devenue l'élement-clé en VLSI pour la compression d'image. Dans notre travail de thèse, nous montrons avec une étude comparative, qu'une grande souplesse d'adaptation algorithmes-architectures existe avec l'utilisation d'outils arithmétiques éfficaces tels l'arithmétique distribuée et le mode de calcul half-line qui permettent de dériver un algorithme hybride TCD/TCDI 2-D pour la conception d'une architecture unifiée.

### **ABSTRACT**

Transform coding utilising the discrete cosine transform (DCT) has been adopted in various standards of image compression. As it is the most operative bloc of the encoder's range, the modern digital image systems require fast DCT computational algorithms, especially dedicated to VLSI implementation. In this work, we show that an adequation algorithms-architectures exists and we presente the derivation and the choice of an hybrid algorithm DCT/IDCT 2-D, based on the distributed arithmetic and the half-line mode of computation, in order to obtain a regular unified architecture TCD/TCDI 2-D.

طُمدِرسة الوطنية المتمددة التقنيبات المحكة به BIBLIGTMEQUE من المحكة المجاورة المحاورة المحا

## LISTE DES MOTS-CLES

Synthèse architecturale

Algorithmique rapide

Transformée orthogonale Cosinus Discrète T.C.D

Circuits intégrés dédiés ( ASICs )

Codage d'images

Norme JPEG

Standard H.261

Standard MPEG

Niveaux de description d'un circuit intégré

Systèmes redondants d'écriture des nombres

Arithmétique sérielle ON-LINE et HALF-LINE

Arithmétique distribuée

Adéquation algorithme - architecture

Mémoire ROM à double buffer

Additionneur à retenue conservée (CSA)

Additionneur à retenue anticipée ( CLA )

Additionneur à propagation de retenue ( CPA )

Arbre additionneur multi-niveaux

Modèle de comparaison des ressources architecturales

Modèle de comparaison de Kai-Hwang

SOMMAIRE Ecolo Nationale Polytechnique

| P | Δ | C | F | 5 |

|---|---|---|---|---|

|   |   |   |   |   |

| Introduction Generale                                         | 1  |

|---------------------------------------------------------------|----|

| CHAPITRE 1: GENERALITES SUR LES TECHNIQUES DE CODAGE D'IMAGES |    |

| 1 - Introduction                                              | 5  |

| 2 - NUMERISATION, CODAGE ET COMPRESSION D'IMAGES              |    |

| 2.1 - Techniques de compression d'images.                     |    |

| 2.1.1 - Techniques avec distorsions                           |    |

| 2.1.1.1 - Le codage prédictif                                 |    |

| 2.1.1.2 - Le codage par transformées orthogonales             |    |

| 2.1.1.3 - Le codage hybride                                   |    |

| 2.1.1.4 - Le codage par quantification vectorielle            |    |

| 2.1.1.5 - La technique de troncature de bloc                  |    |

| 2.1.1.6 - Le codage par interpolation.                        |    |

| 2.1.2 - Techniques sans distorsions                           |    |

| 2.1.2.1- Technique des plages                                 |    |

| 2.1.2 2 - Technique des plans de bits.                        |    |

| 2.1.2.3 - Techniques statistiques                             |    |

| 2.2 - Standardisation en codage d'images                      | 11 |

| 2.2.1 - Aperçu sur la norme JPEG.                             | 12 |

| 2.2.1.1 - Propriétés                                          | 12 |

| 2.2.1.2 - Le codage par la transformée TCD                    | 12 |

| 2.2.1.2.a - Codage par TCD séquentielle                       | 13 |

| 2.2.1.2.b - Codage par TCD progressive                        | 13 |

| 2.2.1.2.c - Propriétés                                        | 13 |

| 2.2.1.3 - Image à plusieurs composants.                       | 14 |

| 2.2.2 - Aperçu sur le standard H.261                          | 15 |

| 2.2.2.1 - Codeur                                              | 15 |

| 2.2.2.2 - Codage par transformée                              | 15 |

| 2.2.2.3 - Quantification.                                     | 16 |

| 2.2.2.4 - Types de balayages                                  |    |

| 2.2.2.5 - Estimation de mouvement                             |    |

| 2.2.2.6 - Filtre de la boucle                                 |    |

| 2.2.2.7 - Codage à longueur variable ( CLV )                  |    |

| 2.2.3 - Aperçu sur le standard MPEG                           |    |

| 2.2.3.1 - Réduction de la redondance temporelle               |    |

| 2.2.3.2 - Compensation de mouvement                           |    |

| 2.2.3.3 - Estimation de mouvement                             |    |

| 2.2.3.4 - Réduction de la redondance spatiale                 |    |

| 3 - CONCLUSION                                                | 20 |

| التقنيسات | المتعددة             | الوطنية | ر سد<br>د | ألمار<br>أحجت |

|-----------|----------------------|---------|-----------|---------------|

|           | <u>iEQUE</u><br>anal |         |           |               |

| Chapitre ii : | LA | TRANSFORMEE | Cosinus | DISCRETE T.C.D. |

|---------------|----|-------------|---------|-----------------|

|---------------|----|-------------|---------|-----------------|

| 1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                   |

| 2 - ALGORITHMIQUE RAPIDE DE LA T.C.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| 2.1 - Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                   |

| 2.1.1 - T.C.D unidimensionnelle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21                   |

| 2.1.2 - T.C.D bidimensionnelle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22                   |

| 2.2 - Propriétés                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22                   |

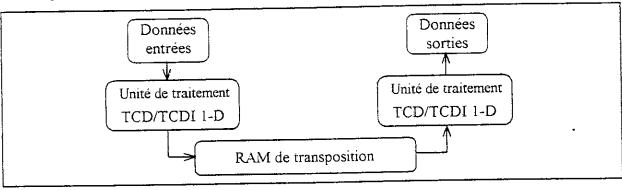

| 2.3 - Algorithmes T.C.D 2-D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | د2                   |

| 2.3.1 - Approche Ligne / Colonne                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                   |

| 2.3.2 - Approche Directe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                   |

| 2.3.2.1 - Algorithme rapide TCD 2-D de N.I.Cho et S.U.Lee                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                   |

| 2.3.2.2 - Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                   |

| 2.4 - Algorithmes T.C.D 1-D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                   |

| 2.4.1 - Décomposition en radical 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32                   |

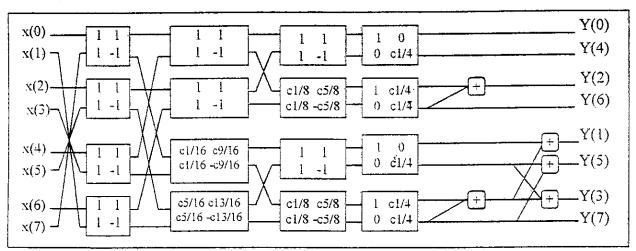

| 2.4.1.1 - Algorithme récursif de Hou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32                   |

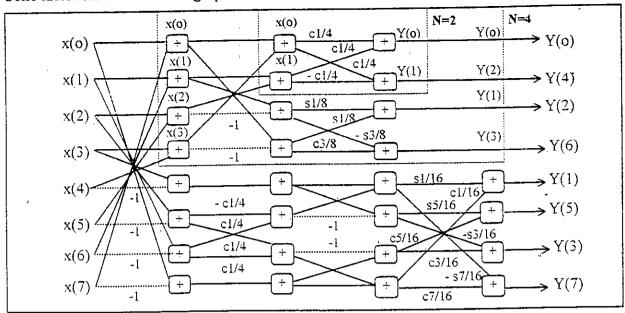

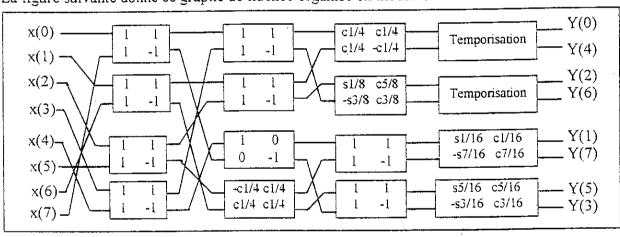

| 2.4.1.2 - Algorithme de Chen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                   |

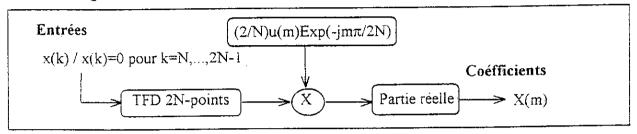

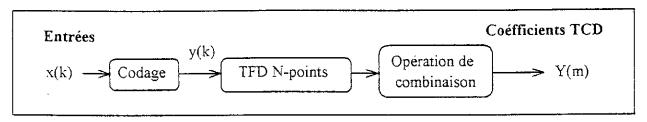

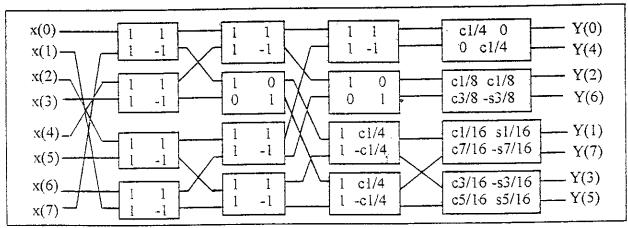

| 2.4.1.3 - Algorithme par T.F.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                   |

| 2.4.2 - Décomposition en radical 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                   |

| 2.4.3 - Décomposition en radical 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                   |

| 2.4.4 - Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                   |

| 3 - CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET ARITHMETIQUE DISTRIBUEE                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46                   |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46<br>46             |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46<br>46<br>46       |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46<br>46<br>46       |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46<br>46<br>47       |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46<br>46<br>47<br>47 |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

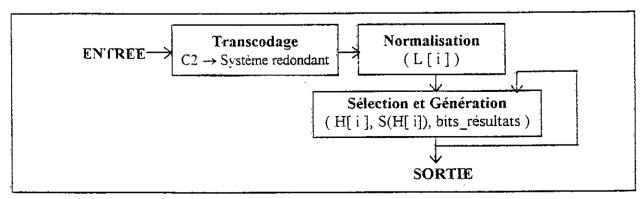

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION.  2 - INCOMMODITES DE L'ARITHMETIQUE CLASSIQUE.  2.1 - Incommodité de la circulation parallèle des opérandes.  2.2 - Incommodité de la propagation de la retenue.  2.3 - Incommodité de la simultanéité.  3 - ARITHMETIQUE « SERIE » OU MODE DE CALCUL SERIEL.  4 - LES SYSTEMES REDONDANTS D'ECRITURE DES NOMBRES.  5 - ARITHMETIQUE ON-LINE ET HALF-LINE.  5.1 - Le mode de calcul On-line.  5.2 - Le mode de calcul Half-line. |                      |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

| CHAPITRE 3: OUTILS ARITHMETIQUES: MODE HALF-LINE ET  ARITHMETIQUE DISTRIBUEE  1 - INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

|                                                          | Scolo Batiocalo Per  |

|----------------------------------------------------------|----------------------|

| 5.6 - Implémentation de l'expression généralisée de la T | C.D                  |

| 5 6 1 - Te bloc de normalisation                         |                      |

| 5.6.1.1. Proposition d'une ROM                           | 56                   |

| 5 6 1 2 - Circuits de décodage de la ROM                 | <i>3</i>             |

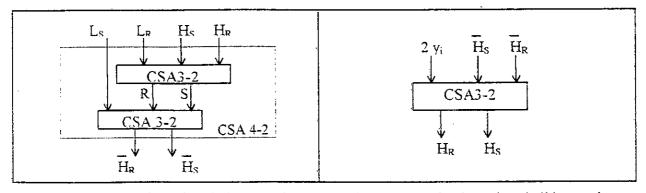

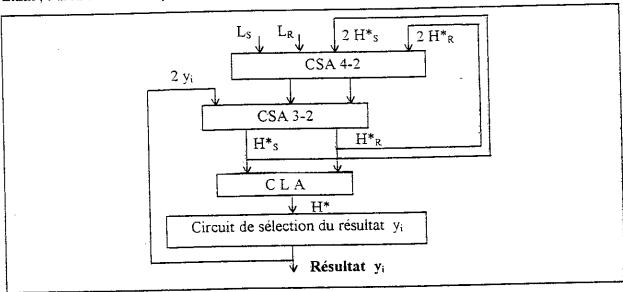

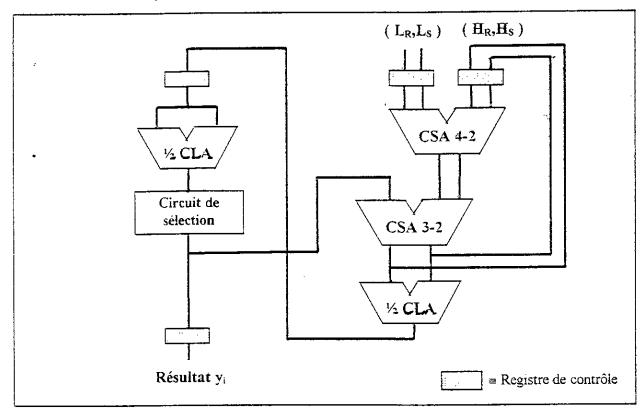

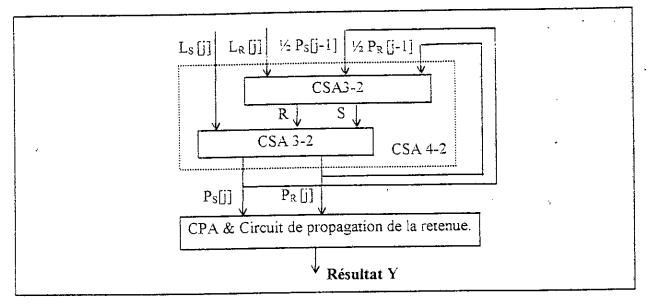

| 5.6.1.3. Additionneur à retenue conservée (CSA)          | 38                   |

| 5 6 1 4 - CSAs multi-niveaux                             |                      |

| 5 6 1 5 - Architecture du bloc de normansation pour      | to radioar o         |

| 5 6 1 6 - Architecture du bloc de normalisation pour     | le radical 8 60      |

| 5 6 2 - Le bloc de sélection                             |                      |

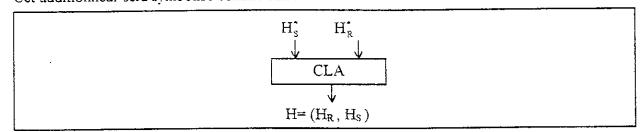

| 5 6 2 1 Additionneur à Retenue Anticinée (CLA)           | 6 <i>i</i>           |

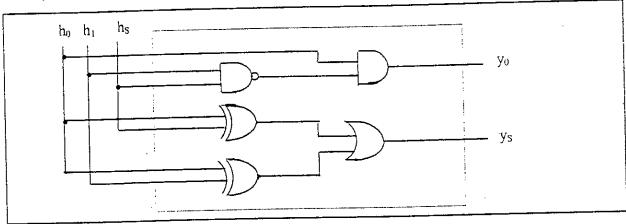

| 5 6 2 2 - Circuit de sélection du bit résultat           |                      |

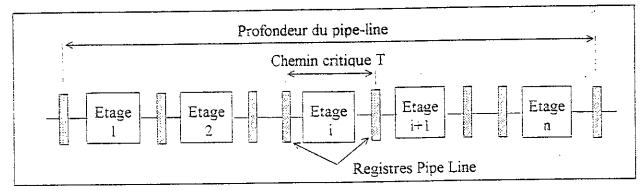

| 5 6 3 - Architecture pipe-linée du bloc de sélection     |                      |

| 5.6.4 - Discussion                                       | 63                   |

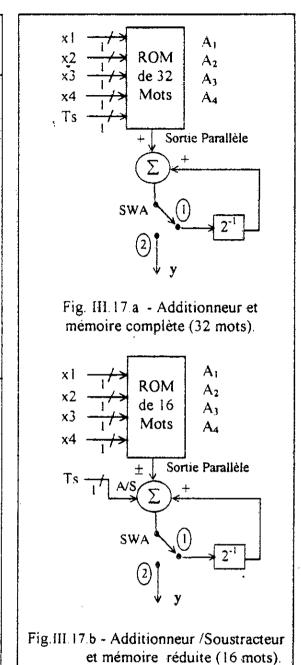

| 6. ARITHMETIQUE DISTRIBUEE (D.A)                         | 66                   |

| 6 1 - Dérivation d'un calcul « arithmétique distribué »  | 66                   |

| 6 2 - Implémentation                                     | 06                   |

| 6 2 1 - Réduction de la taille de la ROM                 | 67                   |

| 6.2.2 - Amélioration de la vitesse de traitement         | 70                   |

| 6.2.3 - Limites de la conception classique               | 71                   |

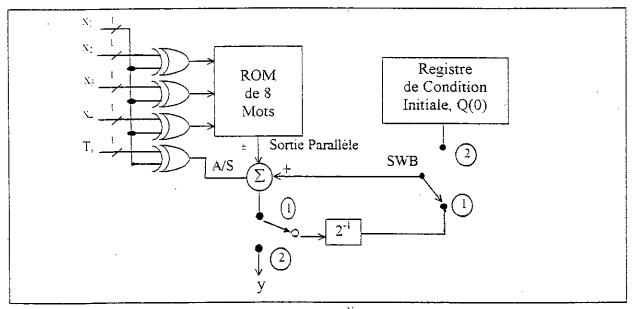

| 6 3 - Optimisation de l'algorithme distribuée de la TCD. | 71                   |

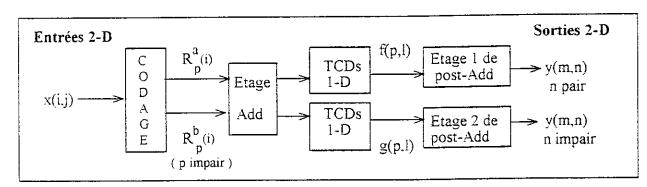

| 6.3.1 - Principe de l'algorithme                         | 71                   |

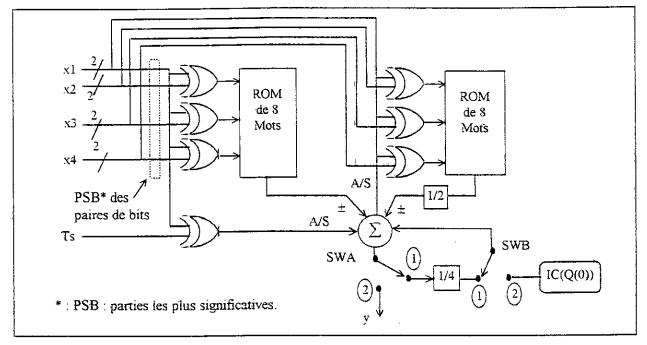

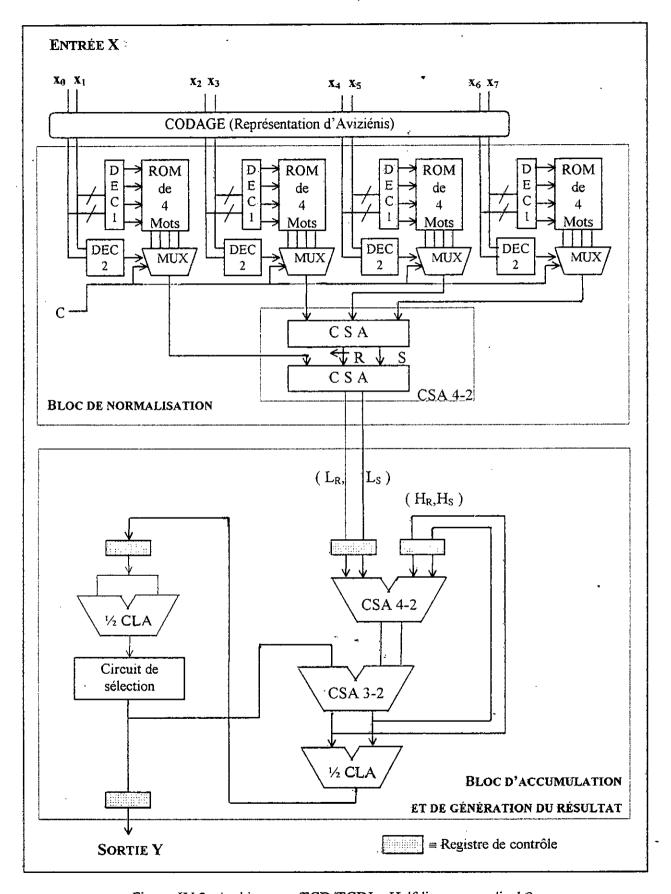

| 6 3 2 - Implémentation de l'expression généralisée de    | la T.C.D 72          |

| 6.3.3 - Etage de Normalisation                           |                      |

| 6.3.3.1 - Architecture du bloc de Normalisation pour     | la T.C.D à radical 8 |

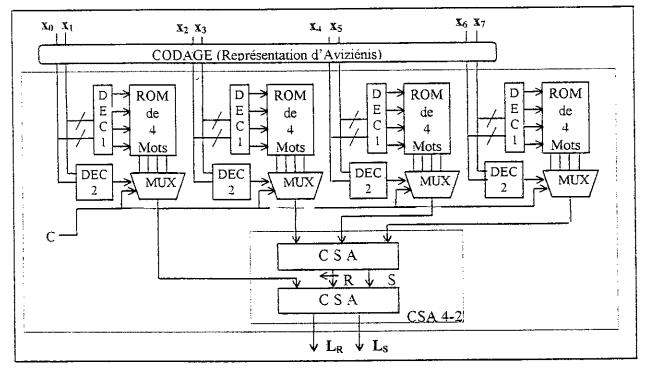

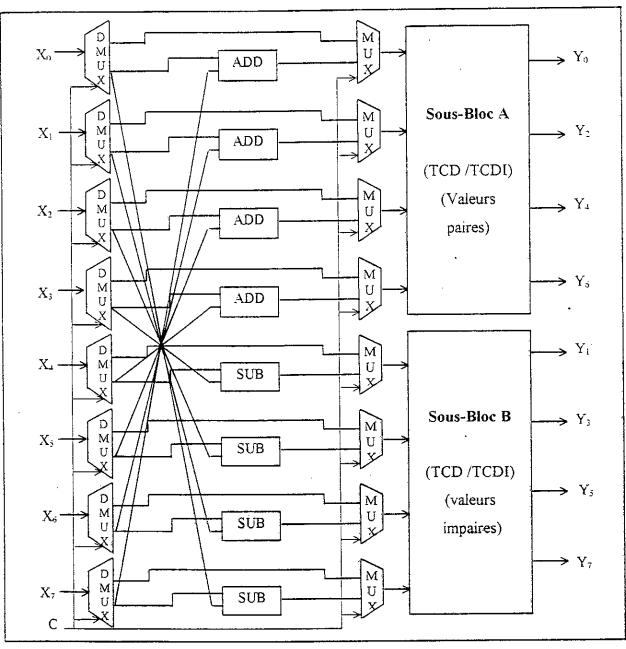

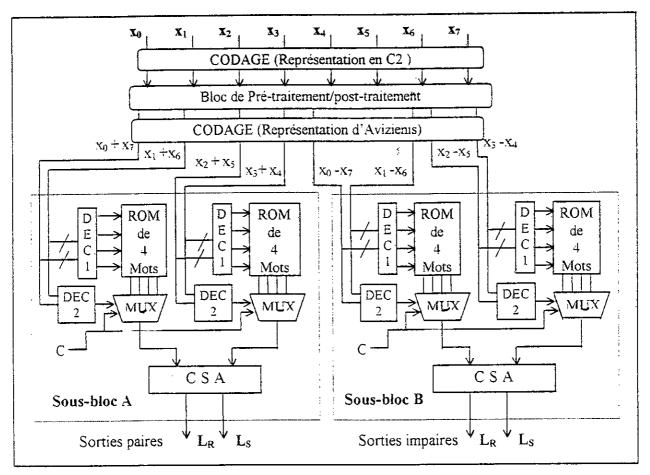

| 6.3.3.2 - Architecture du bloc de Normalisation pour     | la T.C.D à radical 4 |

| 6.3.4 - Etage d'Accumulation                             |                      |

| 6. 3. 4.1 - Additions parallèles                         |                      |

| 6. 3. 4.2 - Propagation de la retenue                    |                      |

| 6.4 - Discussion                                         | 77                   |

| 6.5 - Remarque                                           | 77                   |

| 7. CONCLUSION                                            |                      |

| CHAPITRE 4: COMPARAISON DES ARCHITECTUR                  | ŒS                   |

|                                                          | 70                   |

| 1 - Introduction                                         | 70                   |

| 2 - MODELES DE COMPARAISON                               |                      |

| 2.1- Le modèle de comparaison des ressources architec    | turales79            |

| 2.2. Le modèle de comparaison de Kai Hwang               |                      |

| 3. LA COMPARAISON SPACIALE                               | 80                   |

| 3.1 - L'espace mémoire                                   | 80                   |

| 3.2 - L'espace opératif                                  | 81                   |

Sommaire لمدينة الوطاء

PROGRAMMATION EN LANGAGE C

#### **BIBLIOGRAPHIE**

المدرسة الوطنية المتعددة التقنيبات المحكستيسة -- BIBLIGTHEQUE المحكستيسة -- Ecole Nationalo Polytechnique

# INTRODUCTION GÉNÉRALE

SIGLISTHEQUE - Line Hatienale Pelytochnique

## INTRODUCTION GÉNÉRALE

développement considérables dans les diverses disciplines d'ingénierie. Sa puissance réside dans la multitude d'outils mathématiques rapides et efficaces utilisés pour résoudre et modéliser des applications effectives. Il s'en trouve que l'importance et les performances élevées attendues de certaines applications modernes, ont conduit à développer une nouvelle branche de ces techniques numériques, à savoir l'« Algorithmique Rapide » qui vise à développer des algorithmes rapides de calcul, exploitant au maximum les spécificités du problème traité.

Ces algorithmes rapides gagneraient alors à être implémentés sur des processeurs de calcul pour réaliser les fonctions voulues. Malheureusement, les relations entre algorithmes rapides et architectures de traitement de signal ont évolué pratiquement de manière non-concourante et l'on a même cru, les progrès rapides de la technologie aidant, que le recours à des algorithmes rapides était devenu inutile à cause de la perte de régularité qu'ils introduisent dans leurs graphes de fluence. Aussi, la conception et l'implémentation classiques, efficaces encore pour certaines applications à bat débit, sont vite dépassées et le recours à de nouvelles techniques est devenu incontournable. C'est ainsi que le développement de circuits intégrés spécifiques du type ASIC (en Anglais : Applied Specific Integrated Circuits), est venu répondre aux préoccupations architecturales des applications de traitement en temps réel. La technique et la méthodologie de conception, basées sur la recherche d'une adéquation algorithmes-architectures de l'application considérée, permettent d'arriver à des algorithmes très efficaces une fois implantés.

Le traitement et la transmission d'images sont des applications qui ont bénéficié du développement des techniques numériques et des technologies des semi-conducteurs mais suscitent toujours beaucoup d'intérêt à cause des exigences modernes de traitement de l'information. En effet, des applications comme la visiophonie, la visioconférence, la TVHD ainsi que la consultation des banques de données et d'images, sont des marchés en grande diffusion vu l'importance des services qu'ils offrent. Ces applications présentent certaines difficultés liées en majeure partie au débit des images numérisées traitées. En ce sens que la quantité d'information produite par la numérisation dépassait largement les capacités de stockage et les débits des réseaux existants en dépit des efforts des chercheurs et des organismes de normalisation dans ce domaine.

La réduction du débit et le codage des images de la façon la plus appropriée, sont des domaines de la recherche qui connaissent chaque jour, une innovation. Mais, il reste que l'objectif d'offrir ces services à des prix raisonnables n'est pas entièrement réglé : le problème du coût est surtout reporté sur le CODEC et la solution ne pourra venir que du développement de circuits intégrés ASICs pour ces applications.

Le codage par la transformée orthogonale Cosinus discrète T.C.D est souvent recommandé par les diverses normes internationales de codage d'images. Le développement d'algorithmes rapides de calcul de cette transformée et leur implémentation sur circuits ASICs, sont devenus les éléments-clés de la VLSI de compression d'image. Cette thèse est justement consacrée à la conception d'architectures digitales d'un circuit dédié pour la transformée TCD 2-D et sa transformée inverse TCDI 2-D.

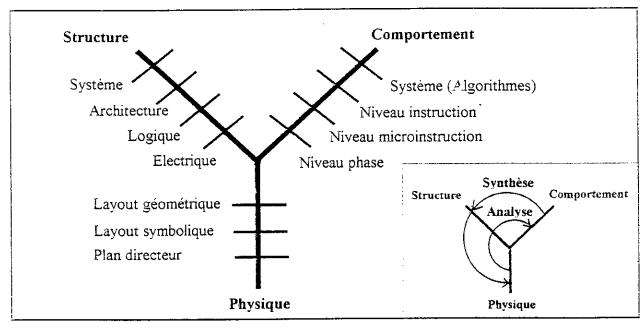

La conception d'architectures est la première phase d'un processus qui doît aboutir à la fabrication du circuit intégré considéré. C'est dans cette phase de conception que s'élaborent les plans du circuit sur la base de ses spécifications fonctionnelles. Dans la méthodologie générale de conception, il y'a trois (03) niveaux de déscription majeurs [1] du circuit à savoir :

- le niveau comportemental s'attachant au fonctionnement du circuit;

- le niveau structurel s'attachant à son architecture;

- et le niveau physique à sa réalisation matérièlle.

Ces niveaux d'abstraction peuvent être représentés selon les trois (03) branches de la représentation en Y de la figure 1, proposée par D.D.Gajski [2].

Figure 1 - Représentation en Y des niveaux de déscription d'un circuit intégré.

Notre travail dans cette thèse, s'inscrit donc dans le passage du premier au second niveau de description c'est-à-dire du niveau comportemental au niveau structurel. Notre objectif est de concevoir une architecture pour un ASIC unifié TCD 2-D / TCDI 2-D sans pour autant arriver au niveau électrique du circuit. C'est un travail de synthèse entre le niveau comportemental « algorithmes » et le niveau structurel « architecture ». Ce travail est finalisé par une étude comparative des architectures obtenues en fonction du mode de calcul adopté : l'arithmétique distribuée et le mode de calcul « half-line ».

Cette thèse est composée de cinq (04) chapitres élaborés comme suit :

- Le chapitre I est un rappel des généralités sur des techniques de compression d'images, et un résumé des spécifications des standards internationaux dans ce domaine comme la norme JPEG, la norme H.261 et la norme MPEG, pour montrer l'utilité et les avantages de l'utilisation de la transformée Cosinus discrète T.C.D en codage d'images.

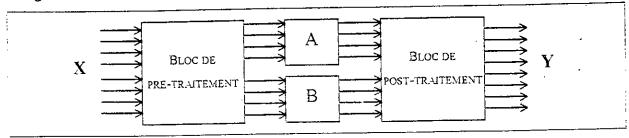

- Le chapitre II est une revue générale des algorithmes bidimensionnels et unidimensionnels de la TCD et son inverse TCDI. Nous y montrons très clairement, que ces algorithmes ont été proposés sans grande préoccupation architecturale aussi bien avec l'approche de calcul direct TCD 2-D qu'avec l'approche conventionnelle ligne/colonne de calcul TCD 1-D, l'objectif étant de minimiser le nombre de multiplications, quels que soient les autres coûts associés. Les algorithmes de décomposition en radical 2, 4 et 8 de cette transformée, y sont sélectionnés pour trouver des artifices d'adaptation et d'adéquation algorithmes-architectures pour arriver à des architectures cibles unifiées possibles pour la TCD 2-D/TCDI 2-D. Nous y montrons aussi que le calcul de ces transformées se résume et ne peut se faire pour l'objectif assigné dans cette thèse, qu'avec une expression paramètrée complexe en radical 4 et 8.

- Le chapitre III montre que le processus de calcul des transformées orthogonales discrètes est caractérisée par une structure parallélo-séquentielle dont les performances d'exécution sont dues à son aspect parallèle. La diminution des contraintes inhérentes au traitement séquentiel, n'a pas été suffisamment approchée dans les diverses études menées sur le calcul des transformées orthogonales. Ce chapitre montre que toutes les possibilités algorithmiques sont conditionnées par les modes de calcul utilisés par les opérateurs arithmétiques, et que l'amélioration du calcul de ces transformées peut être obtenue en utilisant des arithmétiques adéquates comme le mode de calcul « half-line » et l'arithmétique distribuée, et révèle les architectures obtenues.

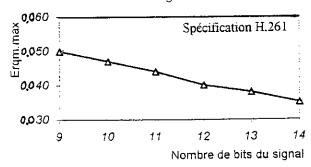

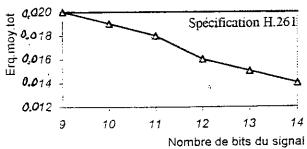

- Le chapitre IV est une comparaison des architectures obtenues avec les outils arithmétiques utilisés, tant du point de vue des ressources architecturales utilisées, le temps de propagation global. la fréquence de traitement ainsi que la précision de chaque algorithme. Des modèles de comparaison y sont donnés avec des résultats de programmation et la discussion du choix final de l'architecture unifiée à adopter compte tenu de l'étude comparative présentée.

- La conclusion générale et les recommandations de notre travail.

- Enfin, la bibliographie utilisée ainsi que deux annexes, sont données à la fin cette thèse :

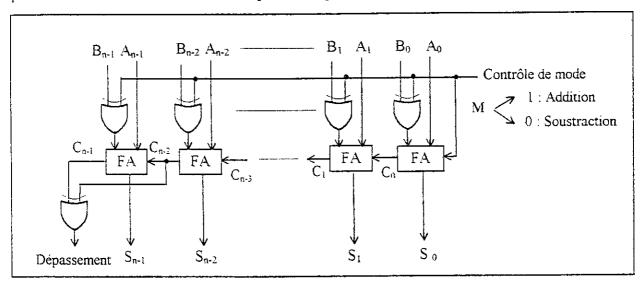

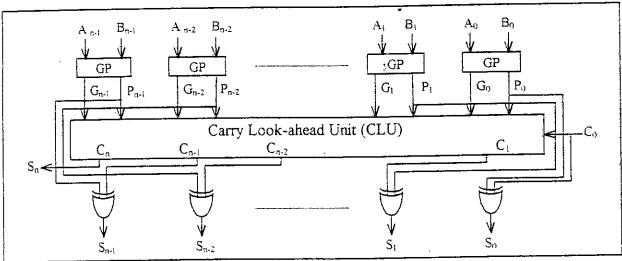

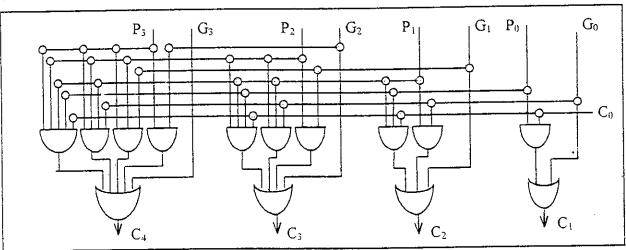

- · l'annexe A traitant des additionneurs parallèles ;

- et l'annexe B donnant la programmation en langage C des algorithmes de la TCD avec le mode de calcul half-line et l'arithmétique distribuée.

## **CHAPITRE I**

## GÉNÉRALITÉS SUR LA COMPRESSION D'IMAGES

### 1 - INTRODUCTION

Le traitement numérique du signal est l'une des techniques les plus largement utilisée dans diverses activités de l'ingénierie et connaissant aujourd'hui un essor considérable dans les disciplines recherchant des outils mathématiques rapides et efficaces. L'« Algorithmique Rapide » qui a fini par constituer une branche en soi du traitement du signal, s'attache à utiliser au maximum la spécificité du problème traité. Les transformées rapides de signal constituent essentiellement la base de cette nouvelle branche, notamment les transformées orthogonales telles que la transformée Cosinus Discrète T.C.D développée par N. Ahmed et al. [3] en 1974, utilisée en compression de données et réduction de débit. D'où l'intérêt de présenter dans ce chapitre, les techniques de compression d'images dans une thèse consacrée à la T.C.D et son inverse T.C.D.I.

Le traitement et la transmission d'images suscitent toujours beaucoup d'intérêt mais présentent certaines difficultés liées en majeure partie au débit de l'image numérisée traitée. En effet, la quantité d'information produite par la numérisation d'image dépassait largement les capacités de stockage et les débits des réseaux existants. Il est devenu donc nécessaire de réduire le débit et de chercher à coder l'image de la façon la plus appropriée. Comme nous le verrons plus loin, la T.C.D est très utilisée dans ce domaine.

Par ailleurs, l'homogénéité et la compatibilité des représentations devaient passer par la standardisation du codage, du stockage, de l'échange et de la restitution des informations manipulées. Ceci a fait que l'activité des organismes internationaux de normalisation a été très intense notamment au cours des quinze (15) dernières années en compression d'image dans le but d'offrir des services à bas débit. En effet, des applications comme la visiophonie, la visioconférence, la TVHD, le stockage sur CD-ROM ainsi que la consultation des banques de données et d'images sont des marchés de grande diffusion, estimés très importants.

Il reste que l'objectif d'offrir ces services à des prix raisonnables n'est pas entièrement réglé : le problème du coût est reporté sur le codec. La solution ne pourra venir que du développement de circuits intégrés ASICs dédiés aux fonctions de ce codec.

## 2 - NUMERISATION, CODAGE ET COMPRESSION D'IMAGES

La numérisation des images a été introduite pour le stockage d'une copie fidèle de l'image originale afin de permettre des traitements plus ou moins complexes. Numériser une image revient à la mettre sous forme d'un tableau de «pixels». A chaque pixel est affectée une valeur numérique codée généralement sur 8 bits.

L'image digitale standard est définie dans la norme CCIR comme étant composée de trois signaux électriques : Y est le signal de luminance, CB et CR sont les signaux de différence de couleurs. Ces signaux sont généres par la matrice des signaux primaires y, r, g et b tels que :

$$\begin{cases} y = 0.299r + 0.587g + 0.114b \\ Y = 219y + 16 \\ CR = 112(r - y) / 0.701 + 128 \\ CB = 112(b - y) / 0.886 + 128 \end{cases}$$

La fréquence d'échantillonnage est de 13.5 MHz pour la luminance Y, et de 6.75 MHz pour les signaux CB et CR. Ainsi pour tout système, le nombre d'échantillons par ligne a été fixé à 720 pixels pour la luminance, 360 pixels pour les signaux CB et CR; chaque pixel étant codé sur 8 bits.

Mais, Il est vite apparu que la quantité d'informations produite par la numérisation n'était pas en adéquation avec les capacités de stockage et les débits de transmission des réseaux existants. La mise en œuvre d'algorithmes de compression est devenue alors une nécessité.

#### 2.1 - TECHNIQUES DE COMPRESSION D'IMAGES

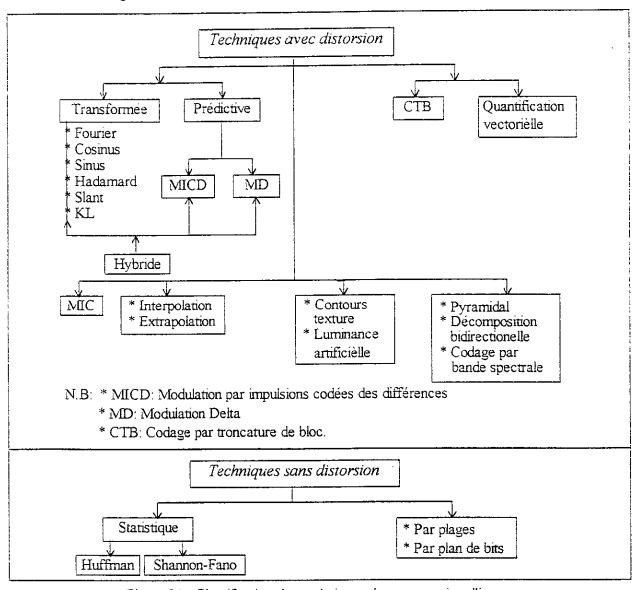

Les techniques de compression sont classées (Fig. I.1) selon deux critères [4] [5] :

Le premier critère est lié à la distorsion apportée à l'image originale, il s'agit :

- des techniques sans distorsion restituant exactement les pixels de l'image source;

- des techniques qui apportent une distorsion aux images reconstruites, indécelable à l'oeil nu.

Le second critère est lié au domaine de leur application, selon que nous avons :

- des techniques spatiales appliquées directement aux pixels de l'image;

- des techniques transformées travaillant dans le domaine « transformé » après l'application d'une transformation orthogonale aux pixels.

#### 2.1.1 - TECHNIQUES AVEC DISTORSIONS

#### 2.1.1.1 - CODAGE PREDICTIF [6] [7]

La technique MICD, modulation à impulsion codée différentielle, est le codage de type prédictif le plus classique. Le principe est qu'un prédicteur établit une estimation de chaque pixel à partir de ses voisins immédiats (le pixel précédent en général).

L'écart  $\epsilon$  entre la luminance Y du pixel et sa valeur de prédiction  $Y_{pr}$ :  $\epsilon = Y - Y_{pr}$ , est quantifiée puis transmise à la sortie du codeur telle que :  $S = \epsilon$   $Q = \epsilon_Q$  où  $\epsilon_Q$  est l'erreur de prédiction quantifiée. Le nombre de ces valeurs quantifiées étant restreint, un plus petit nombre de bits est utilisé pour leur codage. C'est à ce niveau que se fait la réduction du débit. A la réception, le décodeur reçoit l'erreur de prédiction et l'ajoute à son propre prédicteur (le même que celui du

codeur) :  $Y' = \epsilon_Q + Y_{pr}$ . Le résultat ne diffère de la valeur exacte que de l'erreur de quantification. C'est la quantification de ces écarts qui est à la base de la réduction du débit nécessaire au codage de ces erreurs, et de la réduction du débit numérique de l'image. Bien sûr. cette méthode n'est pas sans effet sur la qualité de l'image transmise, mais avec 16 niveaux de quantification, les défauts de codage sont tolérés par l'œil humain.

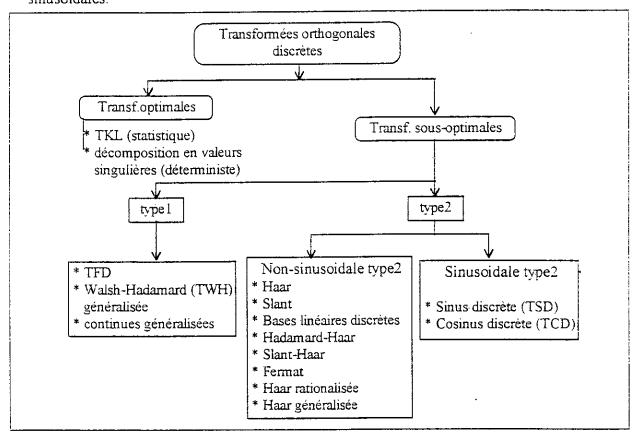

## 2.1.1.2 - CODAGE PAR TRANSFORMEES ORTHOGONALES [8] [9] [10]

Cette technique consiste en la représentation de l'image dans un domaine où la séparation de l'information pertinente de l'information redondante est plus facile. Les transformations orthogonales s'appliquent sur des blocs d'image, de dimension NxN. La taille de ces blocs doit être suffisante pour que la corrélation entre les points les plus éloignés du bloc, soit négligeable. Elle est dite « longueur de corrélation », et est fixée généralement à 8x8 ou 16x16 pixels.

Figure I.1- Classification des techniques de compression d'images.

La transformée orthogonale optimale au sens statistique [11] en codage d'image est la transformée de Karhunen-Lœve (TKL). Malheureusement, son implémentation n'est pas envisageable en temps réel vu qu'elle dépend de l'image traitée. Les autres transformées sont dites sous optimales parce qu'elles ne décorrelent pas totalement la séquence de données mais permettent une implémentation hardware.

La figure I.2 donne la classification de ces transformées en deux catégories:

- 1. Transformations optimales;

- 2. Transformations sous optimales

La catégorie des transformées sous-optimales est répartie en deux catégories :

- type 1 dont les fonctions de base reposent sur le cercle unité;

- type 2 dont les fonctions de base sont soit des fonctions sinusoïdales, soit des fonctions nonsinusoidales.

Figure I.2 - Classification des transformées orthogonales discrètes [11].

Parmi toutes ces transformées, les plus utilisées sont :

- La transformée de Hadamard-Walsh (TWH);

- La transformée de Fourrier discrète (TFD);

- La transformée de Karhunen-Lœve (TKL);

- La transformée Cosinus discrète (TCD).

En effet, ces transformées ont les propriétés communes suivantes:

- Les coefficients obtenus peuvent être interprétés comme des fréquences. L'information relative à la texture et au contour des objets, est contenue dans les basses fréquences et l'information relative à l'éclairage général de la scène, est contenue dans les hautes fréquences.

- Ces transformées ont plus ou moins la capacité de décorréler les pixels du bloc initial. Ceci revient à interpréter chaque coefficient en fonction de tous les pixels de l'image initiale de telle sorte que ces coefficients soient statistiquement indépendants. Ce qui permet de coder indépendamment les coefficients et d'éliminer la redondance.

- Dans le plan transformé, l'énergie est concentrée aux faibles fréquences spatiales

- Le coefficient X(0,0) est appelé coefficient continu, et a la plus grande valeur dans un bloc

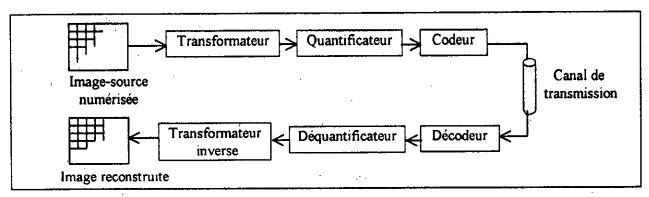

Après la transformation, les coefficients subissent des opérations de quantification et de codage. L'ensemble {transformateur, quantificateur, codeur } ainsi que les opérations inverses constituent la chaîne de transmission appelée « CODEC » illustrée par la figure suivante :

Figure I.3 - Chaine de transmission CODEC à base de transformations orthogonales.

Le bloc transformateur opère le changement de représentation de l'image du domaine temporel vers le domaine fréquentièl spatial. Il ne fait pas de réduction de débit en lui-même mais permet de séparer l'information utile de l'information redondante. Ses performances dépendent du choix de la transformée à adopter à savoir par ordre croissant la TWH, la TFD, la TCD, la TKL. Quoique optimale, la TKL est restée à l'état de concept théorique car ses fonctions de base sont les vecteurs propres de la matrice de covariance de la séquence traitée. Quant à la TFD, elle est utilisée pour calculer la TCD.

Il reste que la TCD est la transformée adoptée par les différentes normes de compression d'image car elle est asymptotiquement équivalente à la TKL. Elle exprime chaque pixel en fonction d'une somme des coefficients multipliés par des fonction de base trigonométrique qui sont une classe des polynômes Chébyshev discrets. Son application ne dépend pas de l'image considérée et la connaissance de ses coefficients suffit pour reconstituer l'image source.

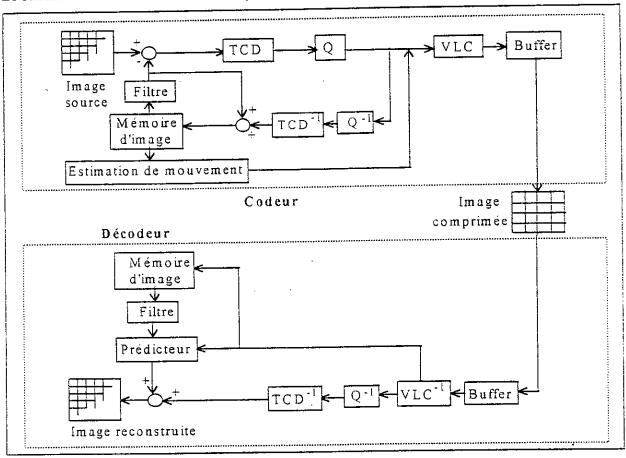

#### 2.1.1.3 - CODAGE HYBRIDE [12] [13]

Cette technique combine les deux précédents : le codage prédictif et le codage par TCD.

La figure suivante montre les différentes étapes suivies.

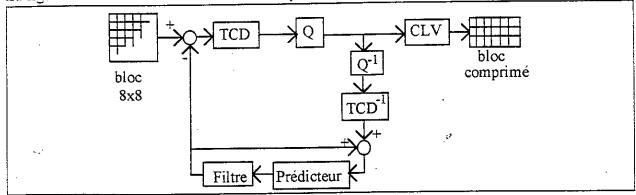

Figure I.4 - Codeur hybride avec compensation de mouvement.

La notion de « compensation de mouvement » signifie que le codec consistera à implémenter un codage prédictif « temporel » et un codage par transformée « spatial ». Cette notion sera plus explicitée dans la norme H.261 adoptée pour la visiophonie. Notons que ce codage nécessite l'utilisation de la transformée TCD et son inverse TCDI.

#### 2.1.1.4 - CODAGE PAR QUANTIFICATION VECTORIELLE [14] [15]

L'image est découpée en petits blocs de pixels. Lors de la transmission, chaque bloc est comparé à un ensemble de vecteurs prédéfinis. Cet ensemble de vecteurs (dictionnaire) est présent au niveau du décodeur, et l'adresse du vecteur le plus proche est transmise. La taille des blocs utilisés, est 4x4 ou 8x8.

La difficulté de cette technique réside dans le développement d'un dictionnaire de vecteurs précis. Il est construit en choisissant statistiquement un ensemble de blocs représentatifs d'un ensemble fini d'images. L'algorithme le plus connu est l'algorithme LBG [16].

Cette technique présente plusieurs atouts, et peut être combinée avec d'autres schémas de codage pour donner un codeur plus efficace.

#### 2.1.1.5 - TECHNIQUE DE TRONCATURE DE BLOC [17]

L'image set décomposée en blocs de pixels, qui seront codés indépendamment. Dans chaque bloc, la moyenne « m » et l'écart-type « e » sont calculés. Ces derniers sont quantifiés puis transmis avec une matrice de signes indiquant pour chaque point du bloc s'il se trouve au dessus ou au dessous de cette moyenne. La valeur restituée est (m-e) ou (m+e) selon les cas.

#### 2.1.1.6 - CODAGE PAR INTERPOLATION [4]

Cette technique envoie seulement un sous-ensemble de pixels de l'image. A la réception, une interpolation est faite pour retrouver les pixels non transmis et ainsi reconstruire l'imagé tout entière.

### 2.1.2 - TECHNIQUES SANS DISTORSIONS

#### 2.1.2.1- TECHNIQUE DES PLAGES [18] [19]

Sur une ligne de la matrice représentant une image, plusieurs échantillons peuvent avoir la même valeur. L'ensemble de ces échantillons est appelé « plage ». Cette technique consistera à décrire ces suites de pixels identiques par leur longueur et leur valeur. Par exemple, une suite de 10 pixels noirs sera décrite par deux nombres : 10 et 0.

Cette méthode est d'autant plus efficace que le nombre de niveaux de gris possibles, est faible.

## 2.1.2.2 - TECHNIQUE DES PLANS DE BITS [18] [20]

Dans cette technique, les pixels d'une image numérique NxN sont codés sur M bits. Le j<sup>ième</sup> bit de chaque échantillon est isolé pour obtenir M images binaires de dimension NxN, appelées « plans de bits ». On pourra appliquer à chacune d'elles, des méthodes de compression spécialement développées pour des images binaires.

#### 2.1.2.3 - TECHNIQUES STATISTIQUES [7] [21]

Ces techniques dites ponctuelles font associer à chaque pixel de l'image un mot de code dont la longueur dépend de la probabilité d'apparition du niveau de gris correspondant. Les techniques de codage les plus performantes sont celles de Huffman et Shannon-Fano.

Ces méthodes sont connues sous le nom de méthodes VLC (variable length cod). Elles peuvent être combinées aux méthodes de codage prédictif ou par transformée.

#### 2.2 - STANDARDISATION EN CODAGE D'IMAGES

Les travaux de normalisation peuvent être classés en quatre parties suivant les services voulus et les applications :

- Transmission et stockage des images fixes;

- Visiophonie, visioconférence et visioréunion;

- Applications T.V. et stockage sur support numérique;

- Réseaux de communications multimédias .

Notons qu'actuellement, beaucoup de laboratoires ne travaillent plus sur le côté algorithmique mais axent leurs recherches sur l'implémentation d'algorithmes existants répondant aux spécifications de normalisation, sur des architectures intégrées. On trouve essentiellement trois (03) normes adoptées pour la compression d'image :

- JPEG pour la compression des images fixes;

- H.261 pour l'algorithme de codage pour la visiophonie;

- MPEG pour la compression d'images animées.

## 2.2.1 - APERCU SUR LA NORME JPEG [22]

La norme JPEG (Joint Photographic Experts Group) est destinée pour le stockage et la restitution des images fixes, monochromes ou couleurs, sur les supports numériques pour des applications comme le fac simili, la vidéotex, la conférence audiographique ...etc. Ses spécifications portent sur les éléments suivants :

- les procédures de conversion de l'image source en image comprimée;

- les procédures de conversion de l'image comprimée en image reconstruite;

- un aperçu sur l'implémentation de ces procédures sur le plan architectural;

- les différentes méthodes à choisir pour le codage et le décodage à savoir :

- le codage par la transformée orthogonale discrète TCD;

- · le codage prédictif « sans pertes ».

Cette norme considère qu'une image numérique est constituée de plusieurs composants; l'image couleurs en possède trois : un composant pour la luminance et deux pour la chrominance; tandis que l'image monochrome n'a qu'un seul composant. Pour le codage à base de TCD, un échantillon est une matrice carrée de 8x8 pixels, dite bloc. Tandis que pour le codage prédictif, les échantillons sont simplement les pixels.

Dans ce qui suit, nous considérons une image monochrome et pour l'image multi-composants, nous donnerons à la fin la procédure de son codage.

#### 2.2.1.1 - Propriétés

- Un pixel est un entier à valeur prise dans le domaine [0, 2<sup>P-1</sup>] avec une précision P de 8 bits, soit un domaine de valeurs possibles des pixels : [0, 255].

- Le balayage de l'image (du composant) se fait de gauche à droite et de haut en bas.

#### 2.2.1.2 - Le codage par la transformée TCD

La norme JPEG spécifie deux (02) méthodes basées sur la TCD :

- Le codage séquentiel;

- Le codage progressif.

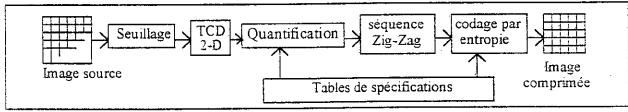

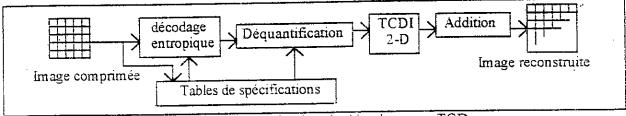

Les figures suivantes donnent les chaînes de codage et de décodage par la TCD.

Figure I.5.a - Chaine de codage par TCD

figure I.5.b - Chaine de décodage par TCD

#### 2.2.1.2.a - Codage par TCD séquentielle

Les échantillons par blocs 8x8, sont introduits de gauche à droite, rangée par rangée et de haut en bas. Après que le bloc ait été quantifié, les 64 coefficients peuvent être codés immédiatement puis transmis.

#### 2.2.1.2.b - Codage par TCD progressive

Les blocs sont introduits de la même façon que précèdemment, mais le codage se fait en plusieurs balayages. Ceci est fait avec l'insertion entre le quantificateur et le codeur d'un buffer pour mémoriser l'image.

Il existe deux (02) procédures de codage des coefficients quantifiés dans le buffer :

- Une sélection «spatiale» tenant compte de la répartition fréquentielle des coefficients, est faite dans le buffer. Une bande précise du spectre de fréquence, est envoyée à la fois vers le codeur.

- Les coefficients quantifiés de la bande de fréquence sélectionnée, sont partiellement codés en commençant par les bits MSB. Les bits LSB sont codés ultérieurement lors de balayages multiples.

#### 2.2.1.2.c - Propriétés

- Le seuillage: il consiste à décaler avant le codage, les valeurs du domaine [0, 2<sup>P</sup> [ au domaine [-2<sup>P-1</sup>, 2 <sup>P</sup>] en soustrayant la valeur 2 <sup>P-1</sup> à chaque coefficient. Cette opération est d'un grand intérêt du fait qu'il introduit une représentation signée qui sera mise à contribution lors du codage entropique. Au décodage, la quantité 2<sup>P-1</sup> est bien sûr rajoutée aux valeurs sortantes de la TCDI pour restituer l'image source.

- Le balayage: L'orientation dans un bloc se fait de gauche à droite, et de haut en bas.

- La quantification: A la sortie du bloc TCD, chacun des 64 coefficients Y(m,n) obtenus, se présente à la quantification. Celle-ci est uniforme pour tous les blocs de l'image. A chaque coefficient Y(m,n), correspond un pas de quantification Q<sub>mn</sub>.

Les coefficients quantifiés  $Y_q(m,n)$  sont définis par :  $Y_q(m,n)$  = Round  $\{Y(m,n) / Q_{m,n}\}$  où « Round » est la fonction « entier le plus prêt ». L'opération de quantification peut être subdivisée en deux (02) phases :

- Normalisation des coefficients pour ajuster leur dynamique :  $Y_N(m,n) = Y(m,n) / Q_{m,n}$ ;

- Application de la fonction « Round » : entier [ $Y_N(m,n) + 0.5$ ].

Au décodage, la déquantification se fera comme suit :  $R(m,n) = Y_N(m,n) * Q_{m,n}$  où R(m,n) sont les coefficients déquantifiés.

- Le codage différentiel de la composante continue DC: On note par DC, la première valeur Y(0,0) du bloc 8x8 transformé. Cette valeur représente la composante continue du signal variant dans l'espace (luminance ou chrominance). Après la quantification, le coefficient DC quantifié (Yq(0,0)) est traité séparément des 63 autres coefficients du bloc notés AC pour composantes alternatives. Le codage de Yq(0,0) se fera de manière différentielle. En effet, vu que le coefficient DC varie peu d'un bloc à un autre, il est préféré de coder la différence par la technique MICD.

- La séquence zigzag: Du fait de la propriété de la TCD de concentration du maximum d'informations aux basses fréquences, les 63 coefficients AC quantifiés sont convertis en une séquence zigzag notée ZZ, pour les positionner dans un vecteur ligne et les préparer au codage entropique. Ainsi on peut avoir des séquences de zéros qui faciliteront le codage.

- Le codage par entropie : Les séquences de codage différentiel pour le DC et RUN-LENGHT pour les AC, sont comprimées à l'aide du codage par entropie. La norme JPEG spécifie deux (02) sortes de codage qui permettent de réduire l'entropie:

- · Le codage par la méthode de Huffman;

- Le codage arithmétique.

Le codage de Huffman est préféré au second du fait de sa simplicité d'implémentation. Chaque valeur prête au codage par entropie, possède deux (02) informations : sa valeur exacte et la longueur de ses bits. Une étude statistique permet de regrouper les valeurs spécifiques au nombre de leurs bits, c-à-d que deux valeurs au même nombre de bits, sont d'une même catégorie. La catégorie, ayant la plus grande probabilité d'apparition, est codée par le minimum de bits, et celle qui a la faible probabilité d'apparition, est codée par un maximum de bits. Deux algorithmes génèrent deux tables de codage: le code de la catégorie noté Huff size, et celui de la longueur associé noté Huff code.

#### 2.2.1.3 - Image à plusieurs composants

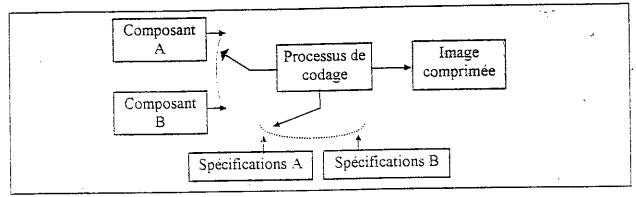

La procédure d'échantillonnage illustrée ci-dessous, est dite « interchangeable ». En effet, pour certaines images, nous ne pouvons pas coder complètement un composant puis passer à un autre. L'échantillonnage interchangeable signifie qu'on code un échantillon du composant A, puis on passe à un échantillon similaire du composant B, puis on revient à un autre échantillon de A, et ainsi de suite. Il faudra que les composants constituant l'image, aient la même dimension, le même nombre de lignes, et le même nombre de colonnes. Les tables de spécifications étant différentes d'un composant à un autre.

Figure I.6 - Procédure d'échantillonnage d'une image multi-composants.

## 2.2.2 - APERCU SUR LE STANDARD H.261 [23] [24]

L'un des premiers standards pour la représentation de l'image animée, est celui du CCITT H.120 qui décrit les versions 625 lignes 50 trames/s et 525 lignes 60 trames/s du codec pour la vidéoconférence. Le H.261 est le standard destiné pour le codage d'images animées pour la visiophonie, connu sous le nom de standard à p x 64 Kbit/s pour ses débits variant de 64 Kbit/s à 2 Mbit/s par pas de 64 Kbit/s. Il utilise un codage dit « hybride », qui combine les techniques de codage par TCD pour réduire la redondance spatiale (codage intra-trames), et le codage prédictif pour réduire la redondance temporelle (codage inter-trames).

#### 2.2.2.1 - Codeur

Le codeur hybride donné précédemment par la figure I.4, réalise les fonctions suivantes :

- L'acquisition numérique de l'image (changement de standard, sous-échantillonnage temporel,..)

- La prédiction avec compensation de mouvement et filtrage dans la boucle. Les images animées ont en effet une forte corrélation temporelle, la prédiction estime la valeur du signal à transmettre afin de n'en coder que la partie innovatrice.

- Les transformées TCD et TCDI.

- La quantification des coefficients transformés et le codage entropique des données (pour n'en conserver que ceux qui sont significatifs).

- ▶ Le multiplexage vidéo des informations (synchronisation, types de codage, vecteurs de mouvement, coefficients...).

#### 2.2.2.2 - Codage par transformée

Dans le modèle de référence adopté par le groupe XV du CCITT, une TCD 2-D est utilisée avec des blocs 8x8 pixels. La normalisation de l'implémentation de l'algorithme TCDI est nécessaire vu les problèmes de non-correspondance de la transformée, dus à l'utilisation de deux circuits différents pour la TCD dans le codeur et le décodeur. Pour les circuits de calcul de la TCD, 9 bits sont utilisés en entrée et 12 bits en sortie.

#### 2.2.2.3 - Quantification:

La quantification, étape importante après la TCD, sert à réduire la redondance et à représenter les coefficients par un mot binaire de longueur finie, en tenant de :

- la définition d'un critère convenable pour obtenir les valeurs de quantification.

- l'exploitation de la corrélation résiduelle parmi les variables.

- la sélection des paramètres de quantification suivant des critères psychovisuels.

- le moyen de contrôler la quantité de données produites par les variations de tels paramètres.

Cette opération fait que les coefficients quantifiés sont tronqués, produisant ainsi un bruit. La réduction de ce bruit et la minimisation de la distorsion sont nécessaires.

#### 2.2.2.4 - Types de balayages

Après la quantification, les coefficients doivent être transmis avec un moyen efficace. La puissance des coefficients est usuellement concentrée dans les séquences d'ordre faible. Le bloc quantifié comprend des coefficients nuls et des coefficients non nuls. Un moyen pour éliminer la dernière chaîne de composantes nulles consiste à appliquer une méthode prédéfinie pour transmettre les coefficients, appelée « balayage » en combinaison avec un code de « fin de bloc ».

Il existe plusieurs types de balayages:

- Balayage en zigzag qui est le plus prometteur;

- Balayage vertical;

- Balayage horizontal;

- Balayage diagonal.

Deux balayages sont fait pour limiter le nombre de coefficients à transmettre :

- Le premier balayage donne une indication sur le nombre de coefficients nuls et non nuls;

- Le second (dans le sens inverse) retrouve le dernier coefficient non nul. Un flag est mis à 1 pour indiquer que le dernier coefficient non nul est retrouvé, et commencer le bloc suivant.

#### 2.2.2.5 - Estimation de mouvement

L'estimation de mouvement est basée sur l'hypothèse que des pixels adjacents ont les mêmes paramètres de déplacement. Un vecteur de mouvement est obtenu en faisant correspondre une fenêtre de mesure rectangulaire, comportant un certain nombre de pixels adjacents avec une fenêtre de mesure correspondante dans l'image suivante. La correspondance est réalisée en recherchant l'extrême d'un critère par exemple la moyenne de la différence absolue de l'image déplacée. L'efficacité de l'estimation dépend de la taille des fenêtres, conjointement avec la quantité actuelle du mouvement. Pour traiter de grands déplacements, il faut des fenêtres de

grandes taille. La méthode adoptée n'est pas normalisée, seule la procédure de transmission des vecteurs de mouvement, est normalisée.

Un bon algorithme d'estimation de mouvement est caractérisé par une bonne précision, un faible effort de calcul, un vrai vecteur de mouvement, et une faible quantité d'information à transmettre. En principe pour bien estimer le mouvement, deux objectifs sont à considérer :

- Une prédiction compensée de mouvement;

- Une interpolation (ou extrapolation) compensée de mouvement.

Dans le premier cas, la précision de l'estimation par des techniques basées sur la correspondance de blocs et un post-traitement (filtre) sont raisonnables. Cependant pour l'interpolation des images « sautées », il est important d'utiliser des « vrais » vecteurs qu'on peut obtenir en utilisant une procédure de correspondance de blocs.

#### 2.2.2.6 - Filtre de la boucle

Afin de réduire l'erreur de prédiction, un filtre passe-bas est introduit dans la boucle de codage après la compensation de mouvement. Ceci pour réduire les effets de haute fréquence introduits par la compensation de mouvement, et diminuer le bruit de quantification dans la boucle de retour.

#### 2.2.2.7 - Codage à longueur variable (CLV)

Le CLV est un outil efficace qui utilise la redondance statistique dans le signal transmis. Il utilise l'algorithme de Huffman. La TCD, la compensation de mouvement, et le filtre de la boucle sont conçus de façon à générer un signal avec une redondance statistique suffisante pour que le CLV produise un débit binaire faible.

#### 2.2.3 - APERCU SUR LE STANDARD MPEG [25]

Les efforts des équipes du CCITT pour le H.261, sont la base du développement du standard de codage d'images animées par l'ISO: MPEG pour « Moving Picture Experts Group ». Contrairement au H.261, en l'ière phase, MPEG est destiné au codage d'images animées, en vue de leur stockage sur des supports numériques, d'où des contraintes plus souples.

La 1<sup>ière</sup> version MPEG-1 spécifie une compression vidéo à un débit de 1.5 Mbit/s. Deux autres versions visent à améliorer la qualité du codage vidéo avec une augmentation de débit : MPEG-2 est destiné à des débits de l'ordre de 10 Mbit/s, et MPEG-3 destiné à la TVHD à des débits de 30 à 40 Mbit/s. La dernière version MPEG-4 concerne le codage d'images animées à très bas débit, l'objectif étant d'obtenir un « standard » tenant compte de toutes les contraintes liées aux applications envisageables.

L'algorithme de compression vidéo MPEG se base sur deux techniques :

- La compensation de mouvement basée sur des blocs pour réduire la redondance temporelle;

- La compression basée sur la TCD pour la réduction de la redondance spatiale.

Les techniques de compensation de mouvement sont appliquées avec des prédicteurs causaux (codage prédictif pur) et des prédicteurs non-causaux (codage interpolatif). L'erreur de prédiction est comprimée avec la TCD; et l'information relative au mouvement est basée sur des blocs 16x16, comprimée avec des CLVs, et transmise avec l'information spatiale.

## 2.2.3.1 - Réduction de la redondance temporelle.

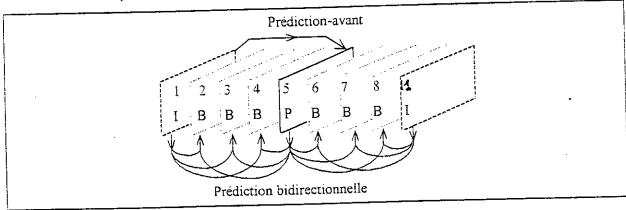

L'une des contraintes du MPEG, est l'accès aléatoire aux séquences d'images. Ceci a conduit à spécifier trois (03) types d'images (Figure I.7) :

- des images Intras (I) : qui fournissent des points d'accès aléatoires toutes les 10 à 15 images;

- des images Prédites (P) : codées avec référence à des images (I) ou (P) passées, et utilisées en général comme référence pour des images (P) futures.

- Des images bidirectionnelles (B): prédites bidirectionnellement avec à la fois deux références passée et future de type (I) ou (P), et ne servent jamais de référence.

La quantité d'informations contenues dans chacune de ces images décroît du type (I) à (P) à (B) à l'inverse de la compression subite.

Figure I.7 - Codage intertrame.

## 2.2.3.2 - Compensation de mouvement

- Compensation par prédiction : Cette technique assume que « localement » l'image courante peut être modélisée par la translation de l'image qui la précède. Localement signifie que l'amplitude et la direction du déplacement ne sont pas nécessairement les mêmes partout dans l'image. Vu son importance, l'information du mouvement doit être codée adéquatement.

- Compensation par interpolation : Cette technique améliore l'accès aléatoire aux séquences d'images, réduit l'effet des erreurs et contribue de façon significative à une bonne qualité de l'image. Elle est dite aussi prédiction bidirectionnelle et possède nombre d'avantages :

- Le taux de compression obtenu est élevé;

- Elle a de bonnes propriétés statistiques permettant en particulier de diminuer l'effet de bruit par un moyennage entre l'image précédente et l'image qui suit;

- Elle permet un découplage entre la prédiction et le codage ( pas d'erreur de propagation );

- Le protocole d'échange associé à la fréquence des images de type (B) est le suivant:

« En augmentant le nombre d'images (B) entre les images de références, on diminue la corrélation entre ces dernières et les images (B), ainsi que la corrélation entre les références elles-mêmes. Pour une large classe d'images, les combinaisons sont du type:

IBBPBBPBB...IBBPBB »

#### 2.2.3.3 - Estimation de mouvement

Le compromis entre le gain du codage de l'information du mouvement seul et le coût associé, a conduit au choix de macro-blocs (M-bloc) 16x16 comme unité de compensation de mouvement. Dans le cas général d'une image(B), la prédiction des M-blocs dépend des références passées ou futures et des vecteurs de mouvement.:

MPEG spécifie comment représenter l'information de mouvement : un (01) vecteur pour les M-blocs de prédiction avant ou arrière, et deux (02) vecteurs pour les M-blocs de prédiction bidirectionnelle. Les vecteurs de mouvement sont calculés en minimisant une fonction coût mesurant la différence entre un bloc et son prédicteur. L'information de mouvement associée à tout M-bloc 16x16 est codée differentièllement avec celle du bloc précédent pour subir ensuite un codage CLV pour plus d'efficacité.

#### 2.2.3.4 - Réduction de la redondance spatiale

On utilise la technique de compression intra-trame par TCD avec une combinaison d'une quantification visuelle adaptative à un codage RUN-LENGTH. L'opération consiste en 3 étapes:

- calcul des coefficients TCD;

- · quantification des ces coefficients;

- conversion des coefficients en paires {run amplitude} après leur réorganisation zigzag.

#### Quantification :

La quantification adaptative assure une bonne qualité visuelle. Elle peut être grossière aux hautes fréquences et presque uniforme aux faibles fréquences avec une différence de comportement du quantificateur autour de zéro (0) selon le type de blocs. Pour les blocs codés intras, le quantificateur ne présente pas de zône-limite (i.e. la région quantifiée au niveau zéro, est plus petite que le pas de quantification), par contre pour les blocs non-intras (différentiels), la zône-limite est large. Le pas de quantification pouvant être modifié aux limites des blocs.

#### Codage entropique :

Pour augmenter la compression par TCD et réduire l'impact de l'information de mouvement sur le taux de compression, un codage CLV est spécifié. Une table de Huffman pour les coefficients TCD, est utilisée pour coder les paires d'événements {run - amplitude}. Seuls les événements à grande probabilité d'apparition sont codés par le CLV.

Le schéma du codec MPEG est donné par la figure suivante;

Figure I.8 - CODEC MPEG

#### 3 - CONCLUSION

Dans ce chapitre, nous avons présenté l'essentiel des techniques de compression d'images illustrées par des figures explicatives pour mieux cerner leurs performances et leurs particularités. La technique de codage par transformée orthogonale TCD permet de grands et meilleurs taux de compression, et résiste mieux aux erreurs [5]. Les techniques prédictives quant à elles, sont efficaces pour des images à faibles évolutions temporelles et/ou spatiales.

Cependant, l'inconvénient majeur des systèmes de compression par transformée TCD réside dans leur complexité d'implémentation vu qu'ils nécessitent des opérations de transformation directe et inverse avant et après le codage selon les différents standards dans ce domaine.

La suite de notre travail sera orientée vers la dérivation d'un algorithme hybride TCD/TCDI et la conception d'une architecture unifiée pour l'implémentation de la transformée orthogonale cosinus discrète et son inverse.

## **CHAPITRE II**

LA TRANSFORMÉE

COSINUS DIRECTE

T.C.D

#### 1 - INTRODUCTION

Les applications modernes utilisant l'imagerie, adoptent un codage par la transformée orthogonale TCD opérant sur des blocs d'image, bidimensionnels dont la taille est appréciée à 8x8 pixels. L'importance et les performances élevées attendues de telles applications, qui sont des marchés en grande diffusion, exigent le développement d'algorithmes rapides de calcul de la TCD, tenant compte de toutes les spécifications des standards de normalisation, dans le sens que leur implémentation est devenue l'élément-clé de la VLSI de compression d'image.

Dans ce qui suit, nous présentons l'essentiel des algorithmes TCD proposés avec diverses techniques de dérivation réduisant la complexité des calculs et augmentant la vitesse d'exécution. Notre but est de dériver et/ou choisir un algorithme efficace de calcul hybride TCD/TCDI 2-D nous permettant la conception d'une architecture unifiée TCD/TCDI.

#### 2 - ALGORITHMIQUE RAPIDE DE LA TCD

Il convient de rappeler que la plupart des algorithmes rapides des transformées de signal telles que la TFR, la TCD, la WHT....etç, sont basées sur une technique dite de « Divide and Conquer » (soit diviser pour régner), qui consiste à transformer le problème initial en plusieurs problèmes du même type, plus petits. Des outils mathématiques jusqu'ici peu utilisés en traitement de signal : algèbre des corps finis, mathématiques discrètes dont le principal promoteur est Winograd, permettent de minimiser le nombre de multiplications à implanter et dont le coût est beaucoup plus important que celui des additions.

#### 2.1 - DÉFINITIONS [3] [11] [26] [27]

#### 2.1.1 - TCD unidimensionnelle

Pour une séquence de données entrées X(i), i= 0, ...N-1, la séquence de coefficients TCD est donnée par :

$$Y(m) = (2 / N) \cdot u(m) \cdot \sum_{i=0}^{N-1} X(i) \cdot Cos[(2i + 1)m\pi / 2N]; \quad m = 0, ... N-1.$$

(II.1)

$$o\dot{u}: \ u(m) = \begin{cases} 1/\sqrt{2} & \text{sim} = 0\\ 1 & \text{sinon} \end{cases}$$

Les coefficients de la transformée inverse TCDI sont donnés par :

$$X(i) = (2/N) \cdot \sum_{m=0}^{N-4} u(m) \cdot Y(m) \cdot Cos[(2i+1)m\pi/2N]; \quad i = 0, ...N-1. \quad (II.2)$$

#### 2.1.2 - TCD bidimensionnelle

Pour une séquence de données entrées X(i,j), i, j = 0,... N-1, la séquence de coefficients TCD 2-D Y(m,n), m,n=0,... N-1, est donnée par :

$$Y(m,n) = (2 / N)^{2} \cdot u(m) \cdot u(n) \cdot \sum_{i=0}^{N-1} \sum_{j=0}^{N-1} X(i,j) \cdot \cos[(2i+1)m\pi / 2N] \cdot \cos[(2j+1)n\pi / 2N]$$

(II.3)

avec:

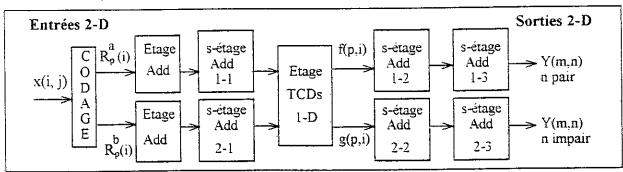

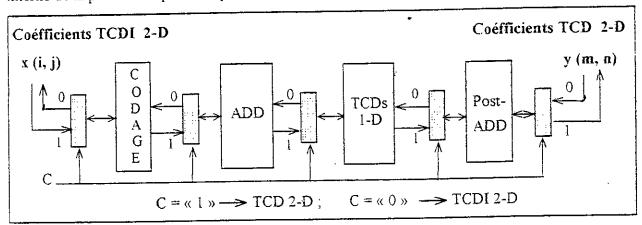

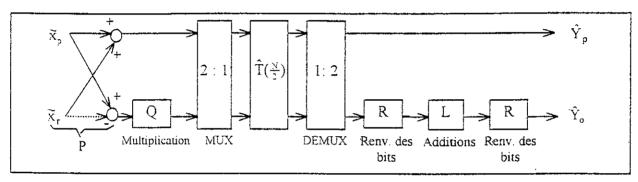

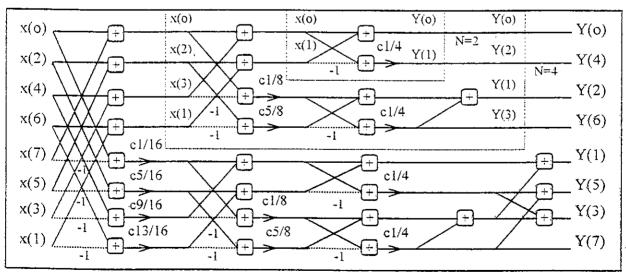

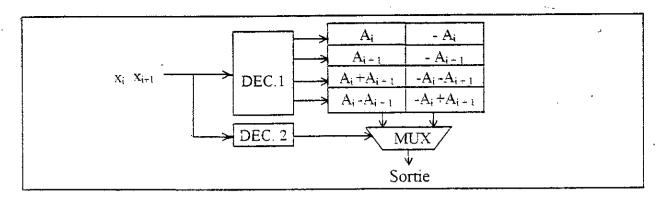

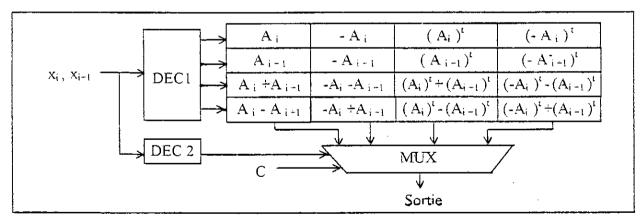

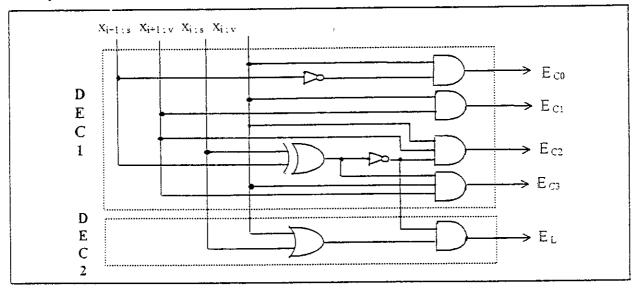

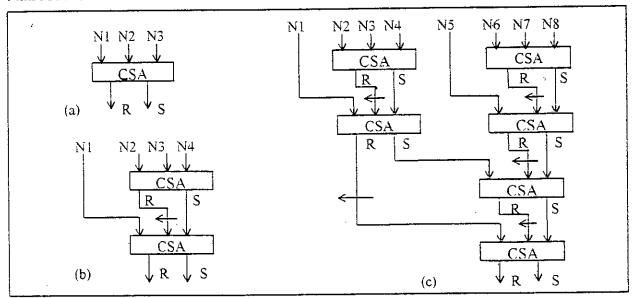

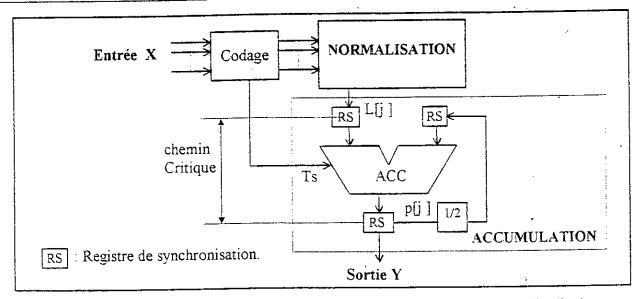

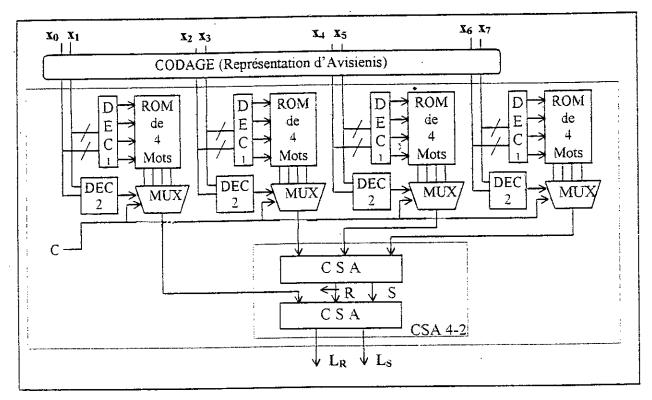

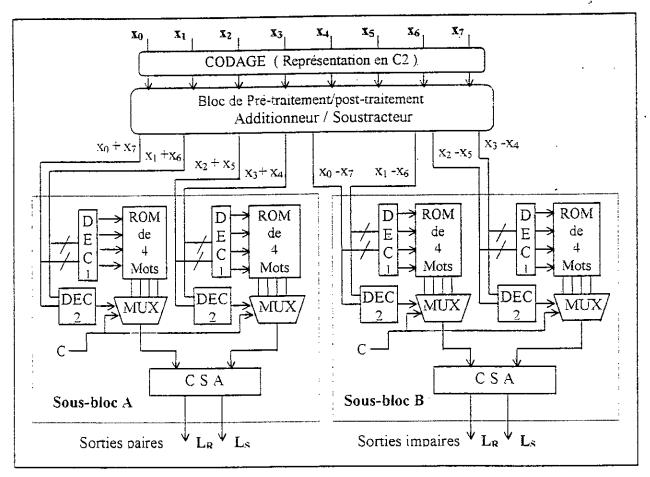

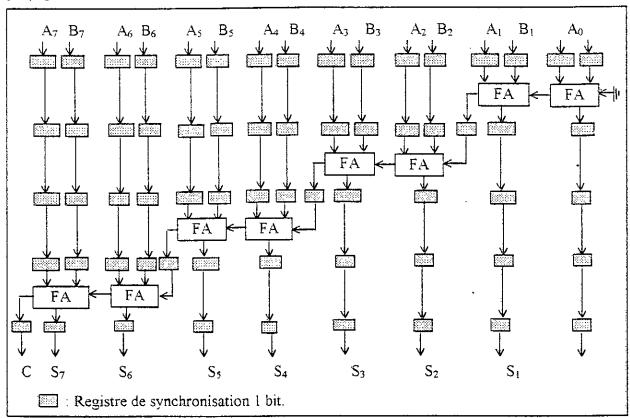

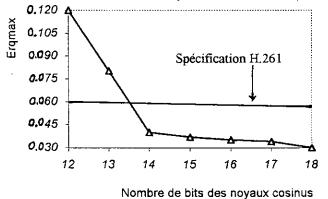

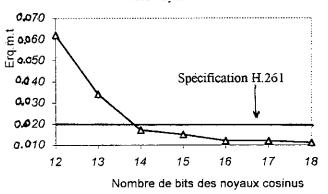

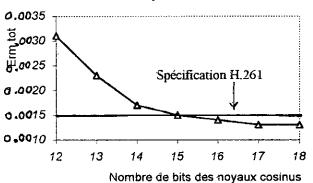

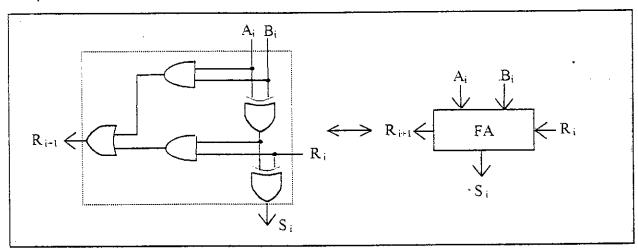

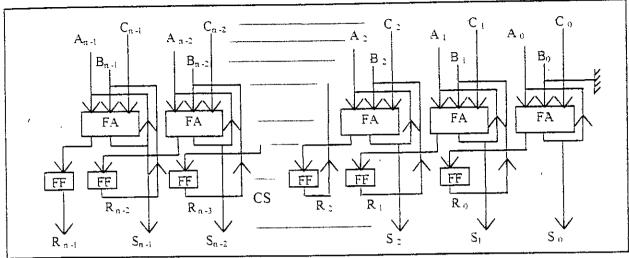

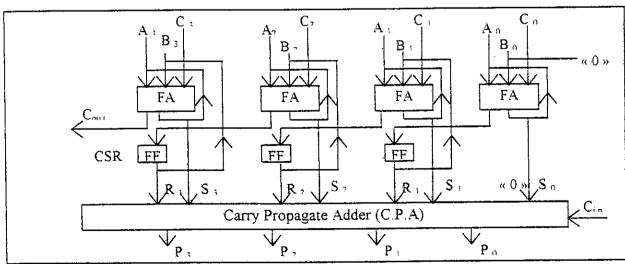

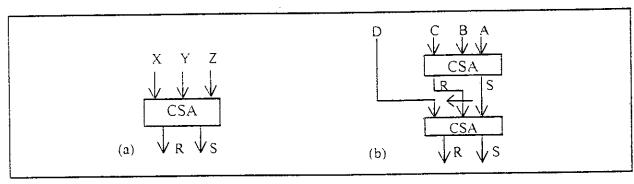

$$u(m)$$