#### REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

#### MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

#### ECOLE NATIONALE POLYTECHNIQUE

#### Département d'Automatique

#### Projet de fin d'études

Pour l'obtention du diplôme

D'Ingénieur d'Etat et du diplôme de Master en Automatique

THÈME

## Implémentation des techniques MLI sur un circuit FPGA

Etudié par :

Proposé et dirigé par :

DJAAFRI Noureddine REBAI Aissa Pr. E.M. BERKOUK Pr. C. LARBES

#### Juin 2012

Laboratoire de Commande des Processus Ecole Nationale Polytechnique, 10, AV. Hassen Badi, El-Harrach, Algérie

# Remerciements

Nous remercions le bon Dieu de nous avoir accordé toute la patience, le courage, la volonté et la motivation qui nous ont permis d'achever ce travail.

Nous exprimons notre profonde gratitude, notre grand respect et notre sincère reconnaissance à notre promoteur le Pr. BERKOUK de l'Ecole Nationale Polytechnique pour avoir assumé la lourde responsabilité de nous encadrer, de nous avoir orienté et conseiller tout au long de ce travail ainsi pour la confiance qu'il nous a accordée.

Nous remercions également notre co-promoteur le Pr. LARBES de l'Ecole Nationale Polytechnique pour ses précieux conseils, son suivi, sa disponibilité et son aide.

Nous remercions chaleureusement les membres du jury pour l'honneur qu'ils nous ont fait en acceptent d'évaluer notre projet.

Nous souhaitons aussi remercier tous les enseignants de l'Ecole Nationale Polytechnique d'Alger, et en particulier, Nos professeurs d'Automatique qui nous ont encadrés auparavant et tous nos enseignants pour les connaissances qu'ils nous ont transmis, leur disponibilité et leurs efforts.

Que tous ceux qui ont contribué de près ou de loin à la réalisation de ce modeste travail trouvent ici l'expression de notre sincère gratitude.

#### Dédicaces

Je dédie ce modeste travail à ma chère mère qui a été de tout temps, la plus proche, qui n'a jamais ménagé leur effort, leur encouragement et leur soutien avec abnégation et patience

Sans oublier mes Grandes mères.

A la mémoire de mon père.

A mes frères et ma sœur.

A l'ensemble des amis que j'ai connu pendant mes études et à ceux qui ont prodigué leurs vifs conseils, encouragements et témoigné de leur amitié.

Aissa

A ma très chère mère,

A mes frères mes sœurs que j'adore,

A toute ma famille,

A mon ami Sofiane, ainsi qu'à tous mes amis,

A vous tous,

A la mémoire de mon très cher père.

Noureddine

#### ملخص:

الهدف من هذا العمل هو دراسة و إنجاز ذراع محول مستمر - متناوب. طرق التحكم المستعملة هي تقنية تعديل عرض النبضة (MLI)، وتقنية عرض النبضة مع حذف توافقيات الإشارة والتحكم في المركبة الأساسية التي وضعها كل من باتل و هوفت.

لذلك قمنا بمحاكاة التقنيات المستعملة باستعمال البرنامج PSIM بعد ذلك قمنا ببرمجة هذه التقنيات على دارة مبرمجة من نوع FPGA Xilinx باستعمال لغة VHDL وبطاقة التطوير Memec Design. في الأخير تم إنجاز الدارة الكاملة للذراع، ثم تجريبها والتعليق على النتائج المحصل عليها.

كلمات مفتاحية: تعديل عرض النبضة المبرمجة، تعديل عرض النبضة، محول مستمر ـ متناوب، دارة FPGA، لغة LYHOL، باتل، هو فت.

#### Résumé:

L'objectif de ce travail est l'étude et la réalisation d'un bras d'onduleur. Les commandes utilisées sont : une MLI calculée On-Line (en temps réel) à élimination d'harmoniques et asservissement du fondamental, et une commande MLI engendrée triangulo-sinusoïdale. Dans ce mémoire nous avons commencé par simuler le système à réaliser dans l'environnement PSIM, puis nous avons implémenté l'algorithme MLI on-line et la commande engendrée sur un circuit FPGA XC2V1000 de XILINX, en utilisant le langage VHDL et la carte de développement Memec Design V2MB1000. Ensuite nous avons réalisé le bras de l'onduleur, Enfin nous avons présenté des tests sur ce bras et des discussions des résultats obtenus.

**Mots clés :** MLI engendrée, MLI calculée, onduleur, circuits FPGA, langage VHDL, Xilinx, Patel et Hoft.

#### **Abstract:**

The aim of this work to design and implement an arm of inverter. The technique used is an On-Line harmonic elimination PWM (HEPWM), with fundamental control and a generated technique PWM. They are a scalar techniques which allows generating high-quality output spectra.

We have used a co-simulation based on PSIM to improve the performances of the techniques used. Then the V2MB1000 Memec Design development card was used to implement the On-Line algorithm in a XILINX FPGA (XC2V1000), using the VHDL language.

Finally, we have built the arm of the inverter. The test of global system and the discussion of the results obtained are given.

**Keywords:** PWM, HEPWM, harmonics, FPGA, VHDL, Voltage source inverter.

## Table des matières

| In | ntroduction Générale |          | 1                                                |    |

|----|----------------------|----------|--------------------------------------------------|----|

| 1  | Gén                  | éralités | sur les onduleurs                                | 3  |

|    | 1.1                  | Introd   | uction                                           | 3  |

|    | 1.2                  | Défini   | tion des onduleurs                               | 3  |

|    | 1.3                  | Divers   | types d'onduleurs                                | 4  |

|    |                      | 1.3.1    | Les onduleurs de tension                         | 4  |

|    |                      | 1.3.2    | Les onduleurs de courant                         | 4  |

|    | 1.4                  | Les Di   | fférents schémas des onduleurs de tension        | 5  |

|    |                      | 1.4.1    | Les onduleurs de tension monophasés en demi-pont | 5  |

|    |                      | 1.4.2    | Les onduleurs de tension monophasés en pont      | 7  |

|    |                      | 1.4.3    | Les onduleurs triphasés                          | 8  |

|    |                      | 1.4.4    | Les onduleurs multi-niveaux                      | 9  |

|    | 1.5                  | Caract   | érisation de la tension fournie par l'onduleur   | 10 |

|    |                      | 1.5.1    | Le facteur d'harmonique (HF)                     | 10 |

|    |                      | 1.5.2    | La distorsion totale d'harmonique (THD)          | 11 |

|    |                      | 1.5.3    | L'harmonique le plus bas ordre (LOH)             | 11 |

|    | 1.6                  | Le pro   | blème de filtrage                                | 11 |

|    | 1.7                  | Domai    | ines d'application                               | 12 |

|    |                      | 1.7.1    | Domaine des fréquences fixes                     | 12 |

|    |                      | 1.7.2    | Domaine des fréquences variables                 | 13 |

|    | 1.8                  | Comm     | ande des onduleurs par techniques M.L.I          | 13 |

|    |                      | 181      | Introduction                                     | 13 |

|   |      | 1.8.2    | Technique MLI multiple                                                  | 14 |

|---|------|----------|-------------------------------------------------------------------------|----|

|   |      | 1.8.3    | Technique MLI engendrée                                                 | 15 |

|   |      | 1.8.4    | Technique MLI vectorielle                                               | 15 |

|   |      | 1.8.5    | Technique MLI à élimination des harmoniques (calculée)                  | 16 |

|   |      | 1.8.6    | Technique MLI delta                                                     | 17 |

|   | 1.9  | Conclu   | usion                                                                   | 18 |

| 2 | Desc | cription | des techniques MLI engendrée et à élimination des harmoniques           | 19 |

|   | 2.1  | Techni   | ique de la MLI engendrée                                                | 19 |

|   |      | 2.1.1    | Principe                                                                | 19 |

|   |      | 2.1.2    | Caractérisation de la modulation                                        | 20 |

|   |      | 2.1.3    | Étude de la tension de sortie                                           | 20 |

|   |      | 2.1.4    | Contrôle de tension d'un onduleur triphasé                              | 21 |

|   |      | 2.1.5    | MLI sinusoïdale modifiée                                                | 22 |

|   | 2.2  | Descri   | ption de la technique de PATEL et HOFT[13]                              | 23 |

|   | 2.3  | calcul   | des valeurs exactes des angles de commutation par la méthode de Newton- |    |

|   |      | Raphs    | on                                                                      | 28 |

|   |      | 2.3.1    | Description                                                             | 28 |

|   |      | 2.3.2    | Résolution du système non linéaire par la méthode de Newton-Raphson     | 29 |

|   | 2.4  | Descri   | ption de l'algorithme 'on-line'                                         | 32 |

|   |      | 2.4.1    | Approximation des angles exacts                                         | 32 |

|   |      | 2.4.2    | Cas k impair                                                            | 34 |

|   |      | 2.4.3    | Cas k pair                                                              | 36 |

|   | 2.5  | Précisi  | ion de l'algorithme                                                     | 37 |

|   | 2.6  | Conclu   | usion                                                                   | 38 |

| 3 | Les  | circuits | FPGA                                                                    | 40 |

|   | 3.1  | Introdu  | uction                                                                  | 40 |

|   | 3.2  | Critère  | es de performances                                                      | 41 |

|   |      | 3.2.1    | Puissance de calcul                                                     | 41 |

|   |      | 3.2.2    | Vitesse de fonctionnement                                               | 41 |

|   |      | 3 2 3    | Canacité de mémoire                                                     | 41 |

|   |       | 3.2.4   | Routabilité                                           | 41 |

|---|-------|---------|-------------------------------------------------------|----|

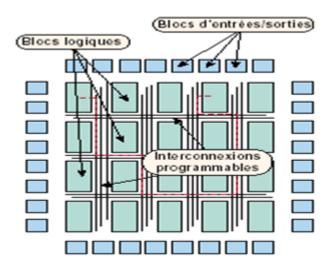

|   | 3.3   | Les cir | reuits FPGA                                           | 42 |

|   |       | 3.3.1   | Définition                                            | 42 |

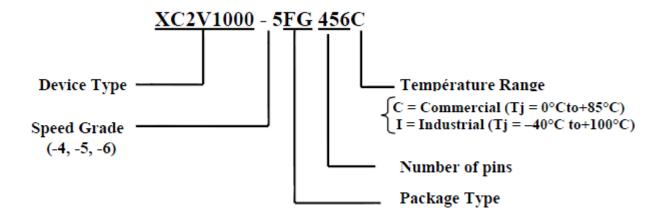

|   |       | 3.3.2   | Nomenclature des circuits FPGA                        | 42 |

|   |       | 3.3.3   | Domaines d'application des circuits FPGA              | 42 |

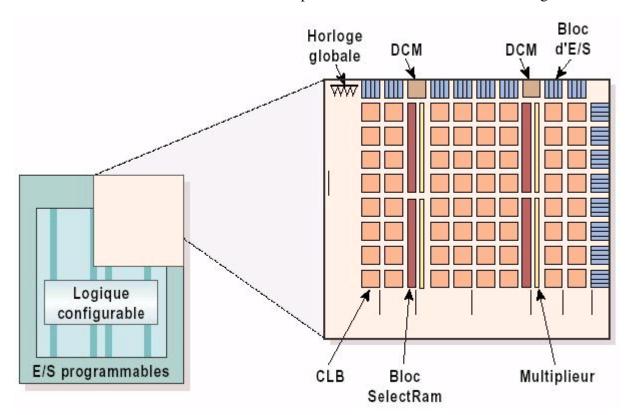

|   | 3.4   | Archite | ecture des FPGA                                       | 43 |

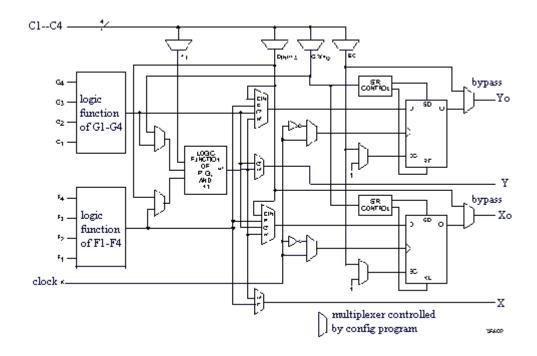

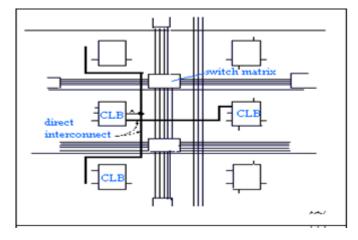

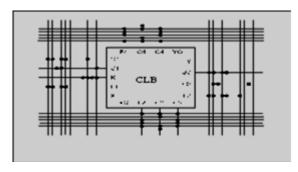

|   |       | 3.4.1   | Les CLB (configurable logic bloc)                     | 44 |

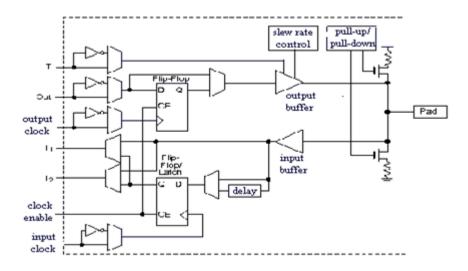

|   |       | 3.4.2   | Les IOB (input output bloc)                           | 46 |

|   |       | 3.4.3   | La configuration en entrée                            | 47 |

|   |       | 3.4.4   | La configuration en sortie                            | 47 |

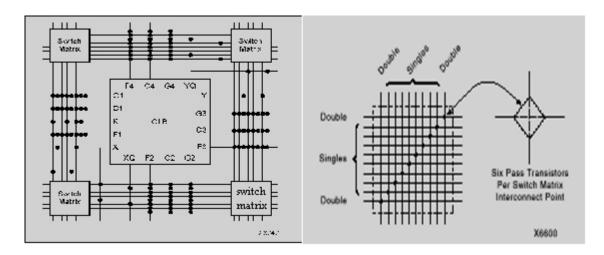

|   |       | 3.4.5   | Les interconnexions[25]                               | 48 |

|   | 3.5   | Config  | guration des FPGA                                     | 50 |

|   | 3.6   | Types   | des FPGA                                              | 50 |

|   | 3.7   | Outils  | de développement des FPGA                             | 51 |

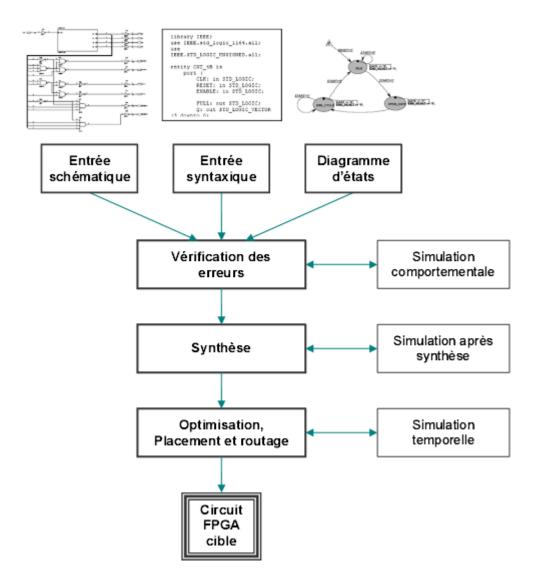

|   | 3.8   | Métho   | dologie de développement d'un projet sur FPGA[28][25] | 51 |

|   |       | 3.8.1   | Logiciel et outil utilisé                             | 52 |

|   |       | 3.8.2   | Implémentation d'un projet sur circuit FPGA           | 53 |

|   | 3.9   | Conclu  | asion                                                 | 54 |

| 4 | Le la | angage  | de description VHDL                                   | 56 |

|   | 4.1   | Introdu | uction                                                | 56 |

|   | 4.2   | Caract  | éristiques de VHDL                                    | 57 |

|   | 4.3   | Structu | are d'un code source VHDL                             | 57 |

|   |       | 4.3.1   | Bibliothèques                                         | 57 |

|   |       | 4.3.2   | Généralités sur la syntaxe                            | 58 |

|   |       | 4.3.3   | Description d'entité                                  | 58 |

|   |       | 4.3.4   | Généralités sur l'architecture                        | 59 |

|   |       | 4.3.5   | Signaux et opérateurs                                 | 59 |

|   | 4.4   | Type d  | le données                                            | 61 |

|   |       | 4.4.1   | Types communs                                         | 61 |

|   |       | 4.4.2   | Types std_logic et std_logic_vector                   | 62 |

5

|     | 4.4.3   | Types signed et unsigned                       | 62 |

|-----|---------|------------------------------------------------|----|

|     | 4.4.4   | Conversion de types                            | 62 |

|     | 4.4.5   | Type time                                      | 63 |

|     | 4.4.6   | Type énuméré                                   | 63 |

|     | 4.4.7   | Tableaux                                       | 63 |

|     | 4.4.8   | Enregistrement                                 | 64 |

|     | 4.4.9   | Attributs                                      | 64 |

| 4.5 | Foncti  | ons rising_edge et falling_edge                | 64 |

| 4.6 | Instruc | ctions concurrentes                            | 65 |

|     | 4.6.1   | Instruction d'affectation                      | 65 |

|     | 4.6.2   | Affectation conditionnelle                     | 65 |

|     | 4.6.3   | Affectation sélective                          | 65 |

|     | 4.6.4   | Affectation implicite                          | 65 |

| 4.7 | Instruc | ctions séquentielles                           | 66 |

|     | 4.7.1   | Process                                        | 66 |

|     | 4.7.2   | Liste de sensibilité                           | 66 |

|     | 4.7.3   | Process et signaux                             | 66 |

|     | 4.7.4   | Variables                                      | 67 |

|     | 4.7.5   | Instructions séquentielles                     | 67 |

| 4.8 | Progra  | mmation modulaire                              | 69 |

|     | 4.8.1   | Les modules                                    | 69 |

|     | 4.8.2   | Les sous-programmes                            | 70 |

| 4.9 | Conclu  | usion                                          | 72 |

| T   | 16 o4-  | otion dos tochniques MI I sun un cinovit EDC A | 73 |

| _   |         | ation des techniques MLI sur un circuit FPGA   |    |

| 5.1 |         | uction                                         | 73 |

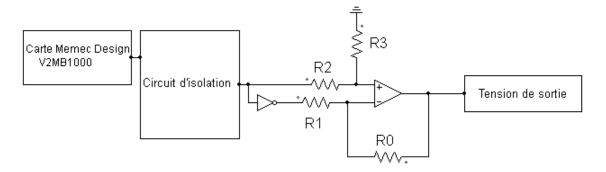

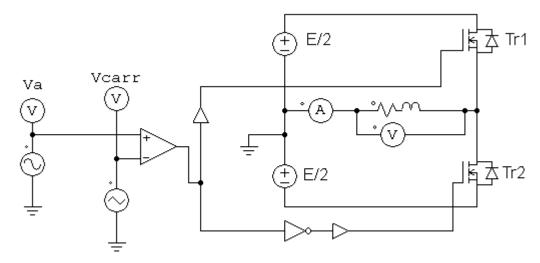

| 5.2 | Descri  | ption du circuit de puissance                  | 73 |

| 5.3 | Implér  | mentation d'une commande MLI engendrée         | 74 |

|     | 5.3.1   | Introduction                                   | 74 |

|     | 5.3.2   | Programme de la commande                       | 75 |

|     | 5.3.3   | Résultats de simulation                        | 79 |

|          | 5.3.4                                             | Implementation de la commande                              | . 81  |  |

|----------|---------------------------------------------------|------------------------------------------------------------|-------|--|

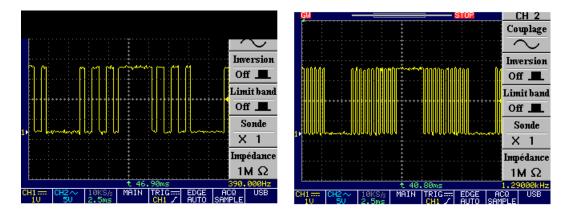

|          | 5.3.5                                             | Visualisation des résultats sur l'osciloscope              | . 82  |  |

|          | 5.3.6                                             | Étude du spectre                                           | . 82  |  |

|          | 5.3.7                                             | Conclusion                                                 | . 86  |  |

| 5.4      | Implén                                            | mentation d'une commande MLI calculée off-line             | . 86  |  |

|          | 5.4.1                                             | Introduction                                               | . 86  |  |

|          | 5.4.2                                             | Programme d'une commande MLI off-line                      | . 86  |  |

|          | 5.4.3                                             | Résultats de simulation                                    | . 88  |  |

|          | 5.4.4                                             | Implémentation de la commande                              | . 89  |  |

|          | 5.4.5                                             | Visualisation des résultats sur l'osciloscope              | . 90  |  |

| 5.5      | Implén                                            | mentation d'une commande MLI calculée 'on-line'            | . 92  |  |

|          | 5.5.1                                             | Introduction                                               | . 92  |  |

|          | 5.5.2                                             | Programme de calcul des angles de commutation              | . 92  |  |

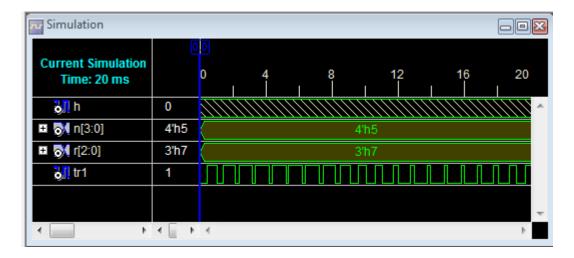

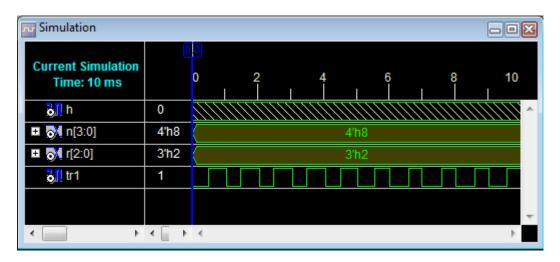

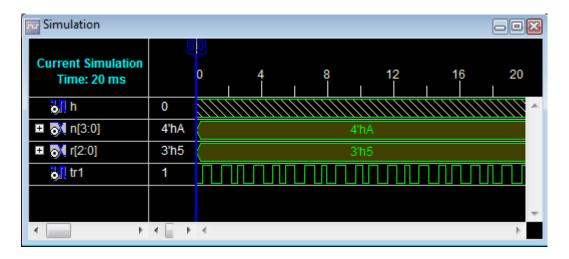

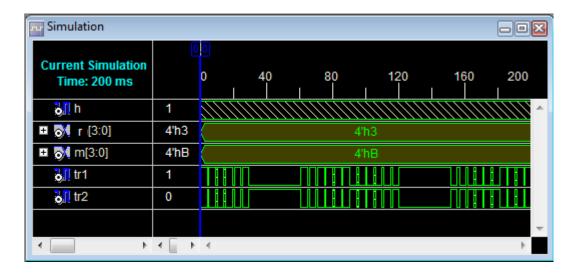

|          | 5.5.3                                             | Résultats de simulation                                    | . 94  |  |

|          | 5.5.4                                             | Programme de génération des signaux de commande            | . 96  |  |

|          | 5.5.5                                             | Résultats de simulation                                    | . 97  |  |

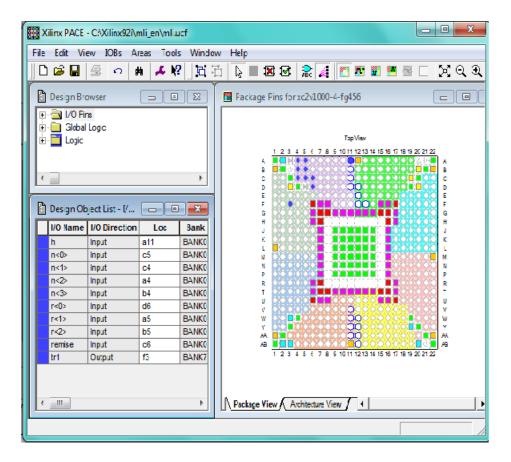

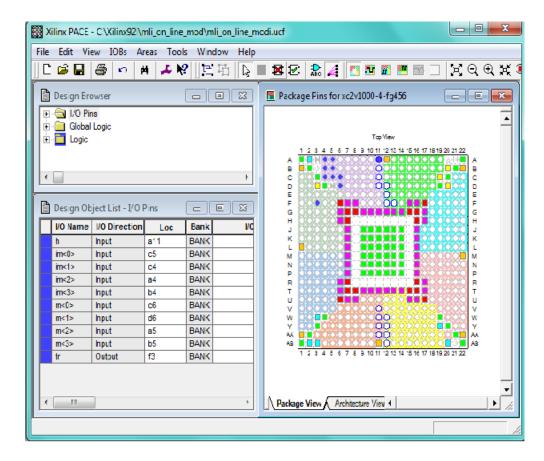

|          | 5.5.6                                             | Implémentation de la commande                              | . 98  |  |

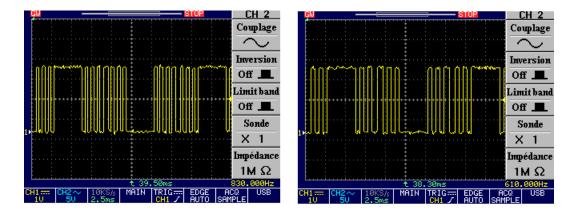

|          | 5.5.7                                             | Visualisation des résultats sur l'osciloscope              | . 99  |  |

|          | 5.5.8                                             | Étude du spectre                                           | . 100 |  |

|          | 5.5.9                                             | Conclusion                                                 | . 104 |  |

| 5.6      | Conclu                                            | asion                                                      | . 104 |  |

| Conclus  | sion Géi                                          | nérale                                                     | 105   |  |

| Bibliogr | aphie                                             |                                                            | 107   |  |

| Annexe   | A : Pro                                           | ogrammation des systèmes automatisés par les circuits FPGA | 110   |  |

| Annexe   | B : Util                                          | lisation du logiciel Xilinx ISE                            | 113   |  |

| Annexe   | C : Des                                           | scription de la carte Memec Design V2MB1000                | 128   |  |

| Annexe   | Annexe D : Description de l'optocoupleur HCPL2200 |                                                            |       |  |

## Table des figures

| 1.1  | Onduleur de tension monophasé en demi-pont                                | 6  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | courant pour une charge RL et pour une charge purement inductive          | 7  |

| 1.3  | Onduleur de tension monophasé en pont                                     | 8  |

| 1.4  | Les onduleurs de tension triphasés                                        | 9  |

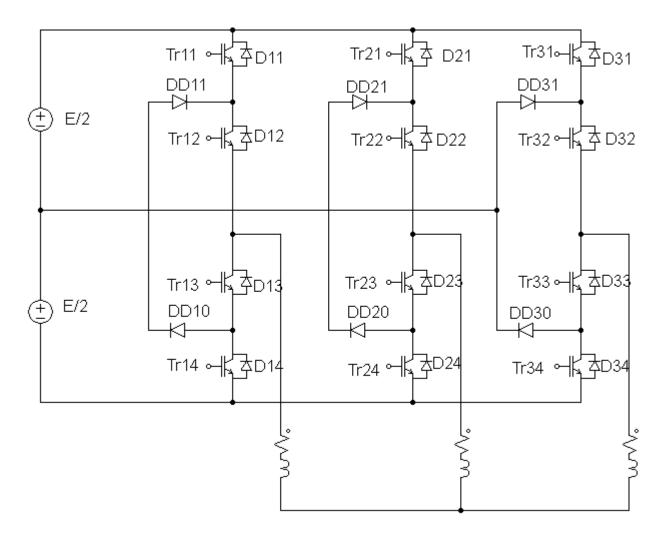

| 1.5  | Onduleur à 3 niveaux à structure NPC [22]                                 | 10 |

| 1.6  | Schéma de principe d'un onduleur pour alimentation de secours             | 12 |

| 1.7  | Schéma de principe d'un onduleur pour la conduite d'un moteur asynchrone  | 13 |

| 1.8  | MLI multiple                                                              | 15 |

| 1.9  | Les états d'un onduleur deux niveaux dans le repère $(\alpha,\beta)$ [18] | 16 |

| 1.10 | MLI calculée                                                              | 17 |

| 1.11 | MLI delta                                                                 | 18 |

| 2.1  | MLI engendrée pour un onduleur monophasé                                  | 21 |

| 2.2  | Onduleur MLI engendrée triphasée                                          | 22 |

| 2.3  | MLI modifiée                                                              | 23 |

| 2.4  | graphe d'une tension MLI calculée                                         | 24 |

| 2.5  | Courbes des angles de commutation exacts pour m égal à 3                  | 31 |

| 2.6  | Courbes des angles de commutation exacts pour m égal à 5                  | 31 |

| 2.7  | Courbes des angles de commutation exacts pour m égal à 7                  | 32 |

| 2.8  | variation de $\Delta_k$ pour $k$ impair[14]                               | 35 |

| 2.9  | variation de $\Delta_k$ pour $k$ pair[14]                                 | 36 |

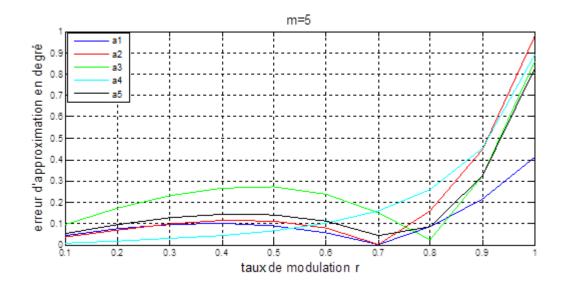

| 2.10 | erreur d'approximation pour $m=5$                                         | 38 |

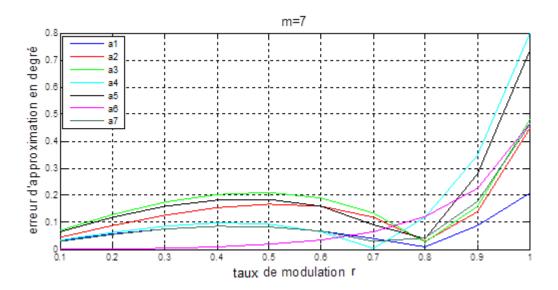

| 2 11 | erreur d'approximation pour $m=7$                                         | 38 |

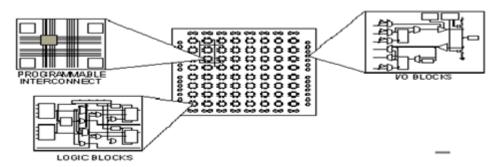

| 3.1  | Architecture interne d'un FPGA[23]                                               | 44 |

|------|----------------------------------------------------------------------------------|----|

| 3.2  | réseaux d'interconnexions configurable[27]                                       | 44 |

| 3.3  | Cellules logiques(CLB)[27]                                                       | 45 |

| 3.4  | Input Output Block (IOB)[10]                                                     | 47 |

| 3.5  | Connexions à usage général et matrice de commutation[25]                         | 49 |

| 3.6  | Les interconnexions directes[25]                                                 | 49 |

| 3.7  | Les longues lignes[25]                                                           | 50 |

| 3.8  | Organisation fonctionnelle de développement d'un projet sur circuit FPGA[25]     | 54 |

| 4.1  | simulation d'une somme logique                                                   | 72 |

| 5.1  | Circuit de commande d'un bras d'onduleur                                         | 74 |

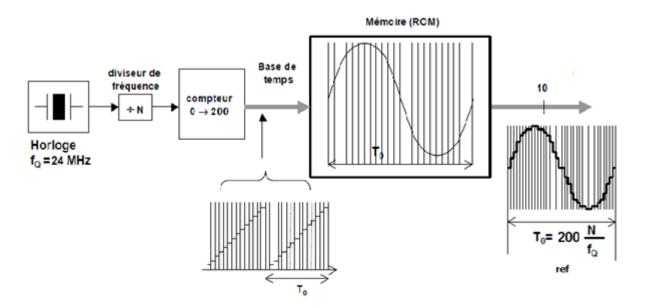

| 5.2  | principe de génération d'un signal sinusoïdal                                    | 75 |

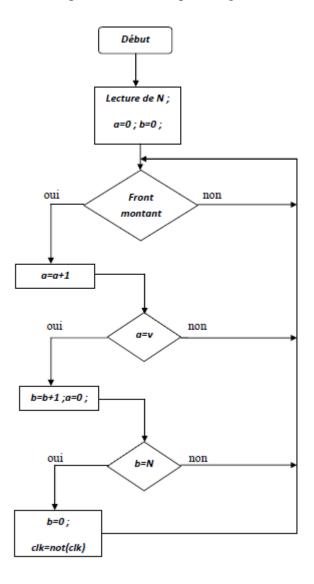

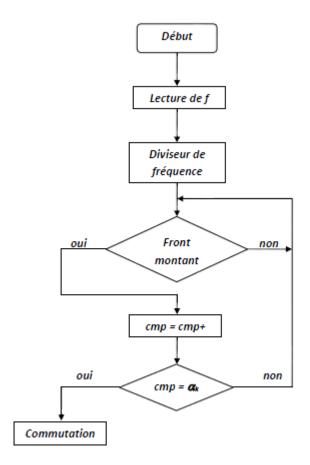

| 5.3  | Organigramme d'un diviseur de fréquence                                          | 76 |

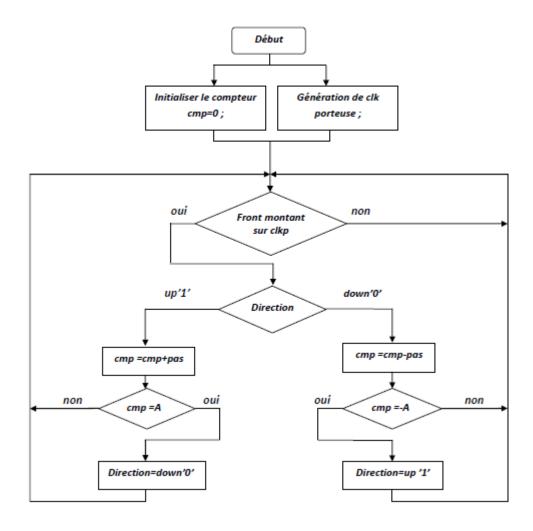

| 5.4  | Organigramme de génération d'un signal triangulaire                              | 77 |

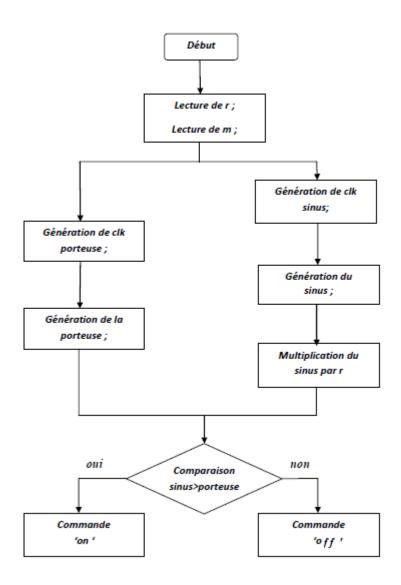

| 5.5  | Organigramme d'une commande MLI engendrée                                        | 79 |

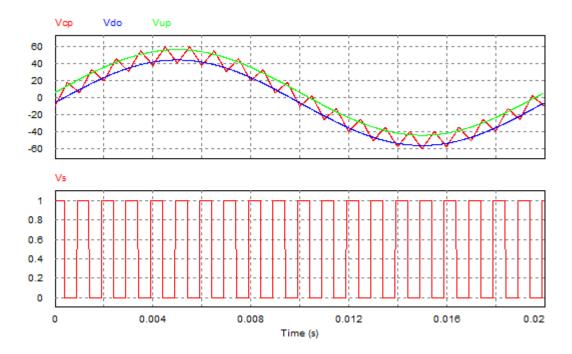

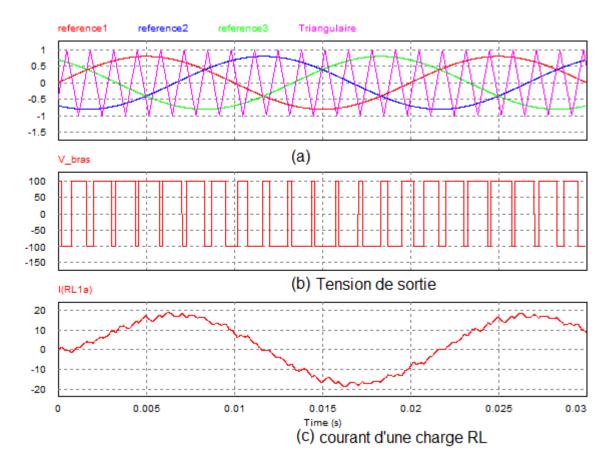

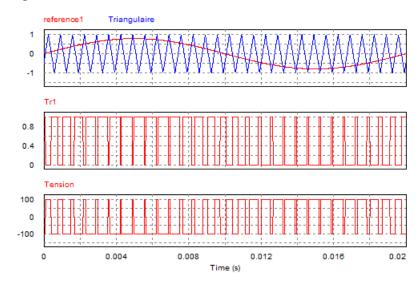

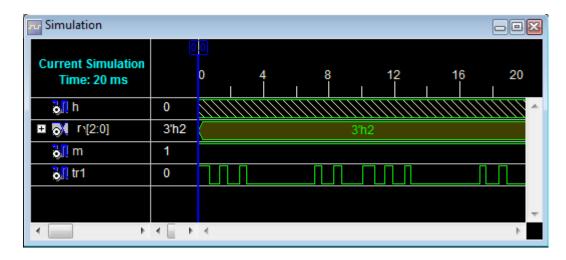

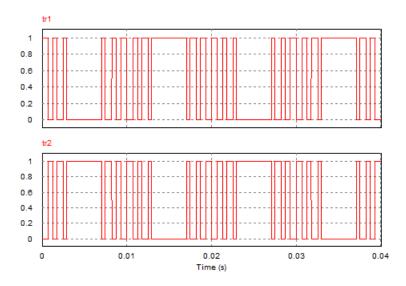

| 5.6  | Résultat de simulation pour $f_r=50Hz,m=20$ et $r=0.7$                           | 80 |

| 5.7  | Résultat de simulation pour $f_r=100Hz, m=10$ et $r=0.2$                         | 80 |

| 5.8  | Résultat de simulation pour $f_r=60Hz, f_p=1kHz$ et $r=0.5$                      | 80 |

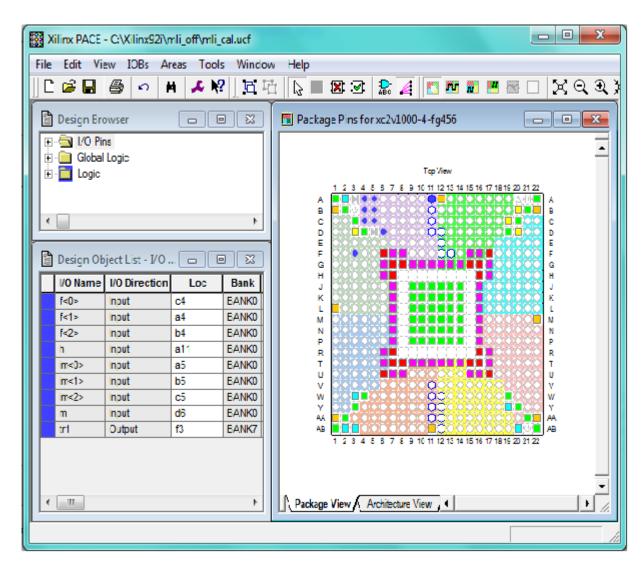

| 5.9  | Aperçu de l'outil d'affectation des broches d'entrées-sorties                    | 81 |

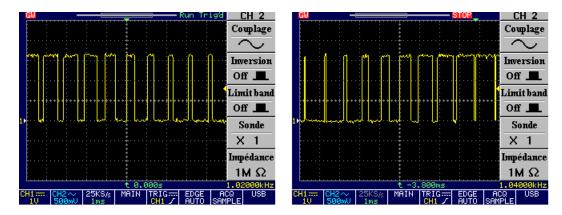

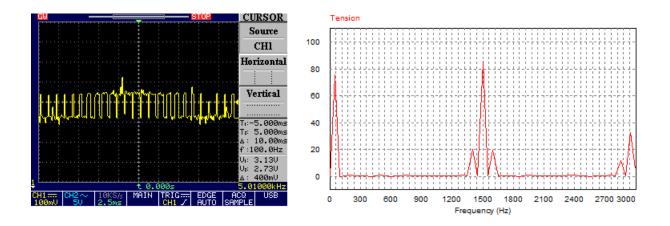

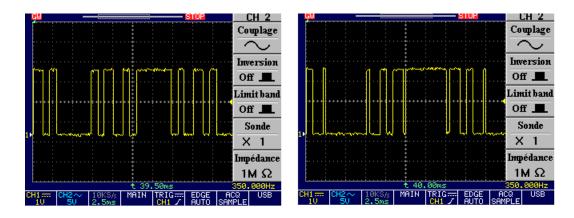

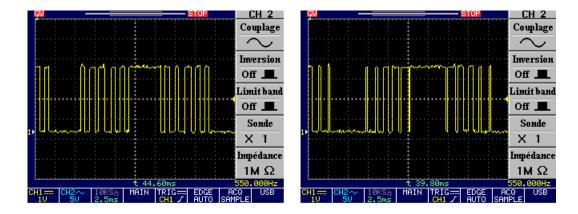

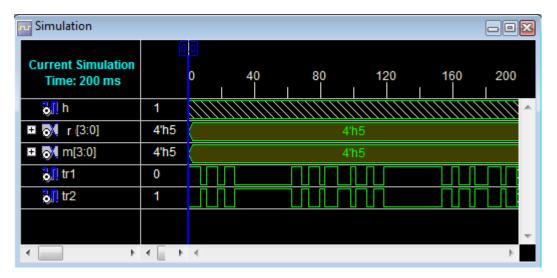

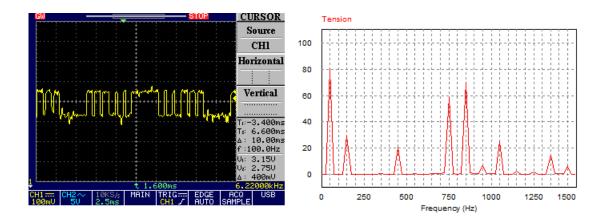

| 5.10 | Commande MLI engendrée pour $m=20,  f_r=50 Hz$ et $r_1=0.6;  r_2=0.9 \; . \; .$  | 82 |

| 5.11 | Commande MLI engendrée pour $m=20,  f_r=50 Hz$ et $r_1=0.2;  r_2=1.2 \; . \; .$  | 82 |

| 5.12 | Onduleur en demi-pont sous PSIM                                                  | 83 |

| 5.13 | Commande MLI engendrée de l'onduleur en demi-pont $m=30$ et $r=0.8$              | 83 |

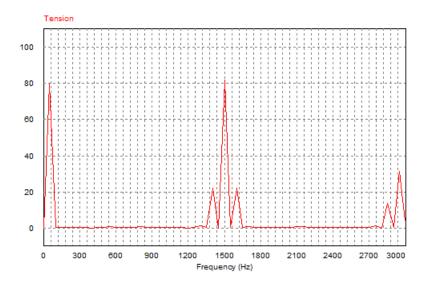

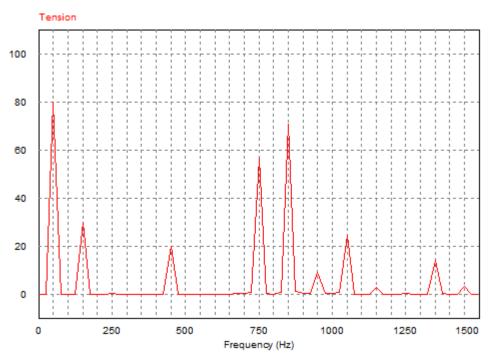

| 5.14 | Spectre de la tension de sortie $m=30$ et $r=0.8$                                | 84 |

| 5.15 | Tension et spectre de sortie d'un onduleur en demi-pont pour $m=30$ et $r=0.8$ . | 85 |

| 5.16 | Organigramme d'une MLI off-line                                                  | 87 |

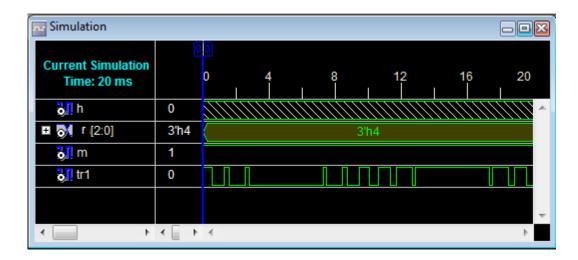

| 5.17 | MLI calculée pour $m=3$ et $r=0.6$                                               | 88 |

| 5.18 | MLI calculée pour $m=5$ et $r=0.8$                                               | 88 |

| 5.19 | MLI calculée pour $m=5$ et $r=1$                                                 | 89 |

| 5.20 | Aperçu de l'outil d'affectation des broches d'entrées sorties                    | 90 |

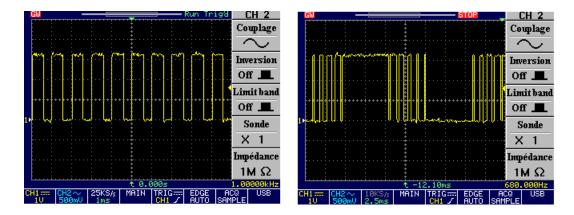

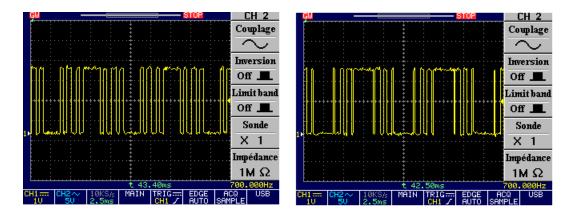

| 5 21 | Commande MI I calculée pour $m=3$ $f=50Hz$ et $r_1=0.6$ : $r_2=1$                | 91 |

| 5.22 | Commande MLI calculée pour $m = 5$ , $f_r = 50Hz$ et $r_1 = 0.6$ ; $r_2 = 1 \dots$    | 91  |

|------|---------------------------------------------------------------------------------------|-----|

| 5.23 | Commande MLI calculée pour $m=3,  f_r=100Hz$ et $r_1=0.6;  r_2=1 \; \ldots \; \ldots$ | 91  |

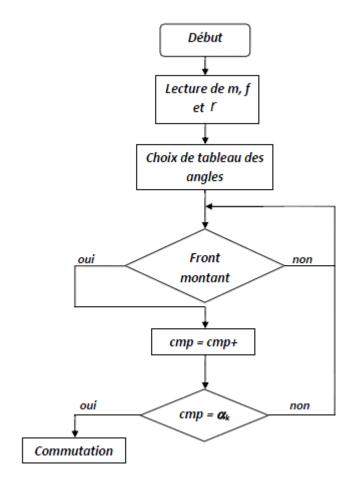

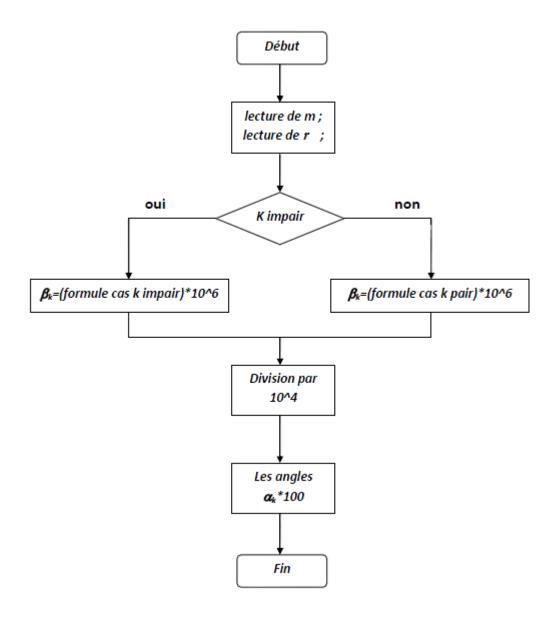

| 5.24 | Organigramme de calcul des angles de commutations                                     | 93  |

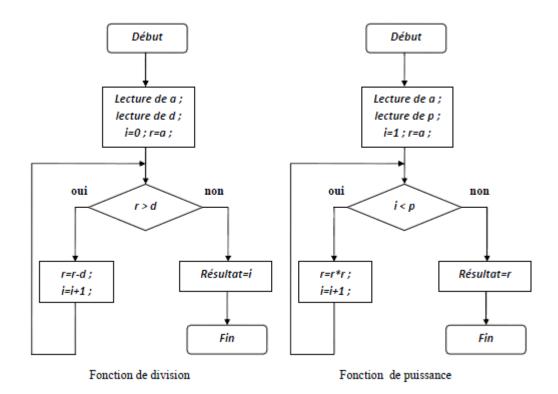

| 5.25 | Organigrammes des fonctions de division et de puissance                               | 94  |

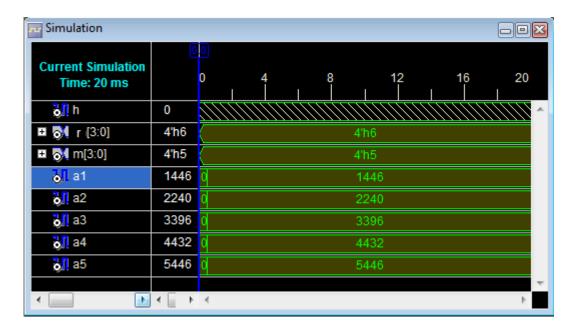

| 5.26 | Les angles de commutation pour $m=5$ et $r=0.2$                                       | 95  |

| 5.27 | Les angles de commutation pour $m=5$ et $r=0.6$                                       | 95  |

| 5.28 | Organigramme de génération des signaux de commande                                    | 96  |

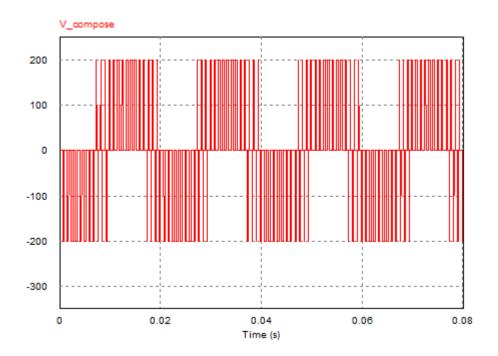

| 5.29 | Résultat de simulation pour $m=5$ et $r=0.5$                                          | 97  |

| 5.30 | Résultat de simulation pour $m=7$ et $r=0.6$                                          | 97  |

| 5.31 | Résultat de simulation pour $m=11$ et $r=0.3$                                         | 98  |

| 5.32 | Aperçu de l'outil d'affectation des broches d'entrées sorties                         | 99  |

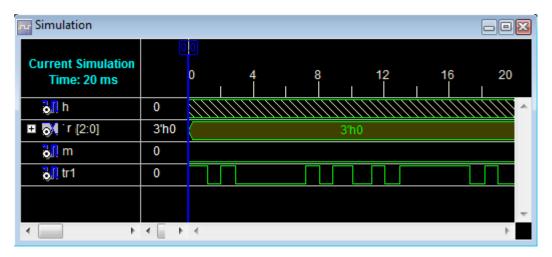

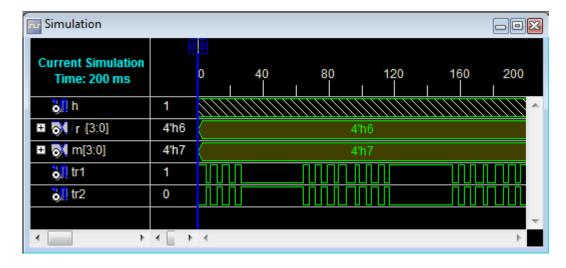

| 5.33 | Résultat d'implémentation pour $m=3,  11$ et $r=0.8 \dots \dots \dots \dots$          | 99  |

| 5.34 | Résultat d'implémentation pour $m=5,  7$ et $r=0.6  \dots  \dots  \dots$              | 100 |

| 5.35 | Commandes des transistors                                                             | 100 |

| 5.36 | Spectre de la tension de sortie                                                       | 101 |

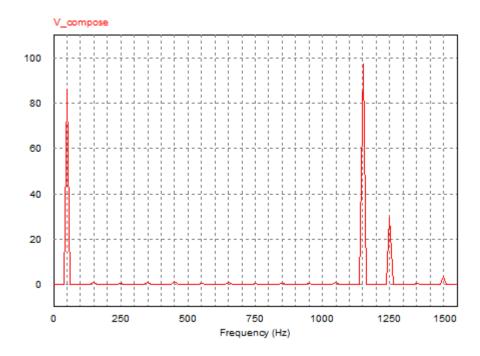

| 5.37 | Tension composée d'un onduleur triphasé $m=7$ et $r=0.5$                              | 102 |

| 5.38 | Spectre de la tension composée d'un onduleur triphasé $m=7$ et $r=0.5$                | 102 |

| 5.39 | Tension et spectre de sortie du bras de l'onduleur pour $m=5$ et $r=0.8$              | 103 |

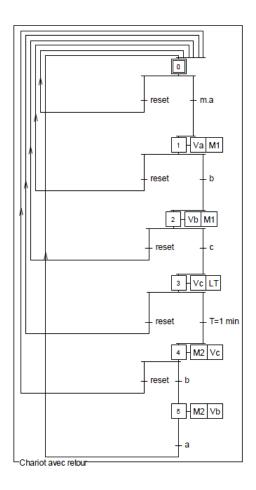

| 40   | Grafcet d'un chariot aller-retour                                                     | 111 |

| 41   | Programme d'un chariot aller-retour                                                   | 112 |

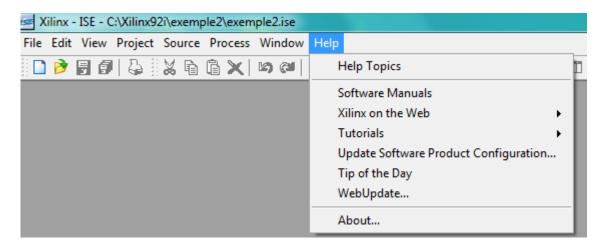

| 42   | Help de ISE                                                                           | 114 |

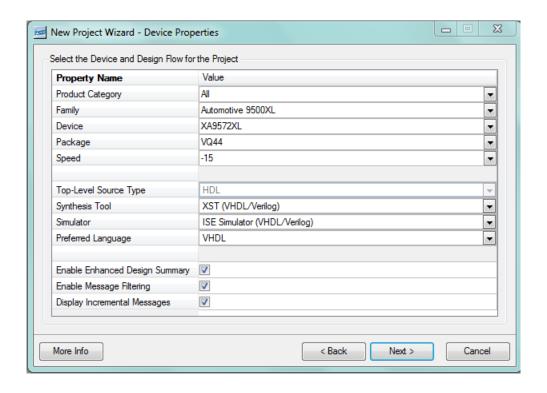

| 43   | Propriétés de dispositif de projet                                                    | 115 |

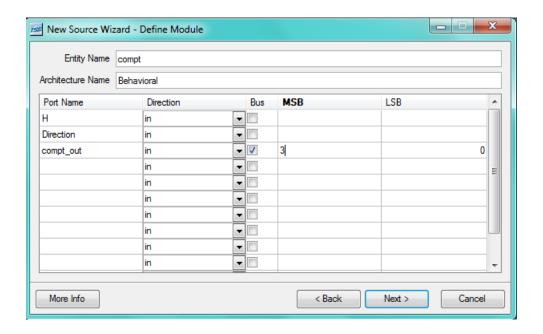

| 44   | Définition du module                                                                  | 116 |

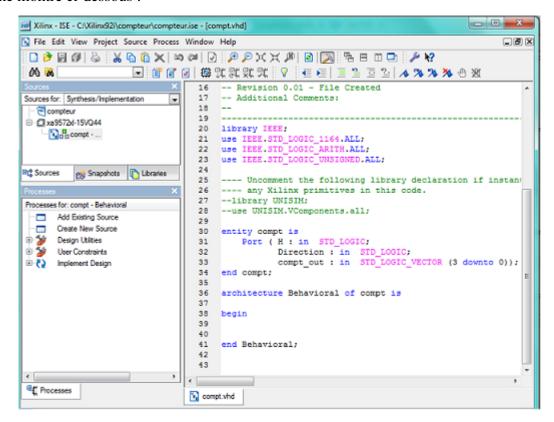

| 45   | Nouveau projet dans ISE                                                               | 117 |

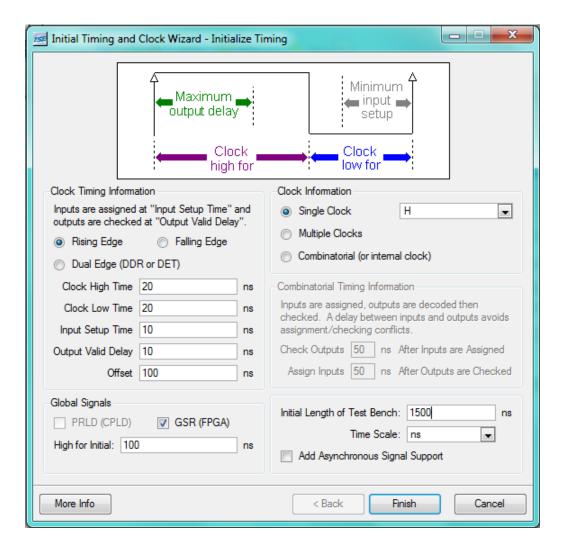

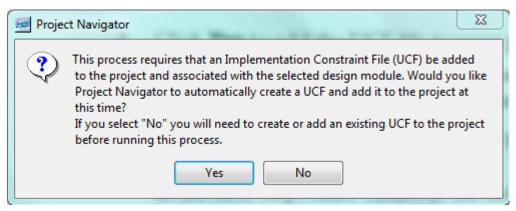

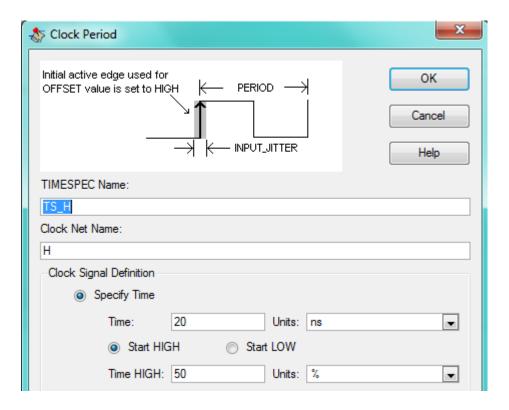

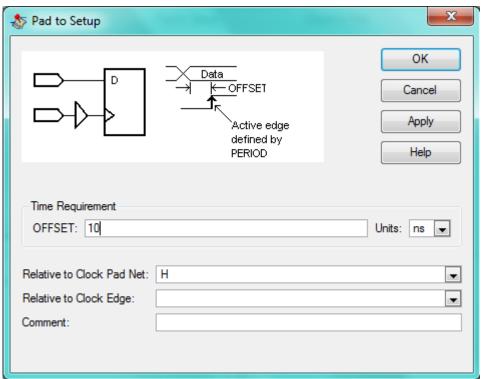

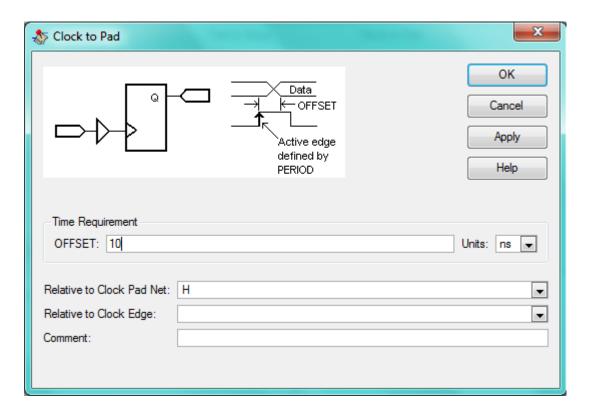

| 46   | Initialisation de synchronisation                                                     | 119 |

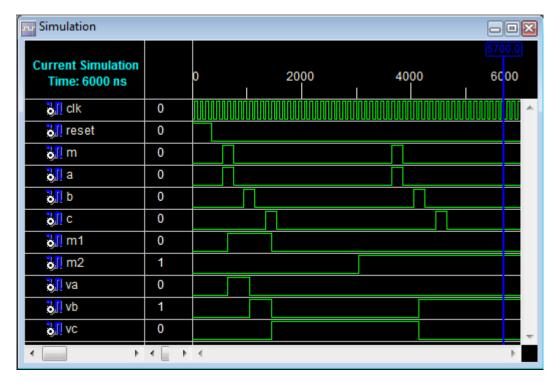

| 47   | Test Bench WaveForm                                                                   | 120 |

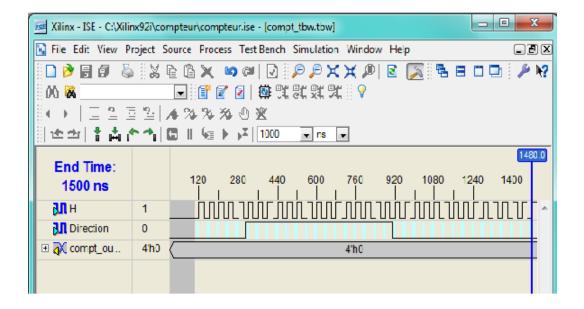

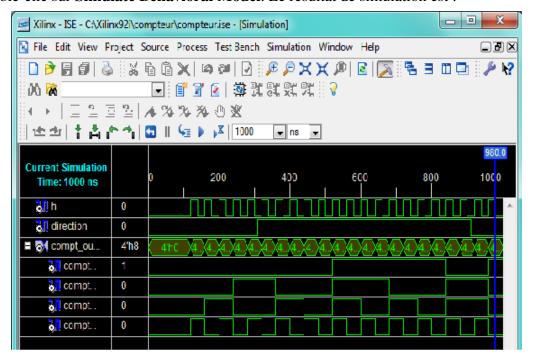

| 48   | compteur decompteur 4 bits                                                            | 120 |

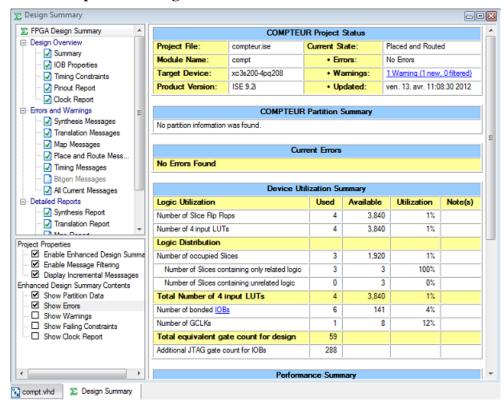

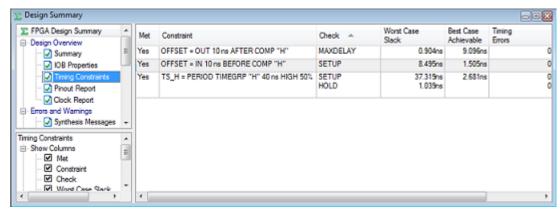

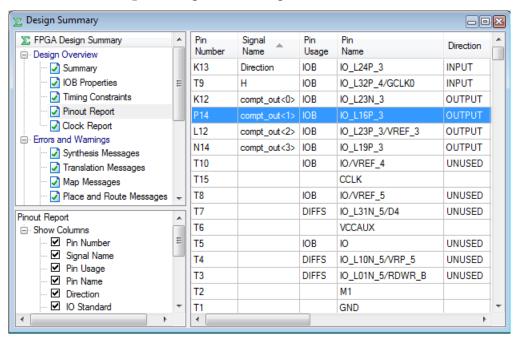

| 49   | Résumé de la conception                                                               | 124 |

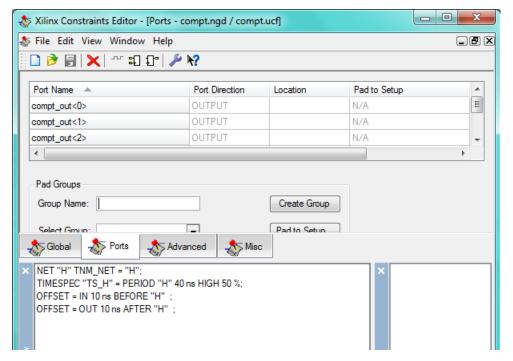

| 50   | Toutes les contraintes de synchronisation                                             | 125 |

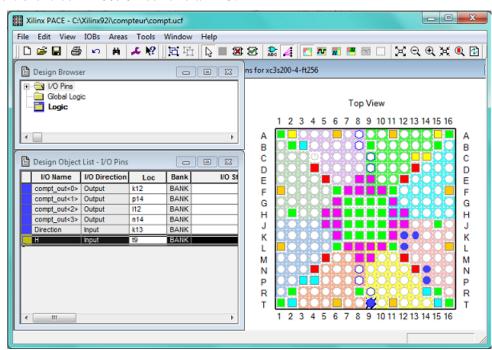

| 51   | Aperçu des broches d'entrées-sorties                                                  | 126 |

| 52   | Architecture interne de la famille VIRTEX-II                                          | 129 |

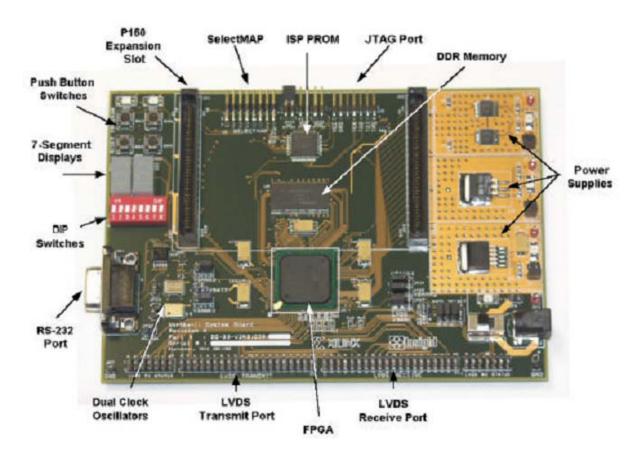

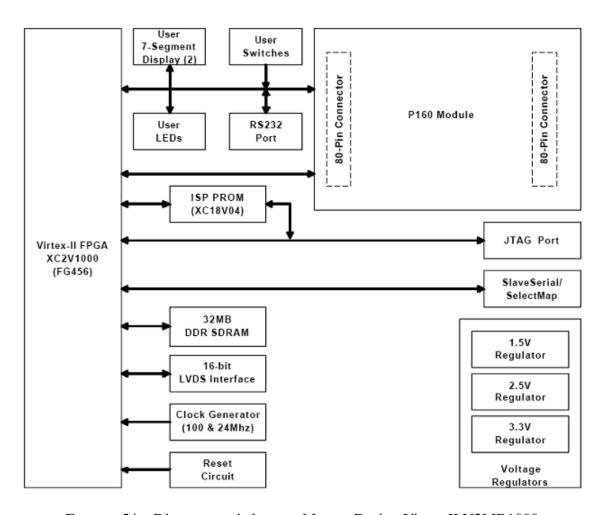

| 53 | Carte de développement "Memec Design V2MB1000"        | 131 |

|----|-------------------------------------------------------|-----|

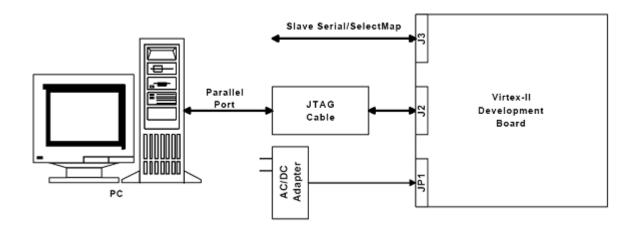

| 54 | Diagramme de la carte Memec Design Virtex-II V2MB1000 | 132 |

| 55 | Chargement du programme sur la carte FPGA             | 134 |

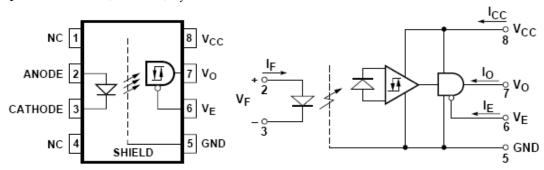

| 56 | L'optocoupleur HCPL2200 et son schéma interne         | 135 |

## Liste des tableaux

| 4.1 | Les opérateurs arithmétiques                    | 60 |

|-----|-------------------------------------------------|----|

| 4.2 | Les types communs                               | 61 |

| 4.3 | Les états du std_logic[2]                       | 62 |

| 4.4 | Les symboles de temps en VHDL                   | 63 |

| 4.5 | Les attributs[12]                               | 64 |

|     |                                                 |    |

| 5.1 | Affectation des broches d'entrées-sorties       | 81 |

| 5.2 | Les angles de commutation exactes pour $m=5$    | 87 |

| 5.3 | Affectation des broches d'entrées-sorties       | 89 |

| 5.4 | Les angles de commutation approximés pour $m=5$ | 94 |

| 5 5 | Affectation des broches d'entrées sorties       | 98 |

## Liste et sigle des abréviations

T: La période de la tension de sortie

E : La tension d'entrée de l'onduleur

$v_0$ : La tension de sortie instantanée

$v_r$ : La tension de référence

$i_0$ : Le courant instantanée de sortie

$V_0$ : La valeur efficace de la tension de sortie

$V_1$ : La valeur efficace du fondamental

$V_n$ : La valeur efficace du  $n^{ime}$  harmonique

$f_0$ : La fréquence de la tension de sortie

$f_p$ : La fréquence du porteuse

$f_r$ : La fréquence du signal de référence

$P_{01}$ : La puissance de sortie

m: L'indice de modulation

r: Le taux de modulation (coefficient de réglage)

$a_n$ : Coefficient de série de Fourier

$b_n$ : Coefficient de la série de Fourier

$\delta_m$ : Largeur de l'impulsion m

$\alpha_m$ : L'angle de commutation de la  $m^{ime}$  impulsion

$E^{(k)}$ : La matrice Jaccobienne

$\Delta \alpha^{(k)}$ : Vecteur d'erreur

$\alpha_s$ : Angle de séparation

VHDL : Very high speed integrated circuit Hardware Description Language

FPGA : Field Programmable Gate Array

MLI : Modulation de Largeur d'Impulsion

PWM : Pulse With Modulation

MLIU : Modulation de Largeur d'Impulsion Uniforme

HF: Facteur d'harmonique

THD : Distorsion totale d'harmonique

LOH : Harmonique le plus bas ordre

ASI : Alimentation Sans Interruption

MAS : Machine Asynchrone

GTO: Gate Turn Off

IGBT : Insulated Gate Bipolar Transistor

NPC : Neutral Point Clamped

PLD : Programmable Logic Device

CPLD : Complex Programmable Logic Device

PSD : Programmable System Devices

PLA : Programmable Logic Array

ASIC : Application Specific Integrated Circuit

SRAM : Static Random Access Memory

LCA : Logic Cells Arays

IOB : Input Output Bloc

CLB: Configurable Logic Bloc

RAM : Random Access Memory

ROM : Read Only Memory

TTL : Transistor-Transistor Logic

CMOS : Complementary Metal Oxide Semiconductor

MOS : Metal Oxide Semiconductor

EPROM : Erasable Programmable Read Only Memory

EEPROM : Electrically Erasable Programmable Read Only Memory

LUT : Look Up Table

RTL : Registre Translate Level

#### **Introduction Générale**

Une des branches de l'électronique en pleine expansion est l'électronique de puissance qui traite et contrôle l'énergie électrique ainsi que sa conversion en d'autres formes d'énergie afin de fournir des tensions et des courants aux différents types de charges selon les applications. On distingue fondamentalement les conversions suivantes : alternatif/continu, continu/alternatif, alternatif/alternatif, et la conversion continu/continu.

L'un des principaux problèmes liés aux convertisseurs statiques, et qui dépend de la stratégie de commande utilisée, est celui de la présence inévitable des harmoniques dans l'onde de sortie. Les harmoniques ont des effets néfastes sur le moteur, ils provoquent l'échauffement excessif, les pulsations du couple et la saturation du circuit magnétique.

Dans un onduleur à Modulation Largeur d'Impulsions (en Anglo-Saxon, Pulse With Modulation), au lieu de de former chaque alternance d'une tension de sortie avec un seul créneau rectangulaire, on la forme de plusieurs créneaux de largeurs convenables. Les schémas des onduleurs restent les mêmes, c'est la commande des interrupteurs qui est modifiée : la fréquence des commutations est supérieure à la fréquence des grandeurs de sortie.

La multiplication du nombre des impulsions formant chacune des alternances d'une tension de sortie présente deux avantages importants :

- Elle repousse vers les fréquences plus élevées les harmoniques de la tension de sortie, ce qui facilite le filtrage.

- Elle permet de faire varier la valeur du fondamental de la tension de sortie, même avec les onduleurs à deux interrupteurs par phase.

L'essor de la Modulation de Largeur d'Implusion est lié aux progrès sur les semi-conducteurs de puissance ; l'augmentation du nombre des commutations entrainerait des pertes excessives si on n'avait pas réussi à réduire les pertes à chacune des commutations.

Le plus souvent on détermine en temps réel les instants de fermeture et d'ouverture des interrupteurs à l'aide d'une électronique de commande analogique ou numérique ou en faisant simultanément appel à ces deux techniques. Pour cette détermination on utilise les intersections d'une onde de référence et d'une onde de modulation. Dans certain applications, on calcule et on mémorise au préalable les instants de commande, les interrupteurs sont ensuite commandés par un microprocesseur.

Le but de notre projet est d'implémenter trois commandes MLI sur une carte FPGA. La première c'est la commande MLI engendrée basée sur l'intersection entre un signal de référence et un signal porteuse, la deuxième c'est une commande MLI basée sur le calcul des angles exactes de commutations par la résolution d'un système d'équation non linéaire, et on termine par une commande MLI avec asservissement du fondamental et élimination des harmoniques sélectives. Dans cette technique les angles de commutation sont approximées à l'aide d'un algorithme on-line.

## Chapitre 1

#### Généralités sur les onduleurs

#### 1.1 Introduction

Les onduleurs constituent une fonction incontournable de l'électronique de puissance, présente dans les domaines d'applications les plus variés. La forte évolution de cette fonction s'est appuyée, d'une part, sur le développement de composants à semi-conducteurs entièrement commandables, puissants, robustes et rapides, d'autre part, sur l'utilisation quasi-généralisée des techniques dites « modulation de largeur d'impulsion ». ces dernières s'appuyant sur les performances en fréquence de découpage permises par les premiers.

#### 1.2 Définition des onduleurs

Les onduleurs de tension sont des convertisseurs statiques qui servent à alimenter, à fréquence fixe ou variable, des charges alternatives. Le but recherché est l'obtention pour chaque tension de sortie d'une forme d'onde approximant au mieux la sinusoïde.

L'onduleur est dit autonome s'il peut fixer lui-même la fréquence et la valeur efficace de sa tension de sortie. Un redresseur commandé tout thyristors peut fonctionner en onduleur. Ce type d'onduleur est dit " non autonome " ou encore " assisté " car il ne permet de fixer ni la fréquence ni la valeur efficace des tensions du réseau alternatif dans lequel il débite [23].

On distingue deux types d'onduleurs autonomes : les onduleurs autonomes de tension, qui sont alimentés par une source de tension continue, d'une impédance interne négligeable et de tension constante, peu affectée par les variations du courant qui la traverse, et Les onduleurs autonomes de courant qui sont alimentés par une source de courant.

#### 1.3 Divers types d'onduleurs

Comme nous avons cité précédemment il y a deux types principales d'onduleurs qui sont les onduleurs autonomes de tension et de courant.

#### 1.3.1 Les onduleurs de tension

On appelle onduleurs de tension un onduleur qui est alimenté par une source de tension continue, c'est-à-dire par une source d'impédance interne négligeable. La tension n'est pas affectée par les variations du courant qui la traverse. La source continue impose la tension à l'entrée de l'onduleur et donc à sa sortie.

Le courant à la sortie et donc le courant à l'entrée dépendent de la charge placée du coté alternatif. Cette charge peut être quelconque à la seule condition qu'il n'agisse pas d'une autre source de tension (capacité ou f.e.m alternative) directement branchée entre les bornes de sortie.

#### 1.3.2 Les onduleurs de courant

Un onduleur de courant (souvent appelé commutateur de courant) est alimenté par une source de courant continue. La source continue impose le courant à l'entrée du convertisseur et donc à sa sortie. La tension à la sortie et donc la tension à l'entrée dépendent de la charge placée du coté alternatif [5].

#### 1.4 Les Différents schémas des onduleurs de tension

#### 1.4.1 Les onduleurs de tension monophasés en demi-pont

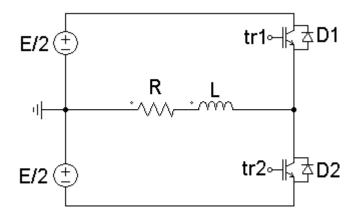

La topologie de l'onduleur monophasé de tension en demi pont est présentée selon la figure 1.1.Il utilise deux interrupteurs bidirectionnels en courant unidirectionnels en tension et une source de tension à point milieu. Les interrupteurs utilisés sont des composants électroniques de puissance commandables tels que le transistor bipolaire, le GTO, l'IGBT, etc ...

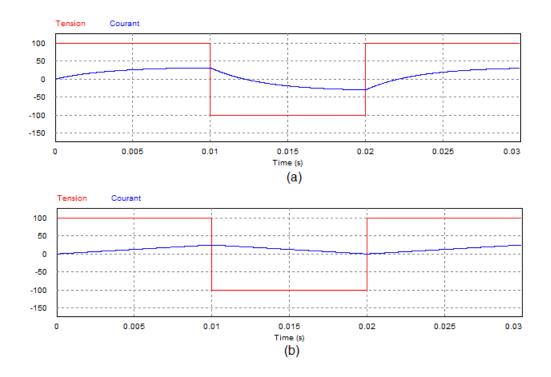

Le principe de fonctionnement de cet onduleur est le suivant [26] : l'interrupteur tr1 se met à conduire pendant une demi période soit T/2, tandis que tr2 est bloqué; alors la tension instantanée aux bornes de la charge est E/2. Mais si au contraire tr2 conduit et tr1 bloqué pendant T/2, la tension instantanée aux bornes de la charge vaut -E/2. La loi de commande doit être faite de sorte que les deux interrupteurs ne conduisent pas en même temps. La figure 1.2-a montre l'évolution du courant pour une charge RL, tandis que la figure 1.2-b montre l'évolution du courant de sortie et le temps de conduction des composants pour une charge purement inductive. Le courant dans ce type de charge ne peut pas changer immédiatement avec la variation de la tension de sortie; si au temps T/2 l'interrupteur tr1 se bloque, le courant dans la charge ne s'annule pas immédiatement, continuera à circuler dans la diode D2 et la charge jusqu'à ce qu'il atteigne zéro. Ce principe est similaire quand tr2 est bloqué au temps T; pendant ce temps, le courant circule dans la partie supérieure de l'onduleur, c'est à dire dans la diode D1 et la charge. Ces diodes D1et D2 sont connues sous le nom de diodes de réaction ou de retour car elles conduisent l'énergie vers la source. Chaque interrupteur conduit pendant T/4; la tension inverse à ses bornes vaut E. Si nous considérons que la tension de sortie est égale à E/2 pendant une demi période, nous pouvons trouver la valeur efficace de cette tension comme suit :

$$V_0 = \left(\frac{2}{T} \int_0^{\frac{T}{2}} \frac{E^2}{4} dt\right)^{\frac{1}{2}}$$

La tension de sortie instantanée peut être exprimée en série de Fourier comme :

$$v_0 = \sum_{n=1}^{+\infty} \frac{2E}{n\pi} sin(n\omega t)$$

$n = 1, 3, 5, ...$

Où  $\omega=2\pi f_0$  est la fréquence de la tension de sortie en rad/s. Pour n = 1, l'équation précédente de  $v_0$  donne la valeur efficace de la composante fondamentale comme :

$$V_1 = \frac{2E}{\sqrt{2}\pi} = 0.45E$$

Il faut noter que pour une charge purement inductive, un seul transistor conduit pour t=T/2 ou  $(90^{\circ})$ . En fonction du facteur de puissance de la charge, la période de conduction d'un transistor pourra varier de  $90^{\circ}$  à  $180^{\circ}$ .

Le courant instantané  $i_0$  pour une charge RL peut être trouvé d'après :

$$i_0 = \sum_{n=1}^{+\infty} \frac{2E}{n\pi\sqrt{R^2 + (nL\omega)^2}} sin(n\omega t - \theta_n)$$

$n = 1, 3, 5, ...$

Où:

$$\theta_n = \tan^{-1}(n\frac{L\omega}{R})$$

Si  $I_{01}$  est la valeur efficace de la fondamentale du courant de charge, la puissance de sortie (pour n=1) est :

$$P_{01} = V_1 I_{01} \cos(\theta_1) = I_{01}^2 R = \left[\frac{2E}{\sqrt{2}\pi\sqrt{R^2 + (L\omega)^2}}\right]^2$$

FIGURE 1.1 – Onduleur de tension monophasé en demi-pont

FIGURE 1.2 – courant pour une charge RL et pour une charge purement inductive

#### 1.4.2 Les onduleurs de tension monophasés en pont

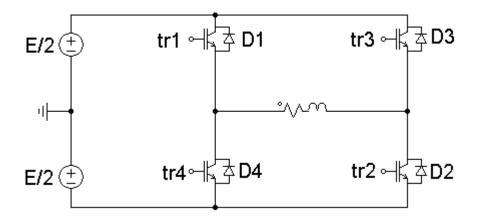

La structure de base de l'onduleur de tension en pont se présente à la figure 1.3. Il se compose de quatre interrupteurs à semi conducteurs avec des diodes antiparallèles. La charge est branchée entre les deux bras de l'onduleur aux points milieux.

Le principe de fonctionnement de cet onduleur est le Suivant [4] : quand tr1 et tr2 sont fermés, tr3 et tr4 sont ouverts, la charge est connectée à la tension E, alors la tension de sortie  $v_o$  à la charge est maintenant égale à E, Cette valeur est aussi obtenue si tr3 et tr4 sont fermés, tr1 et tr2 sont ouverts, la tension à la charge sera égale à -E. Ainsi, l'onduleur de tension en pont peut fournir trois niveaux de tension :E, 0, -E; ce qui n'est pas le cas pour l'onduleur monophasé en demi-pont, qui donnait deux niveaux de tension +E/2, -E/2. Cette caractéristique est un avantage de l'onduleur monophasé en pont, car cela permet de faire varier et régler la tension de sortie  $v_o$  de  $\pm E$ .

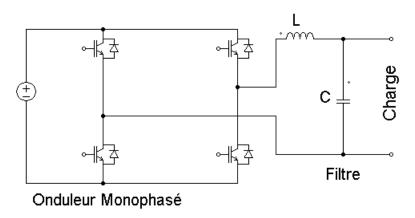

FIGURE 1.3 – Onduleur de tension monophasé en pont

Il faut aussi remarquer que la tension inverse maximale du blocage aux bornes des interrupteurs et des diodes de retour est la même pour les deux types d'onduleurs, si la tension E à la même valeur.

Cependant, avec les conditions égales pour les deux onduleurs, la puissance délivrée par l'onduleur en pont est quatre fois plus importante et sa composante fondamentale harmonique est deux fois plus élevée que celle de l'onduleur en demi pont. La tension de sortie efficace  $v_o$  de l'onduleur à un créneau par alternance est égale à :

$$V_o = \sqrt{\frac{2}{T} \int_0^{\frac{T}{2}} E^2 dt} = E$$

Et l'expression de la série de Fourier est :

$$v_o = \sum_{n=1}^{+\infty} \frac{4E}{n\pi} sin(n\omega t)$$

$n = 1, 3, 5, ...$

où  $\omega=2\pi f_0$  est la fréquence de la tension de sortie en rad/s. Pour n = 1, l'équation précédente de  $v_0$  donne la valeur efficace de la composante fondamentale comme :

$$V_1 = \frac{2\sqrt{2}E}{\pi} = 0.90E$$

#### 1.4.3 Les onduleurs triphasés

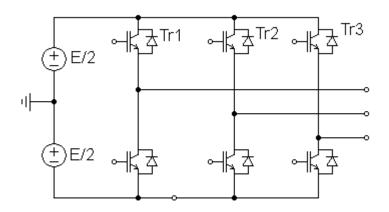

Trois onduleurs monophasés en demi-ponts peuvent être connectés en parallèle pour constituer un onduleur triphasé de tension (figure 1.4).

Les onduleurs monophasés sont utilisés pour des applications de faible puissance, alors que les onduleurs triphasés couvrent la gamme des moyennes et des fortes puissances. L'objectif de cette topologie est de fournir une source de tension triphasée, dont l'amplitude, la phase et la fréquence sont contrôlables [4].

FIGURE 1.4 – Les onduleurs de tension triphasés

Il est facile de généraliser ce principe à un onduleur p-phasé en pont qui comporterait donc p cellules. Dans cette configuration, la cellule de commutation peut donc être considérée comme une phase de l'onduleur, la composante alternative de sa tension de sortie constituant une tension simple du système polyphasé [17].

#### 1.4.4 Les onduleurs multi-niveaux

Les onduleurs multi-niveaux triphasés dont la topologie est basée sur la mise en série d'onduleurs partiels par phase (figure 1.5). Généralement, les tensions continues alimentant les onduleurs partiels. Le bras d'onduleur à n niveau permet de régler les échanges d'énergie entre n-1 sources de tension et une source de courant (charge)[22].

FIGURE 1.5 – Onduleur à 3 niveaux à structure NPC [22]

#### 1.5 Caractérisation de la tension fournie par l'onduleur

Les onduleurs sont caractérisés par la qualité de la tension alternative qu'ils fournissent à leurs sorties. Celle-ci est évaluée par trois paramètres : le facteur d'harmonique, la distorsion totale d'harmonique et l'harmonique de plus bas ordre.

#### 1.5.1 Le facteur d'harmonique (HF)

Il représente la mesure de la contribution individuelle d'une harmonique (par exemple celle du  $n^{ime}$  harmonique).

$$HF_n = \frac{V_n}{V_1}$$

Avec :  $V_1$  :valeur efficace du fondamental.

$V_n$  :valeur efficace du  $n^{ime}$  harmonique.

#### 1.5.2 La distorsion totale d'harmonique (THD)

Elle représente la mesure de rapprochement dans le forme entre l'onde de tension et son fondamental :

$$THD = \frac{\sqrt{\sum_{n=2}^{+\infty} V_n^2}}{V} = \frac{\sqrt{V^2 - V_1^2}}{V} < 1;$$

Ou encore:

$$THD = \frac{V}{V_1} > 1$$

#### 1.5.3 L'harmonique le plus bas ordre (LOH)

C'est celui dont la fréquence est la plus proche du fondamental et dont l'amplitude est supérieure ou égale à 3% de celle du fondamental.

#### 1.6 Le problème de filtrage

La tension en sortie du convertisseur continu/alternatif n'est pas sinusoïdale. En effet, les semiconducteurs travaillant en commutation, la tension de sortie sera toujours constituée de morceaux de tension continue.

Cette tension non sinusoïdale peut être considérée comme la somme d'un fondamental (que l'on souhaite) et de tensions de fréquences multiples de celle du fondamental, les harmoniques (que l'on ne souhaite pas). Ces tensions harmoniques provoquent la circulation de courants harmoniques.

L'objectif du filtrage dépend du système considéré [18] :

– Dans le cas des alimentations sans interruption, on souhaite une tension analogue à celle délivrée par le réseau donc sinusoïdale. On va donc filtrer la tension avec des condensateurs. L'impédance en alternatif d'un condensateur étant  $Z_c = \frac{1}{C\omega}$ , on voit que pour les harmoniques de tension de rang croissants, cette impédance est de plus en plus faible.

– Dans le cas des variateurs de vitesse pour MAS, on souhaite que le courant soit sinusoïdal pour éviter les couples harmoniques générateurs de pertes et de vibrations. On va donc lisser le courant avec des inductances. L'impédance en alternatif d'une inductance étant  $Z_l = L\omega$ , on voit que pour les harmoniques de courants de rang croissants, cette impédance est de plus en plus grande. Dans le cas d'un MAS, l'inductance propre du stator suffit généralement a assurer un filtrage convenable.

#### 1.7 Domaines d'application

Les deux grands domaines applications classiques des onduleurs de tension sont les alimentations de secours et la commande des moteurs alternatifs. Ils sont également caractéristiques de deux grandes familles, respectivement celle des systèmes à fréquence fixe et celle des systèmes à fréquence variable.

#### 1.7.1 Domaine des fréquences fixes

Dans ce premier domaine, l'onduleur de tension est destiné à palier les défaillances ou même l'absence d'un réseau alternatif en recréant la tension correspondante à partir d'une batterie. Le schéma de principe d'une telle application est donné par la figure 1.6

FIGURE 1.6 – Schéma de principe d'un onduleur pour alimentation de secours

Cette application requiert généralement la fourniture d'une tension de sortie très pure, donc sans les harmoniques de découpage, d'où la nécessité d'un filtre de sortie.

#### 1.7.2 Domaine des fréquences variables

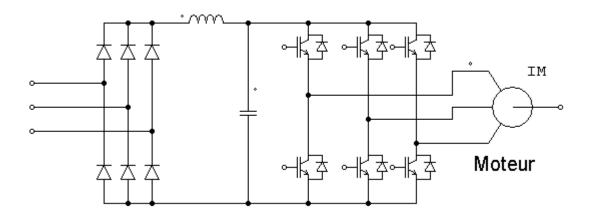

Dans ce deuxième domaine, l'onduleur est généralement alimenté par l'intermédiaire d'un réseau alternatif. La source continue est donc un redresseur suivi d'un filtre d'entrée qui peut avoir une double fonction, à savoir éliminer les composantes harmoniques de courant issues de l'onduleur, et les composantes harmoniques de tension dues au redressement.

Une autre différence notable par rapport au cas précèdent réside dans le domaine de fonctionnement beaucoup plus étendu tant en fréquence fondamentale (de quelques hertz à quelques centaine de hertz) qu'en amplitude[17]. Le domaine d'applications des onduleurs de tension le plus connu est sans doute celui de la variation de vitesse des machines à courant alternatif. Le schéma de principe d'une telle application est donné par la figure 1.7.

FIGURE 1.7 – Schéma de principe d'un onduleur pour la conduite d'un moteur asynchrone

#### 1.8 Commande des onduleurs par techniques M.L.I

#### 1.8.1 Introduction

L'objectif principal de techniques de commande, appliquées aux onduleurs, est de permettre l'obtention d'ondes de tension alternatives, d'amplitude et de fréquence fondamentale réglables, en éliminant ou en repoussant le plus loin possible les composantes harmoniques parasites résultant du découpage. Quelle que soit la forme de l'onde alternative recherchée (le plus souvent sinusoïdale), l'établissement de la stratégie de commande devra, prendre en compte la façon dont ces techniques

vont pouvoir s'insérer dans les boucles de contrôle et de régulation qui sont obligatoirement présentes dans toutes les applications des onduleurs.

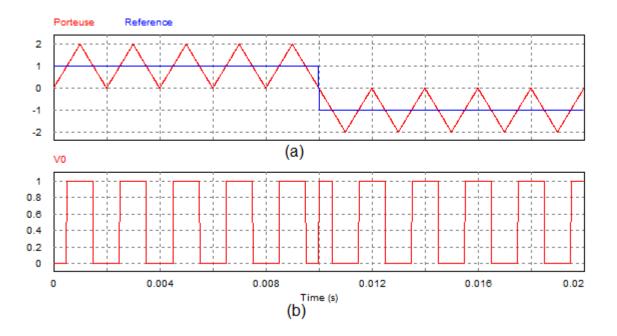

#### 1.8.2 Technique MLI multiple

Lorsqu'on veut réduire le contenu harmonique, on utilise plusieurs impulsions dans chacune des alternances de la tension de sortie. Cette technique est connue sous le nom de MLI multiple. La génération des signaux de commande pour permettre la conduction et le blocage des transistors est montrée sur la figure 1.8 obtenue en comparant un signal de référence avec une porteuse triangulaire. La fréquence du signal de référence règle la fréquence de sortie  $f_0$  et la fréquence  $f_p$  du signal porteuse détermine le nombre d'impulsions durant la période p. Le taux de modulation contrôle l'amplitude de la tension de sortie. Ce type de modulation est également connue sous le nom de Modulation en Largeur d'Impulsions Uniforme (MLIU «Uniform Pulse Width Modulation »). Le nombre d'impulsions par période est :

$$p = \frac{f_p}{f_0} = m$$

Où  $m=\frac{f_p}{f_0}$  est l'indice de modulation. La variation de taux de modulation r de 0 à 1 fait varier la largeur d'impulsion de 0 à  $\pi/p$  et la tension de sortie de 0 à E. La tension de sortie d'un onduleur en pont est donnée par la figure 1.8-b pour une MLI uniforme. Dans cette technique la largeur de chaque impulsion est constante tel que :  $0 < \delta < \frac{\pi}{2p}$ [22].

FIGURE 1.8 – MLI multiple

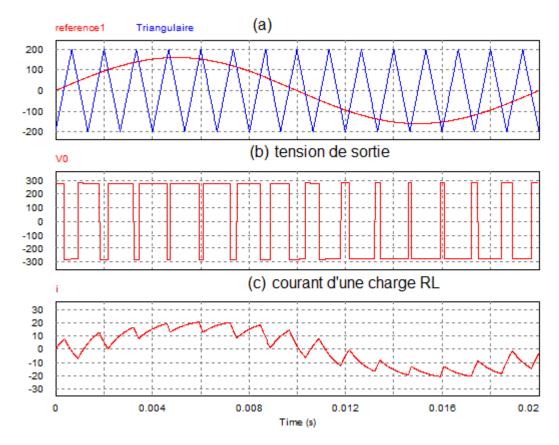

#### 1.8.3 Technique MLI engendrée

La commande MLI Triangulo-sinusoïdale consiste à comparer une valeur de tension de référence de fréquence  $f_r$ , image du signal souhaité à la sortie appelée modulante (généralement sinusoïdal), à une porteuse triangulaire ou en dent de scie de fréquence  $f_p$ . Les points d'intersection entre la modulante et la porteuse engendre l'enclenchement/déclenchement constituant ainsi une impulsion de durée variable et l'ensemble de ces impulsions reconstitue, de ce fait, le fondamental de la sinusoïde de référence.

#### 1.8.4 Technique MLI vectorielle

La technique de modulation vectorielle est une technique numérique pour laquelle l'objectif est de générer une onde MLI de tension v(t) à la sortie de l'onduleur dont la valeur moyen sur chaque période de découpage T est égale à celle de tension sinusoïdale de référence  $v_r(t)$  sur cette période. Ceci est effectué à chaque période d'échantillonnage en sélectionnant les états appropriés des interrupteurs parmi la table d'excitation de l'onduleur à deux niveaux et en déterminant la durée d'application de chacun des états. La sélection des états et la détermination des durées sont basées

sur la transformation triphasée (abc)-biphasée ( $\alpha$ ,  $\beta$ ).

La théorie du transformation triphasée-biphasée dit que les grandeurs triphasées dans la sommes des composantes est nulles dans le référentiel fixe (a,b,c) peuvent être représentée par une grandeur biphasée dans un repère fixe  $(\alpha,\beta)$ . par exemple le vecteur  $[v_{ref}]_{abc} = [v_a,v_b,v_c]$  peut être représenté par le vecteur  $[v_{ref}]_{\alpha\beta} = [v_\alpha,v_\beta]$  en utilisant la transformation :

$$v_{\alpha} = \frac{2}{3}(v_a - \frac{1}{2}(v_b + v_c))$$

$$v_{\beta} = \frac{\sqrt{3}}{3}(v_b - v_c)$$

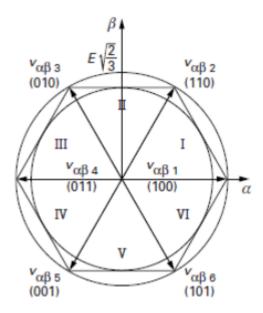

De même cette transformation est appliquée aux huit états de l'onduleur à deux niveaux qui correspond à huit vecteurs dans le repère  $(\alpha, \beta)$  (figure 1.9)[22].

FIGURE 1.9 – Les états d'un onduleur deux niveaux dans le repère  $(\alpha, \beta)$ [18]

Les durées d'application des états des interrupteurs sont déterminées par la relation vectorielle suivante :

$$\overrightarrow{v}_{ref}T = \overrightarrow{v}_i T_i + \overrightarrow{v}_{i+1} T_{i+1} + \overrightarrow{v}_z T_z$$

#### 1.8.5 Technique MLI à élimination des harmoniques (calculée)

La philosophie des MLI calculées est sensiblement différente. Elles sont utilisées lorsque le rapport entre la fréquence de découpage et la fréquence fondamentale est faible, ce qui est fréquent

en forte puissance. Dans ce cas, il y a présence de composantes harmoniques, que l'on cherche à éliminer ou à minimiser en exploitant au mieux le nombre d'impulsions disponibles sur la période fondamentale. Pour atteindre cet objectif, on détermine a priori des formes d'ondes optimisées.

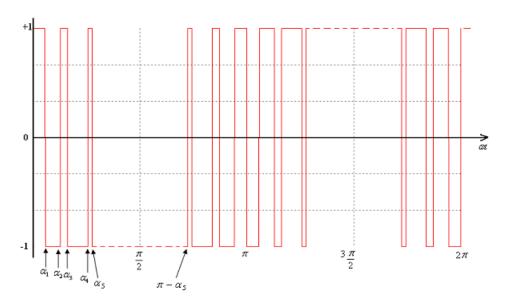

La technique MLI « programmée » est basée l'algorithme de calcul des angles de commutation de Patel et Hoft. Dans cette technique, il est possible d'asservir le fondamental de la tension MLI et d'annuler les amplitudes des *m-1* premiers harmoniques où *m* est le nombre d'angles de commutation de la tension MLI de sortie ou nombre de commutations par quart-d'onde.

FIGURE 1.10 – MLI calculée

#### 1.8.6 Technique MLI delta

une onde triangulaire est utilisée pour osciller à l'intérieur d'une fenêtre définie  $\triangle v$  comme l'enveloppe d'une onde sinusoïdale de référence  $v_r$ . La fonction de commutation de l'onduleur, identique à la tension de sortie  $v_o$  est générée à partir de la verticale de l'onde triangulaire  $v_c$  comme le montre la figure 1.11 .Cette technique de commande est aussi connue sous le nom de « modulation d'hystérésis ». Si la fréquence de l'onde modulée change en maintenant la pente de l'onde triangulaire constante, le nombre d'impulsions et les largeurs des impulsions de l'onde modulante changent aussi.

La fondamentale de la tension de sortie peut être au-dessus de 1E, et dépend de l'amplitude maximale  $V_r$ , et la fréquence  $f_r$  de la tension de référence. La modulation delta peut commander le rapport de tension par rapport à la fréquence qui est une caractéristique désirable en contrôle des moteurs à courant alternatif[6].

FIGURE 1.11 – MLI delta

#### 1.9 Conclusion

Dans ce chapitre, nous avons présenté les principes des différents schémas des onduleurs de tension ainsi quelque stratégies de commande des onduleurs.

La technique MLI présente l'une des techniques les plus utilisées, elle permet d'obtenir un bon spectre de sortie en augmentant l'indice de modulation mais ça nécessite un espace mémoire considérable pour une implémentation numérique.

Les deux techniques MLI engendrée et programmée avec asservissement du fondamental et élimination d'harmoniques objet de ce mémoire sont présentées au chapitre suivant.

### Chapitre 2

# Description des techniques MLI engendrée et à élimination des harmoniques

#### 2.1 Technique de la MLI engendrée

#### 2.1.1 Principe

Au lieu de maintenir la largeur de toutes les impulsions constantes, comme dans le cas de la MLI uniforme, dans ce cas, la largeur de chaque impulsion varie en fonction de l'amplitude d'une onde sinusoïdale évaluée au centre de la même impulsion. Le facteur de distorsion et les harmoniques sont réduits significativement. Les signaux de commande sont montrés sur la figure 2.1-a et sont générés en comparant un signal de référence sinusoïdale avec une onde porteuse triangulaire de fréquence  $f_p$ . Ce type de modulation est communément utilisé dans les applications industrielles. La fréquence du signal de référence  $f_r$  détermine la fréquence  $f_0$  de l'onduleur; alors que l'amplitude maximale contrôle  $V_r$  l'indice de modulation m qui à son tour détermine la tension efficace de sortie  $V_0$ . Le nombre d'impulsions par demi cycle dépend de la fréquence de l'onde porteuse. La tension instantanée de sortie de la figure 2.1-b montre que deux transistors d'une même branche ne peuvent conduire à la fois.

#### 2.1.2 Caractérisation de la modulation

Si la référence est sinusoïdale, deux paramètres caractérisent la commande :l'indice de modulation m et le taux de modulation r.

D'ordinaire la modulation est synchrone, c'est-à-dire que la fréquence  $f_p$  est un multiple entier de  $f_r$ . La tension de sortie est alors vraiment périodique et bien de fréquence  $f_0 = f_r$ .

Mais dans certains cas la modulation est asynchrone, notamment quand à fréquence de modulation  $f_p$  donnée on fait varier de façon continue la fréquence de référence[5].

En modulation synchrone, si m est impair, l'alternance négative de la tension de sortie reproduit au signe près son alternance positive. Le développement en série de Fourier de la tension de sortie ne comporte que des harmoniques impairs.

Au contraire si m est pair, on trouve dans le développement en série de la tension de sortie une composante continue, des harmoniques pairs et impairs. Lorsque l'onduleur est à sortie monophasée, on choisit donc des valeurs impaires de m[5].

#### 2.1.3 Étude de la tension de sortie

La tension efficace de sortie peut être variée en variant l'indice de modulation m. On peut observer que la zone de chaque impulsion correspond approximativement à la zone au dessus de l'onde sinusoïdale entre la moitié des points adjacents de la fin de la période au début des signaux de commande. Si  $\delta_m$  est la largeur de la  $m^{ime}$  impulsion, la tension efficace de sortie peut être écrite sous la forme :

$$V_0 = E \sqrt{\sum_{m=1}^p \frac{\delta_m}{\pi}}$$

Où :p est le nombre d'impulsions.

Ainsi le coefficient de la série de Fourier de cette tension est :

$$b_n = \sum_{m=1}^{p} \frac{2E}{n\pi} sin \frac{n\delta_m}{2} \left[ sin(n(\alpha_m + \frac{\delta_m}{2})) - sin(n(\pi + \alpha_m + \frac{\delta_m}{2})) \right] n = 1, 3, 5, \dots$$

Cette technique réduit le facteur de distorsion mieux que la MLI multiple. Elle élimine toutes les harmoniques inférieures ou égales à 2p-1. Pour p=5, l'harmonique de rang le petit est le neuvième. Toute fois, la tension de sortie contient des harmoniques. Cette modulation repousse ces

harmoniques dans le domaine des hautes fréquences autour de la fréquence de commutation  $f_c$  et ces multiples[1].

FIGURE 2.1 – MLI engendrée pour un onduleur monophasé

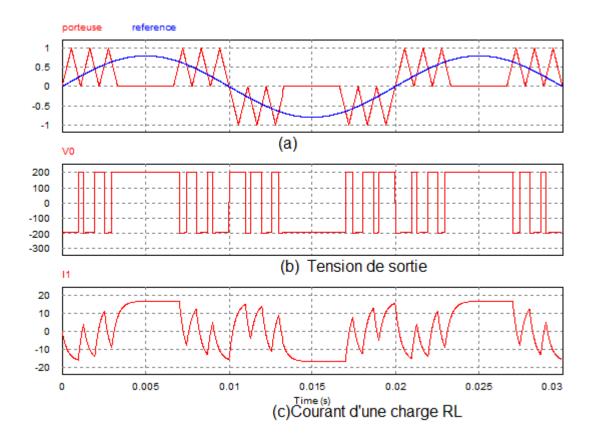

## 2.1.4 Contrôle de tension d'un onduleur triphasé

Un onduleur triphasé peut être considéré comme étant trois onduleurs monophasés déphasés de  $120^{\circ}$ . Ainsi, les techniques que ces derniers utilisent, sont applicables aux onduleurs triphasés. Par exemple, la génération des signaux de commande avec une MLI sinusoïdale est montrée sur la figure 2.2-a. On remarque que les trois ondes de référence sinusoïdales ont déphasées de  $120^{\circ}$  entre elles.

Une onde porteuse est comparée avec le signal de référence de la phase correspondante pour générer le signal de commande de cette phase.

La tension de sortie comme l'indique la figure 2.2-b est générée en éliminant la condition que deux dispositifs de commutation de la même branche ne peuvent conduire en même temps.

FIGURE 2.2 – Onduleur MLI engendrée triphasée

#### 2.1.5 MLI sinusoïdale modifiée

Selon la caractéristique de la MLI sinusoïdale, les largeurs des impulsions s'approchent de l'amplitude maximale de l'onde sinusoïdale pour ne pas changer significativement avec la variation de l'indice de modulation. Cela est dû à la caractéristique d'une onde sinusoïdale et la technique de MLI sinusoïdale peut être modifiée en appliquant l'onde sinusoïdale durant le début et la fin d'un intervalle de 60° par demi cycle; c'est à dire 0 à 60° et de 120° à 180°. Ce type de modulation est connu sous le nom de MLI sinusoïdale modifiée. La composante fondamentale est ainsi augmentée et les caractéristiques des harmoniques sont améliorées. Il réduit le nombre de commutations des dispositifs de puissance et réduit également les pertes dues aux commutations. La figure 2.3 montre le principe de cette modulation[27].

FIGURE 2.3 – MLI modifiée

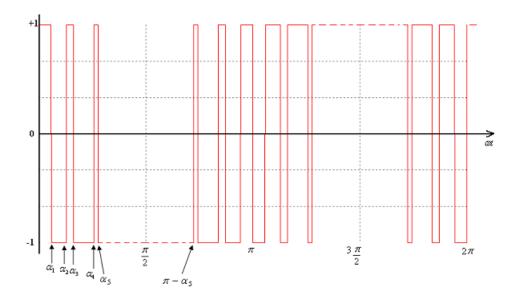

## 2.2 Description de la technique de PATEL et HOFT[13]

Considérons un onduleur demi-pont monophasé.

Soit la tension de sortie à deux états de l'onduleur en demi-pont de la figure 2.4. Les angles de commutation impairs  $\alpha 1, \alpha 3, \alpha 5, \ldots$  définissent des transitions négatives, tandis que les angles de commutation pairs  $\alpha 2, \alpha 4, \alpha 6, \ldots$  définissent des transitions positives. On suppose la tension de sortie périodique d'amplitude unité. Dans ce cas, la tension de sortie  $f(\alpha)$  ou Vao peut s'écrire en série de Fourier :

$$f(\alpha) = a_0 + \sum_{n=1}^{+\infty} (a_n \sin(n\alpha) + b_n \cos(n\alpha))$$

(2.1)

FIGURE 2.4 – graphe d'une tension MLI calculée

Les coefficients  $a_n$  et  $b_n$  sont donnés par :

$$a_0 = \frac{1}{2\pi} \int_0^{2\pi} f(\alpha) d\alpha$$

$$a_n = \frac{1}{\pi} \int_0^{2\pi} f(\alpha) \sin(n\alpha) d\alpha \qquad n = 1, 2, 3, \dots$$

(2.2)

$$b_n = \frac{1}{\pi} \int_0^{2\pi} f(\alpha) \cos(n\alpha) d\alpha$$

D'autre part comme  $f(\alpha)$  présente une symétrie par rapport a  $\frac{\pi}{2}$  et anti-symétrie par rapport a  $\pi$  i.e

$$\begin{cases} f(\alpha)=f(\pi-\alpha)\\\\ f(\pi+\alpha)=-f(\alpha) \end{cases}$$

Le calcul des valeurs de  $a_0,a_n$  et  $b_n$  nous donne :

$$a_0 = \frac{1}{\pi} \int_0^{2\pi} f(\alpha) d\alpha = a_0 = \frac{1}{2\pi} [\int_0^{\pi} f(\alpha) d\alpha + \int_{\pi}^{2\pi} f(\alpha) d\alpha]$$

On effectue un changement de variable :

$$y = \pi - \alpha \to d\alpha = -dy$$

et  $\alpha = \pi - y$ .

$$\Rightarrow \int_{\pi}^{2\pi} f(\alpha) d\alpha = \int_{0}^{\pi} f(\pi - y)(-dy) = -\int_{0}^{\pi} f(y) dy$$

$$\Rightarrow a_{0} = 0.$$

Pour calculer  $a_n$  on effectue le changement de variable :

$$y = \alpha - \pi \to d\alpha = dy.$$

$$\Rightarrow \int_{\pi}^{2\pi} f(\alpha) \sin(n\alpha) d\alpha = \int_{0}^{\pi} f(\pi + y) \sin(n\pi + ny) (dy) = -\int_{0}^{\pi} f(y) \sin(n\pi + ny) dy$$

On voit bien que:

$$sin(n\pi+ny) = \left\{ egin{array}{ll} sin(ny) & ext{si } n ext{ est pair} \\ \\ -sin(ny) & ext{si } n ext{ est impair} \end{array}

ight.$$

Donc:

Donc:

$$\int_{\pi}^{2\pi} f(\alpha) sin(n\alpha) d\alpha = \begin{cases} -\int_{0}^{\pi} f(y) sin(n\pi + ny) dy \Rightarrow a_{n} = 0 & \text{si } n \text{ est pair} \\ \\ \int_{0}^{\pi} f(y) sin(n\pi + ny) dy \Rightarrow a_{n} = \frac{2}{\pi} \int_{0}^{\pi} f(\alpha) sin(n\alpha) d\alpha & \text{si } n \text{ est impair} \end{cases}$$

Finalement:

$$a_n = \frac{2}{\pi} \int_0^{\pi} f(\alpha) sin(n\alpha) d\alpha$$

avec *n* impair.

Pour  $b_n$ , on effectue le même changement de variable on trouve :

$$b_n = \frac{2}{\pi} \int_0^{\pi} f(\alpha) cos(n\alpha) d\alpha$$

avec  $n$  impair.

On peut simplifier les deux expressions par un autre changement de variable :  $\alpha=\pi-y$ . On trouve :

$$a_n = \frac{4}{\pi} \left[ \int_0^{\frac{\pi}{2}} f(\alpha) sin(n\alpha) d\alpha + \int_{\frac{\pi}{2}}^{\pi} f(\alpha) sin(n\alpha) d\alpha \right]$$

$$= \frac{2}{\pi} \left[ \int_0^{\frac{\pi}{2}} f(\alpha) sin(n\alpha) d\alpha + \int_{\frac{\pi}{2}}^0 f(\pi - y) sin(n\pi - ny) (-dy) \right]$$

$$= \frac{2}{\pi} \left[ \int_0^{\frac{\pi}{2}} f(\alpha) sin(n\alpha) d\alpha + \int_0^{\frac{\pi}{2}} f(y) sin(ny) dy \right]$$

$$\Rightarrow a_n = \frac{2}{\pi} \int_0^{\frac{\pi}{2}} f(\alpha) sin(n\alpha) d\alpha \quad \text{avec } n \text{ impair.}$$

Pour  $b_n$ :

$$b_{n} = \frac{2}{\pi} \left[ \int_{0}^{\frac{\pi}{2}} f(\alpha) \cos(n\alpha) d\alpha + \int_{\frac{\pi}{2}}^{\pi} f(\alpha) \cos(n\alpha) d\alpha \right]$$

$$= \frac{2}{\pi} \left[ \int_{0}^{\frac{\pi}{2}} f(\alpha) \cos(n\alpha) d\alpha + \int_{\frac{\pi}{2}}^{0} f(\pi - y) \cos(n\pi - ny) (-dy) \right]$$

$$= \frac{2}{\pi} \left[ \int_{0}^{\frac{\pi}{2}} f(\alpha) \sin(n\alpha) d\alpha - \int_{0}^{\frac{\pi}{2}} f(y) \cos(ny) dy \right]$$

$$\Rightarrow b_{n} = 0 \qquad \forall n$$

Donc on obtient finalement les expressions des coefficients  $a_0,a_n$  et  $b_n$  :

$$a_0 = 0$$

$$a_n = \frac{4}{\pi} \int_0^{\frac{\pi}{2}} f(\alpha) \sin(n\alpha) d\alpha \qquad n = 1, 3, 5, 7, \dots$$

$$b_n = 0 \qquad \forall n$$

$$(2.3)$$

Remplaçons  $f(\alpha)$  par sa valeur dans l'équation 2.3 :

$$a_{n} = \frac{4}{\pi} \left[ \int_{0}^{\alpha_{1}} (1) \sin(n\alpha) d\alpha + \dots + \int_{\alpha_{m-1}}^{\alpha_{m-2}} (-1)^{m-1} \sin(n\alpha) d\alpha + \int_{\alpha_{m}}^{\frac{\pi}{2}} (-1)^{m} \sin(n\alpha) d\alpha \right]$$

$$= \frac{4}{n\pi} \left[ (1 - \cos(n\alpha_{1})) + (\cos(n\alpha_{2}) - \cos(n\alpha_{1})) + \dots + (-1)^{m} (\cos(n\alpha_{m}) - \cos(n\alpha_{m-1})) + \dots + (-1)^{m} (\cos(n\alpha_{m}) - \cos(\frac{n\pi}{2})) \right]$$

Donc:

$$a_n = \frac{4}{n\pi} \left[ 1 + 2\sum_{k=1}^m (-1)^k \cos(n\alpha_k) \right] \qquad n = 1, 3, 5, \dots$$

(2.4)

On considère une alimentation unité, i.e  $E_d/2=1$ .

Le coefficient  $a_n$  est l'amplitude de l'harmonique n du signal suivant :

$$V_{ao}(t) = f(wt) = \sum_{n=1}^{+\infty} a_n sin(n\omega t)$$

Le système d'équation 2.4 possède m variables inconnues  $\alpha_1, \alpha_2, ..., \alpha_m$  appelées angles de commutation exactes. Le problème est de calculer les valeurs de celles-ci qui permettent :

$-\,$  D'annuler les amplitudes  $a_n$  des (m-1) premiers harmoniques  $f_n$  :

$$f_n(\omega t) = a_n sin(n\omega t)$$

$n \neq 1$

- D'assigner une valeur déterminée au fondamental  $f_1$ :

$$f_1(\omega t) = a_1 sin(\omega t)$$

Ces équations sont non linéaires. On utilisera la méthode de Newton-Raphson pour résoudre ce système de m équations non linéaires à m inconnues, méthode que l'on décrira en détail dans la

section 2.

# 2.3 calcul des valeurs exactes des angles de commutation par la méthode de Newton-Raphson

### 2.3.1 Description

La relation 2.4 est un système de m équations non linéaires à m inconnues  $\alpha_1, ..., \alpha_m$ . On assigne une valeur déterminée r, appelée taux de modulation, à l'amplitude  $a_1$  du fondamental et on annule les amplitudes  $a_n$  des (m-1) premiers harmoniques.

On résoud ce système par la méthode itérative de Newton-Raphson. Celle-ci converge bien quadratiquement si l'on possède un bon estimé initial de la solution.

Pour les montages triphasés, les harmoniques de rang 3 et multiple de 3 sont inopérants. Pour cette raison les triplets ne sont pas éliminés dans cette étude.

Le système 2.4 s'écrit encore :

$$a_1 = \frac{4}{\pi} [1 + 2 \sum_{k=1}^{m} (-1)^k \cos(\alpha_k)] = -r$$

$$a_5 = \frac{4}{5\pi} [1 + 2\sum_{k=1}^{m} (-1)^k \cos(5\alpha_k)] = 0$$

$$a_7 = \frac{4}{7\pi} [1 + 2\sum_{k=1}^{m} (-1)^k \cos(7\alpha_k)] = 0$$

(2.5)

.

:

$$a_n = \frac{4}{n\pi} [1 + 2\sum_{k=1}^{m} (-1)^k \cos(n\alpha_k)] = 0$$

Ces amplitudes sont normalisées i.e la tension d'alimentation continue est supposée égale à l'unité. On doit signaler que la valeur du taux de modulation r assignée au fondamental est un indice sans

dimension. Pour obtenir la valeur correspondante en volt, il faut multiplier r par  $E_d/2$ , la tension d'alimentation continue de l'onduleur demi-pont.

D'autre part la méthode itérative de Newton-Raphson ne converge pas pour une valeur positive de r. C'est pourquoi on assigne une valeur négative -r au fondamental[28]. Ce qui correspond à un déphasage de  $\pi$  du fondamental.

En résumé, on a un système de forme générale :

$$f_1(\alpha_1, ..., \alpha_m) = \frac{4}{\pi} [1 + 2 \sum_{k=1}^m (-1)^k \cos(\alpha_k)] + r = 0$$

$$f_2(\alpha_1, ..., \alpha_m) = \frac{4}{5\pi} [1 + 2\sum_{k=1}^m (-1)^k \cos(5\alpha_k)] = 0$$

$$f_3(\alpha_1, ..., \alpha_m) = \frac{4}{7\pi} [1 + 2\sum_{k=1}^m (-1)^k \cos(7\alpha_k)] = 0$$

$$\vdots$$

(2.6)

:

$$f_m(\alpha_1, ..., \alpha_m) = \frac{4}{n\pi} [1 + 2\sum_{k=1}^m (-1)^k \cos(n\alpha_k)] = 0$$

## 2.3.2 Résolution du système non linéaire par la méthode de Newton-Raphson

Notons :  $\alpha^*=(\alpha_1^*,\alpha_2^*,...,\alpha_m^*)$  le vecteur solution du système non linéaire 2.6[28] :

$$f_i(\alpha) = 0$$

avec  $i = 1 : m$  et :  $\alpha = (\alpha_1, ..., \alpha_m)$ .

Si chaque fonction  $f_i$  est continue et continûment différentiable, alors on peut la développer en série de Taylor d'ordre 1 dans le voisinage d'un estimé  $\alpha^{(k)}$  (obtenu à la kième itération) proche de  $\alpha^*$ .

On obtient:

$$f_i(\alpha^*) = f_i(\alpha^* + (\alpha^{(k)} - \alpha^*))$$

$$= f_i(\alpha^{(k)}) + \sum_{i=1}^m \left[\frac{\partial f_i(\alpha)}{\partial \alpha_j}\right]_{\alpha = \alpha^{(k)}} \cdot (\alpha_j^* - \alpha_j^{(k)}) = 0$$

Le système s'écrit donc :

$$f_i(\alpha^{(k)}) + \sum_{j=1}^m \left[\frac{\partial f_i(\alpha)}{\partial \alpha_j}\right]_{\alpha = \alpha^{(k)}} \cdot (\alpha_j^* - \alpha_j^{(k)}) = -f_i(\alpha^*)$$

(2.7)

Définissons la matrice des dérivées premières :  $E^{(k)} = (E_{ij}^{(k)})$

Avec:

$$E_{ij}^{(k)} = [\frac{\partial f_i(\alpha)}{\partial \alpha_j}]_{\alpha = \alpha^{(k)}}$$

$i = 1...m;$   $j = 1...m$

D'où:

$$E^{(k)} = \frac{8}{\pi} \begin{pmatrix} sin(\alpha_1) & -sin(\alpha_2) & \cdots & -(-1)^m sin(\alpha_m) \\ 5sin(5\alpha_1) & -5sin(5\alpha_2) & \cdots & -5(-1)^m sin(5\alpha_m) \\ \vdots & \vdots & \ddots & \vdots \\ nsin(n\alpha_1) & -nsin(n\alpha_2) & \cdots & -n(-1)^m sin(n\alpha_m) \end{pmatrix}$$

Définissons le vecteur d'erreur :  $\triangle \alpha^{(k)} = [\triangle \alpha_1^{(k)}, \triangle \alpha_2^{(k)}, ..., \triangle \alpha_m^{(k)}]^t$  avec :  $\triangle \alpha_j^{(k)} = \alpha_j^* - \alpha_j^{(k)}$ .

Soit le vecteur :

$$F^{(k)} = [F_1^{(k)}, F_2^{(k)}, ..., F_m^{(k)}]$$

avec :  $F_i^{(k)} = -f_i(\alpha^{(k)})$

Alors le système 2.7 s'écrit sous la forme matricielle suivante :

$$E^{(k)}.\triangle\alpha^{(k)} = F^{(k)} \tag{2.8}$$

Où  $\triangle \alpha^{(k)}$  est le vecteur inconnu.

Le système 2.8 est un système linéaire de Cramer que l'on peut résoudre par l'algorithme de Gauss. Une fois le vecteur  $\Delta \alpha^{(k)}$  déterminé, on obtient un meilleur estimé  $\alpha^{(k+1)}$  de  $\alpha^*$  par la relation :  $\alpha^{(k+1)} = \alpha^{(k)} + \Delta \alpha^{(k)}$ .

On continue jusqu'à ce que :  $\mid \alpha^* - \alpha^{(k)} \mid \to 0$  .

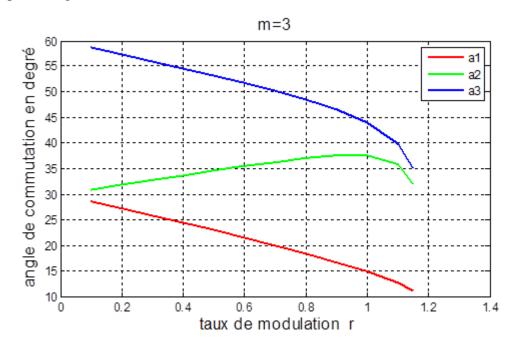

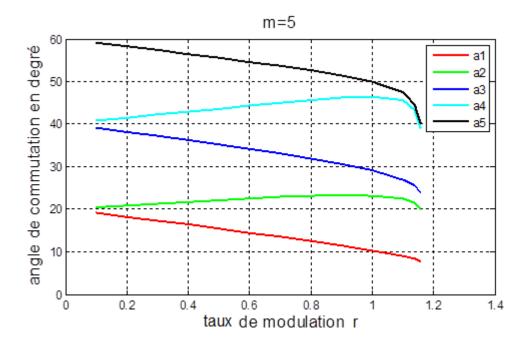

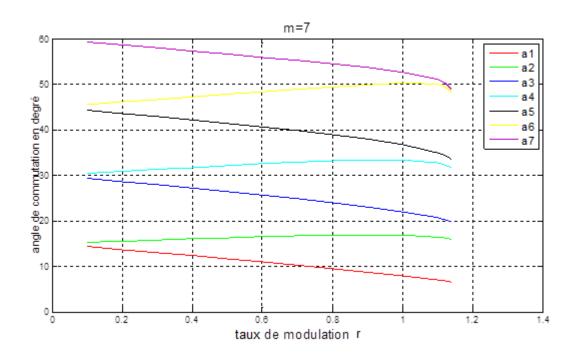

Les figures 2.5, 2.6 et 2.7 donnent, à titre d'exemple, les graphes des angles de commutation exacts calculés pour m égal à 3 ,5 et 7.

FIGURE 2.5 – Courbes des angles de commutation exacts pour m égal à 3.

FIGURE 2.6 – Courbes des angles de commutation exacts pour m égal à 5.

FIGURE 2.7 – Courbes des angles de commutation exacts pour m égal à 7.

## 2.4 Description de l'algorithme 'on-line'

Les équations utilisées pour calculer les angles de commutation sont non linéaires et transcendantes, donc leur solution ne peut pas être faite on-line. Ces angles sont calculés off-line par des méthodes numériques bien connues, ensuite stockés dans des mémoires; mais avec une large gamme de variation du taux de modulation r et l'interpolation requise demande une énorme puissance de calcul et rend le système plus coûteux.

Ce problème a poussé les chercheurs d'élaborer des algorithmes permettant un calcul on-line de ces angles. Dans les paragraphes qui suivent on va élaborer un algorithme MLI calculée on-line, c'est un algorithme basé sur la méthode des moindres carrées.

## 2.4.1 Approximation des angles exacts

Il faut entendre par 'exact' une grandeur calculée en utilisant les valeurs exactes des angles de commutation et par 'approximé' une grandeur calculée en utilisant les valeurs approximées

des angles de commutation. Les valeurs exactes sont calculées par un système d'équations non linéaires. Les valeurs approximées sont calculées par le nouvel algorithme.

D'après les figures 2.5, 2.6 et 2.7 et Pour un taux de modulation r égal à zéro, l'angle  $\alpha_s$ , appelée angle de séparation, est donné par la formule approchée[14] :

$$\alpha_s = rac{2 imes 60^o}{m+1}$$

avec m impair

Pour m fixe, les courbes de rang k impair présentent une pente négative et sont presque parallèles dans la majeure partie de l'intervalle de variation [0,1.15] du taux de modulation r, à l'exception des valeurs extrêmes de cet intervalle. De même les courbes de rang k pair présentent cette fois une pente positive et sont 'presque' parallèles dans les mêmes conditions de variation du taux de modulation r que précédemment. Cette caractéristique nous amènent à approximer les courbes correspondantes à k impair différemment de celles correspondantes à k pair. De plus la forme de ces courbes laisse penser que les fonctions qui approximent les courbes exactes devraient être la combinaison d'une fonction linéaire et d'une autre fonction non linéaire du taux r et dont l'expression reste à déterminer.

L'idée, donc, consiste à approximer la valeur exacte de l'angle de commutation en approximant chaque courbe exacte en deux étapes.

Dans une première étape, on donne une forme générale des angle de commutation en fonction de k, m, r et  $\Delta \alpha_k$ . Dans une seconde étape, on cherche à approximer  $\Delta \alpha_k$  en fonction de k et m.

La mise en œoeuvre de ces deux étapes d'approximation nécessite la conception et la mise au point d'un programme d'approximation basé sur la méthode des Moindres Carrés. Ce programme calcule les coefficients  $A_0, A_1, ...., A_p(p < n)$  de la fonction d'approximation suivante :

$$\phi(x) = A_0 \phi_0(x) + \dots + A_p \phi_p(x)$$

(2.9)

permettant l'approximation de la fonction f(x) connue empiriquement en (n+1) points et qui prend les valeurs  $b_0, b_1, ..., b_n$  aux abscisses  $a_0, a_1, ..., a_n$ . Les fonctions élémentaires d'approximation  $\phi_0, \phi_1, ..., \phi_p$  sont choisies à l'avance[28].

#### 2.4.2 Cas k impair

1. Première étape d'approximation de  $\alpha_k$ : Soit  $\alpha_k$  la valeur exacte de l'angle de commutation et  $\alpha_s$  l'angle de séparation pour m et k données et pour r fixe, on définit [14]:

$$\Delta \alpha_k = \frac{60^o(k+1)}{m+1} - \alpha_k \tag{2.10}$$

La variation normalisée de  $\Delta \alpha_k$  noté  $\Delta_k$  est donnée par :

$$\Delta_k = \frac{\Delta \alpha_k}{\alpha_s} = \frac{(m+1)\Delta \alpha_k}{2 \times 60^o}$$

On remplace dans l'équation 2.10 :

$$\alpha_k = \frac{60^o(k+1)}{m+1} - \frac{2 \times 60^o}{m+1} \Delta_k$$

Par conséquent on cherche d'approximer  $\alpha_k$  par une fonction linéaire de la forme :

$$\phi_{k,m}(r) = A_0 + A_1 r$$

Avec :

$$A_0=rac{60^o(k+1)}{m+1}$$

$$A_1=C_0rac{2 imes60^o}{m+1}\Delta_k \quad \text{Avec $C_0$ paramètre à définir}$$

Pour chaque valeur de m et de k, on fait varier le taux de modulation r de 0.1 à 1.1 par pas de 0.1. Pour chaque valeur du taux r, on calcul la déférence. Le coefficient  $C_0$  est pratiquement constant et égal à -1.25.

Donc:

$$\phi_{k,m}(r) = \frac{60^{\circ}(k+1)}{m+1} - \left[\frac{2 \times 60^{\circ}}{m+1} \times \frac{\Delta_k \times r}{0.8}\right]$$

2. Deuxième étape d'approximation de  $\alpha_k$ : Après l'approximation linéaire de l'angle 'exact' de commutation, dans la première étape d'approximation, on va effectuer maintenant l'approximation de la pente  $\Delta_k$  de la fonction  $\phi(k,r)$  en fonction de k et m.

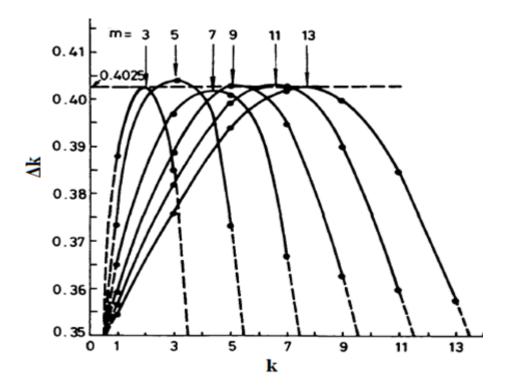

Pour étudier la forme de  $\Delta_k$ , on va calculer  $\Delta_k$  pour des valeur de m et k variant par valeurs impaires et La figure 2.8 représente la fonction  $\Delta_k(k, m)$ .

FIGURE 2.8 – variation de  $\Delta_k$  pour k impair[14]

Cependant, en observant ces courbes on constate qu'elles ont chacune une forme non linéaire parabolique. Elles diminuent en fonction de m pour même k et passent par un maximum fixe quelque soit m et en remarque que  $\Delta_k(k,m)$  est pratiquement égale à  $\Delta_k(m+1-k,m)$  c'est-à-dire elles présentent une symétrie par rapport à  $\frac{(m+1)}{2}$ .

Le problème maintenant est de rechercher comment effectuer l'approximation des courbes de la figure 2.8 à l'aide de fonctions simples et avec une plus grande précision.

Pour répondre à cette question, considérons la fonction suivante[15] :

$$\phi_2(k,m) = \frac{C_1}{m^2} \times (k - \frac{m+1}{2})^2 + C_2$$

On fait varier k (impair) pour chaque m et on calcul les paramètres  $C_1$  et  $C_2$ . Les paramètres précédents sont choisis en minimisant le critère quadratique des moindres carrés. On trouve :  $C_1 = -0.21, C_2 = 0.4025$ .

Finalement la formule approximée des angles de commutation pour k impair est donnée par :

$$\hat{\alpha}_k = \frac{60^o(k+1)}{m+1} - \left[\frac{2 \times 60^o}{m+1} \frac{\hat{\Delta}_k \times r}{0.8}\right]$$

(2.11)

$$\hat{\Delta_k} = \frac{-0.21}{m^2} \times (k - \frac{m+1}{2})^2 + 0.4025$$

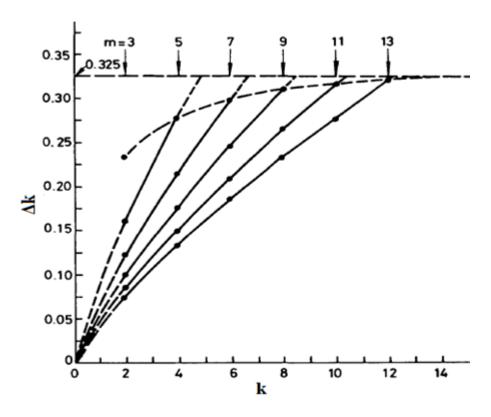

#### 2.4.3 Cas k pair

Pour le cas pair on suive le même raisonnement, la forme de l'angle de commutations a la même forme que le cas impair avec une pente positive :

$$\hat{\alpha}_k = \frac{60^o k}{m+1} + \left[ \frac{2 \times 60^o}{m+1} \frac{\Delta_k \times r}{0.8} \right]$$

Pour étudier la forme de  $\Delta_k$  pour le cas pair, on va calculer  $\Delta_k$  pour des valeur de m et k variant par valeurs paires et La figure 2.9 représente la fonction  $\Delta_k(k,m)$ .

FIGURE 2.9 – variation de  $\Delta_k$  pour k pair[14]

On observe que toutes les courbes  $\Delta_k(k,m)$  passer par l'origine et croissant avec k, et diminuant avec m pour même k.