## REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

ECOLE NATIONALE POLYTECHNIQUE

DÉPARTEMENT D'ÉLECTRONIQUE

Mémoire de projet de fin d'études pour l'obtention du diplôme d'ingénieur d'état en Electronique Thème :

# Implémentation sur FPGA d'un décodeur LDPC pour les communications sans fils

#### **Oualid MOUHOUBI**

Sous la direction de :

M. Mohamed TAGHI

Présenté et soutenu publiquement le 23/06/2016

## Composition du Jury:

Président M. Zidane TERRA Dr ENP Rapporteur M. Mohamed TAGHI Pr ENP Examinateur Mme. Aicha MOUSSAOUI Dr ENP

Promotion: Juin 2016

## D'edicace

" Je dédie ce travail à toute ma famille. À mes chers parents pour tous leurs sacrifices consentis pour mon éducation et ma formation, sans eux je ne serais jamais arrivé à ce niveau. À mon frère et ma sœur pour leurs précieux soutiens et encouragements. À tous mes amis et camarades, à toutes les personnes qui m'ont enseigné tout au long de mon parcours. À tous ceux que je n'ai pas cités et que je n'oublierai jamais leurs soutiens et leurs aides. "

## Remerciement

Je remercie M. M.TAGHI pour son soutien continu, sa disponibilité, son aide et ses précieux conseils.

je tien à remercier chaleureusement monsieur M. Z.TERRA pour m'avoir fait l'honneur de présider le jury de ce mémoire, ainsi que Mme. A.MOUSSAOUI pour voir accepté d'examiner mon travail.

je remercie toute personne qui, d'une manière ou d'une autre a contribué à l'élaboration de ce travail. Enfin, je tien à remercier tous mes amis et camarades ainsi que tous les enseignants du département d'Électronique de l'ENP.

تمثل رموز اختيار التكافؤ منخفض الكثافة (LDPC) رموز مصححات الخطأ الأكثر فعالية لأنها تسمح بالحصول على نتائج قريبة من تلك المعرفة ب نهاية شانون (SHANON) للرموز ذات المجموعات الواسعة جدا فيما يخص جودة تصحيح الخطأ هذه الدراسة خصصناها لتصميم تخطيط نصف متوازي مرن لجهاز فك الرموز بالاعتماد على نظام الحلول الحسابية (خوارزمية) لفك الترميز Min-Sum تم تأكيد كفاءة هذه الخوارزمية عن طريق المحاكاة على جهاز الكمبيوتر. تخطيط جهاز فك الرموز تم دمجه في بطاقة FPGA بعد تقليص حجم رموز ال (LDPC) الخاص بهذا العمل بسبب منطلبات الاختبار. في الأخير تم ربط نتائج التركيب مع الأنماط البيانية المولدة من لغة وصف الأجهزة HDL الخاصة بهذا التخطيط

كلمات مفتاحيه: اختيار التكافؤ منخفض الكثافة (LDPC), جهاز فك الرموز HDL, بطاقة FPGA, التخطيط, لفك الترميز... Min-Sum

#### **Abstract**

Low-density parity-check (LDPC) are among the most powerful forward error correcting codes since they achieve error correction performance very close to the Shannon limit for large block lengths. LDPC block. In this thesis, we investigate into the design architecture of an array type LDPC code based on min-sum algorithm. The performance of the decoding algorithm was first validated via simulations. The detailed design of the decoding architecture was implemented on a field-programmable gate array (FPGA) kit with a short block length as an example. The schematics generated have been documented along with the synthesis results

**Key words:** LDPC, FPGA, HDL, Min-Sum, Decoder, Architecture, Implementation.

#### Résumé

Low-density parity-check (LDPC) codes font partie des codes correcteurs d'erreur les plus performant, puisque ils permettent d'atteindre une performance de correction d'erreur très proche de la limite de Shanon pour des codes en block très larges. Nous avons consacré notre travail à la conception d'une architecture semi parallèle, flexible d'un décodeur LDPC basée sur l' de décodage Min-sum. Les performances de cet algorithme de décodage ont été validé dans un premier temps par le biais d'une simulation. La conception de l'architecture du décodeur a été ensuite implémentée sur la carte FPGA après réduction de la taille du code LDPC considéré pour ce travail, à cause des exigences de test. Les schémas générés par la description HDL de cette architecture ont été associé aux résultats de synthèse.

Mots Clés: LDPC, FPGA, HDL, Min-Sum, Décoder, Architecture, Implémentation.

# Table des matières

| Ta            | able (              | les figures                                                         |    |

|---------------|---------------------|---------------------------------------------------------------------|----|

| Li            | ste d               | es tableaux                                                         |    |

| $\mathbf{Li}$ | ${ m ste} \ { m d}$ | es Abréviations                                                     |    |

| Li            | ste d               | es notations                                                        |    |

| In            | $\mathbf{trod}$     | action générale                                                     | 13 |

| 1             | Gér                 | éralités sur le codage correcteur d'erreur                          | 15 |

|               | 1.1                 | Introduction                                                        | 15 |

|               | 1.2                 | la chaine de communication numérique                                | 15 |

|               |                     | 1.2.1 codage source                                                 | 16 |

|               |                     | 1.2.2 Codage canal                                                  | 17 |

|               |                     | 1.2.3 La modulation                                                 | 17 |

|               |                     | 1.2.4 Le canal de communication                                     | 17 |

|               |                     | 1.2.5 Le canal radio mobile                                         | 19 |

|               |                     | A Bruit dans un canal radio mobile                                  | 19 |

|               |                     | B Impérfection dans le canal radio mobile                           | 20 |

|               |                     | 1.2.6 La capacité d'un canal                                        | 22 |

|               |                     | 1.2.7 Le théorème fondamental du codage canal                       | 24 |

|               | 1.3                 | Les codes correcteur d'erreur                                       | 25 |

|               |                     | 1.3.1 Définitions et notation                                       | 25 |

|               |                     | 1.3.2 Mesure des performances d'un code correcteur d'erreur         | 26 |

|               |                     | 1.3.3 Concaténation de codes                                        | 27 |

|               |                     | 1.3.4 les classes de code correcteurs d'erreurs                     | 28 |

|               | 1.4                 | Les types des codes correcteurs d'rreurs                            | 28 |

|               |                     | 1.4.1 les codes en bloc                                             | 28 |

|               |                     | A Les codes linéaire en bloc                                        | 29 |

|               |                     | B Exemples de codes en bloc                                         | 31 |

|               |                     |                                                                     | 31 |

|               |                     |                                                                     | 32 |

|               |                     |                                                                     | 33 |

|               |                     | 1.4.3 Comparaison des performances entre quelques codes correcteurs |    |

|               |                     | • • •                                                               | 34 |

|               | 1.5                 |                                                                     | 35 |

| 2             | Coc                 | age LDPC                                                            | 36 |

|               | 2.1                 |                                                                     | 36 |

|               | 2.2                 | •                                                                   | 37 |

|               | 2.3                 | •                                                                   | 27 |

|   |                                               | 2.3.1                                                                                                                                    | Codes réguliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                                                                                                        |  |  |  |

|---|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

|   |                                               | 2.3.2                                                                                                                                    | Codes irréguliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                                                        |  |  |  |

|   | 2.4                                           | Consti                                                                                                                                   | ruction des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38                                                                                                        |  |  |  |

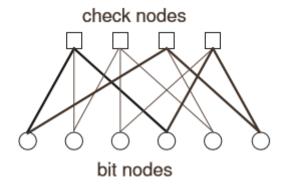

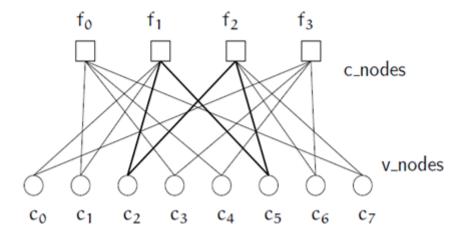

|   | 2.5                                           | sentation graphique des codes LDPC                                                                                                       | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                           |  |  |  |

|   |                                               | 2.5.1                                                                                                                                    | Le profil d'irrégularité des noeuds de données et des noeuds de contrôle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                                                                        |  |  |  |

|   |                                               | 2.5.2                                                                                                                                    | La notion de cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41                                                                                                        |  |  |  |

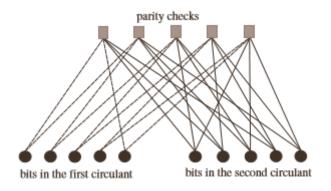

|   | 2.6                                           | Les co                                                                                                                                   | des quasi-cycliques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                                                                                        |  |  |  |

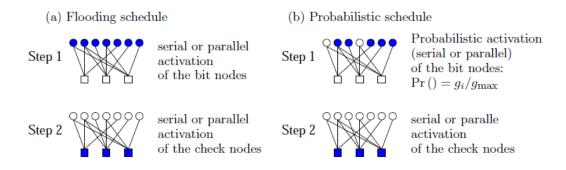

|   | 2.7                                           | Ordon                                                                                                                                    | nancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42                                                                                                        |  |  |  |

|   | 2.8                                           | Opéra                                                                                                                                    | tions d'encodage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                                                        |  |  |  |

|   | 2.9                                           | conclu                                                                                                                                   | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                                                                                                        |  |  |  |

| 3 | Prir                                          | ncipau                                                                                                                                   | x algorithmes de décodage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46                                                                                                        |  |  |  |

|   | 3.1                                           |                                                                                                                                          | thme bit flipping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46                                                                                                        |  |  |  |

|   | 3.2                                           | Algori                                                                                                                                   | thme sum-Product (log-domain)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                                                        |  |  |  |

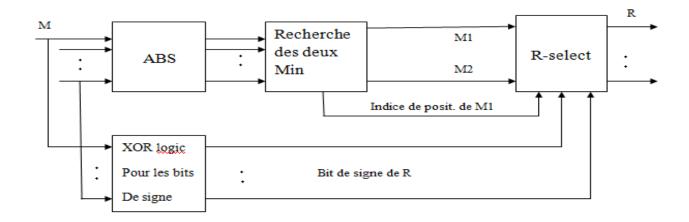

|   | 3.3                                           | Algori                                                                                                                                   | thme Min-Sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                        |  |  |  |

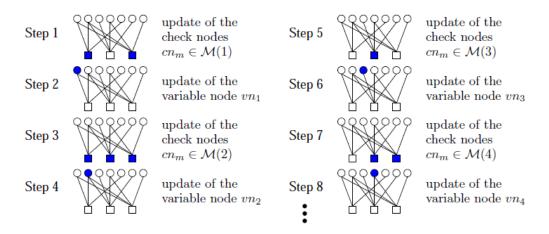

|   | 3.4                                           | Ordon                                                                                                                                    | nancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                        |  |  |  |

|   | 3.5                                           | Étude                                                                                                                                    | des performances des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54                                                                                                        |  |  |  |

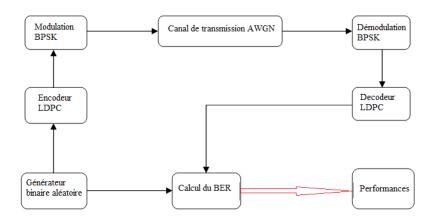

|   |                                               | 3.5.1                                                                                                                                    | Présentation de la chaîne de simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                                                                                                        |  |  |  |

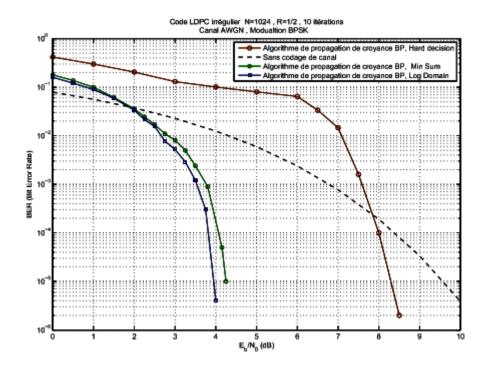

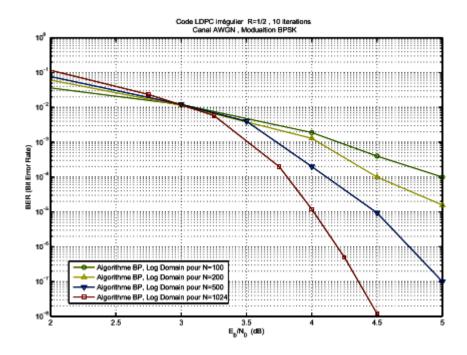

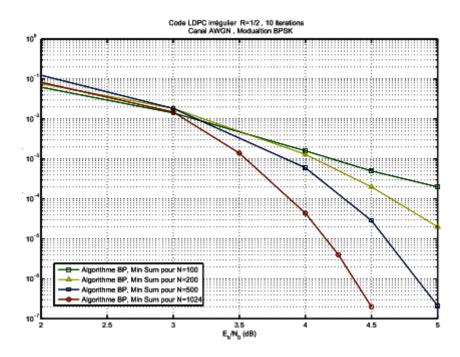

|   |                                               | 3.5.2                                                                                                                                    | Comparaison entre les différents algorithmes de décodage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                                                        |  |  |  |

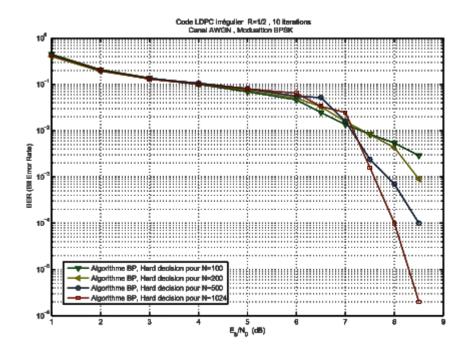

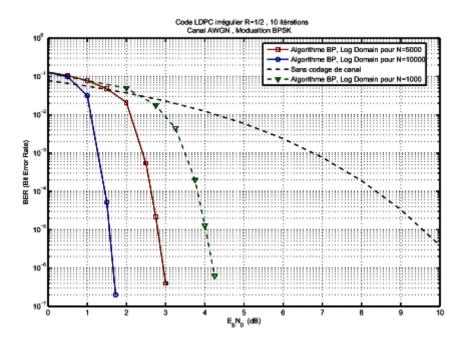

|   |                                               | 3.5.3                                                                                                                                    | Influence de la taille du code sur les performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56                                                                                                        |  |  |  |

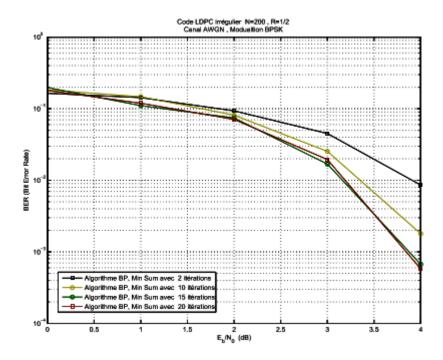

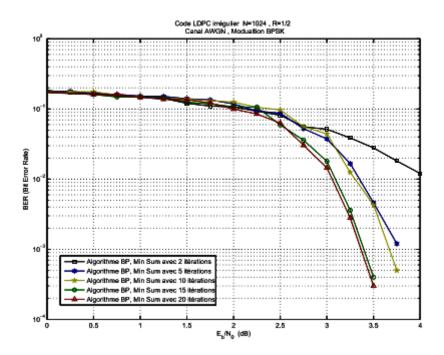

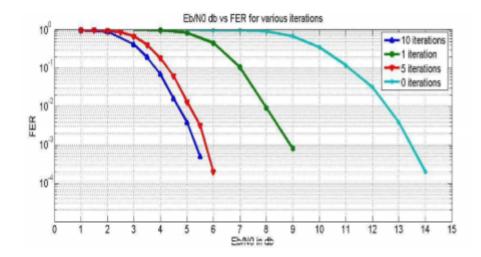

|   |                                               | 3.5.4                                                                                                                                    | Influence du nombre d'itérations du processus de décodage sur les                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           |  |  |  |

|   |                                               |                                                                                                                                          | performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58                                                                                                        |  |  |  |

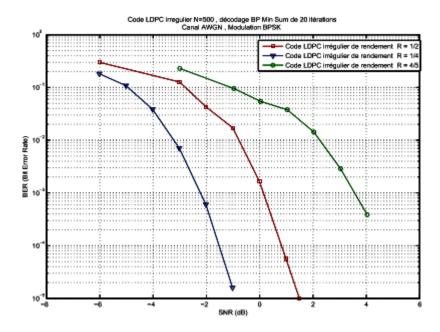

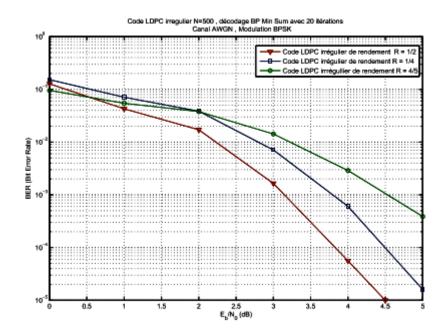

|   |                                               | 3.5.5                                                                                                                                    | Infuence du rendement de codage sur les performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                                                        |  |  |  |

|   | 3.6                                           | conclu                                                                                                                                   | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60                                                                                                        |  |  |  |

|   | _                                             | es choix de conception d'un décodeur LDPC 63                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |  |  |  |

| 4 | Les                                           | choix                                                                                                                                    | de conception d'un décodeur LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                                                                                                        |  |  |  |

| 4 | <b>Les</b> 4.1                                |                                                                                                                                          | de conception d'un décodeur LDPC<br>ecture des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>63</b>                                                                                                 |  |  |  |

| 4 |                                               | Archit                                                                                                                                   | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                         |  |  |  |

| 4 | 4.1                                           | Archit                                                                                                                                   | ecture des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63                                                                                                        |  |  |  |

| 4 | 4.1                                           | Archit<br>Choix<br>4.2.1<br>4.2.2                                                                                                        | ecture des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63<br>64<br>64<br>64                                                                                      |  |  |  |

| 4 | 4.1                                           | Archit<br>Choix<br>4.2.1                                                                                                                 | ecture des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63<br>64<br>64                                                                                            |  |  |  |

| 4 | 4.1                                           | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3                                                                                               | ecture des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63<br>64<br>64<br>64                                                                                      |  |  |  |

| 5 | 4.1<br>4.2<br>4.3                             | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa                                                                                      | ecture des codes LDPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63<br>64<br>64<br>64<br>66<br>67                                                                          |  |  |  |

|   | 4.1<br>4.2<br>4.3<br>Imp                      | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa                                                                                      | de conception du décodeur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63<br>64<br>64<br>64<br>66<br>67                                                                          |  |  |  |

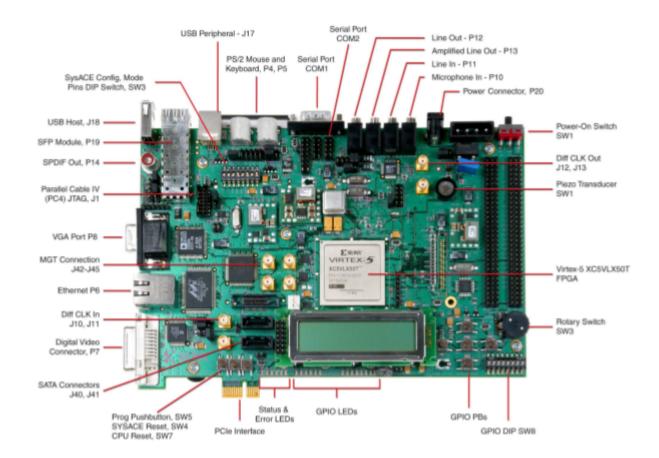

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1        | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa<br>démen<br>Descri                                                                   | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501                                                                                                                                                                                                                                                                                                                                                                                                          | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b>                                                             |  |  |  |

|   | 4.1<br>4.2<br>4.3<br>Imp                      | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lément<br>Descri<br>Archit                                                       | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)                                                                                                                                                                                                                                                                                                                                                               | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69                                                       |  |  |  |

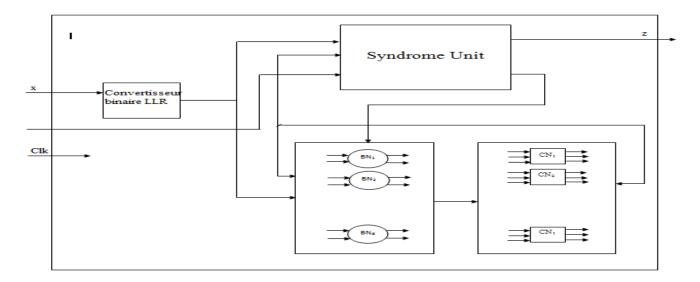

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1        | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1                                               | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA                                                                                                                                                                                                                                                                                                             | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69                                                 |  |  |  |

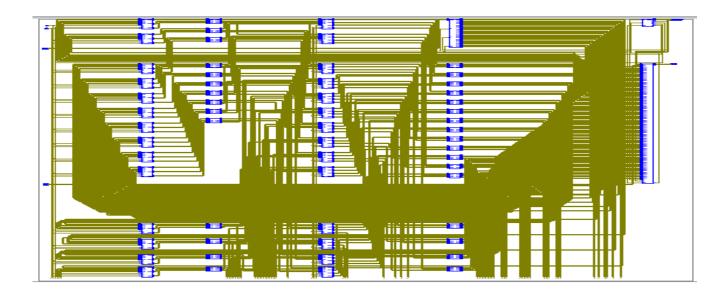

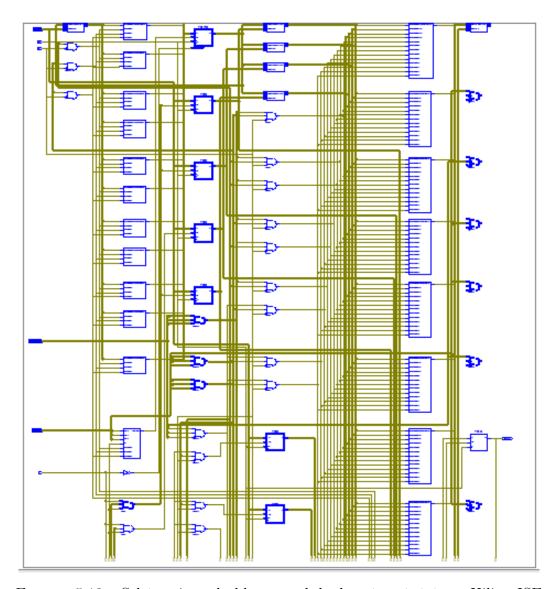

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1        | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lément<br>Descri<br>Archit                                                       | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE                                                                                                                                                                                                                                                              | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71                                           |  |  |  |

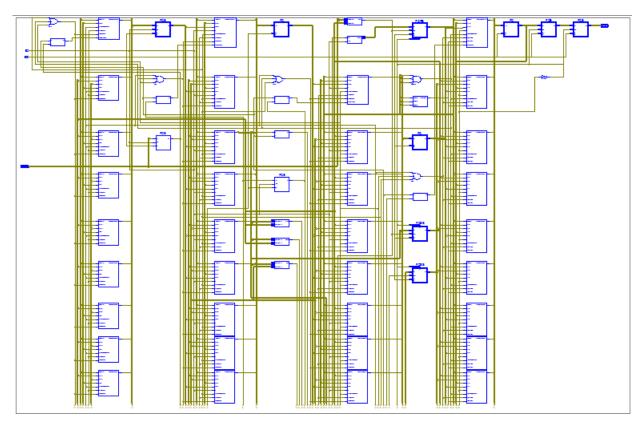

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>compa-<br>lémen<br>Archit<br>5.2.1<br>5.2.2                                      | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  Architecture série  Architecture série  Architecture série  Architecture LDPC basée sur l'algorithme minter de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE  A Schéma globale de l'architecture                                                                                                                                                                                                              | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>71                                     |  |  |  |

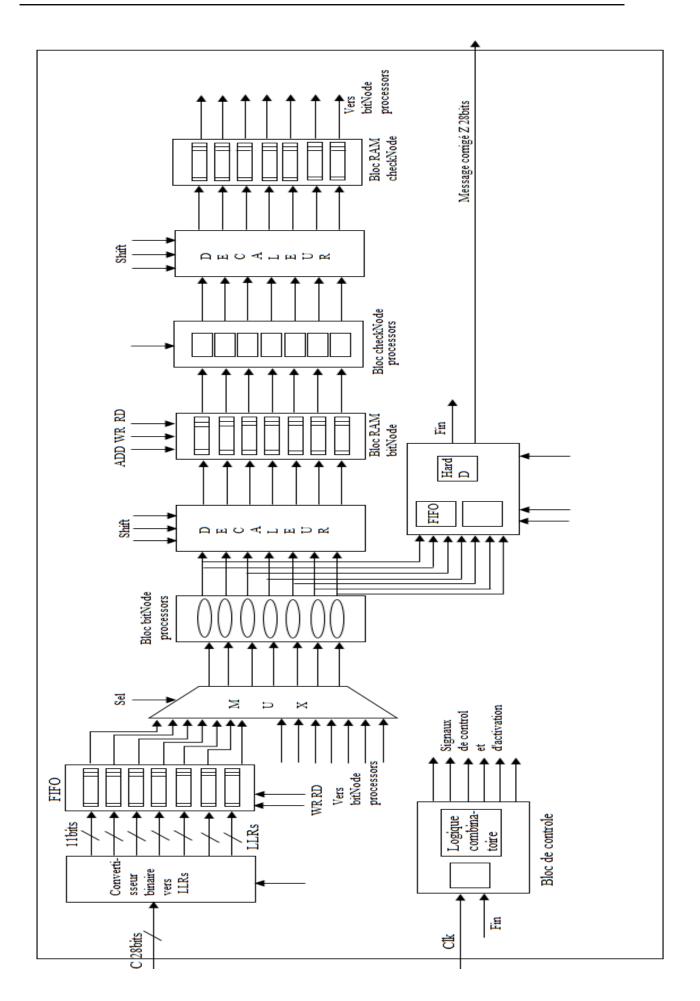

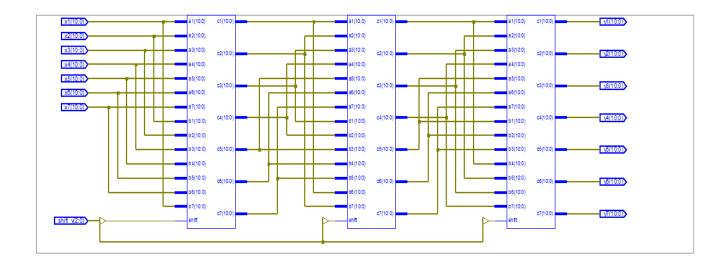

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1        | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1<br>5.2.2                                      | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE  A Schéma globale de l'architecture  ecture Semi-parallèle du code cyclique LDPC                                                                                                                                                                             | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>71<br>72                               |  |  |  |

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archite Choix 4.2.1 4.2.2 4.2.3 Compared Descrite Archite 5.2.1 5.2.2 Archite 5.3.1                                                      | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  Architecture série  Araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE  A Schéma globale de l'architecture  ecture Semi-parallèle du code cyclique LDPC  Détails de la conception architecturale sur FPGA                                                                                                       | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>71<br>72<br>74                         |  |  |  |

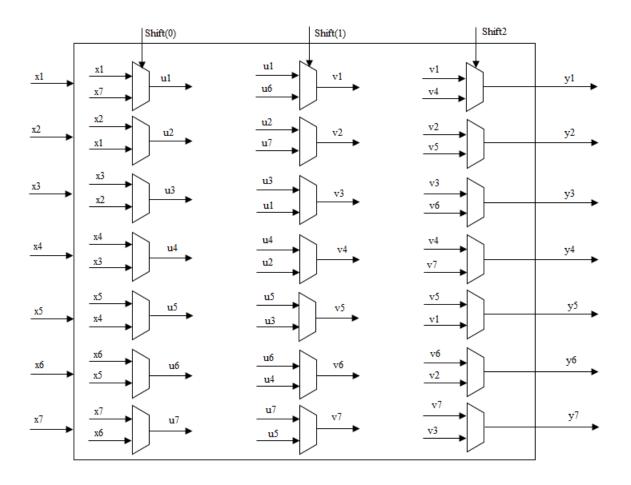

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1<br>5.2.2<br>Archit<br>5.3.1<br>5.3.2          | de conception du décodeur Architecture entièrement parallèle Architecture partiellement parallèle Architecture série araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min- ption de la carte FPGA Vertex5 ML501 ecture parallèle du code régulier 20(3,4) Détails de la conception architecturale sur FPGA Bloc du décodeur ainsi généré sous xilinx ISE A Schéma globale de l'architecture ecture Semi-parallèle du code cyclique LDPC Détails de la conception architecturale sur FPGA Détails de la conception architecture                                                                                                | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>72<br>74<br>76                         |  |  |  |

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1<br>5.2.2<br>Archit<br>5.3.1<br>5.3.2<br>5.3.3 | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE  A Schéma globale de l'architecture  ecture Semi-parallèle du code cyclique LDPC  Détails de la conception architecturale sur FPGA  Decaleur  Pipeline                                                                                                       | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>71<br>72<br>74<br>76<br>78             |  |  |  |

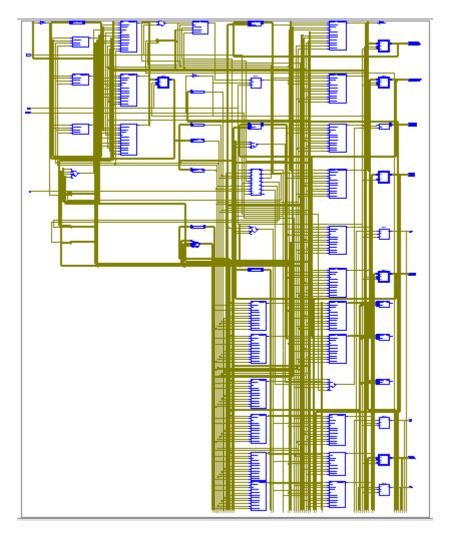

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1<br>5.2.2<br>Archit<br>5.3.1<br>5.3.2          | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE  A Schéma globale de l'architecture  ecture Semi-parallèle du code cyclique LDPC  Détails de la conception architecturale sur FPGA  Decaleur  Pipeline  Bloc du décodeur ainsi généré sous xilinx ISE                                                        | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>72<br>74<br>76<br>78                   |  |  |  |

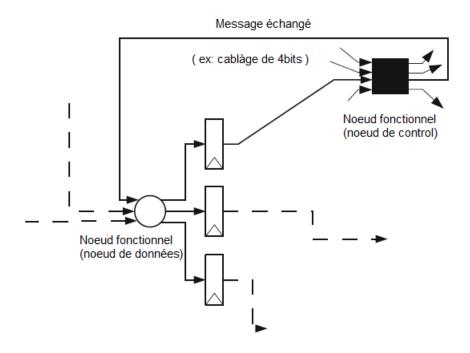

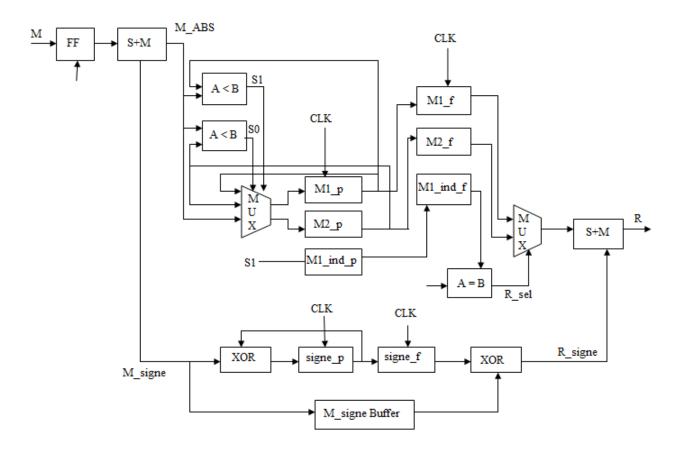

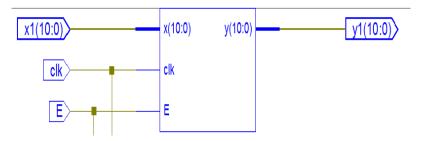

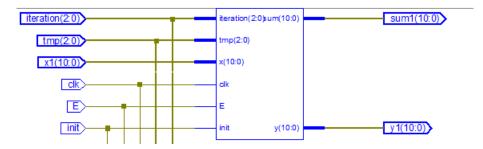

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1<br>5.2.2<br>Archit<br>5.3.1<br>5.3.2<br>5.3.3 | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE  A Schéma globale de l'architecture  ecture Semi-parallèle du code cyclique LDPC  Détails de la conception architecturale sur FPGA  Decaleur  Pipeline  Bloc du décodeur ainsi généré sous xilinx ISE  A processeur de noeuds de contrôle                    | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>71<br>72<br>74<br>76<br>78<br>79       |  |  |  |

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1<br>5.2.2<br>Archit<br>5.3.1<br>5.3.2<br>5.3.3 | de conception du décodeur Architecture entièrement parallèle Architecture partiellement parallèle Architecture série araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min- ption de la carte FPGA Vertex5 ML501 ecture parallèle du code régulier 20(3,4) Détails de la conception architecturale sur FPGA Bloc du décodeur ainsi généré sous xilinx ISE A Schéma globale de l'architecture ecture Semi-parallèle du code cyclique LDPC Détails de la conception architecturale sur FPGA Decaleur Pipeline Bloc du décodeur ainsi généré sous xilinx ISE A processeur de noeuds de contrôle B processeur de noeuds de données | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>71<br>72<br>74<br>76<br>78<br>79<br>79 |  |  |  |

|   | 4.1<br>4.2<br>4.3<br>Imp<br>sum<br>5.1<br>5.2 | Archit<br>Choix<br>4.2.1<br>4.2.2<br>4.2.3<br>Compa-<br>lémen<br>Descri<br>Archit<br>5.2.1<br>5.2.2<br>Archit<br>5.3.1<br>5.3.2<br>5.3.3 | de conception du décodeur  Architecture entièrement parallèle  Architecture partiellement parallèle  Architecture série  araison des deux conceptions  tation d'une architecture LDPC basée sur l'algorithme min-  ption de la carte FPGA Vertex5 ML501  ecture parallèle du code régulier 20(3,4)  Détails de la conception architecturale sur FPGA  Bloc du décodeur ainsi généré sous xilinx ISE  A Schéma globale de l'architecture  ecture Semi-parallèle du code cyclique LDPC  Détails de la conception architecturale sur FPGA  Decaleur  Pipeline  Bloc du décodeur ainsi généré sous xilinx ISE  A processeur de noeuds de contrôle                    | 63<br>64<br>64<br>64<br>66<br>67<br><b>69</b><br>69<br>69<br>71<br>71<br>72<br>74<br>76<br>78<br>79       |  |  |  |

Bibliographie 86

# Table des figures

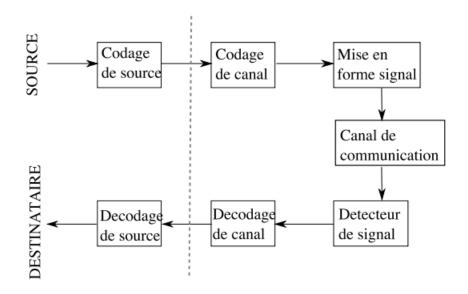

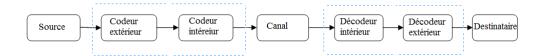

| 1.1  | schema fonctionnel d'une communication numerique                                                                          | 10 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

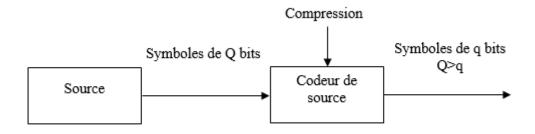

| 1.2  | Schéma simplifié d'un codeur de source                                                                                    | 16 |

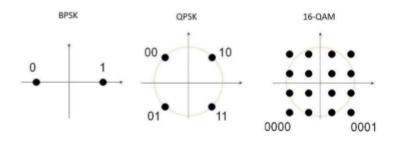

| 1.3  | Exemple de modulation numérique                                                                                           | 17 |

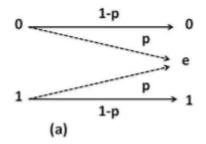

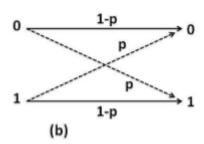

| 1.4  | (a) Le canal binaire avec effacement BEC. (b) Le canal binaire symétrique                                                 |    |

|      | BSC                                                                                                                       | 18 |

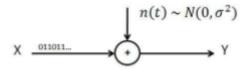

| 1.5  | Canal à entrée binaire perturbée par l'addition d'un bruit blanc gaussien .                                               | 19 |

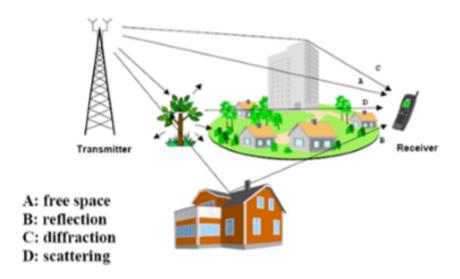

| 1.6  | Propagation par trajets multiples [15]                                                                                    | 21 |

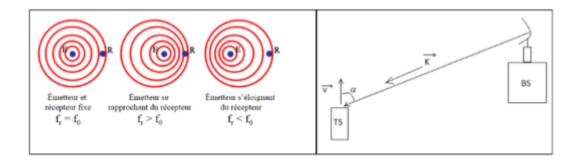

| 1.7  | Principe de l'effet Doppler [15]                                                                                          | 21 |

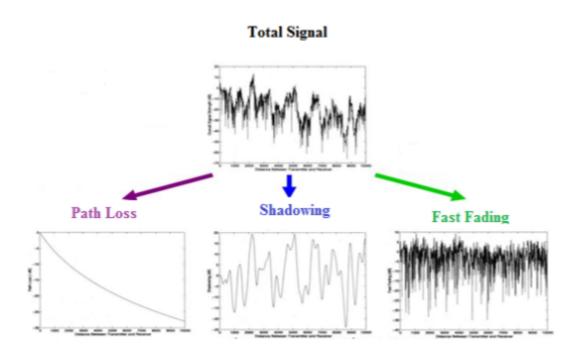

| 1.8  | schéma récapitulatif des différents types d'évanouissement $[15]$                                                         | 23 |

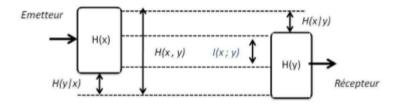

| 1.9  | schéma représentatif de l'information mutuelle                                                                            | 23 |

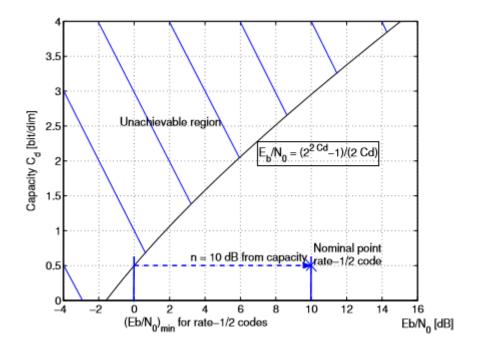

| 1.10 | variation de la capacité du canal AWGN en fonction du SNR                                                                 | 24 |

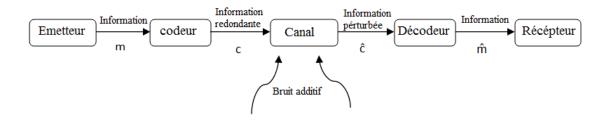

| 1.11 | Schéma simplifié d'un codeurdecodeur de canal                                                                             | 25 |

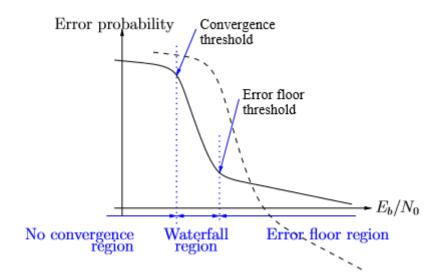

| 1.12 | Illustration des régions caractérisant les performances d'un code correcteur                                              |    |

|      | d'erreurs.                                                                                                                | 27 |

| 1.13 | Concaténation de deux codes correcteurs d'erreurs                                                                         | 27 |

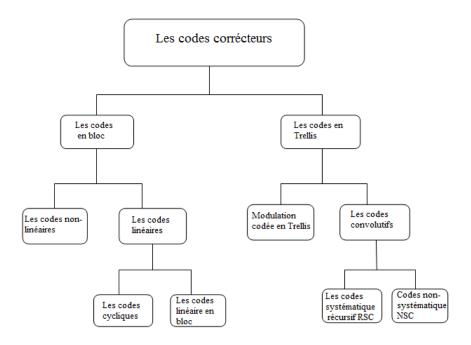

| 1.14 | Classification codes corrécteurs d'erreurs                                                                                | 28 |

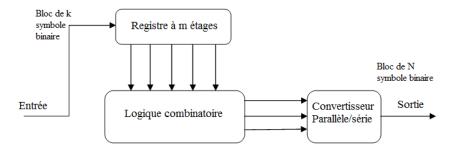

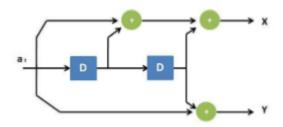

| 1.15 | Schéma de principe d'un codeur convolutif de rendement R et de mémoire                                                    |    |

|      | $m.  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                            | 31 |

| 1.16 | Exemple d'un code convolutif de rendement $R = 1/2$                                                                       | 32 |

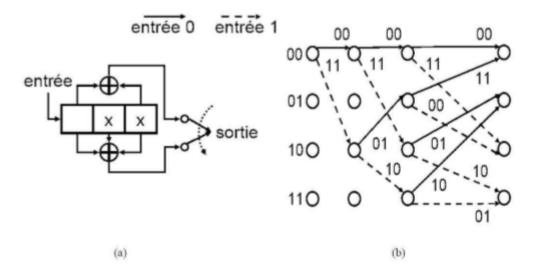

|      | (a) Un code convolutif de R=1/2. (b) Un diagramme en Treillis                                                             | 32 |

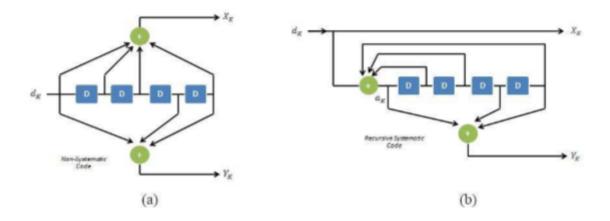

| 1.18 | (a) Un code non-systématique (NSC) (b) Un code récursif systématique                                                      |    |

|      | (RSC)                                                                                                                     | 33 |

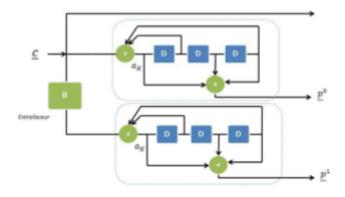

|      | Schéma de principe d'un turbo-code.                                                                                       | 33 |

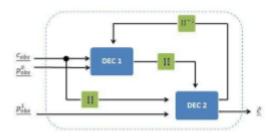

|      | Schéma de principe d'un turbo-decode                                                                                      | 34 |

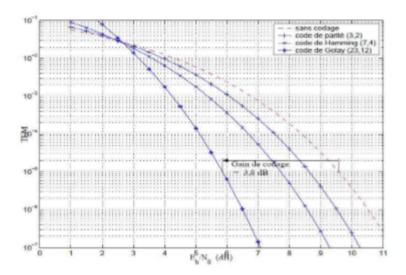

| 1.21 | Comparaison entre les performances des codes de parité, de Hamming et de Golay (Courbes reproduites de la référence [13]) | 34 |

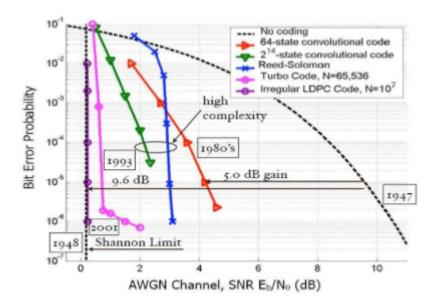

| 1.22 | Comparaison entre les performances des codes convolutifs, Reed-Solomon                                                    |    |

|      | et les techniques de codage avancées (LDPC et Turbo-codes) (Courbes                                                       | 25 |

|      | reproduites de laréférence[2])                                                                                            | 35 |

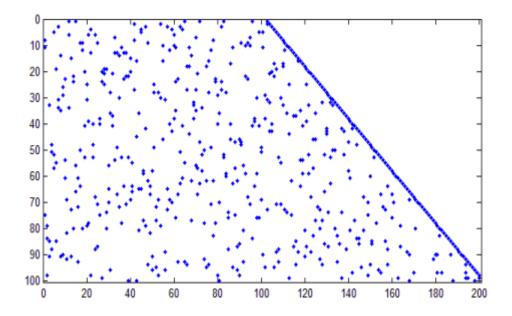

| 2.1  | Représentation d'une matrice irrégulière $N = 2000 \dots \dots \dots$                                                     | 38 |

| 2.2  | Quelques constructions aléatoire de codes réguliers basées sur la méthode                                                 |    |

|      | de Gallager (a) celle de McKay (b,c). Exemple de code régulier de taille                                                  |    |

|      | N=12. Les permutation peuvent aussi par rapport aux colonnes que par                                                      |    |

|      | rapport aux lignes (a,b)                                                                                                  | 40 |

| 2.3  | Représentation graphique d'une matrice irrégulière $N=2000$                                                               | 41 |

| 2.4  | Représentation graphique d'un cycle-4 par le graphe de Tanner                                                             | 42 |

| 2.5  | Graphe de Tanner du code quasi-cyclique représenté par 2.11                                                               | 43 |

| 3.1  | Organigramme de l'algorithme de décodage " bit-flippin "                                                                  | 47 |

| 3.2  | Graphe de la fonction $fi$                                                                                                | 52 |

| Comparaison des performances entre les differents algorithmes de décodage   |                                                                                                    |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| •                                                                           | 52                                                                                                 |

| Les première étape de décodage dans le cas de l'ordonnancement horizon-     |                                                                                                    |

| tale lors 'une itération $i$                                                | 53                                                                                                 |

| Le modèle de simulation utilisé pour l'évaluation des performances des      |                                                                                                    |

|                                                                             | 54                                                                                                 |

|                                                                             |                                                                                                    |

|                                                                             | 56                                                                                                 |

| •                                                                           | 50                                                                                                 |

|                                                                             | 57                                                                                                 |

|                                                                             | 57                                                                                                 |

|                                                                             |                                                                                                    |

|                                                                             | 57                                                                                                 |

|                                                                             |                                                                                                    |

| 9                                                                           | 58                                                                                                 |

| Influence de la taille du code sur les performances pour l'algorithme de    |                                                                                                    |

| décodage Log-Domain                                                         | 59                                                                                                 |

| Influence du nombre d'itérations sur les performances des codes LDPC pour   |                                                                                                    |

| <u>.</u>                                                                    | 59                                                                                                 |

|                                                                             |                                                                                                    |

|                                                                             | 61                                                                                                 |

|                                                                             |                                                                                                    |

|                                                                             | )<br>61                                                                                            |

|                                                                             | 01                                                                                                 |

|                                                                             | co                                                                                                 |

| =I(ED/NU)).                                                                 | 62                                                                                                 |

|                                                                             |                                                                                                    |

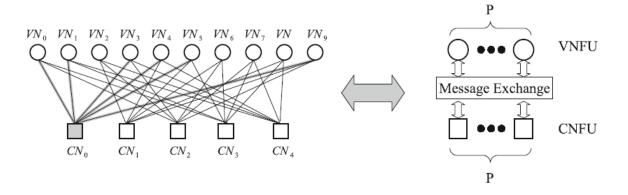

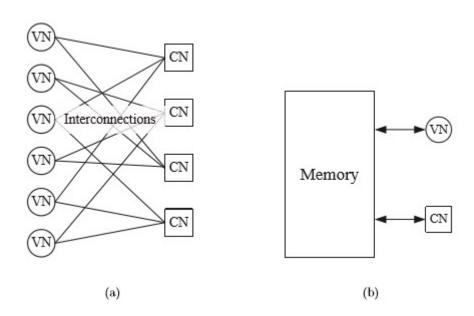

| Chemin de donnée d'une architecture entièrement parallèle, cette figure est |                                                                                                    |

| Chemin de donnée d'une architecture entièrement parallèle. cette figure est | 65                                                                                                 |

| dérivée de [43]                                                             | 65<br>66                                                                                           |

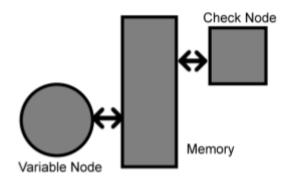

| dérivée de [43]                                                             | 66                                                                                                 |

| dérivée de [43]                                                             |                                                                                                    |

| dérivée de [43]                                                             | 66<br>66                                                                                           |

| dérivée de [43]                                                             | 66<br>66<br>67                                                                                     |

| dérivée de [43]                                                             | 66<br>66                                                                                           |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68                                                                               |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70                                                                         |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71                                                                   |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71                                                                   |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72                                                       |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73                                                 |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73<br>75                                           |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73                                                 |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73<br>75                                           |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73<br>75<br>76                                     |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73<br>75<br>76<br>77                               |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73<br>75<br>76<br>77<br>78                         |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>72<br>73<br>75<br>76<br>77<br>78<br>79                         |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73<br>75<br>76<br>77<br>78<br>79<br>80             |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>72<br>73<br>75<br>76<br>77<br>78<br>80<br>80                   |

| dérivée de [43]                                                             | 66<br>66<br>67<br>68<br>70<br>71<br>71<br>72<br>73<br>75<br>76<br>77<br>78<br>80<br>80<br>81       |

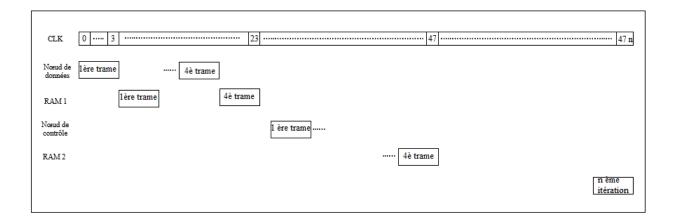

|                                                                             | Les première étape de décodage dans le cas de l'ordonnancement horizontale lors 'une itération $i$ |

# Liste des tableaux

| 1.1 | addition et multiplication dans le corp de Galois F2                               | 26 |

|-----|------------------------------------------------------------------------------------|----|

| 3.1 | Les paramètres de simulation utilisés pour évaluer les performances des codes LDPC | 55 |

|     | Degré de distribution des lignes de la matrice H                                   | 55 |

|     | Caractéristiques de la carte FPGA Vertex5 ml501                                    |    |

#### Liste des abréviations

**APP** A Posteriori Probability

**AWGN** Additive White Gaussian Noise

**BCH** Bose-Chaudhuri-Hocquenghem

**BEC** BinaryErasure Channel

**BER** Bit Error Rate

**BLAST** Bell LayeredSpace Time

**BP** Belief Propagation

**BPSK** Binary Phase Shift Keying

**BSC** BinarySymmetric Channel

**CCSDS** The Consultative Committer for Space Data Systems

**CNRS** Centre National de Recherche Scientifique

**DVB-S2** 2<sup>nd</sup>Géeneration Digital Video Broadcast Spatial

**DVB-T** Digital VideoBroadcastTerrestrial

**ENSPM** Ecole Nationale Supérieure de Physique de Marseille

**FER** Frame Error Rate

**FSO** Free SpaceOptie

**GSM** Goupe Signaux Multidimentionnels

**GUI** Graphic User Interface

i.i.d indépendant identiquement didtribué

**IEEE** Institute of Electrical and ElectronicsEngineers

**LD** Linear Dispersion

**LDPC** LowDensityParity Check

**LLR** Log Likelihhod Ratio

MAP Maximum A Posteriori

MIT Massachusetts InstituteofTechnology

MMSE Minimum Mean Square Eroor

**MP** Message Passing

MUX Schéma de Multiplixage Spatial

## Liste des notations

| sign(.           | ) La fonction signe                                                   |  |  |

|------------------|-----------------------------------------------------------------------|--|--|

| abs(.)           | La valeur absolue                                                     |  |  |

| (.) <sup>t</sup> | La transposé d'un vecteur ou d'une matrice                            |  |  |

| (.) <sup>H</sup> | L'opérateur Hermitien c.à.d. le conjugué de la transposé d'une matric |  |  |

| (.)*             | )* Le conjugué                                                        |  |  |

| L(.)             | Le log-rapport de vraisemblance                                       |  |  |

| II               | La fonction d'entrelacement                                           |  |  |

| $II^{-1}$        | La fonction de désentrelacement                                       |  |  |

| C                | Le veteur de la séquence d'information                                |  |  |

| $M_{y/x}$        | Matrice de transition d'un canal                                      |  |  |

| C                | La capacité d'un canal                                                |  |  |

| $d_x$            | Le débit symbole de la source                                         |  |  |

| X                | Le vecteur du mot de code                                             |  |  |

| P                | Le vecteur de Parité                                                  |  |  |

| K                | La taille de la séquence d'information                                |  |  |

| N                | La taille du mot de code                                              |  |  |

| M                | Le nombre de bits de redondance ou parité                             |  |  |

| R                | Rendement de codage de canal                                          |  |  |

| v                | Longueur de contrainte d'un code convulitif                           |  |  |

| m                | Mémoire d'un code convulitif                                          |  |  |

| $F_q$            | Corps de galois et de q éléments                                      |  |  |

| $d_H$            | La distance de Hamming                                                |  |  |

| $W_H$            | Le poid de Hamming                                                    |  |  |

| $d_{min}$        | La distance minimale                                                  |  |  |

| X                | La matrice du code espace-temps                                       |  |  |

| N                | La matrice de bruit                                                   |  |  |

| Y                | La matrice de récepton                                                |  |  |

| $R_{STC}$        | Rendemenr de codage espace-temps                                      |  |  |

# Introduction générale

Le monde vit ces 2 dernières décennies l'ère du tout numérique où la technologie des communications sans fils se taille la part du lion. Cet extraordinaire essor que connaît cette technologie est principalement dû aux avancées considérables dans domaine de la micro(nano) électronique ainsi qu'à la demande de plus en pressante de moyens de communications souples, plus rapides, et plus efficaces.

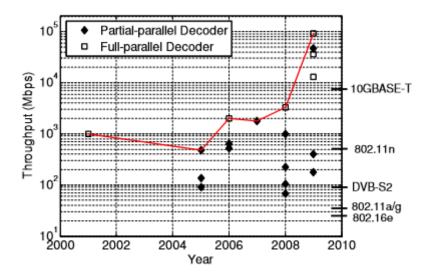

Les Techniques développées récemment dans ce secteur ont permis d'atteindre des débits de transmission très élevés de l'ordre du Gbps Les dispositifs et circuits de corrections d'erreurs qui sont une brique de base dans les systèmes de communications ont été l'objet de recherches intenses dans le but d'augmenter la fiabilité de transmission et de permettre des débits très élevés.

La découverte dans les années 90 des Turbo-codes et, plus généralement du principe itératif appliqué au traitement du signal, a révolutionné la manière d'appréhender un système de communications numériques. Cette avancée notable a permis la redécouverte des codes correcteurs d'erreurs inventés par R. Gallager en 1963, appelés codes Low Density Parity Check (LDPC).

En 2004, les codes LDPC ont été introduits pour la première fois dans la norme de télédiffusion numérique par satellite (DVB-S2) [1], et à partir de cette année, les applications de ces codes ne cessent d'augmenter, surtout dans les communications sans fils, en effet, ils ont été adopté quelques années plu-tard par plusieurs standard récents, tels que le WiMAX WLAN 802.16e [1], le G.hn/G.9960 pour les réseaux domestiques filaire [2], et le 10GBASE-T standard pour les 10 Gigabit Ethernet (802.3an) [3]

L'intégration des techniques de codage dites avancées, telles que les codes LDPC, se généralise donc dans les standards de communications. Dans ce contexte l'objectif de notre travail est d'étudier en largeur et en profondeur les codes LDPC notamment les algorithmes de décodage et les différentes techniques architecturale et matérielle existantes, afin de proposer une architecture d'un décodeur LDPC, d'un un code prédéfini choisi à partir du standards de communications Wi-max, alliant performance et flexibilité.

#### Organisation du document

Ce mémoire est organisé comme suit :

Le **chapitre 1**, décrit brièvement les concepts généraux liés à la théorie de l'information et au codage canal, une description de la chaîne de communication est initialement introduit ensuite détaillée, en indiquant le rôle de chaque élément la constituant, suivit d'une définition générale des codes correcteur d'erreurs et finalement une comparaison de performance entre les codes correcteurs d'erreurs les plus connus.

Dans le **chapitre 2**, une large présentation des codes LDPC est proposée, incluant les notations et outils mathématiques indispensable à la compréhension, particulièrement au sujet d'encodage situé dans la dernière section; Ce chapitre traite de la classe des codes LDPC, de la construction des codes LDPC et du concept d'ordonnancement qui sera d'une grande utilité pour le chapitre **chapitre 5** afin de discuter les différents types d'architectures possible lors de l'implémentation d'un code LDPC, ce chapitre introduira de plus, la représentation de ces codes et enfin le concept des codes cycliques et leur avantage à augmenter la flexibilité du décodeur.

Le **chapitre 3** est divisé en deux parties, dans un premier temps, une profonde description des algorithmes de décodage des codes LDPC dérivée de la théorie du chapitre précédent et d'une logique mathématique qui finit par une déduction de l'algorithme Minsum, qui fera l'objet de notre architecture. tandis que la deuxième partie est consacrée pour une étude de performance des différents algorithmes de décodage conçu pour différents types de codes LDPC.

Quand au **chapitre 4**, il fera l'objet d'une description architecturale de différentes implémentations des codes LDPC en déduisant les avantages et inconvénient de chacune d'elles, et enfin une comparaison des différents types de conceptions

Enfin dans le **chapitre 5**, est entamé par une présentation de la carte FPGA ML501 sur laquelle l'implémentation de notre travaille à été effectuée, nous proposons deux types d'architecture basée sur l'algorithme Min-sum sur lesquelles nous avons travaillé tout au long de notre projet, pour chacune d'entre elles, un détail de conception, une présentation des différents blocs ainsi généré par la plate-forme Xilinx ISE Virtex 5 XC5VLX110, et enfin une simulation accompagnée d'une discussion des résultats obtenus est proposée.

Une **conclusion** et quelques **perspectives** sont finalement donnés à la fin de ce document.

# Chapitre 1

# Généralités sur le codage correcteur d'erreur

Ce premier chapitre a pour objectif de présenter des principes et des concepts fondamentaux qui seront utiles pour la compréhension et l'implémentation des codes LDPC. Ce chapitre commence par illustrer la chaîne de communication et expliquer brièvement le rôle et l'intérêt de chaque bloc de la chaîne, avant d'introduire les différents types des codes correcteurs d'erreurs, et finir par une comparaison de leur performance.

#### 1.1 Introduction

L'objectif fondamental d'un système de communication, est de reproduire en un point decla chaîne de communication un message transmis à partir d'un autre point, mais le problèmecqui se pose, est que le canal est généralement soumis à des perturbations, telles que le bruit et les interférences. Alors, comment faire pour établir une communication fiable dans ces conditions?