#### REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

#### MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

#### ECOLE NATIONALE POLYTECHENIQUE DEPARTEMENT ELECTRONIQUE LABORATOIRE SIGNAL ET COMMUNICATIONS

## Thèse de Doctorat

En Électronique

Présentée par **IZEBOUDJEN NOUMA**Magister en électronique à l'ENP

#### Intitulé

# Plateforme pour l'Implémentation des Réseaux de Neurones sur FPGA: Application à l'Algorithme de la Rétro Propagation du Gradient (RPG)

Soutenue publiquement le 09 Avril 2014 devant le jury composé de :

Président : GUERTI MHANIA PROFESSEUR ENP

Directeur de thèse : FARAH AHCENE PROFESSEUR ENSTA

Co-directeur de thèse: BESSALAH HAMID MAITRE DE RECHERCHES/A CDTA

Examinateur: BABA ALI RIAD MAITRE DE CONFERENCES/A USTHB

Examinateur: LARBES CHERIF PROFESSEUR ENP

Examinateur: TOUHAMI RACHIDA PROFESSEUR USTHB

#### **ENP 2014**

#### ملخص

إن العمل المنجز في إطار هذه الأطروحة يتعلق بتصميم منصة لتنفيذ شبكات الأجهزة العصبية الاصطناعية المبرمجة على FPGA. و وقد كرسنا الفصل الأول من هذا العمل في عرض لمحة FPGA. و وقد كرسنا الفصل الأول من هذا العمل في عرض لمحة علمة عن الشبكات العصبية وبالأخص PERCEPTRON المتعدد الطبقات المستند إلى خوارزمية(RPG). في الفصل الثاني أجرينا دراسة عن درجة ما وصلت إليه الأبحاث في ما يخص تنفيذ أجهزة الشبكات العصبية ، وقد أدى ذلك بنا إلى اقتراح مقاربة جديدة لتصنيف الدوائر العصبية تبدأ من الأجهزة القياسية و تنتهي إلى الدوائر و الأنظمة المدمجة على الشرائح. في الفصل الثالث، أجرينا دراسة مختلف الجوانب لتنفيذ خوارزمية RPG على FPGA على FPGA ، أي ودرجة التوازي ، واختيار لغة وصف الأجهزة و تقييم الأداء من البنية المقترحة. وأولينا اهتماما خاصا بتأثير اختيار دائرة المضاعف على أداء الشبكة العصبية؛ من حيث المساحة وسرعة التنفيذ. كما أخدنا بعين الاعتبار الجوانب ذات الصلة باختيار عائلة PPGA و كذا المسألة المتعلقة بكثافة التكامل في الفصل الرابع، طبقنا البرمجة الديناميكية على خوارزمية. وقد تم إجراء دراسة مقارنة لثلاثة أساليب في البرمجة الديناميكية ل PPGA: برمجة ثابتة، برمجة ديناميكية شاملة ويرمجة محلية. في الفصل الخامس، نقترح منهجية جديدة لتصميم الشبكات العصبية الاصطناعية، مبنية على أساس تطبيق مفهوم إعادة الاستخدام للتصميم على شبكات الأجهزة العصبية.

الكلمك الرئيسية: الشبكات العصبية، منصة، خوار زمية الانتشار الرجعي للخطأ، عائلة FPGA ،البرمجة الديناميكية ، إعادة الاستخدام، والتوازي

#### Résumé

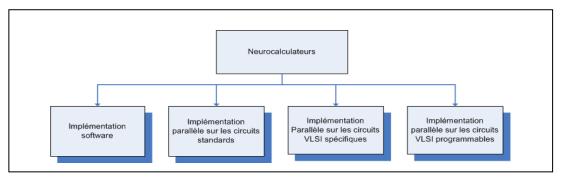

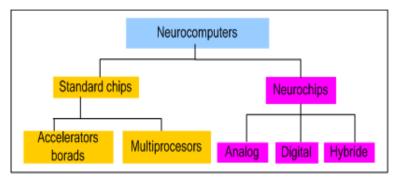

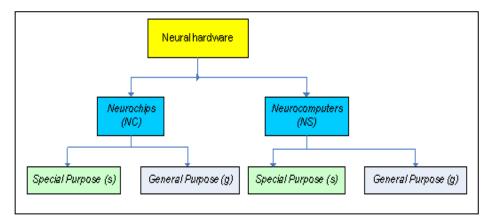

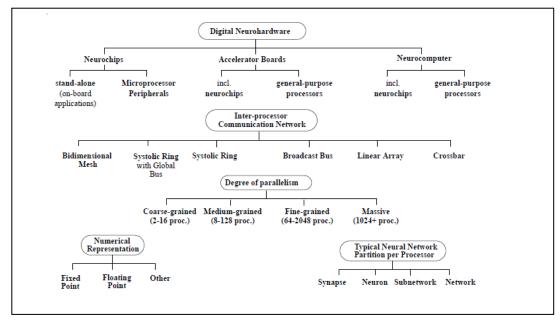

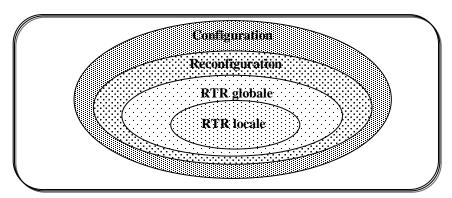

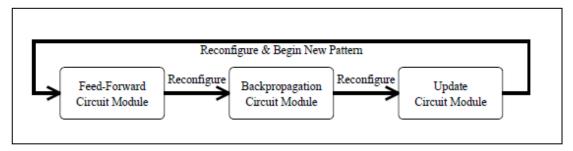

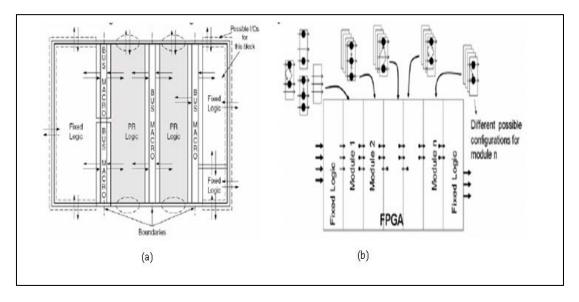

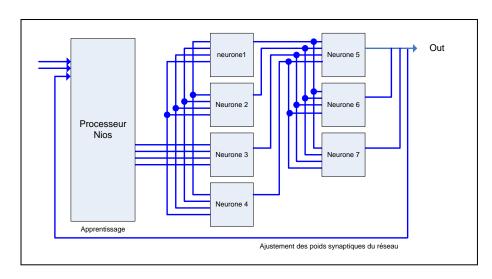

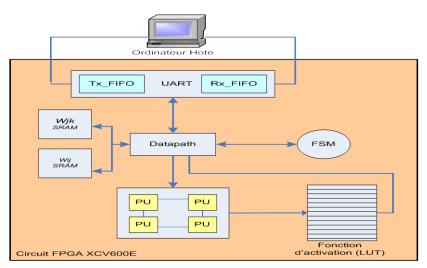

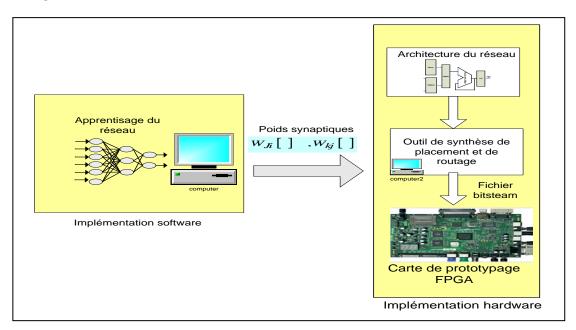

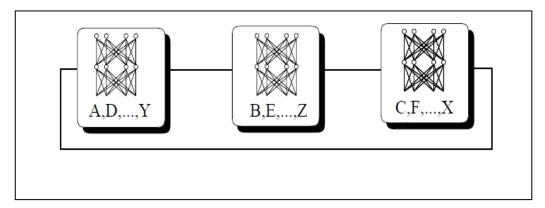

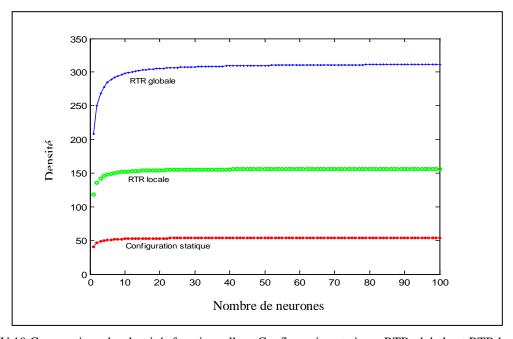

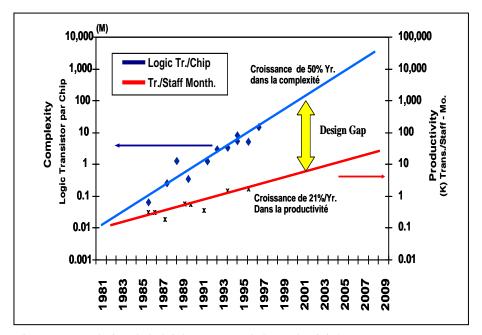

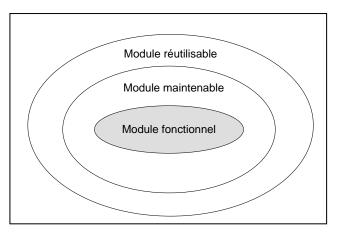

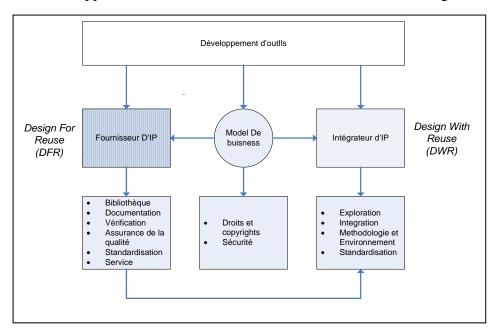

Le travail effectué dans le cadre de cette thèse se rapporte à la conception d'une plateforme pour l'implémentation hardware des réseaux de neurones sur FPGA, plus particulièrement l'algorithme de la rétro propagation du gradient (RPG). Les réseaux de neurones étant au cœur de notre sujet, nous avons consacré le premier chapitre à une présentation générale des réseaux de neurones, en particulier le preceptron multicouche basé sur l'algorithme RPG. Dans le deuxième chapitre, nous avons effectué une étude sur l'état de l'art concernant l'implémentation hardware des réseaux de neurones. Ce qui nous a conduits à proposer une nouvelle approche de classification du hardware neuronal allant des circuits standards jusqu'aux circuits et systèmes sur puce. Dans le chapitre III, nous avons effectué une étude des différents aspects liés à l'implémentation hardware de l'algorithme RPG sur FPGA, à savoir, l'apprentissage, le degré de parallélisme, le choix du langage de description matérielle ainsi que l'évaluation des performances de l'architecture proposée. Nous avons consacré une attention particulière quand à l'influence du choix du multiplieur sur les performances du réseau de neurones ; en terme de surface et de temps d'exécution. Aussi, dans ce chapitre, nous avons pris en considération les aspects liés au choix de la famille des circuits FPGAs et le problème lié à la densité d'intégration. Dans le chapitre IV, nous avons appliqué la reconfiguration dynamique à l'algorithme RPG. Pour cela, nous avons effectué une étude comparative des trois approches de reconfiguration dynamiques, à savoir la reconfiguration statique, la reconfiguration dynamique globale et la reconfiguration dynamique locale. Dans le chapitre V, nous avons proposé une nouvelle méthodologie pour l'implémentation hardware des réseaux de neurones, basée sur l'application du concept de réutilisation « design reuse ».La méthodologie proposée constitue l'épine dorsale pour la construction d'une plateforme permettant de regrouper l'ensemble des techniques et moyens liés à l'implémentation sur FPGA des réseaux de neurones.

Mots clés: Réseaux de neurones, Plateforme, rétropropagation du gradient, FPGA, reconfiguration dynamique, réutilisation, parallélisme

#### **Abstract**

The work presented in the context of this thesis concerns the design of a platform for the hardware implementation of neural networks into FPGAs, in particular the back propagation algorithm (RPG). Neural networks are at the heart of our subject, we have devoted the first chapter to an overview of neural networks, especially the multilayer perceptron based on the RPG algorithm. In the second chapter, we conducted a study on the state of the art on the hardware implementation of neural networks. This has led us to propose a new classification approach for neural hardware ranging from standard chips to embedded circuits and systems on chip. In Chapter III, we conducted a study of various aspects of hardware implementation of the RPG algorithm on FPGA, namely the learning procedure, the degree of parallelism, the choice of the hardware description language and the performance evaluation of the proposed architecture. We devoted a special attention regarding the influence of the multiplier type on the performance of the neural network; in terms of area and execution time. Also, in this chapter we have considered the aspects related to the choice of the FPGA family circuits and the problem related to the integration density. In Chapter IV, we applied the dynamic reconfiguration algorithm to the RPG algorithm. For this, we performed a comparative study of three approaches, namely the static reconfiguration, the global dynamic reconfiguration and the local dynamic reconfiguration. In Chapter V, we have proposed a new methodology for hardware implementation of neural networks, based on the application of the design reuse concept. The proposed methodology is the backbone for the construction of a platform to bring the set of all the techniques and capabilities associated with the implementation of neural networks into FPGAs.

**Keywords:** Neural Networks, Platform, backpropagation, FPGA, dynamic reconfiguration, design reuse, parallelism

## **AVANT PROPOS**

Le travail présenté dans cette thèse de Doctorat, préparée à l'Ecole Nationale Polytechnique d'Alger (ENP), a été effectué au sein de la Division Microélectronique et Nanotechnologies (DMN) du Centre de Développement des Technologies Avancées (CDTA), en collaboration avec le département Computer Engineering de la Queen's University of Belfast (UK), à la faveur d'une bourse de finalisation de thèse de doctorat accordée par le Ministère de l'Enseignement Supérieur et de la Recherche Scientifique (MESRS) et entrant dans le cadre du programme national exceptionnel de formation à l'étranger (PNE).

# Dédicaces

A la mémoire de ma mère, que dieu l'accueille dans son vaste paradis

A mon père, pour l'éducation qu'il ma donné et ses sacrifices tout au long de la vie

A tous ceux qui me sont chers

Je dédie le fruit de ce modeste travail

#### **REMERCIEMENTS**

Tout d'abord, je tiens à remercier Madame MHANIA GHERTI d'avoir accepté la présidence de mon jury de thèse, ainsi que Madame RACHIDA TOUHAMI, Messieurs RIAD BABA ALI et CHERIF LARBES qui m'ont fait l'honneur de faire partie de mon jury de thèse.

Je remercie tout particulièrement Monsieur AHCENE FARAH de m'avoir encadré durant cette thèse de doctorat, ainsi que mes coencadreurs, en Algérie, Monsieur HAMID BESSALAH et à l'étranger, Monsieur AHMED BOURIDENE. Je les remercie tous, pour leur aide, leurs précieux conseils, leur disponibilité ainsi que les grandes valeurs humaines que j'ai trouvé en eux.

Je tiens à remercier tous mes collègues de travail pour leur soutien moral.

J'adresse aussi mes remerciements à ma famille pour sa patience et ses encouragements à finaliser ce travail.

# **SOMMAIRE**

SOMMAIRE LISTE DES FIGURES LISTE DES TABLEAUX ABREVIATIONS

| INTRODUCTION GENERALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| CHAPITRE I LES RESEAUX DE NEURONES : PRINCIPES ET DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| I.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5   |

| I.2 Historique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

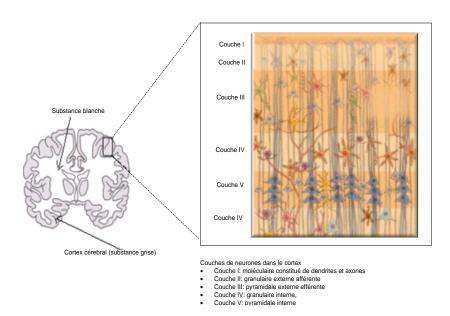

| I.3 Fondements biologiques des réseaux de neurones artificiels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

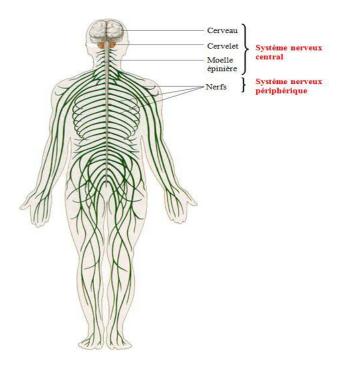

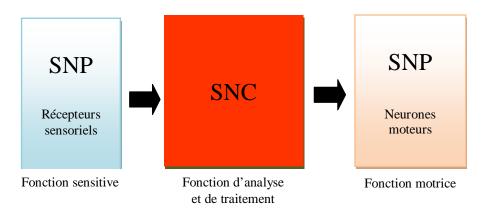

| I.3.1 Le système nerveux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7   |

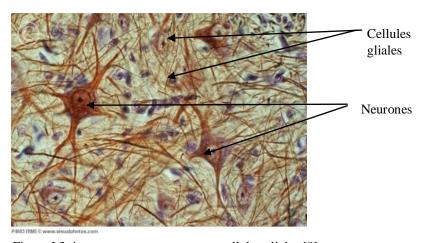

| I.3.2 Physiologie du neurone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

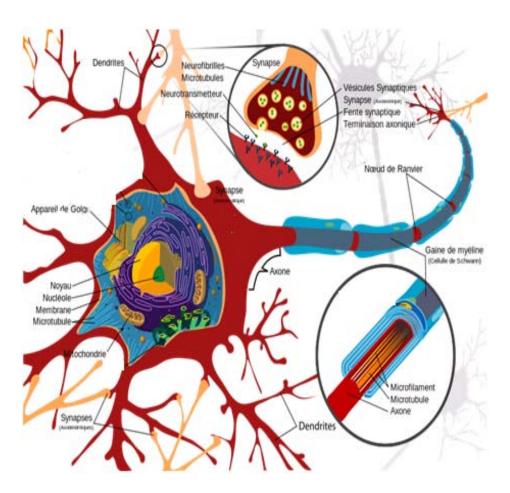

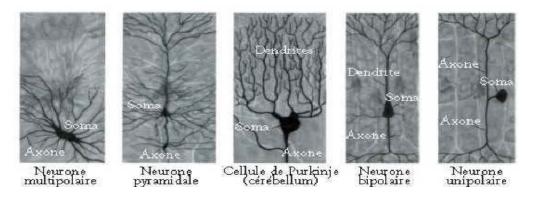

| I.3.2.1 Description du neurone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8   |

| I.3.2.2 Caractéristiques des neurones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10  |

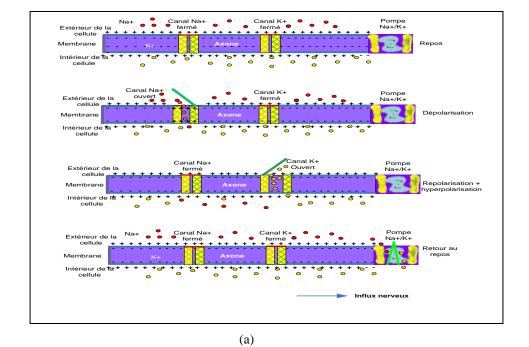

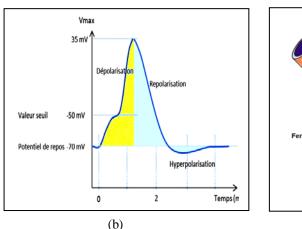

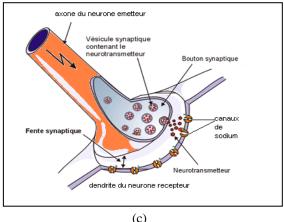

| I.3.2.3 Fonctionnement du neurone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

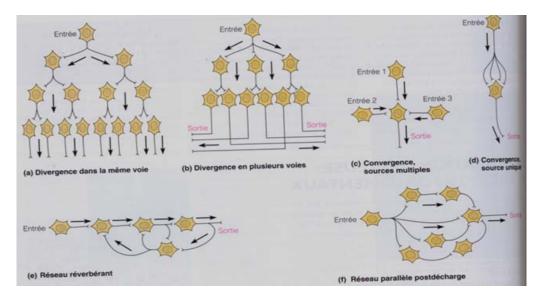

| I.3.3 Organisation des neurones dans le système nerveux central                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| I.4 Réseaux de neurones artificiels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

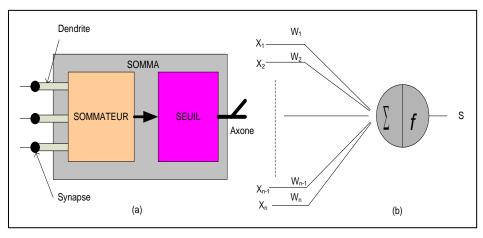

| I.4.1 Le neurone artificiel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

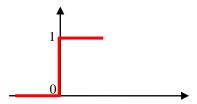

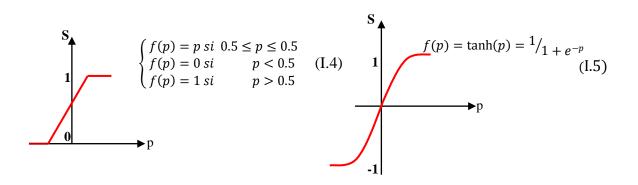

| 1.4.1.1 Première génération : les modèles du neurone à fonction échelon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 1.4.1.2 Seconde génération : Le neurone à fonction d'activation continue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

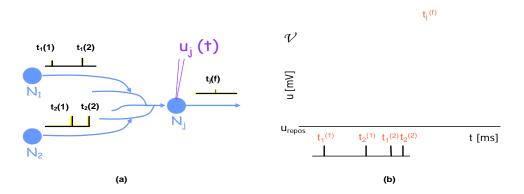

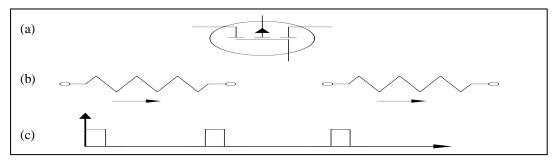

| 1.4.1.3 Troisième génération : Le neurone impulsionnel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| I.4.2 Construction des réseaux de neurones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

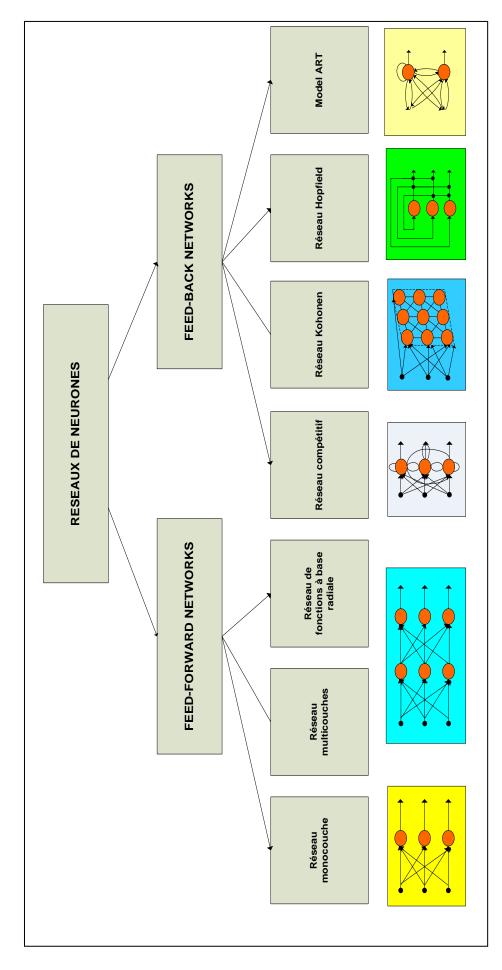

| I.4.2.1 Architecture des réseaux de neurones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| I.4.2.2 Apprentissage des réseaux de neurones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

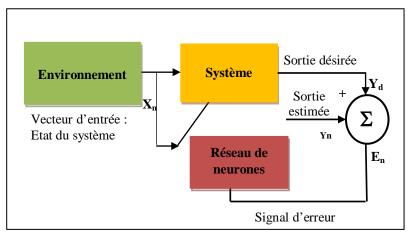

| I.4.2.2.1 Apprentissage supervisé                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

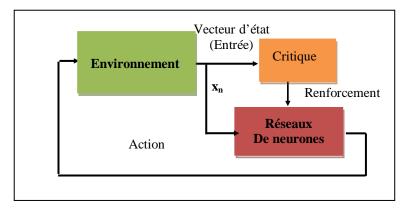

| I.4.2.2.2 Apprentissage renforcé                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| I.4.2.2.3 Apprentissage non supervisé                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| I.5 Les règle d'apprentissage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| I.5.1. La règle de Hebb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| I.5.2 La règle d'apprentissage du Perceptron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| I.5.3 La règle de Widrow-Hoff ou règle delta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| I.5.4 La règle delta généralisé                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22  |

| I.6 Le perceptron multicouches et l'algorithme de la rétropropagation du gradient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22  |

| I.7 Propriété des réseaux de neurones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26  |

| I.8 Domaines d'applications des réseaux de neurones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26  |

| I.9 Conclusion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27  |

| CHAPITRE II APERCU SUR L'IMPLEMENTATION HARDWARE DES RESE<br>DE NEURONES : ETAT DE L'ART ET PERSPECTIVES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AUX |

| II. 1 Introduction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26  |

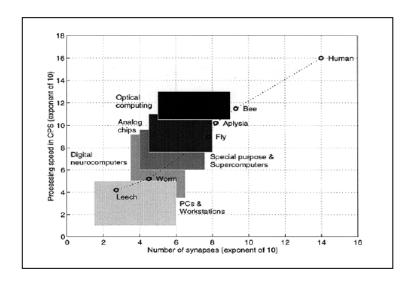

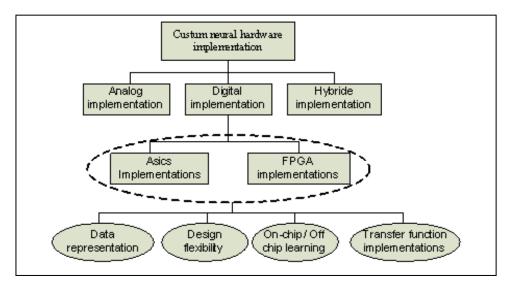

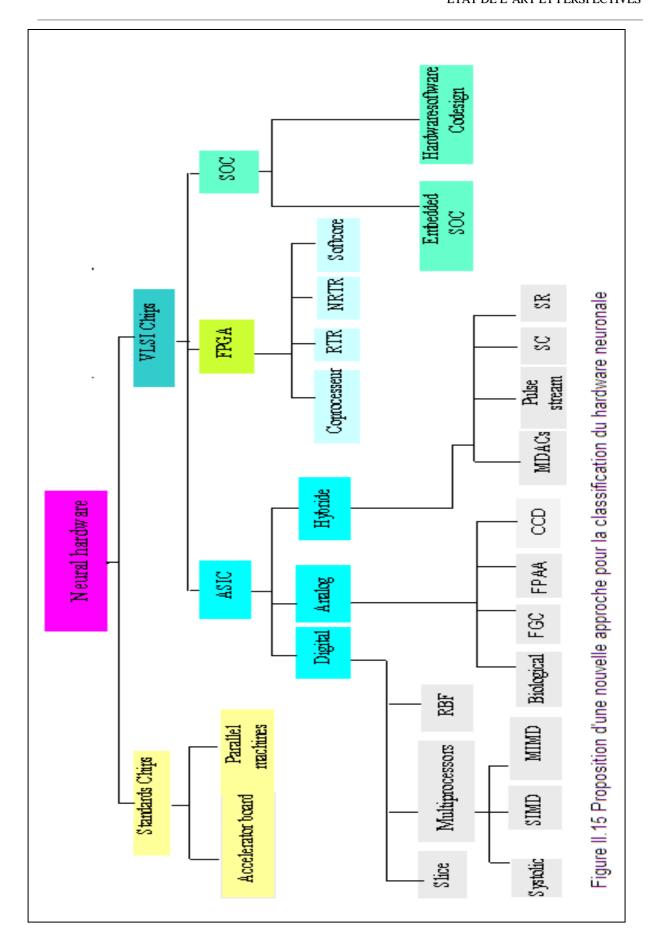

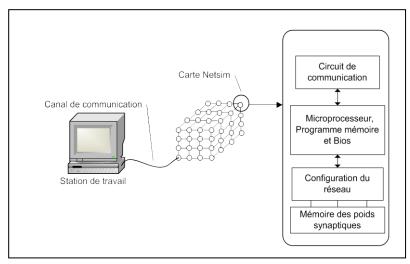

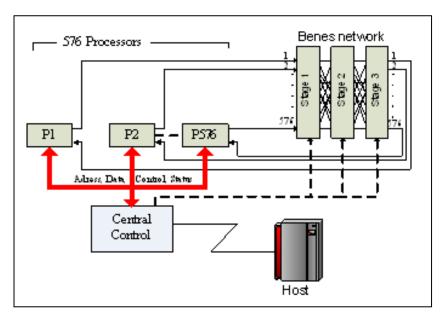

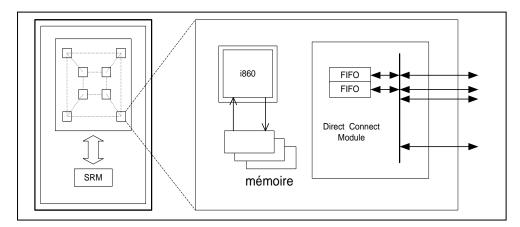

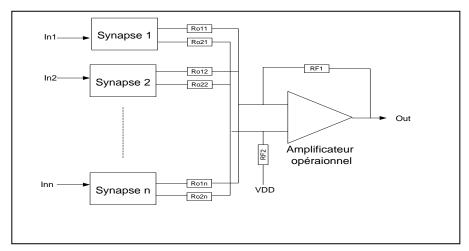

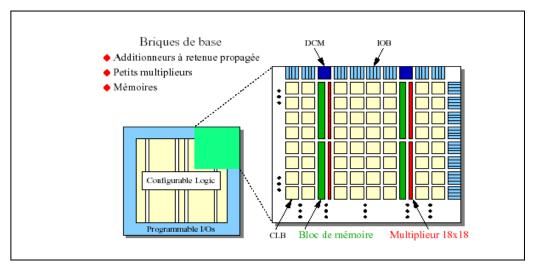

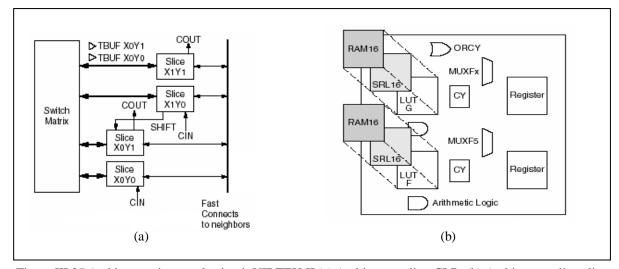

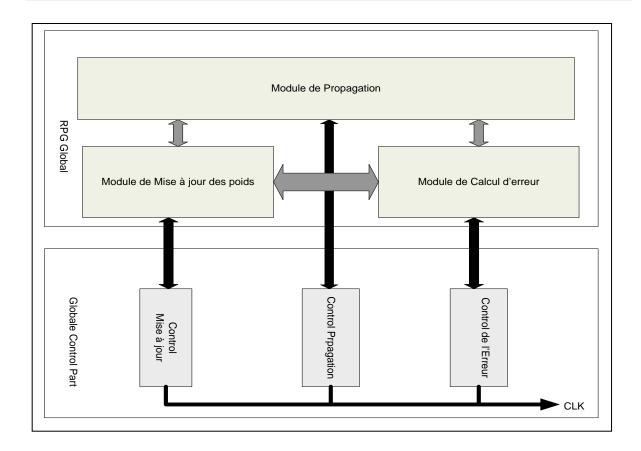

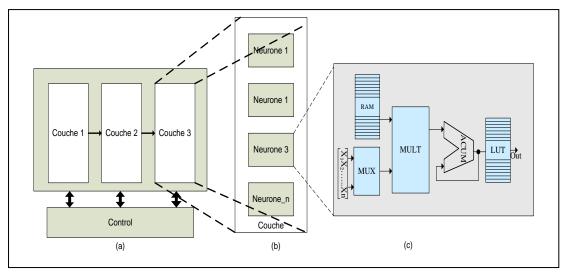

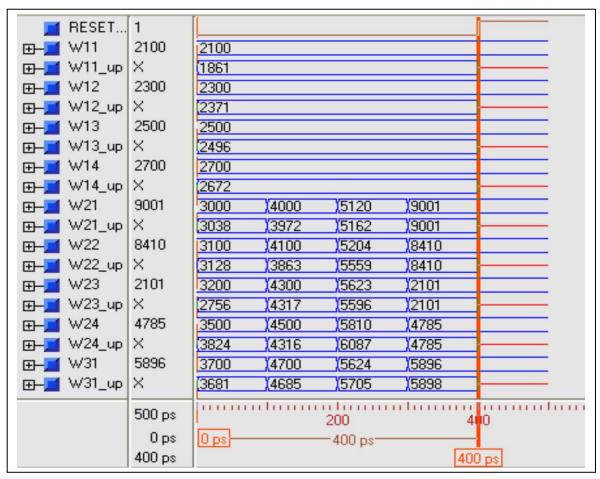

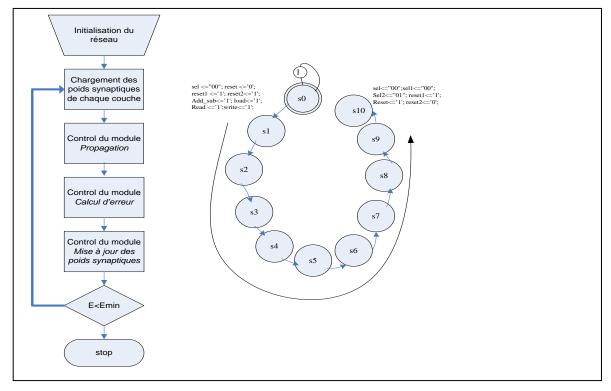

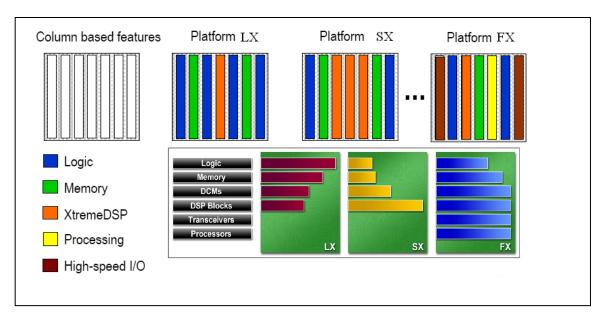

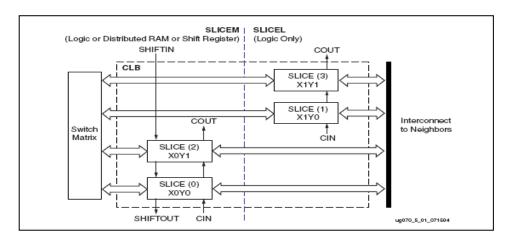

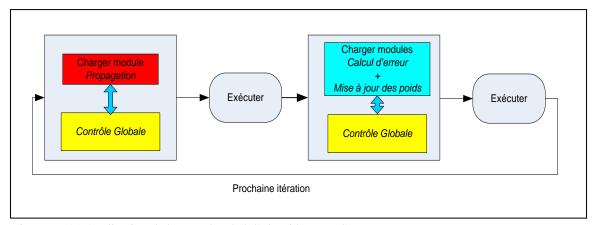

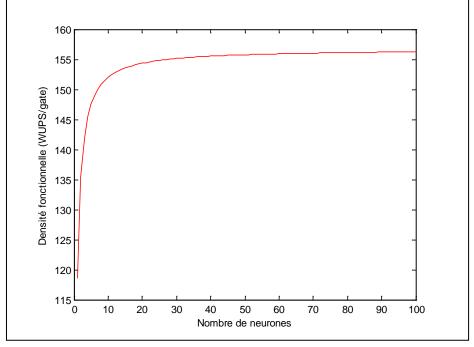

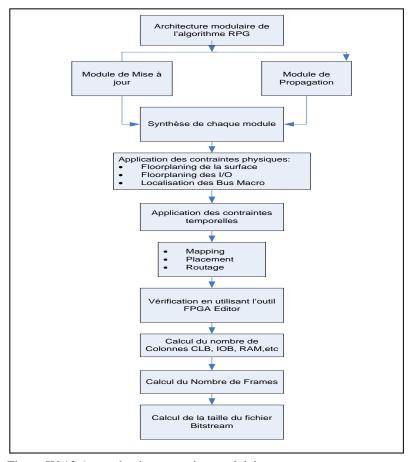

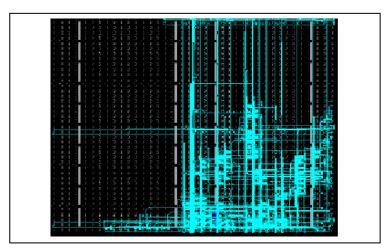

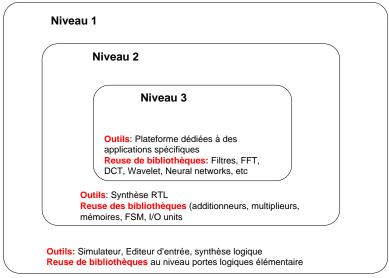

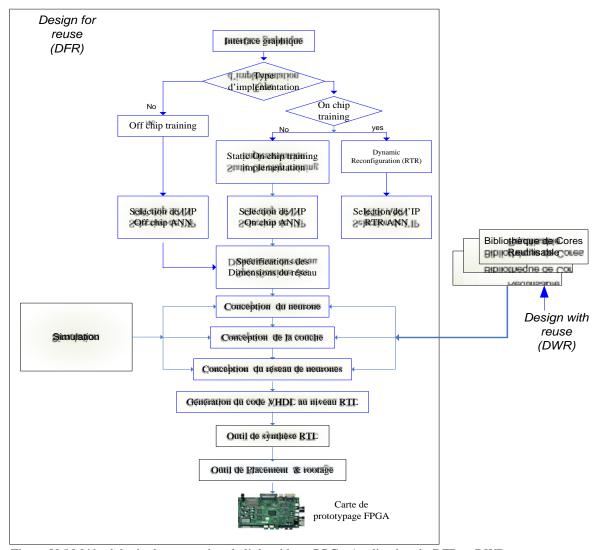

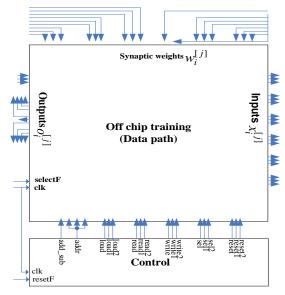

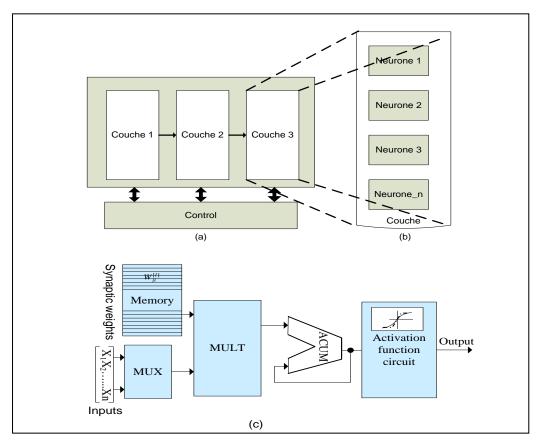

| II.2 Architecture hardware de base des réseaux de neurones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |