République Algérienne Démocratique et Populaire

Ministère de l'enseignement Supérieur et de la Recherche Scientifique

D.E.R de Génie Electrique et Informatique Filière : Electronique

Projet de fin d'études pour l'obtention du diplôme

D'INGENIEUR D'ETAT EN ELECTRONIQUE

Thème\_

# CONCEPTION ET REALISATION D'UNE CARTE D'ESSAI APPLIQUEE A LA DIDACTIQUE D'ELECTRONIQUE

Proposé et Dirigé par : A . BENBELKACEM Etudié par : AHMID Tahar BOUSNADJI Salem

Promotion

Octobre 1997

M

E.N.P. 10, AVENUE HASSEN BADI - EL-HARRACH - ALGER

#### République Algérienne Démocratique et Populaire

Ministère de l'enseignement Supérieur et de la Recherche Scientifique

#### Ecole Nationale Polytechnique

D.E.R de Génie Electrique et Informatique Filière : Electronique

Projet de fin d'études pour l'obtention du diplôme D'INGENIEUR D'ETAT EN ELECTRONIQUE

## CONCEPTION ET REALISATION D'UNE CARTE D'ESSAI APPLIQUEE A LA DIDACTIQUE D'ELECTRONIQUE

Proposé et Dirigé par : A . BENBELKACEM Etudié par : AHMID Tahar BOUSNADJI Salem

Promotion

Octobre 1997

W.

E.N.P. 10, AVENUE HASSEN BADI - EL-HARRACH - ALGER

#### **DEDICACES**

المدرسة الوطنية المتعددة التقنيبات المكتبسة — DIBLIOTHEQUE المكتبسة — Ecclo Cationale Polytechniquo

#### Je dédie ce travail à:

- Ma mère ZINEB, en témoignage de mon amour et de mon affection, et pour toute la patience qu'elle m'a fait preuve pendant les moments difficiles.

- A mon père HAMED, pour tous ses sacrifices consentis a mon égard.

- A mes frères: HOCINE, SMAIL, ABD EL KADER.

A mes soeurs: SAKINA, MABROUKA, FATMA, ALDJIA, SOUMIA

Pour tous les encouragements qu'ils m'ont prodigué.

- · A tous mes cousins.

- A tous mes amis en particulier: ABD EL KADER, DIDO et FARID.

#### TAHAR

#### Je dédie ce mémoire à:

- Ma mère, pour mon amour et ma reconnaissance, pour tous les sacrifices qu'elle a toujours su affronter durant les moments difficiles et pour tous les conseils et les encouragemements qu'elle m'a prodigué durant ma scolarité.

- Mon père, en témoignage de mon affection et de ma reconnaissance, et pour tous ses sacrifices consentis pour ma scolarité.

- Ma soeur, pour mon affection et ma reconnaissance.

- Tous mes cousins.

- tous mes amis.

SALEM

#### **REMERCIEMENTS**

المدرسة الوطنية التعددة التقنيبات المكسسية — BIBLIOTHEQUE المكسسية — Ecolo Nationale Polytechnique

Nos plus vifs remerciements s'adressent à Monsieur A BENBELKACEM notre promoteur, chargé de cours à l'ENS de Kouba, qui nous a dirigé tout le long de ce travail, pour son soutient permanent et pour les précieux conseils qu'il nous a prodigué.

Nous tenons àussi à remercier Messieurs K. CHEGROUN, A. MERAGHNI et D.KENDIL chargés de cours à l'ENS pour l'aide qu'ils ont bien voulu nous apporter et pour leur aide documentaire,

SAID, du département d'informatique de l'ENS, pour toute l'aide qu'il nous a apporter et tous les services qu'il nous a rendu.

Et toute l'équipe du laboratoire de Physique de l'ENS pour leur soutien permanent, en particulier à RACHID.

Que tous les professeurs qui ont contribué à notre formation, veuillent bien trouver içi, l'expression de nos vifs remerçiements.

المدرسة الوطنية المتعددة التقنيبات المكتبة — BIBLIOTHEQUE المكتبة — Scole Hationale Polytechnique

## RESUME

المدرسة الوطنية المتددة التقنيبات IBLIOTHEQUE المكتبة Ecolo Nationale Polytechnique

خلاصنا

تشهد كل مجالات التكنلوجيا و الصناعة في عصرنا هذا تطور انتيجة لظهور و تطور إستعمال وسيلة الإعالم الآلي.

إنه من الضروري إدخال هنه الاخيرة في سيران الأعمال النطبيقيــة الإلكترونية. وذلك لجعلها مرنــة و فعالة وفي هذا الإطار يكمن مشروعنا.

إن مشروعنا يهدف إلى تصميم لوحمة تجارب للأعمال التطبيقية الألكترونية الخاصة بالطور الأول الجامعي مسيرة بالحاسوب لكي تسمح بتصحيح الأخطاء التوصيلية و التركيبية للطالب, و كذلك بتوليد وقياس مختلف الإشارات اللازمة لسيران الأعمال التطبيقية وذلك كله دون التدخل المستمر للاستاذ.

#### **RESUME**

Tous les domaines technologiques et industriels ont connu un essor considérable depuis l'avènement de l'outil informatique, il est donc très avantageux d'intégrer ce dernier dans les travaux pratiques d'électronique afin d'assouplir leur déroulement et d'augmenter leur rendement. C'est dans ce cadre que se situe notre projet.

Notre projet consiste à élaborer une carte d'essai assistée par ordinateur pour les travaux pratiques d'éléctronique de premier cycle universitaire.

Cette carte permettra de corriger les fautes de câblage et de montage de l'étudiant, elle permettra également de générer et de mesurer divers signaux nécessaires au déroulement des travaux pratiques, et ceci sans l'intervention d'un assistant.

#### **ABSTRACT**

All technological and industrial domains have known a big developpement since the appear of computer science tool. Therefore, it's useful to add it in the electronic practice work to increase the performance of the electronic teaching loboratory, and our project goes this way.

Our project consist of the design of a computer aided test card for the electronic practice work of the first university cycle.

This card will allow the student to correct the connexions and montage errors and also to generate and measure various signals which are necessary in the experimental laboratories, without any human help.

المدرسة الوطنية المتعددة التغنيات المكتبة — BIBLIOTHEQUE Cole Nationale Polytechnique

#### **SOMMAIRE**

1

| INTRODUCTION GENERALE                                                  | 1  |

|------------------------------------------------------------------------|----|

| CHAPITRE I: LA CARTE D'ESSAI:                                          |    |

| I. INTRODUCTION                                                        |    |

| II. ETUDE DE LA CARTE D'ESSAI                                          |    |

| II . 1 . DEFINITION DU NOMBRE DE NOEUDS                                |    |

| II . 2 . DISPOSITION NOEUDS - NOEUDS ET NOEUDS - TROUS                 | 6  |

| II.3. CONFIGURATION ET EMPLACEMENT DES COMPOSANTS                      | 10 |

| II.3.1. CONFIGURATION DES COMPOSANTS SIMPLES                           | 10 |

| II.3.2. CONFIGURATION DES CIRCUITS INTEGRES                            | 14 |

| CHAPITRE II: CONCEPTION DES CIRCUITS D'INTERFACE:                      |    |

| I. MODE DE TRANSFERT DES DONNEES                                       | 19 |

| I.1. ACQUISITION DES DONNEES EN TEMPS REEL.                            | 19 |

| I.2. MODE DIFFERE                                                      |    |

| 1.3. CHOIX DU MODE DE TRANSFERT DE DONNEES.                            |    |

| II. CARTE DE DECODAGE DES ADRESSES                                     |    |

| IV. CARTE DE TEST.                                                     |    |

| IV.1. METHODES DE DETECTION                                            |    |

| IV . 2 . CONCLUSION                                                    |    |

| V. CARTES DE CONVERSION                                                |    |

| V.1. CARTE DE CONVERSION NUMERIQUE - ANALOGIQUE                        |    |

| V.2. CARTE DE CONVERSION ANALOGIQUE - NUMERIQUE                        |    |

|                                                                        | •  |

| Chapitre III: LOGICIEL D'APPLICATION:  I. LOGICIEL DE TEST DES DONNEES |    |

|                                                                        | 47 |

| I. 1. ALGORITHME DE DETECTION  DE L'EMPLACEMENT DES CONTACTS           | 45 |

| I. 2. ALGORITHME DE DETECTION                                          | 4, |

| DU SENS DE PLACEMENT DES COMPOSANTS                                    | 16 |

| II . ALGORITHME DE GESTION                                             |    |

| DE LA CARTE A CONVERTISSEUR ANALOGIQUE NUMERIQUE                       | 57 |

| III . ALGORITHME DE GESTION                                            | 3, |

| DE LA CARTE A CONVERTISSEUR NUMERIQUE - ANALOGIQUE                     | 58 |

|                                                                        |    |

| CONCLUSION GENERALE                                                    | 61 |

| ANNEXE 1                                                               | 63 |

|                                                                        |    |

| A BIRLENKIN G                                                          |    |

المدرسة الوطنية المتعددة التقنيسات المكسسية --- BIBLIOTHEQUE المكسسية المكسسية المكسسية المكافقة المحافظة المحافظة المعافقة المع

## **INTRODUCTION**

**GENERALE**

#### **INTRODUCTION GENERALE**

Il n'est plus à démontrer que le monde de la technologie moderne est devenu synonyme d'informatique.

De la télécommunication au traitement d'image, et commande numérique, l'informatique est désormais l'outil indispensable pour tout travail rapide et fiable.

Il s'en est ainsi déclenché une multitude d'innovations, pour augmenter et élargir l'utilisation du micro-ordinateur qui a lui même évolué d'une façon assez rapide.

L'évolution de cet outil informatique a ainsi permis son implantation progressive dans pratiquement tous les domaines technologiques et industriels, ce qui a eu pour conséquence de restreindre la présence humaine dans ces derniers.

Afin de remplir son objectif , l'enseignement de l'électricité , en particulier de l'électronique dépend surtout de l'expérimentation . Sans l'expérimentation , l'électronique n'aurait jamais atteint de tels progrès .

La connaissance que l'étudiant acquiert par des moyens théoriques est à son tour utilisée pour faire des expériences afin de tester les lois et les modèles et afin de mettre en évidence les différences existantes entre le côté théorique et le côté pratique des phénomènes observés.

L'intégration de l'outil informatique dans les travaux pratiques offre une grande souplesse dans leur déroulement, elle facilite grandement le travail de l'étudiant au cours de sa manipulation.

Notre projet consiste à élaborer une carte d'essai assistée par ordinateur pour les travaux pratiques d'électronique.

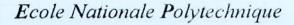

Cette réalisation est constituée de trois blocs essentiels:

- 1. La carte d'essai : contient les trous d'enfichage et est munie de deux niveaux de contact (détection, mesure).

- 2. La carte d'interface : ayant pour fonction la liaison entre la carte d'essai et l'unité de traitement.

3. L'unité de traitement : gère toutes les opérations d'acquisition et de traitement de données.

#### Ce mémoire compte 03 chapitres :

- Le premier chapitre donne une présentation de la carte d'essai et de la configuration des composants enfichables.

- Le deuxième chapitre traite de la conception des divers cartes d'interface.

- Le troisième chapitre consiste en la description du logiciel d'application .

- En conclusion, nous présenterons les résultats obtenus et les perspectives de développement pour l'amélioration de notre réalisation.

## **CHAPITRE I:**

## LA CARTE D'ESSAI

#### Chapitre I: LA CARTE D' ESSAI

#### **I.INTRODUCTION:**

Généralement, Les travaux pratiques classiques se déroulent comme suit :

- 1. L'étudiant reçoit tout d'abord un polycopié des manipulations constitué de deux parties :

- Une partie théorique permettant la compréhension de l'aspect théorique de la manipulation.

- Une partie réalisation contenant les instructions que l'étudiant devra suivre pendant la séance de travaux pratiques.

- 2. Durant la séance de travaux pratiques, l'étudiant aura à réaliser un montage suivant les instructions du polycopié.

- 3. Enfin , il sera demandé à l'étudiant de relever des mesures , de tracer des graphes et d'interpréter les résultats obtenus .

- 4. L'étudiant présente à chaque fin de manipulation un rapport écrit de la manipulation.

Pendant la séance de travaux pratiques, l'assistant aura pour rôle d'assister l'étudiant dans sa manipulation en :

- -Vérifiant le montage réalisé par l'étudiant.

- -Contrôlant les mesures faites par l'étudiant.

- -répondant éventuellement aux questions posées par les étudiants .

Les travaux pratiques classiques ont essentiellement pour objectif de développer chez l'étudiant l'aspect de maîtrise de :

- \* câblage et montage de circuits électroniques.

- \*mesure.

### <u>DEROULEMENT DES TRAVAUX PRATIQUES ASSISTES PAR</u> <u>ORDINATEUR:</u>

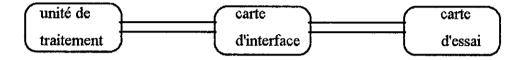

Le laboratoire de travaux pratiques comprendra un certain nombre de tables de manipulation contenant chacune un ordinateur PC auquel sera connectée une carte d'essai.

Ces ordinateurs fonctionneront comme des "esclaves" et seront pilotés par un ordinateur PC "maître". (voir figure I.1).

La carte d'essai et l'ordinateur PC seront les outils de travail de l'étudiant.

- La carte d'essai permettra à l'étudiant d'enficher des composants afin de réaliser son montage.

- L'ordinateur aura pour fonction de tester le câblage de l'étudiant, il détectera ainsi les fautes de câblage de l'étudiant, et permettra ainsi :

- \*La visualisation des éventuelles différences existantes entre le circuit que l'étudiant vient de réaliser et le circuit à réaliser.

- \*La visualisation des divers grandeurs électriques du circuit après correction de celui-ci.

#### **AVANTAGES:**

Contrairement aux travaux pratiques classiques, les travaux pratiques assistés par ordinateur présentent une très grande souplesse d'utilisation.

- 1) Elle permet à l'étudiant de travailler en collaboration avec l'ordinateur sans l'intervention directe d'un assistant.

- 2) Le travail de manipulation qui était demandé lors des séances de travaux pratiques classiques devient une opération élémentaire, celui-ci étant quasiment effectué par l'ordinateur d'où:

- Un gain de temps considérable pour le travail de câblage et de montage d'un circuit électronique.

- Une vérification et une correction rapide du montage.

- Mesures rapides.

FIG I . 1 . DISPOSITION DES TABLES DE MANIPULATION AU LABORATOIRE .

3) Pour les étudiants ayant acquis suffisamment de notions d'électronique, le travail de manipulation des travaux pratiques classiques deviendra plutôt un travail de conception.

On incitera l'étudiant à réaliser des montages répondant aux exigences d'un cahier de charges prédéfini, ce qui aura pour avantage de développer un aspect de recherche et de créativité chez l'étudiant.

4) tout travail fait par l'étudiant sera sauvegardé sous forme de fichier que l'assistant pourra aisément consulter pour juger du travail de l'étudiant, ce qui facilite la tâche de l'assistant lors de l'évaluation de l'étudiant.

#### II. ETUDE DE LA CARTE D'ESSAI:

#### II. 1. DEFINITION DU NOMBRE DE NOEUDS:

Ce sont les limites nombre de noeuds que doivent avoir les circuits électroniques réalisables.

- Avec deux noeuds on peut plaçer plusieurs dipôles, cependant un tel circuit ne permet pas de réaliser tous les montages électroniques de base.

- La limite supérieure du nombre de noeuds dépend des circuits utilisés.

#### II. 2. DISPOSITION NOEUDS-NOEUDS ET NOEUDS-TROUS:

Afin de permettre à l'utilisateur de reproduire facilement son circuit sur la carte d'essai, on normalise :

- la distance entre les trous de chaque noeuds.

- la distance entre les noeuds.

Les critères de normalisation sont les suivants :

- La valeur maximale des branches d'un noeud n'est pas fixe, elle dépend des circuits concernés.

- En prenant la valeur maximale comme nombre de trous d'un noeud, il y aurait beaucoup de fiches qui ne seraient pas utilisées (il est rare de trouver le noeud ayant un nombre de branches égal à cette valeur maximale).

#### Chapitre I LA CARTE D'ESSAI

• Puisque l'extension du nombre de trous se fait par multiplexage, et comme les multiplexeurs ont comme nombre de lignes d'entrées un exposant de deux, il serait préférable de prendre comme valeur du nombre de trous d'un noeud un exposant de deux.

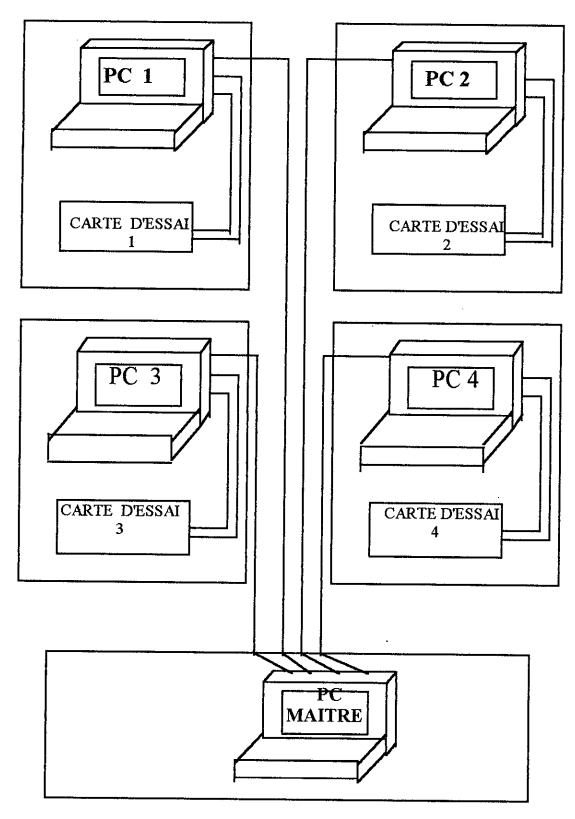

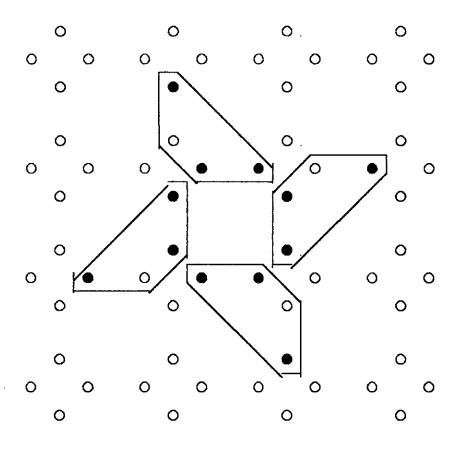

#### SOLUTIONS PROPOSEES: [1]

La combinaison des deux premiers critères nous amène à prendre six trous par noeuds, du fait qu'on a l'habitude de rencontrer des noeuds de six branches, et c'est la plus grande valeur pouvant se répéter. (voir figure I.2).

En ajoutant le troisième critère aux deux précédents, et en les combinant, on se voit être dirigés aux conditions suivantes :

- Le plus grand nombre de branches d'un noeud fréquemment utilisé.

- Un exposant de deux.

Compte tenu de ces conditions, on se voit dirigés vers des noeuds de quatres branches (Voir figure I.3).

Une précédente étude a été réalisée sur le choix du pixel de connection [1], le troisième choix a été retenu.

#### TYPE DE CONTACT:

Lorsque l'étudiant réalise un montage, il faut que le microprocesseur détecte les composants et leur sens de placement, ensuite fait la mesure. Donc c'est à travers le contact que le microprocesseur fait le test et la mesure. La carte d'essai possède alors deux niveaux de contact:

- 1. Niveau de test.

- 2. Niveau de mesure.

FIGI. 2. CONFIGURATION DES NOEUDS EN COMBINANT LES DEUX PREMIERS CRITERES.

A. troisième choix (orienté).

B. quatrième choix (non orienté).

FIGI. 3. CONFIGURATION DES NOEUDS EN AJOUTANT LE 3 IEME CRITERE AUX DEUX PRECEDENTS.

#### CHOIX DE LA FICHE DE CONTACT:

La fiche doit permettre l'isolation entre le circuit de détection et celui de mesure.

La fiche JACK STEREO comprend trois niveaux de contact, elle vérifie ainsi la condition précédente, de plus elle est disponible sur le marché national, nous choisirons donc ce type de fiche.

#### II. 3. CONFIGURATION ET EMPLACEMENT DES COMPOSANTS:

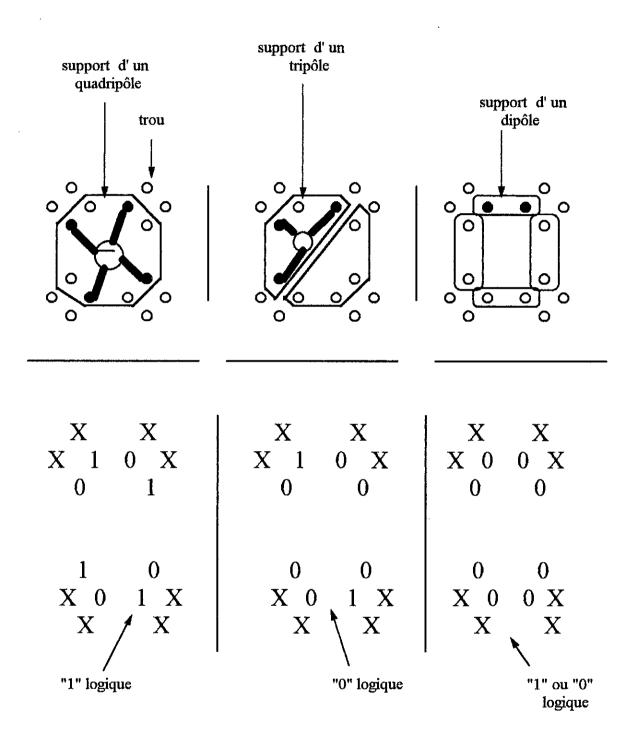

#### II.3.1. CONFIGURATION DES COMPOSANTS SIMPLES:

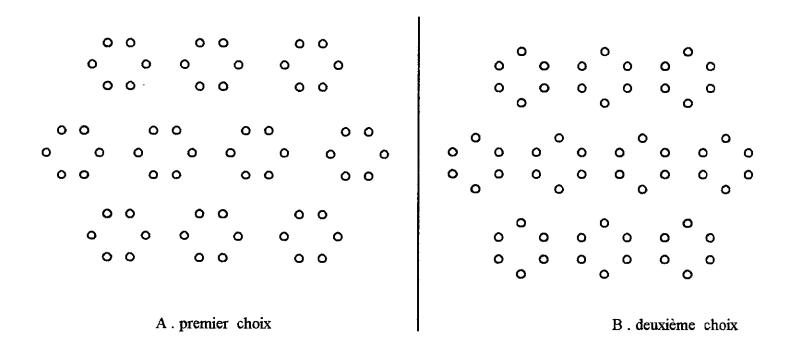

Plusieurs propositions de configurations des composants ont été envisagées, la proposition qui a été retenue, compte tenu des problèmes de redondance qu'elles présentent, est représentée en figure I . 4 [1].

#### **CRITIQUES:**

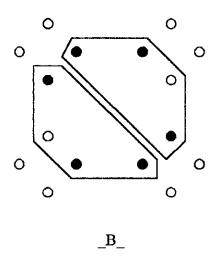

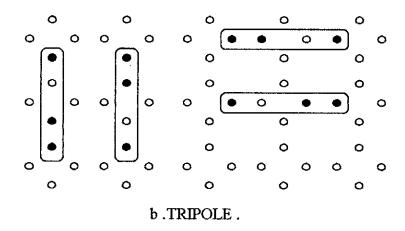

Lors de l'analyse du 3 ième choix nous avons rencontré un certain nombre d'ambiguïtés dans la discernement des différents composants, nous citons entre autres deux exemples (figure I . 5 ):

- Pour A: La figure représente 4 tripôles, les 8 bits au milieu sont à 1' état "0" et d'après la figure I. 4 ils seront considérés comme quatre dipôles en parallèles deux à deux.

- Pour B : d'après la figure I . 4 on risque de confondre les deux tripôles avec un quadripôle .

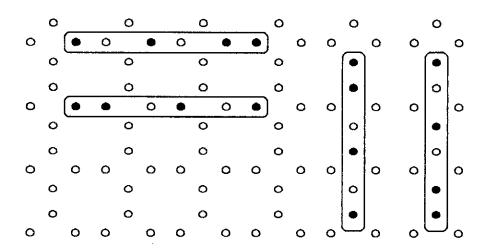

#### **PROPOSITION:**

Les éléments sont enfichés dans un seul sens, soit horizontalement, soit verticalement, les distances entre les broches des supports étant normalisées (figl.6).

#### **AVANTAGES:**

- Nous n'avons plus d'ambiguïtés dans le discernement des composants.

- Le programme devient plus simple : on exploite dans ce cas , une seule direction, soit horizontale , soit verticale pour détecter le type et l'emplacement de l'élément .

FIGI. 4. NORMALISATION DES COMPOSANTS DU TROISIEME CHOIX.

$_{\mathbf{A}}$

FIG I . 5 . EXEMPLES DE REDONDANCE DANS LE TROISIEME CHOIX

a. DIPOLE.

c . QUADRIPOLE

FIG I . 6 .PROPOSITION DE LA CONFIGURATION DES COMPOSANTS DE LA CARTE D'ESSAI .

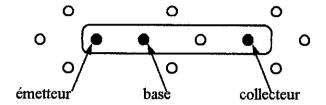

• Pour le cas du transistor, on peut facilement reconnaître la base, l'émetteur et le collecteur :

#### **INCONVENIENTS:**

• Nous perdons un trou pour les tripôles et deux trous pour les quadripôles.

#### **REMARQUE:**

Dans cette proposition les formes des tripôles et des quadripôles sont non conformes au modèle théorique (forme triangulaire pour les tripôles et rectangulaire pour les quadripôles), mais on peut y remédier en dissimulant les pattes des composants du à l'aide d'un support :

- Triangulaire pour les tripôles.

- Rectangulaire pour les quadripôles.

#### III. 3. 2. CONFIGURATION DES CIRCUITS INTEGRES:

Dans tout ce qui précède nous n'avons pas consideré le cas des circuits intégrés, qui, en réalité prennent une place importante dans les travaux pratiques d'électronique.

Le circuit intégré le plus simple comporte au minimum 8 pattes donc 8 trous au minimum doivent être enfichés, c'est ce type de circuits integrés auquel nous nous limiterons, ceux-ci étant essentiellement les plus utilisés au cours des séances de travaux pratiques.

Nous proposons 3 types de dispositions du circuit intégré:

- · Circuit intégré extérieur au montage.

- Circuit intégré extérieur au montage avec interrupteurs.

- Circuit intégré intérieur au montage.

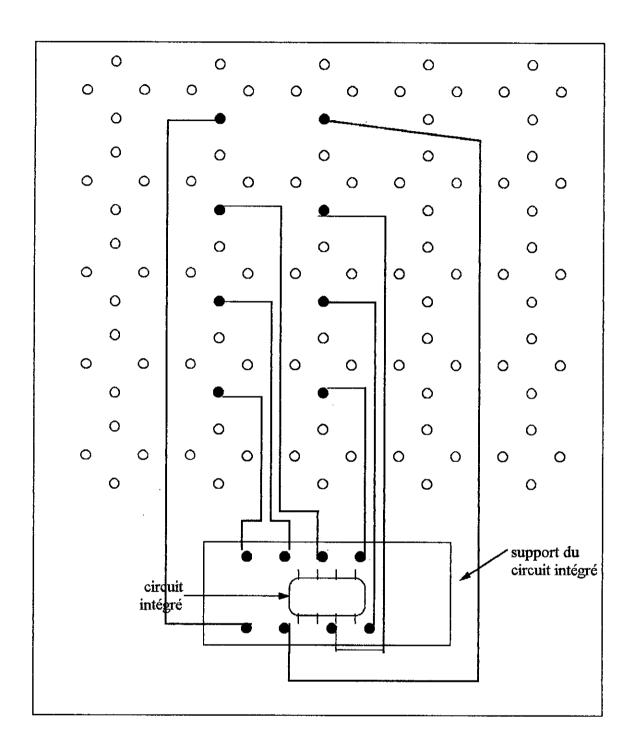

#### 1) CIRCUIT INTEGRE EXTERIEUR AU MONTAGE :

On fixe un support de circuit intégré hors du montage les divers broches du support seront reliées au montage à l'aide de fils que nous enficherons dans des trous de notre choix sur la carte d'essai (voir figure I . 7)

#### **AVANTAGES:**

- La circuiterie est simple.

- On économise le nombre de trous enfichés.

#### **INCONVENIENTS:**

- Elle encombre considérablement le montage par l'enchevêtrement des fils.

- Risque de confusion des endroits où les broches du circuit intégré sont enfichés.

- On doit utiliser un programme spécifique pour gérer les circuits intégrés.

#### 2) CIRCUIT INTEGRE EXTERIEUR AU MONTAGE AVEC INTERRUPTEURS :

On fixe, comme précédemment, un support de circuit intégré à l'extérieur du montage, mais cette fois, pour éviter l'encombrement dû aux fils, on relie ceux-ci aux trous de la carte sans qu'ils soient visibles (sous la carte d'essai).

Chaque fils sera muni d'un interrupteur et sera relié à 3 trous appartenant à 3 noeuds distincts.

Pour les trous que l'on désirera utiliser, les interrupteurs des fils qui y sont reliés seront fermés.

#### **AVANTAGES:**

- On évite l'enchevêtrement des fils.

- On économise le nombre de trous utilisés.

#### **INCONVENIENTS:**

- La circuiterie est complexe.

- Risque de confusion des endroits où les broches du circuit intégré sont enfichés.

- On doit utiliser un programme spécifique pour gérer les circuits intégrés.

FIGI. 7. CONFIGURATION DU CIRCUIT INTEGRE EXTERIEUR AU MONTAGE.

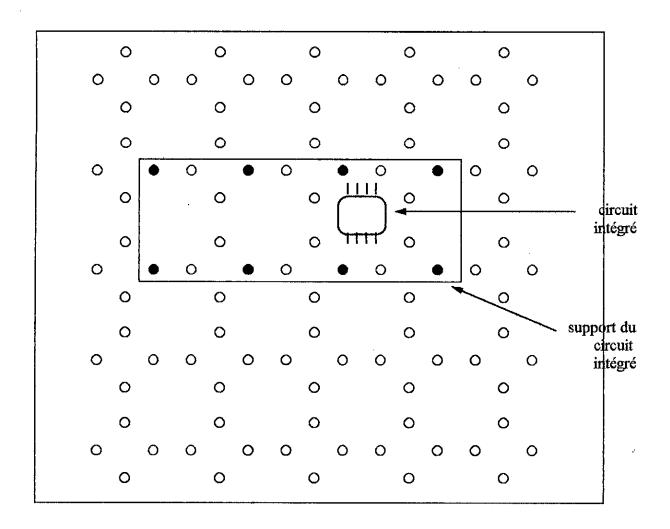

#### 3) CIRCUIT INTEGRE A L'INTERIEUR DU MONTAGE:

Le support dans ce cas n'est pas fixé, il pourra être placé et déplacé à volonté sur la carte d'essai.

Ce support possédera 8 broches dont les distances de l'une par rapport à l'autre est normalisée. (figure I. 8)

#### **AVANTAGES:**

- La circuiterie est simple.

- On n'utilise pas de programme spécifique pour gérer les circuits intégrés.

#### **INCONVENIENTS:**

• Perte de 12 trous.

En comparant les 3 types de configurations, le 3 ième nous parait le plus intéressant, compte tenu des avantages qu'il présente par rapport aux autres types.

FIG I . 8 .EMPLACEMENT DES CIRCUITS INTEGRES INTERIEUR AU MONTAGE.

## **CHAPITRE II:**

# CONCEPTION DES CIRCUITS D' INTERFACE

## CHAPITRE II: CONCEPTION DES CIRCUITS D'INTERFACE

#### I. MODE DE TRANSFERT DES DONNEES:

#### I.1. ACQUISITION DES DONNEES EN TEMPS REEL:

Afin de pouvoir lire des données en temps réel, le programme d'acquisition des données doit être en boucle fermée infinie permettant ainsi :

- La mémorisation de l'information concernant toutes les liaisons (bornes des composants enfichés).

- La correction des éventuels changements de position des composants sur la carte.

#### **AVANTAGES:**

- Au cas où les pattes sont enfichées en même temps le problème de redondance ne se pose pas, car le nombre de pattes enfichées déterminera le type de l'élément enfiché:

- \* 2 pattes enfichées : dipôle .

- \* 3 pattes enfichées : tripôle.

- \* 4 pattes enfichées : quadripôle.

- Nous n'avons pas de perte de trous dans ce cas (on adoptera des supports de composants de telle sorte à n'avoir aucune perte de trous).

#### **INCONVENIENTS:**

- Le déroulement du programme est lourd du fait qu'il y a exécution du programme à chaque boucle.

- Il est impossible d'enficher toutes les pattes d'un composant en même temps, on a donc toujours confusion lors de l'enfichage des composants.

#### **PROPOSITION:**

A chaque fois qu'on enfiche un composant on demande au microprocesseur de reconnaître le type et l'emplacement du composant sur la carte, le microprocesseur détecte alors les états de toutes les fiches et les mémorise.

Il compare ensuite ces données avec les données précédentes afin de détecter les changements réalisés, ces changements déterminerons le type et l'emplacement de l'élément enfiché.

#### <u>AVANTAGES:</u>

- On remédie au premier inconvénient précédent.

- Le programme devient moins lourd (le nombre de boucles est restreint)

- Le programme fonctionne en temps réel.

#### **INCONVENIENTS:**

- La routine est lourde (il y a éxécution du programme à chaque boucle).

- Il se pourrait qu'entre deux éléments enfichés, on oublie de demander au microprocesseur de détecter l'élément, nous aurons alors un dysfonctionnement du programme.

#### I.2. MODE DIFFERE:

Il faut que l'utilisateur ait terminé de réaliser son montage pour que le microprocesseur commence à détecter les composants et leur emplacement.

#### **AVANTAGES:**

- Il y a exécution du programme une seule fois.

- Du point de vue pédagogique, il permet à l'utilisateur d'enficher ses composants à n'importe quel noeud, sans se soucier de la détection jusqu' à ce qu'il termine la réalisation du montage.

L'acquisition des données se fait après avoir enfiché tous les composants, cela implique qu'il n'y a pas possibilité d'erreur au niveau des données.

#### **INCONVENIENTS:**

• On a un retard dû au fait que l'éxécution du programme d'acquisition se déroule après le câblage du circuit et non simultanément.

#### I.3. CHOIX DU MODE DE TRANSFERT DE DONNEES:

On adopte le mode différé pour la simplicité de son utilisation et pour éviter d'éventuelles erreurs au niveau des données.

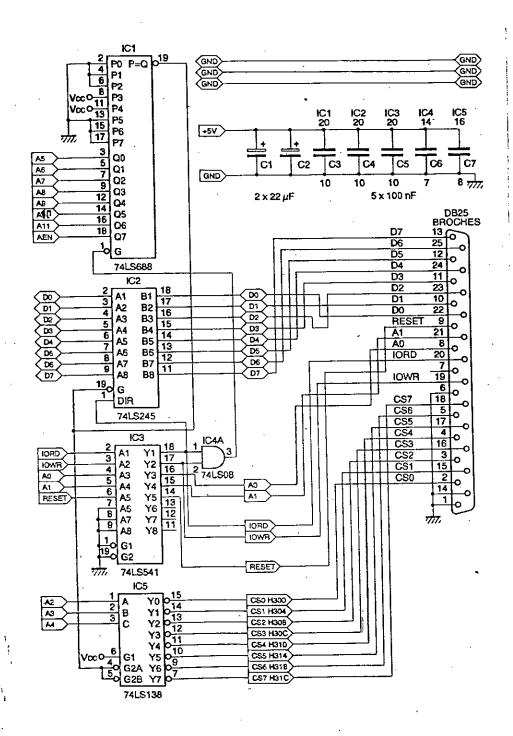

#### II. CARTE DE DECODAGE DES ADRESSES:

Cette carte est un circuit de liaison absolument nécessaire entre l'ordinateur et les cartes externes.

Le schéma de principe est donné en figure II.1.

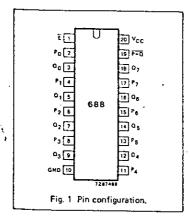

Le groupe des lignes A5 à A11, ainsi que la ligne AEN parviennent aux entrées Q d'un circuit intégré 74LS688, ce circuit est un comparateur.

Sur ses entrés P sont appliqués des niveaux logiques prédéterminés.

Le comparateur compare donc l'état de ses lignes d'entrée Q avec celui de ses entrées P, ainsi, lorsque les lignes d'adresses A5, A6, A7, A10 et A11 et la ligne AEN présentent un niveau bas et les lignes A8 et A9 présentent un niveau haut, sa sortie passe au niveau logique bas, indiquant aux circuits suivants que la carte prototype est adressée.

Cela se produit lorsque sur son entrée de validation G/ un niveau bas est appliqué soit par la ligne IOWR/ (écriture) soit par la ligne IORD/ (lecture).

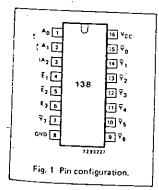

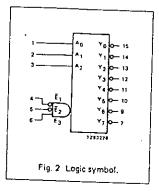

Cette sortie P=Q valide entre autre un circuit décodeur - démultiplexeur 3 vers 8 par ses entrées de validation G2A et G2B : en effet, ses trois entrées A, B et C sont connectées aux lignes d'adresses A2, A3 et A4.

Ainsi lorsque le comparateur signale l'adressage, A2, A3 et A4 peuvent présenter des niveaux différents et partagent ainsi le domaine des cartes prototypes en huit parties.

Les lignes A0 et A1 restent disponibles et seront employées par certaines des cartes externes.

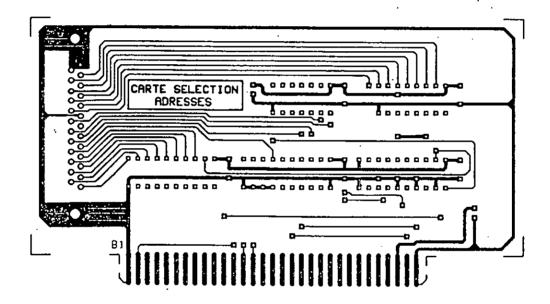

FIG II.1, SCHEMA DE LA CARTE DE DECODAGE DES ADRESSES.

La sortie du comparateur IC1 valide également le circuit IC2 , qui est un 74LS245 , utilisé comme tampon de bus bidirectionnel .

Lorsqu'il est validé par son entrée G/ et que son entrée DIR est maintenue au niveau haut, le bus de données (D0 à D7) transmet ses informations du microprocesseur vers l'extérieur.

Lorsqu' au contraire, son entrée DIR est soumise à un niveau bas, les informations transitent de l'extérieur vers le microprocesseur.

La broche DIR est donc connectée à la ligne IORD/ qui se charge de présenter automatiquement ces niveaux lors d'une écriture ou d'une lecture.

Le circuit IC3 est un amplificateur de type 74LS541.

Il est chargé d'isoler les lignes provenant du bus de l'ordinateur des cartes qui utiliseront ces lignes. Nous ne sommes en effet jamais à l'abri d'une fausse manoeuvre, et la présence de ce circuit est une très bonne sécurité pour le micro-ordinateur. Il fait transiter les lignes A0 et A1, IORD/ et IOWR/, et la ligne RESET.

Tous les circuits intégrés ont leurs ligne d'alimentation positive découplée par un condensateur de 100nF. De plus , deux condensateurs de  $22~\mu F$  filtrent la tension de +5V prélevée sur le bus du PC .

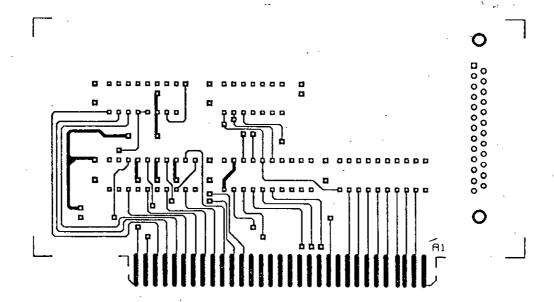

Cette carte est obligatoirement réalisée en circuit double face puisqu'elle est déstinée à être insérée dans l'un des slots libres de l'ordinateur.

Le dessin du circuit imprimé côté composants est donné en figure II. 2 (a), celui de la face côté soudures est donné en figure II. 2 (b).

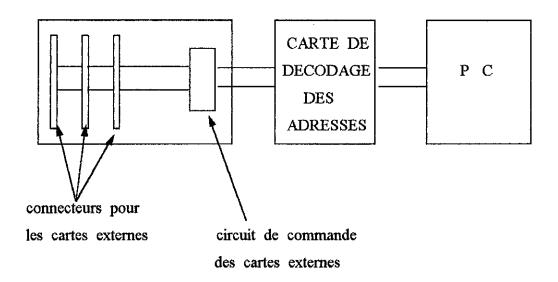

#### III. LA CARTE DE BASE: fig(II.3)

Le rôle de cette carte est de :

- 1. Assurer tout d'abord le décodage des adresses de chaque carte de conversion.

- 2. Distribuer les signaux et les lignes provenant de l'ordinateur à chaque carte externe assurant ainsi la circulation bidirectionnelle des données.

FIG II. 2 (a). CIRCUIT IMPRIME DE LA CARTE DE DECODAGE D'ADRESSES COTE COMPOSANTS.

FIG II . 2 (b). CIRCUIT IMPRIME DE LA CARTE DE DECODAGE D'ADRESSES COTE SOUDURES.

3. Assurer l'alimentation électrique de ces cartes et leur positionnement à l'aide de slots.

FIG II.3. Configuration de la carte de base.

#### FONCTIONNEMENT DE LA CARTE:

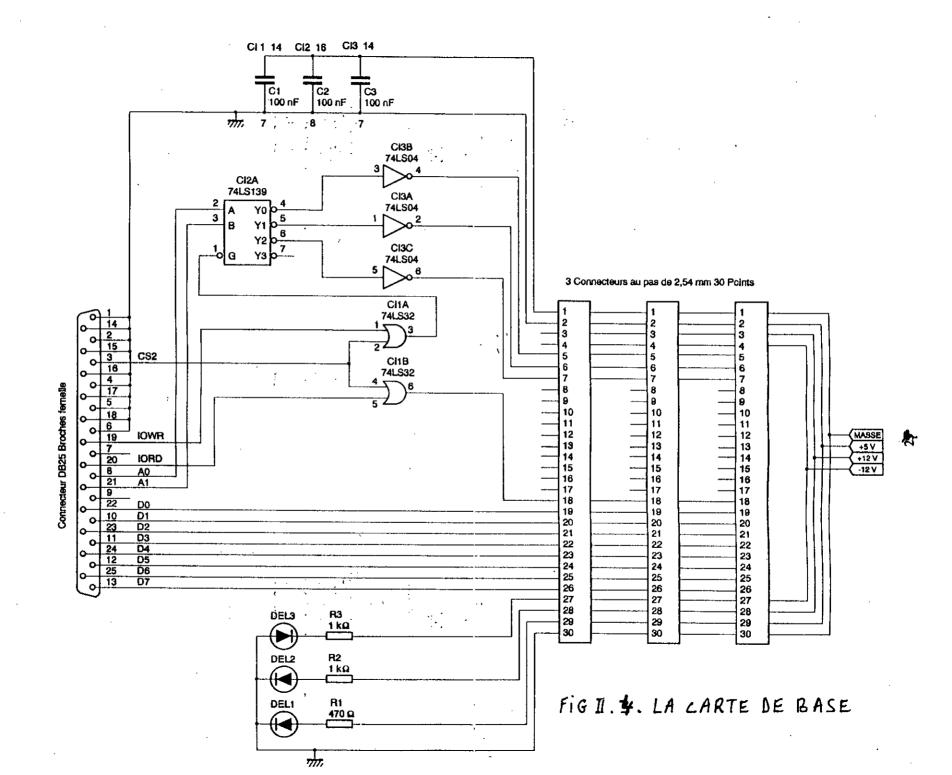

Le schéma de principe est donné en figure II.4.

La carte de base est reliée à la carte de décodage des adresses du précédent paragraphe.

L'adresse de base a été fixée à H308.

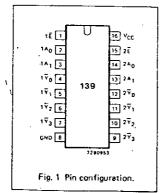

Les deux lignes A0 et A1 viennent aux deux entrées d'un décodeurdémultiplexeur 2 vers 4, un 74LS139 (CI2A).

Ce circuit ne pourra être validé que lorsqu' un ordre sera envoyé en écriture à l'adresse H308.

En effet, le signal de validation provenant de la porte OU CI1A (74LS32), et qui résulte de la combinaison des signaux IOWR/ et H308 (ou CS2) parvient à l'entrée G/ du 74LS139.

La sortie Y0/ présentera un niveau bas lorsque l'adresse visée sera H308.

La sortie Y1/ sera active lorsque l'adresse sera H309 et la sortie Y3/ le sera à

l'envoi d'un ordre en H30A.

Ces signaux négatifs seront ensuite inversés par trois inverseurs (CI3A, CI3B, CI3C), les cartes suivantes nécessitant un signal positif.

Pour le fonctionnement du système, nous n'aurons l'utilité que d'un seul signal de lecture, Ce dernier est obtenu par la combinaison des signaux IORD/ et CS2.

Trois DEL (DEL1, DEL2, DEL3) dont le courant est limité par trois résistances (R1, R2, R3), signalent la présence, sur la carte de base, des trois tensions nécessaires au fonctionnement des cartes éxternes (+5 V, +12 V et -12V).

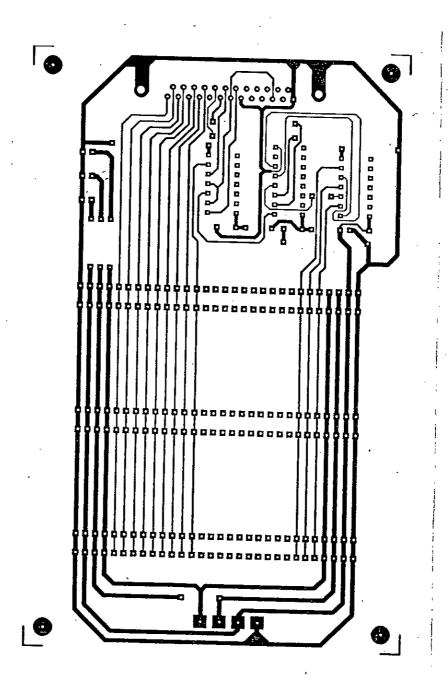

Le dessin du circuit imprimé est donné en figure II. 5.

#### IV. CIRCUIT DE TEST:

#### IV. 1. METHODES DE DETECTION:

On distingue 3 méthodes de détection :

- Méthode matricielle ( méthode du clavier ) .

- Détection par buffers.

- · détection par multiplexeurs.

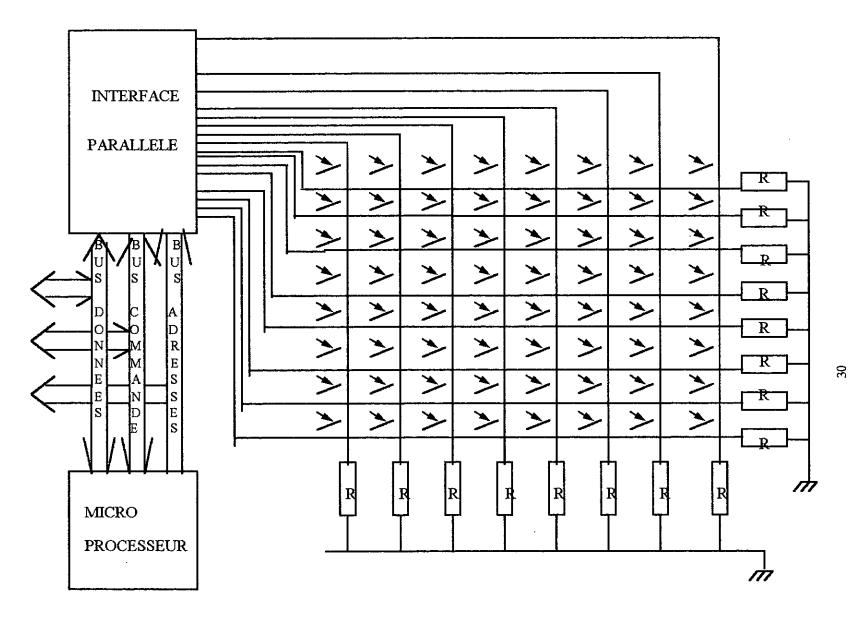

#### 1) METHODE MATRICIELLE: " METHODE DU CLAVIER "

C'est la méthode généralement utilisée pour la détection des touches du clavier, les lignes de conduction sont disposées de façon matricielle (lignes et colonnes, et les contacts forment les éléments de cette matrice). (fig II.6)

#### **AVANTAGES:**

• Elle ne nécessite que seize résistances, comme matériel, pour une détection de soixante quatre trous.

FIG II. 5. CIRCUIT IMPRIME DE LA CARTE DE BASE

FIG II. 6. DETECTION PAR LA METHODE MATRICIELLE.

#### **INCONVENIENTS:**

• Les lignes d'acquisition de données sortantes des différents trous sont reliées entre elles suivant les lignes et suivant les les colonnes, cela pose un problème pour la détection du nombre exact de contacts :

\*Lorsqu' on enfiche deux dipôles, on aura quatre contacts A, B, C et D.

Si trois d'entre eux (A, B et C) sont sur la même ligne et le quatrième (D) sur la même colonne qu'un des trois (C), alors le microprocesseur détectera six contacts.

Les contacts détectés sont A, B, C et D avec deux autres qui sont sur la ligne de D et sur les colonnes de A et B.

#### 2) DETECTION PAR BUFFERS:

Les buffers sont des circuits de validation qui ne sont validés qu' à un certain niveau (haut ou bas) d'une de leur broches (broche de validation).

Donc on ne retire que huit informations à chaque fois, par le biais de la validation d'un des buffers.

On considère que les buffers forment les lignes (fig II. 7), l'information est donc reçue ligne par ligne.

#### COUT:

Les composants simples (fiches et résistances ) étant les mêmes dans chaque méthode, leur prix de revient reste donc le même, on se préoccupera pour cela uniquement du prix des circuits intégrés afin de pouvoir faire la comparaison des méthodes de détection.

Le prix d'un Buffer " 244 " étant de 45 DA, le circuit constitué de 8 Buffers aura donc un coût de 360 DA.

#### **AVANTAGES:**

• Les lignes d'acquisition des données sortantes des différents trous ne sont pas reliées entre elles. Autrement dit, la détection nous donne le nombre réellement existant des contacts, contrairement à la méthode matricielle.

CONCEPTION DES CIRCUITS D'INTERFACE

Chapitre II

#### **INCONVENIENTS:**

• Encombrement, vu l'utilisation de huit buffers et de 64 résistances.

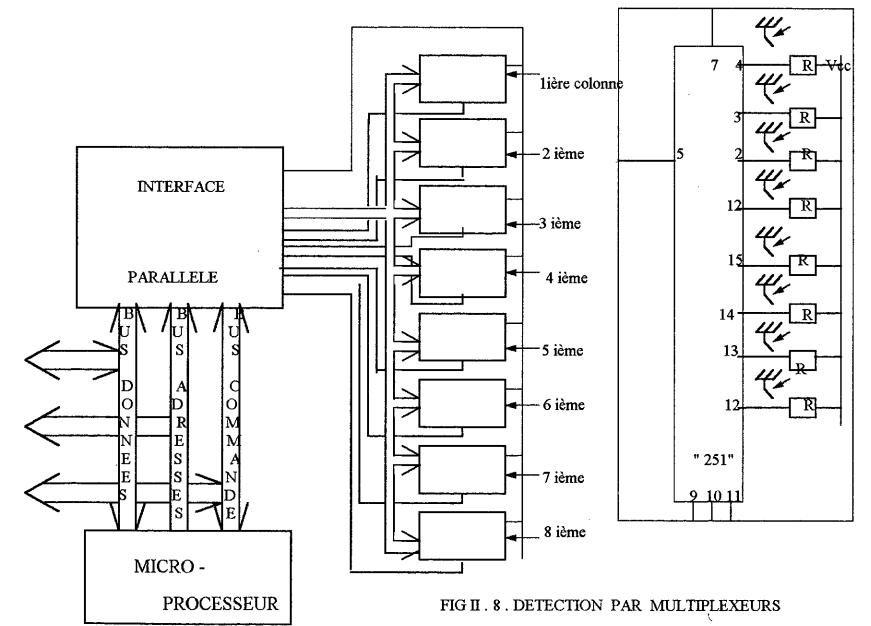

#### 3) DETECTION PAR MULTIPLEXEURS:

Le microprocesseur ne reçoit l'information d'un contact qu'après validation du multiplexeur correspondant et la sélection de la ligne.

Les multiplexeurs forment les colonnes. (fig II.8)

L'information est donc reçue ligne par ligne (puisqu' on sélectionne à chaque fois la même ligne de chaque multiplexeurs).

#### COUT:

Le prix d'un multiplexeur "251" est de 40 DA, le prix de 8 multiplexeurs sera donc de 320 DA.

#### **AVANTAGES:**

• Les lignes d'acquisition des données (sortantes des différents trous) ne sont pas reliées entre elles. Donc la détection nous donne le nombre de contacts réellement existants.

#### **INCONVENIENTS:**

• Encombrement vu l'utilisation de huit multiplexeurs et d'un nombre de résistances égal à celui des trous dans la carte.

#### IV. 2. CONCLUSION:

La méthode de détection par multiplexeurs est plus économique que la méthode de détection par buffers.

La carte d'essai qu'on utilise est constituée de 25 noeuds. A chaque noeud correspond 4 trous, donc on a 100 trous dans la carte.

On remarque qu'il y en a 20 dans lesquels on ne peut enficher des composants (les trous externes), il reste donc 80 trous à détecter.

• On peut utiliser 10 multiplexeurs pour ne pas encombrer la carte d'interface, mais dans ce cas:

34

\*Après acquisition de 5 lignes et de 3 colonnes par les huit premiers multiplexeurs (le microprocesseur reçoit 8 données à la fois), il restera 2 colonnes qui seront lues ligne par ligne (le microprocesseur reçoit dans ce cas 2 données à la fois) par les deux multiplexeurs restants.

Ceci va engendrer un ralentissement du processus d'acquisition des données.

• On peut utiliser 10 buffers, mais le prix dans ce cas sera assez élevé : 450DA.

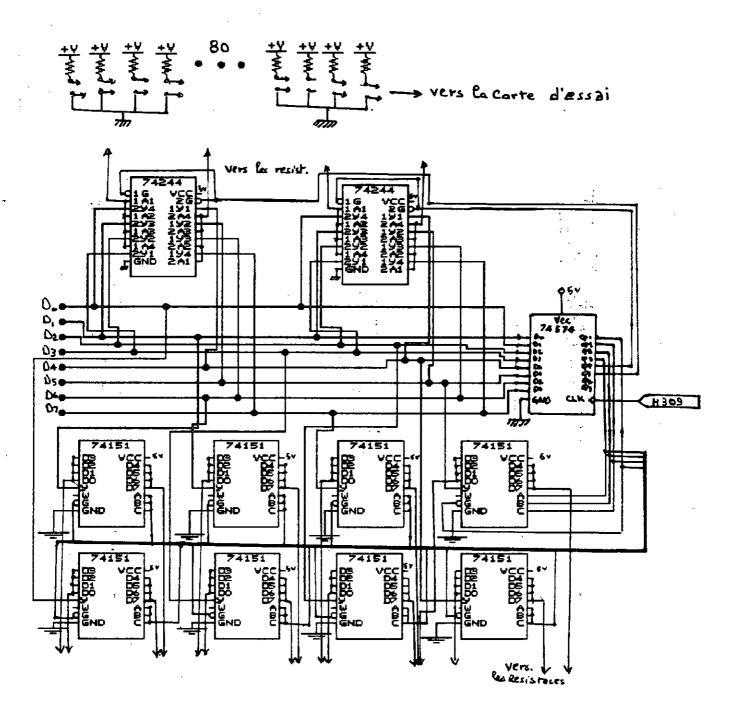

#### PROPOSITION:

Par la combinaison des 2 méthodes, on peut concevoir un circuit constitué de 8 multiplexeurs et 2 buffers, ainsi:

- On réduit le prix de revient du circuit (le prix se réduit à 410 DA).

- Dans ce cas, nous n'avons pas de perte de lignes des multiplexeurs lors du déroulement du programme, le processus d'acquisition des données n'est donc plus ralentie.

Vu les avantages que cette proposition présente par rapport au méthodes précédentes, ce choix sera retenu. Le schéma du montage est représenté en figure II.9.

La prise en compte, par la bascule CI1 (74HCT574), de l'information a lieu lorsque le signal appliqué sur sa broche CLOCK présente un front positif, ce front est disponible à l'adresse H309.

La bascule CI1 permet, suivant la valeur du bus de données :

\*La validation des multiplexeurs par leur broches 7.

\*La selection des lignes des multiplexeurs par leurs broches 9, 10, 11.

\*La validation et la selection des quartets de lignes des buffers par leurs broches 1 et 19.

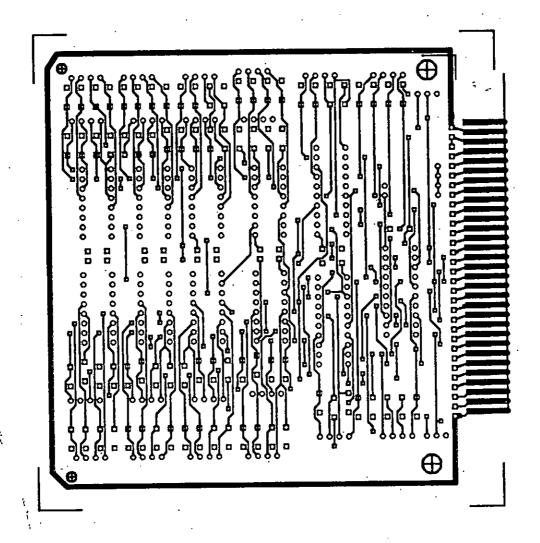

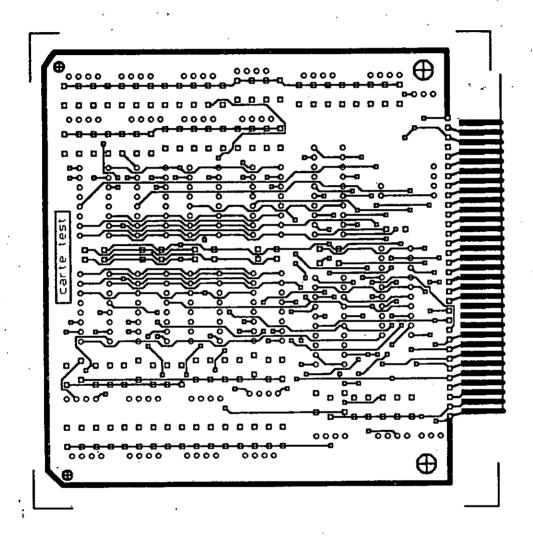

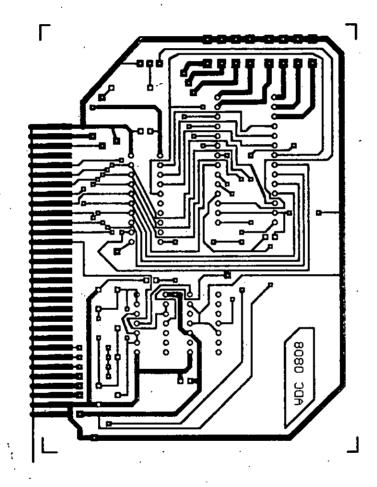

Le dessin du circuit imprimé est donné en figure II. 10.

FIG II.9. SCHEMA DU CIRCUIT DE TEST.

FIG II.10. CIRCUIT IMPRIME DE LA CARTE DE TEST\_COTE

COMPOSANTS.

FIG II . 10 . CIRCUIT IMPRIME DE LA CARTE DE TEST\_COTE SOUDURES.

#### **V. CARTES DE CONVERSION:**

Il est nécessaire, lorsque l'on désire confier à l'ordinateur la mesure de données analogiques de procéder à la transformation de ces dernières en des données numériques assimilables par le système, cette dernière est réalisée par les convertisseurs analogique - numérique (CAN).

De même, c'est par l'intermédiaire des convertisseurs numérique - analogique (CNA) que les calculateurs donnent des ordres ou transmettent des informations vers le monde extérieur analogique.

#### PARAMETRES DE CHOIX DES CONVERTISSEURS:

Le principal objectif de notre projet est la conçeption d'un système de génération, de mesure et de visualisation :

- De tout signal dont la fréquence atteindra au maximum une fréquence de 100 khz, la forme de ce signal pouvant être quelconque.

- De tout signal alternatif dont la plage d'amplitude s'étend entre -5 V et +5 V.

- De tout signal continu dont la plage d'amplitude s'étend entre -15 V et +15V. Ceci compte tenu des travaux pratiques actuellement en application en premier cycle universitaire.

#### CHOIX DES CONVERTISSEURS:

Choix du CNA: Nous avons choisi le DAC 0808 pour les raisons suivantes:

- il possède un temps de conversion très faible (environ 100 ns).

- sa plage d'amplitude de sortie est modifiable selon la tension de référence appliquée.

- il est disponible sur le marché national à un prix raisonnable.

Choix du CAN: La fréquence maximale du signal à traiter étant relativement élevée (100 khz) (caracteristique la plus importante à prendre en compte pour notre choix), seuls les convertisseurs hautes performances peuvent parvenir à cette fréquence. ces derniers sont d'un coût inabordable et ne sont pas disponibles sur le marché national.

Pour cette raison nous avons choisi le convertisseur ADC 0808 ayant pour principales caracteristiques :

- temps de conversion de 100 μs : il peut donc convertir un signal ayant une fréquence maximale d'environ 5 khz.

- plage d'amplitude d'entrée modifiable selon la tension de référence appliquée.

- disponible sur le marché national à un prix abordable.

#### V.1. LA CARTE DE CONVERSION NUMERIQUE-ANALOGIQUE:

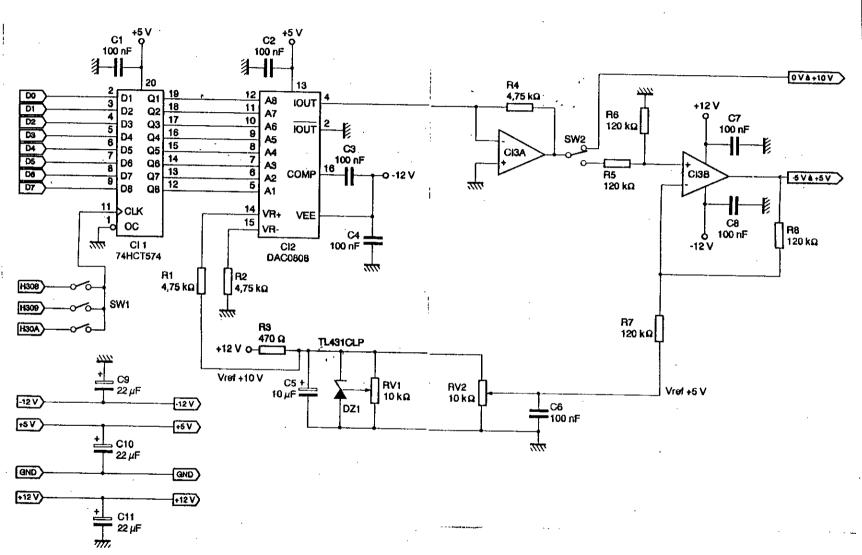

FONCTIONNEMENT DE LA CARTE: (figure II.11)

La carte que nous allons décrire permettra la génération d'une tension soit simple (0 V à +10 V), soit bipôlaire (-5 V à +5 V), par la conversion d'un octet qui lui sera envoyé à l'aide des cartes précédentes (cartes d'adresses et de base).

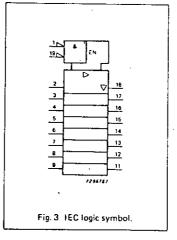

Nous remarquons tout d'abord l'octuple bascule CI1, un 74LS574.

En effet, le convertisseur que nous avons utilisé (le DAC0808), ne contient pas, contrairement à beaucoup d'autres circuits convertisseurs, de bascules destinées à mémoriser l'octet qui lui est envoyé par le bus du microprocesseur.

Nous avons donc dû lui adjoindre cette dernière en externe.

La prise en compte par CI1 de l'information a lieu lorsque le signal appliqué sur sa broche CLOCK présente un front positif.

Ce front peut être disponible à trois adresses différentes, et trois switches permettent le choix de cette adresse.

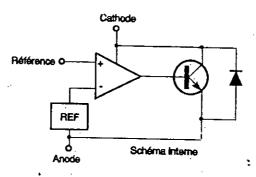

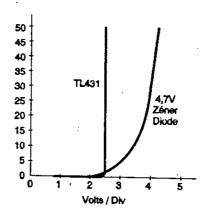

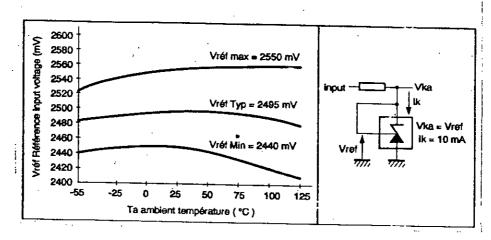

Pour qu'il puisse fonctionner, le CNA nécessite une tension de référence +10V, tension qui doit être d'une précision et d'une stabilité excellentes.

Celle-ci est fournie par une diode Zener de référence, la TL431CLP.

Sa tension est ajustable par une résistance variable RV1.

Un condensateur C5 de 10µF, filtre cette tension.

Elle est ensuite appliquée à la broche Vref (+) du convertisseur.

FIG II. 11. LA CARTE DE CONVERSION NUMERIQUE - ANALOGIQUE

#### PLAGE D'AMPLITUDE DE LA TENSION DE SORTIE :

La sortie du CNA a lieu sur sa broche 4.

Elle est alors appliquée à un amplificateur opérationnel (CI3A) configuré en convertisseur courant-tension.

Sur sa sortie est alors disponible une tension pouvant varier entre 0V et + 10 V, suivant le poids de l'octet qui lui sera appliqué sur ses entrées (0 à 255).

Afin de pouvoir disposer d'une tension bipolaire (-5 V à +5 V), il a été ajouté un second amplificateur opérationnel qui fonctionne de la manière suivante :

CI3B est configuré en amplificateur inverseur de gain unitaire.

Sur son entrée inverseuse est appliquée en permanence une tension de référence de +5 V.

Supposons la tension de sortie du convertisseur égale à 0V, la sortie de CI3B présente alors un potentiel de sortie de -5 V.

Si son entrée non inverseuse est soumise à un potentiel de +5 V, alors sa sortie présente une tension nulle, les potentiels de +5 V et -5 V s'annulant.

Enfin pour une tension de sortie de +10 V du CNA, le potentiel de la sortie de CI3B sera égal à +5 V (+10 V - 5 V = +5 V).

Un second switch SW2 permet, par sa manoeuvre, le passage de la tension de sortie unipolaire en tension de sortie bipolaire.

Tous les convertisseurs réclament un découplage éfficace de leurs points d'alimentation par des condensateurs situés au plus près de leur boîtier, c'est ce qui est fait par C2, C3 et C4.

Tous les autres circuits, logiques et analogiques, sont également munis de leur capacité.

Les lignes d'alimentation provenant de la carte de base sont également filtrées par des condensateurs de  $22\mu F$ .

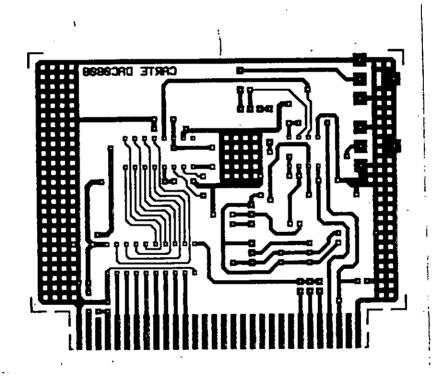

Le dessin du circuit imprimé est donné en figure II.12.

FIG II. 12. CIRCUIT IMPRIME DE LA CARTE DE CONVERSION NUMERIQUE - ANALOGIQUE.

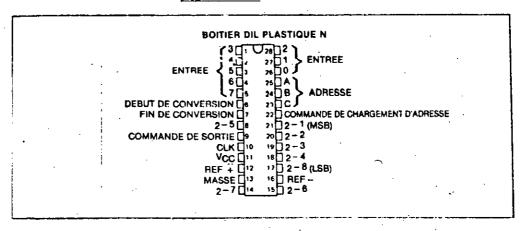

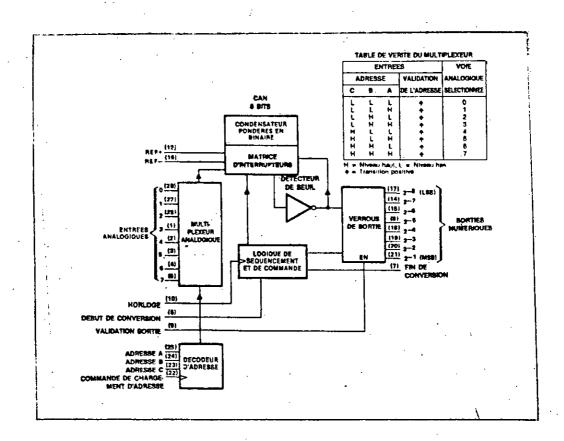

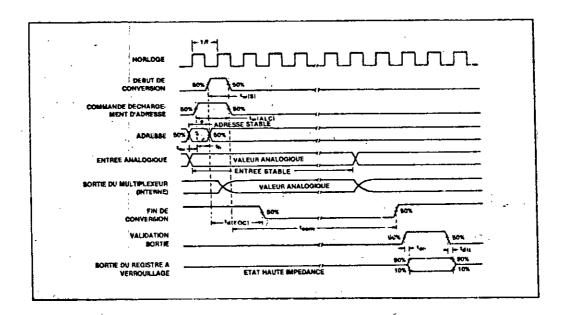

#### V. 2. LA CARTE DE CONVERSION ANALOGIQUE-NUMERIQUE :

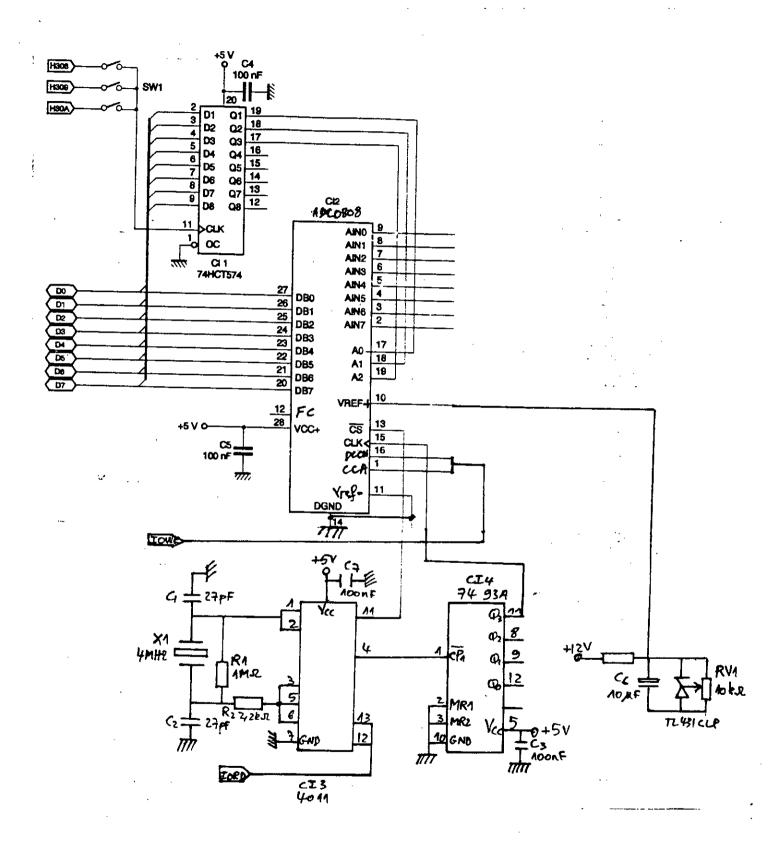

Le schéma de principe est donné en figure II. 13.

Les lignes de données provenant de la carte de base sont directement connectées au CAN (1' ADC0808), ce dernier possèdant des latches nécessaires à la mise en mémoire des états logiques de chaque ligne.

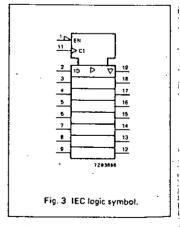

Afin de déterminer laquelle des entrées (IN1 à IN7) on désire lire, les trois broches d'adresses du convertisseur sont reliées à une bascule 74LS574, CI1, laquelle est validée, comme pour la carte précédente par l'un des trois signaux disponibles sur la carte de base.

Ainsi, si l'on envoie l'octet 00 à la bascule CII, ce sera l'entrée IN1 qui sera active, si nous envoyons l'octet 07, ce sera l'entrée IN8 qui sera choisie.

Lorsqu'un signal d'écriture est envoyé au circuit, l'équivalent en valeur binaire de la tension d'entrée du canal choisi apparaît sur les sorties DB0 à DB7.

Ce signal d'écriture est appliqué sur les broches début de conversion (DCON) et commande de chargement d'adresse (CCA) du convertisseur.

Le microprocesseur envoie ensuite un signal de lecture afin de lire ces données.

Le convertisseur nécessite l'emploi d'une horloge externe afin de cadencer le processus de conversion.

Le signal d'horloge est généré par un quartz dont la fréquence d'oscillations de 4 Mhz est divisée par un compteur binaire, 12-74HC4811 (CF3).

Cette fréquence est ensuite divisée par & par un autre compteur binaire CI4 (le 74L93), la fréquence de sortie devient donc 500 KHZ, elle est alors appliquée sur l'entrée CLOCK du convertisseur.

La tension de référence nécessaire au CAN est d'une valeur de +5 V, elle est produite par la Zener de référence DZ1, une TL431CLP.

Le dessin du circuit imprimé est donné en figure II. 14.

FIG II. 13. LA CARTE DE CONVERSION ANALOGIQUE - NUMERIQUE.

FIG II. 14. CIRCUIT IMPRIME DE LA CARTE DE CONVERSION ANALOGIQUE - NUMERIQUE.

## **CHAPITRE III:**

# LOGICIEL D'APPLICATION

### CHAPITRE III: LOGICIEL D' APPLICATION

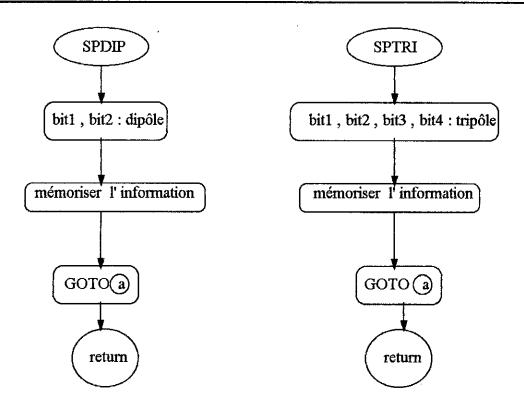

#### I. LOGICIEL DE TEST DES DONNEES:

Moyennant le circuit d'interface, le microprocesseur doit détecter l'emplacement des composants, ensuite, le sens de placement des composants sur la carte d'essai.

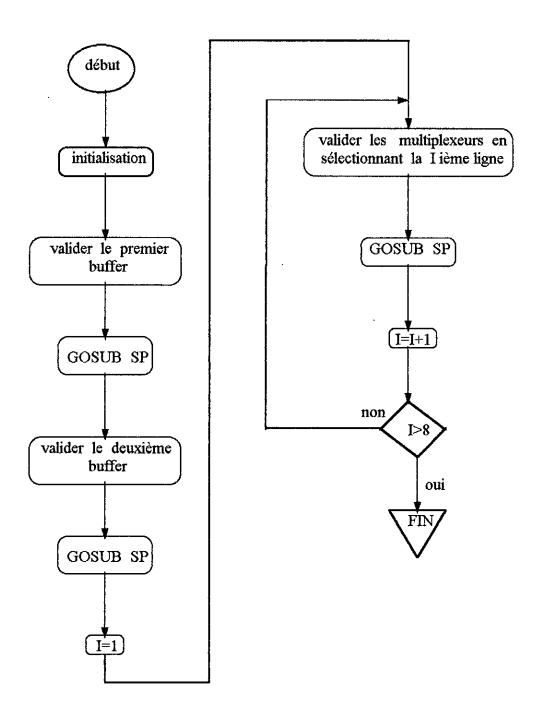

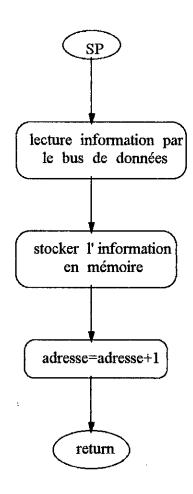

## I . 1 . ALGORITHME DE DETECTION DE L'EMPLACEMENT DES CONTACTS :

Pour la détection de l'enfichage des composants, il faut :

- mettre le bus de données en sortie.

- valider le premier buffer .

- mettre le bus de données en entrée.

- saisir l'information et la mettre en mémoire.

- mettre le bus de données en sortie.

- valider le deuxième buffer.

- mettre le bus de données en entrée.

- saisir l'information et la mettre en mémoire.

- mettre le bus de données en sortie.

- valider les multiplexeurs en sélectionnant la première ligne.

- mettre le bus de données en entrée.

- saisir l'information et la mettre en mémoire.

- refaire le même travail pour les sept autres lignes.

#### **ORGANIGRAMME:**

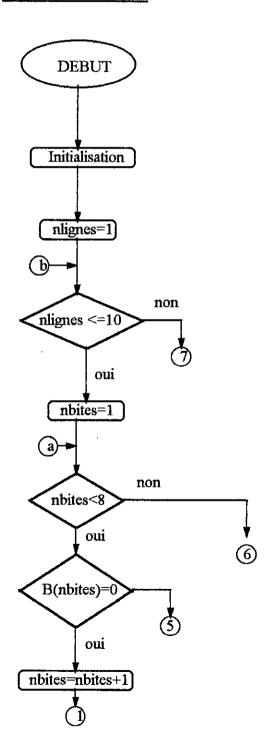

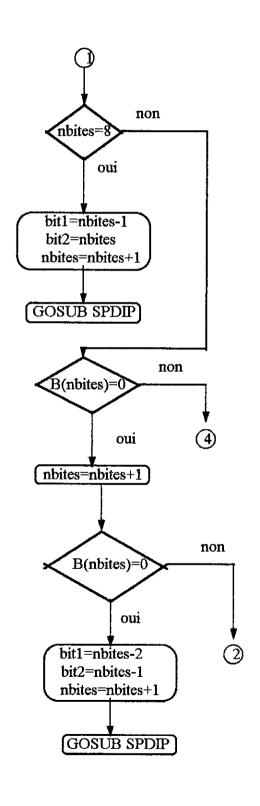

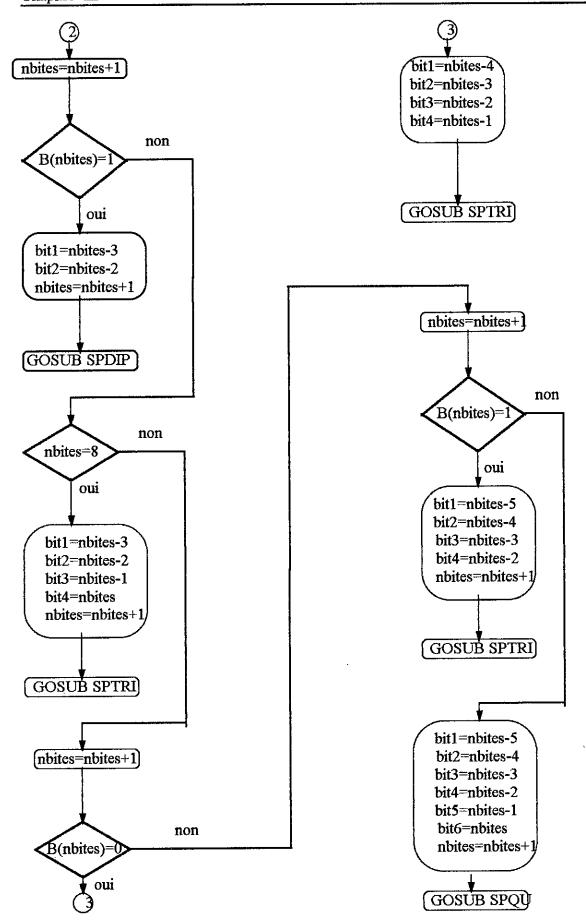

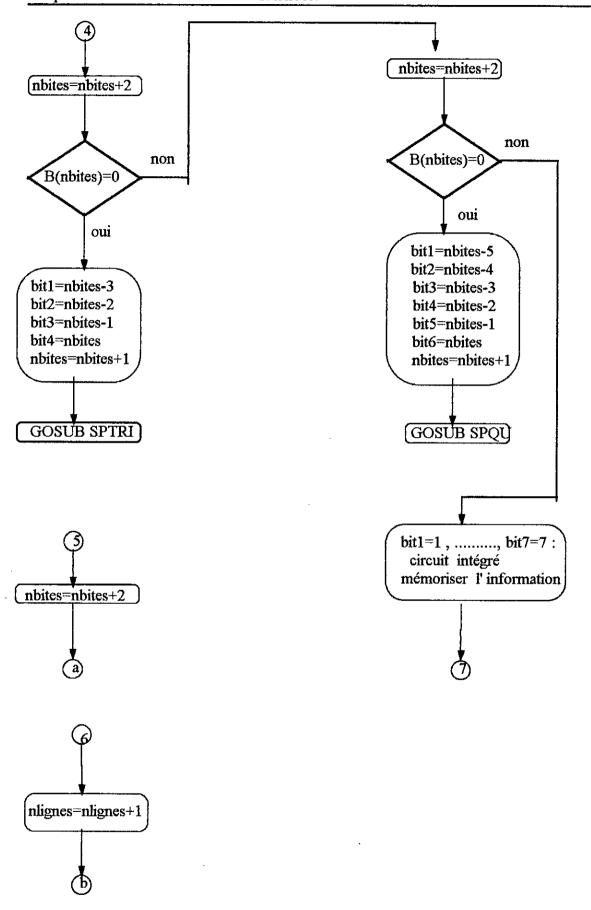

## I.2. ALGORITHME DE DETECTION DU SENS DE PLACEMENT DES COMPOSANTS:

Initialisation

nlignes=1

(3) tant que nlignes <10 faire

nbites=1

(1) si nbites <8 alors :

si B(nbites)=0 alors :

nbites=nbites+1

```

►si nbites=8 alors:

* (nbites-1) et (nbites) : dipôle.

* mémoriser l'information.

GOTO (2)

Fin si

si B(nbites)=0 alors:

nbites=nbites+1

■ si B(nbites)=0 alors:

* (nbites-2) et (nbites-1) : dipôle.

* mémoriser l'information.

GOTO (1)

Fin si

nbites=nbites+1

si B(nbites)=1 alors:

* (nbites-3) et (nbites-2) : dipôle .

* mémoriser l'information.

* nbites=nbites+1.

GOTO (1)

Fin si

si nbites=8 alors:

* (nbites-3), (nbites-2), (nbites-1), (nbites): tripole

* mémoriser l'information.

GOTO (2)

Fin si

```

```

nbites=nbites+1

si B(nbites)=0 alors:

* (nbites-4), (nbites-3), (nbites-2), (nbites-1:

tripole.

* mémoriser 1' information .

GOTO (1)

Finsi

nbites=nbites+1

si B(nbites)=1 alors:

* (nbites-5), (nbites-4), (nbites-3),

(nbites-2): tripole.

* mémoriser l'information.

* nbites=nbites+1.

GOTO(1)

Finsi

* (nbites-5), (nbites-4), (nbites-3),

(nbites-2), (nbites-1), (nbites):

quadripôle.

* mémoriser l'information.

* nbites=nbites+1.

GOTO(1)

Fin si

nbites=nbites+2

```

```

si B(nbites)=0 alors:

* (nbites-3), (nbites-2), (nbites-1), (nbites): tripole.

* mémoriser l'information.

* nbites=nbites+1.

GOTO (1)

Fin si

nbites=nbites+2

si B(nbites)=0 alors:

* (nbites-5), (nbites-4), (nbites-3), (nbites-2), (nbites1),

(nbites): quadripôle.

* mémoriser l'information.

* nbites=nbites+1.

GOTO(1)

Fin si

* (nbites-5), (nbites-4), (nbites-3), (nbites-2), (nbites-1),

(nbites), (nbites+1): circuit intégré.

* mémoriser l'information.

* nlignes = nlignes + 1.

GOTO (2)

Fin si

, nbites=nbites+2

GOTO (1)

Fin si

```

(2) nlignes=nlignes+1

GOTO (3)

FIN.

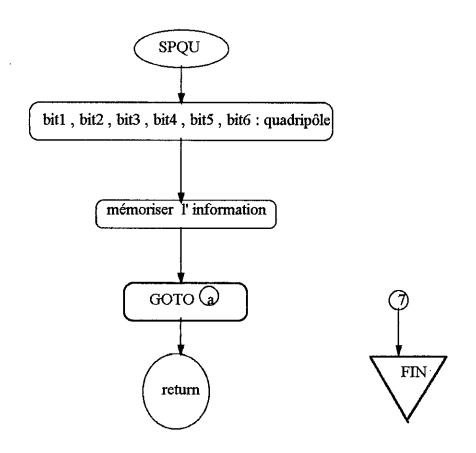

#### **ORGANIGRAMME**:

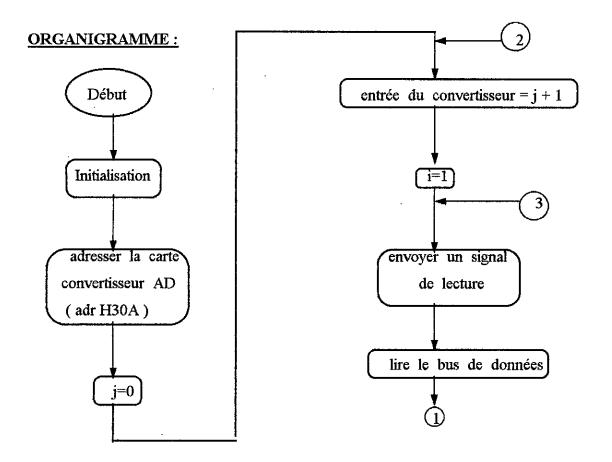

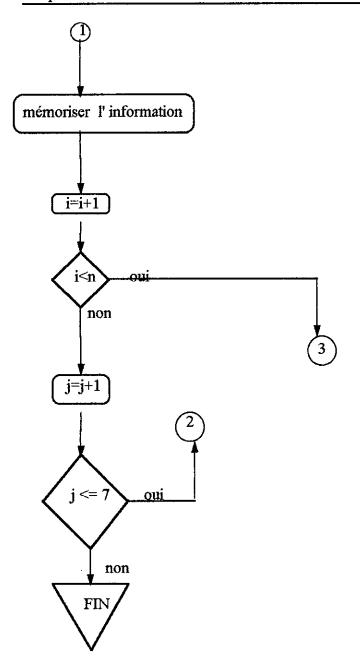

## II . ALGORITHME DE GESTION DE LA CARTE DE CONVERSION ANALOGIQUE - NUMERIQUE :

Pour gérer la carte convertisseur, il faut :

- 1. Initialiser le système.

- 2. sélectionner la carte convertisseur AD.

- 3. envoyer la valeur 00 sur le bus de données (pour sélectionner IN1).

- 4. envoyer le signal de lecture.

- 5. lire les données du bus de données.

- 6. mémoriser l'information.

- 7. envoyer un autre signal de lecture.

- 8. lire la donnée sur le bus de données.

- 9. mémoriser l'information.

- 10.répéter les opérations (4, 5, 6) autant qu'il faut pour reconstituer le signal.

- 11. envoyer la valeur 01 sur le bus de données (pour sélectionner IN2).

- 12.répéter les opérations 4 à 10.

- 13.refaire le même travail pour les autres entrées (INO à IN7).

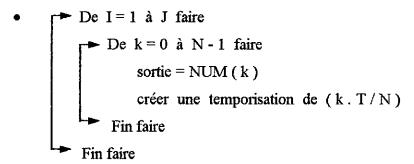

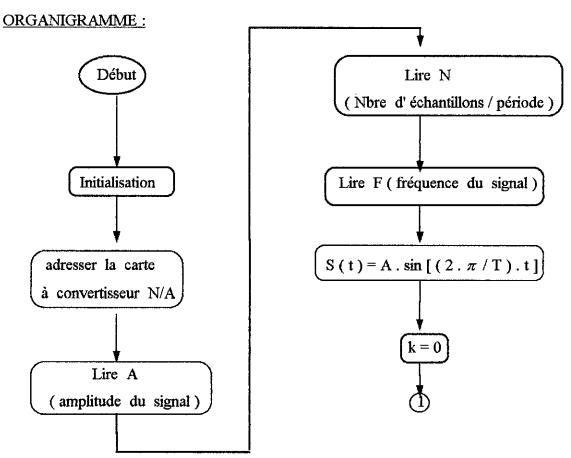

### III . ALGORITHME DE GESTION DE LA CARTE A CNA : EXEMPLE : GENERATION D' UNE SINUSOIDE :

#### **ALGORITHME:**

- Initialisation .

- Sélectionner la carte à convertisseur numérique analogique .

- Donner la valeur de l'amplitude A ( <= 2,5 ) du signal.

- Donner le nombre d'échantillons N par périodes du signal.

- Donner la fréquence F du signal.

- T = 1/F.

- $S(t) = A \cdot \sin [(2 \cdot \pi / T) \cdot t]$ .

- Pour k = 0 à N 1 faire

ECH (k) = A.

$$\sin [(2.\pi/T).k.T/N]$$

NUM (k) = arrondi [(ECH (k) + 5).255/Vref]

Fin faire

• Donner la valeur de J (nombre de périodes à générer).

• Fin

# CONCLUSION GENERALE

# **CONCLUSION GENERALE:**

Pour conclure ce mémoire nous signalons l'achèvement quasi total du travail exigé par le cahier de charges.

Lors du test des cartes réalisées, nous avons obtenu les résultats suivants:

- La carte de test des composants a fourni des résultats satisfaisants, elle nous a permis de détecter l'enfichage, le type des composants enfichés et la configuration du montage réalisé, elle nous a aussi permis de comparer un circuit réalisé sur la carte d'essai avec un circuit préalablement implémenté dans la mémoire de l'ordinateur permettant ainsi de détecter les erreurs existantes entre les deux circuits.

- La carte à convertisseur numérique analogique nous a permis la génération d'une tension soit simple (de 0 V à + 10 V), soit bipolaire (de 5 V à + 5 V), mais la fréquence maximale que nous avons pu obtenir était d'environ 20 à 25 Hz (qui est une très basse fréquence), du fait de la lenteur du langage de programmation qu'on a utilisé (le "QUICKBASIC"), mais si on aurait utilisé un langage de programmation plus rapide, notamment l'"ASSEMBLEUR", on serait parvenu à une fréquence nettement plus élevée, le convertisseur que nous avons utilisé possédant un temps de conversion de 100 ns, il permet donc la conversion d'un signal de fréquence maximale pouvant aller jusqu' à 5 Mhz.

L'avantage majeur de cette carte est le fait qu' on peut générer un signal ayant n'importe quelle forme qu' on peut imaginer à condition bien sûr, qu' il obéisse à la condition de Shannon.

Pour la même raison évoquée précédemment, la carte de conversion analogique numérique nous a permis la mesure d'un signal de fréquence maximale d'environ 20 à 25 Hz. Vu l'indisponibilité de convertisseurs analogique - numérique suffisamment rapides pour atteindre une fréquence de 100 Khz (fréquence que nous désirions obtenir), le convertisseur que nous avons utilisé permet la conversion d'un signal de fréquence maximale 5 Khz puisqu'il possède un temps de conversion de 100 µs, fréquence trop inférieure à celle qui était recquise.

Ces résultats nous ont permis de proposer plusieurs voies de développement qui restent à être entreprises par de futurs candidats, notemment :

- L'extension du nombre de noeuds sur la carte d'essai.

- L'élaboration d'un banc de mesure plus performant, permettant la mesure de signaux de fréquence supérieure à 5 Khz.

- Un logiciel d'application plus performant.

- La mise en place d'une stratégie de simulation .

Enfin, il faut noter que le présent projet nous a permis un perfectionnement dans le domaine de l'électronique numérique et une maîtrise d'un grand nombre de possibilités que permet le microprocesseur.

Par le biais de ce projet, nous avons également pu être préparé au métier d'ingénieur et à la prise de décision devant les problèmes techniques qui surgissent.

# ANNEXE 1

# ANNEXE 1

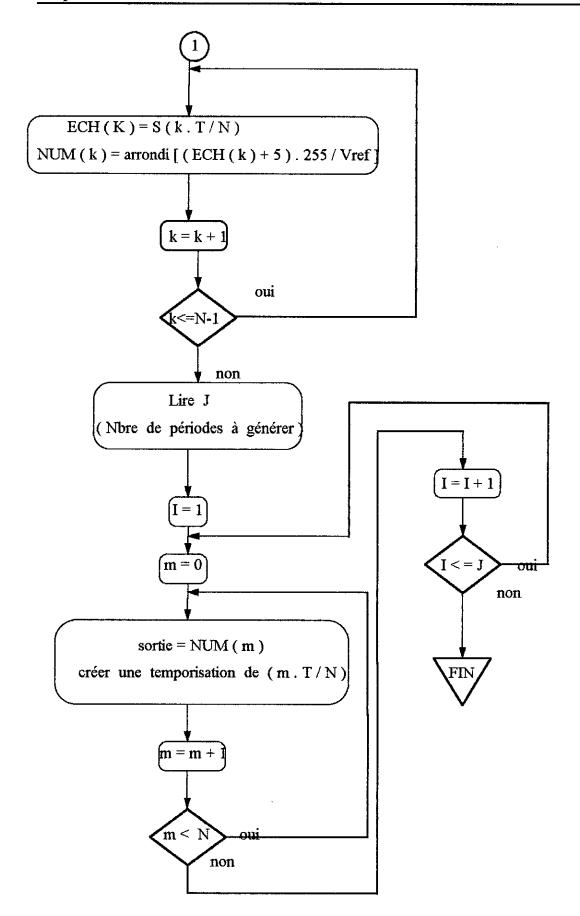

#### **LE BUS D' EXTENSION :**

Le bus d'extension de l'ordinateur de la gamme PC AT486 s'étend sur une rangée de 7 connecteurs ( de X1 à X7 ). Chaque broche est séparement câblée en parallèle avec toutes les autres broches du même numéro.

La figure ci-dessous représente un bloc diagramme de ces connecteurs :

- · X1, X2, X3 et X4 sont des connecteurs à 62 broches pour des dispositifs 8 bits.

- $\cdot$  X5, X6 et X7 sont des connecteurs à 98 broches pour des dispositifs 16 bits .

FIG A . 1 . LE BUS D'EXTENSION .

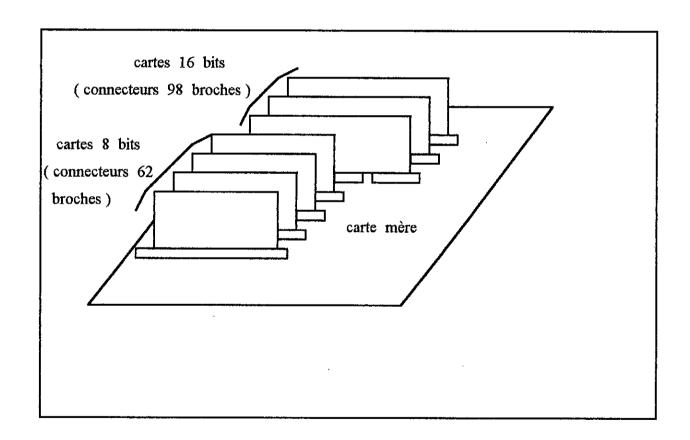

#### LES CONNECTEURS 8 BITS:

Tous les connecteurs à 8 bits (de X1 à X7) sont capables de supporter des dispositifs 8 bits étant donné que les 62 broches sont cablées en parallèle.

Les numéros des broches de ces connecteurs figurent sur le schéma ci-dessous :

FIG A . 2 . CONNECTEUR 8 BITS: NUMEROTATION DES BROCHES

Chaque côté de ce connecteur possède 31 broches. Vu du côté des composants, le côté (a) est sur la droite alors que le côté (b) est sur la gauche.

Le tableau ci-après donne les noms des différents signaux correspondant aux 62 broches ainsi que leurs types:

|            |       |        | T          | 1       |              |

|------------|-------|--------|------------|---------|--------------|

| PIN        | NOM   | TYPE   | PIN        | NOM     | TYPE         |

| al         | СНСК\ | Entrée | h1         | GND     | Masse        |

| a2         | D07   | E/S    | b2         | RESET   | Sortie       |

| а3         | D06   | E/S    | h3         | + 5 V   | Alimentation |

| <b>a4</b>  | D05   | E/S    | b4         | IRQ9    | Entrée       |

| .a5        | D04   | E/S    | b5         | - 5 V   | Alimentation |

| аб         | D03   | E/S    | <b>b6</b>  | DRQ2    | Entrée       |

| a7.        | D02   | E/S    | <b>b</b> 7 | - 12 V  | Alimentation |

| <b>a8</b>  | D01   | E/S    | b8         | ows     | Entrée       |

| а9         | D00   | Entrée | ь9         | + 12 V  | Alimentation |

| a10        | RDY   | Sortie | ь10        | GND     | Masse        |

| - a11      | AEN   | E/S    | b11        | SMEMW\  | Sortie       |

| a12        | A19   | E/S    | b12        | SMEMR\  | Sortie       |

| a13        | A18   | E/S    | ь13        | iow\    | E/S          |

| a14        | A17   | E/S    | b14        | IOR\    | E/S          |

| a15        | A16   | E/S    | b15        | DACK3\  | Sortie       |

| <b>a16</b> | A15   | E/S    | b16        | DRQ3    | Entrée       |

| a17        | A14   | E/S    | b17        | DACK1\  | Sortie       |

| a18        | A13   | E/S    | ь18        | DRQ1    | Entrée       |

| a19        | A12   | E/S    | b19        | REFRESH | E/S          |

| <b>a20</b> | A11   | E/S    | b20        | CLK     | Sortie       |

| n21        | A10   | E/S    | b21        | IRQ7    | Entrée       |

| a22        | A09   | E/S    | b22        | IRQ6    | Entrée       |

| a23        | A08   | E/S    | b23        | IRQ5    | Entrée       |

| a24 | A07 | E/S | b24 | IRQ4   | Entrée       |

|-----|-----|-----|-----|--------|--------------|

| a25 | A06 | E/S | b25 | IRQ3   | Entrée       |

| n26 | A05 | E/S | b26 | DACK2\ | Sortie       |

| a27 | A04 | E/S | b27 | T/C    | Sortie       |

| a28 | A03 | E/S | b28 | BALE   | Sortie       |

| a29 | A02 | E/S | h29 | + 5 V  | Alimentation |

| я30 | A01 | E/S | ь30 | OSC    | Sortie       |

| я31 | A00 | E/S | b31 | GND    | Masse        |

Affectation des broches

# ANNEXE 2

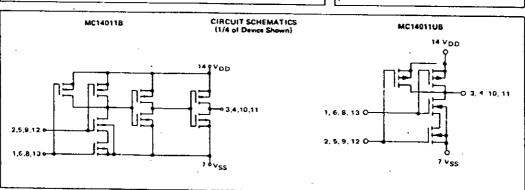

# MC14011B MC14011UB

#### QUAD 2-INPUT "NAND" GATE

The MC14011B and MC14011UB are constructed with P and N channel enhancement mode devices in a single monolithic structure (Complementary MOS). Their primary use is where low power dissipation and/or high noise immunity is desired.

- Quiescent Current = 0.5 nA typ/pkg € 5 Vdc

- Noise Immunity = 45% of V<sub>DD</sub> typ

- Supply Voltage Range = 3.0 Vdc to 18 Vdc

- All Outputs Buffered (MC140118 only)

- Capable of Driving Two Low-power TTL Loads, One Low-power Schottky TTL Load or Two HTL Loads Over the Rateo Temperature Range. (MC14011B only)

- Double Diode Protection on All Inputs

- Pin-for-Pin Replacements for CD4011B and CD4011UB

#### MAXIMUM RATINGS (Voltages referenced to VSS)

| Rating                                                     | Symbol           | . Value                   | Unit           |

|------------------------------------------------------------|------------------|---------------------------|----------------|

| DC Supply Vultage                                          | VOU              | 0510+18                   | Vøc            |

| Input Voltage All Inputs                                   | Vin              | 05 tu VDD -05             | Vdc            |

| DC Current Urain per Pin                                   | 1                | 10                        | mAde           |

| Operating Temperature Bunge - All Device -<br>CLICP Device | T <sub>A</sub>   | -55 to +125<br>-40 to +85 | <sub>D</sub> C |

| Storage Temperature Range                                  | T <sub>51Q</sub> | -65 to +150               | чc             |

See the MC14001B data sheet for complete characteristics of the B-Series device.

See the MC14001UB data sheet for complete characteristics for the UB device.

#### **CMOS SSI**

ILOW POWER COMPLEMENTARY MOSI

QUAD 2-INPUT "NAND" GATE

WYYYY.

L SUFFIX CERAMIC PACKAG CASE 632

P SUFFIX PLASTIC PACKAGE CASE 646

ORDERING INFORMATION

MC14XXXB

Suffix Denotes

Or UB,

B1 applicable

L Ceramic Package

P Plastic Package

A Extended Operating

Temperature Range

C Limited Operating

# LOGIC DIAGRAM 1 2 3 5 4 VOD - Put 14 VSS - Put 7 8 9 10 11

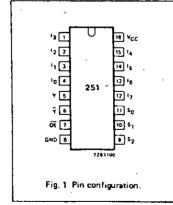

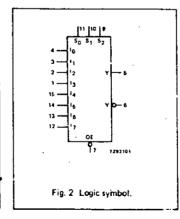

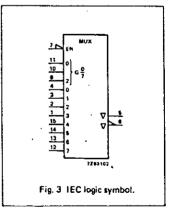

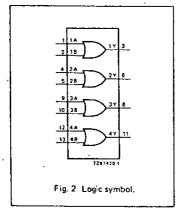

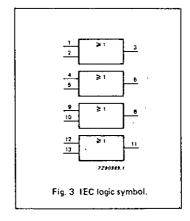

#### 8-INPUT MULTIPLEXER; 3-STATE

#### **FEATURES**

- True and complement outputs

- Both outputs are 3-state for further multiplexer expansion

- Multifunction capability

- Permits multiplexing from n-lines to one line

- Output capability: standard

- I<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

The 74HC/HCT251 are high-speed Si-gate CMOS devices and are pincompatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

The 74HC/HCT251 are the logic implementations of single-pole 8-position switches with the state of three select inputs (So. S1, S2) controlling the switch positions.

Assertion (Y) and negation  $(\overline{Y})$  outputs are both provided.

The output enable input (OE) is active LOW. The logic function provided at the output, when activated, is:

- Y = OE. (10.50.51.52 + 11.50.51.52 +

- + 12.50.51.52 + 13.50.51.52 +

- + I4.50.51.52 + I5.50.51.52 +

- + 16.50.51.52 + 17.50.51.52)

Both outputs are in the high impedance OFF-state (Z) when the output enable input is HIGH, allowing multiplexer expansion by tying the outputs.

| SYMBOL                    | PARAMETER                                         | CONDITIONS                                      | TYPICAL                         |          | UNIT           |

|---------------------------|---------------------------------------------------|-------------------------------------------------|---------------------------------|----------|----------------|

| STINBUL                   | FARAMETER                                         | CONDITIONS                                      | 15 19 17 19 20 20 21 21 3.5 3.5 |          |                |

| <sub>ՄԻԻԸ</sub> /<br>ՄԻԼΗ | propagation delay In to Y In to ∇ Sn to Y Sn to ∇ | C <sub>L</sub> = 15 pF<br>V <sub>CC</sub> = 5 V | 17<br>20                        | 19<br>20 | ns<br>ns<br>ns |

| cı                        | input capacitance                                 |                                                 | 3.5                             | 3.5      | рF             |

| C <sub>PD</sub>           | power dissipation capacitance per package         | notes 1 and 2                                   | 44                              | 46       | ρF             |

GND = 0 V; Tamb = 25 °C; tr = tf = 6 ns

1. CPD is used to determine the dynamic power dissipation (PD in  $\mu$ W):

PD = CPD ×  $VCC^2$  ×  $f_i$  +  $\Sigma$  (CL ×  $VCC^2$  ×  $f_0$ ) where:

- fi = input frequency in MHz

- □ output frequency in MHz

- $\mathsf{C}_\mathsf{L}$ - output load capacitance in pF

- VCC = supply voltage in V

- $\Sigma (C_L \times V_{CC}) \times f_0 = \text{sum of outputs}$

- 2. For HC the condition is V<sub>1</sub> = GND to V<sub>CC</sub>

For HCT the condition is V<sub>1</sub> = GND to V<sub>CC</sub> 1.5 V

#### ORDERING INFORMATION/PACKAGE OUTLINES

PL74HC/HCT251P: 16-lead D1L; plastic (SCT-38Z). PC74HC/HCT251T: 16-lead mini-pack; plastic (SO-16; SOT-109A).

| PIN NO.                       | SYMBOL                                           | NAME AND FUNCTION                        |

|-------------------------------|--------------------------------------------------|------------------------------------------|

| 4, 3, 2, 1, 15,<br>14, 13, 12 | lu to I7                                         | multiplexer inputs                       |

| 5                             | Y                                                | multiplexer output                       |

| 6                             | Ÿ                                                | complementary multiplexer output         |

| 7                             | δĒ                                               | 3-state output enable input (active LOW) |

| В                             | GND                                              | ground (0 V)                             |

| 11, 10, <del>9</del>          | S <sub>0</sub> , S <sub>1</sub> , S <sub>2</sub> | select inputs                            |

| 16                            | Vcc                                              | positive supply voltage                  |

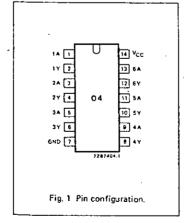

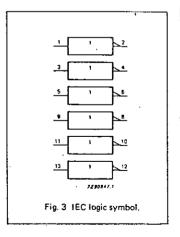

# HEX INVERTER

FEATURES

Output capability: standard e. Icc category: SSI

# GENERAL DESCRIPTION

The 74HC/HCT04 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT04 provide six inverting

| SYMBOL               | PARAMETER                                 | CONDITIONS                                      | TYPICAL |     |      |

|----------------------|-------------------------------------------|-------------------------------------------------|---------|-----|------|

| 31MBOL               | FARAMETER                                 | CONDITIONS                                      | HC      | нст | UNIT |

| ΦΗ <b>L</b> /<br>ΦLΗ | propagation delay<br>nA to nY             | C <sub>L</sub> = 15 pF<br>V <sub>CC</sub> = 5 V | .7      | 8   | ns   |

| CI                   | input capacitance                         |                                                 | 3.5     | 3.5 | pF , |

| C <sub>PD</sub>      | power dissipation<br>capacitance per gate | notes 1 and 2                                   | 21      | 24  | pF   |

GND = 0 V;  $T_{amb}$  = 25 °C;  $t_f$  =  $t_f$  = 6 ns

#### Notes

- 1. CPD is used to determine the dynamic power dissipation (PD in  $\mu W)$  :

- PD = CPD ×  $VCC^2$  ×  $f_i$  +  $\Sigma$  { $C_L$  ×  $VCC^2$  ×  $f_o$ } where:

- fi = input frequency in MHz fo = output frequency in MHz

- $C_L = \text{output load capacitance in pF}$   $V_{CC} = \text{supply voltage in V}$

- $\Sigma (C_L \times V_{CC}^T \times f_0) = \text{sum of outputs}$

- 2. For HC the condition is V<sub>I</sub> = GND to V<sub>CC</sub>

For HCT the condition is V<sub>I</sub> = GND to V<sub>CC</sub> 1.5 V

#### ORDERING INFORMATION/PACKAGE OUTLINES

PC74HC/HCT04P: 14-lead DIL; plastic (SOT-27). PC74HC/HCT04T: 14-lead mini-pack; plastic (SO-14; SOT-108A).

| PIN NO.            | SYMBOL   | NAME AND FUNCTION       |

|--------------------|----------|-------------------------|

| 1, 3, 5, 9, 11, 13 | 1A to 6A | data inputs             |

| 2, 4, 6, 8, 10, 12 | 1Y to 6Y | data outputs            |

| 7                  | GND      | ground (0 V)            |

| 14                 | vcc      | positive supply voltage |

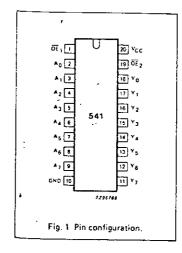

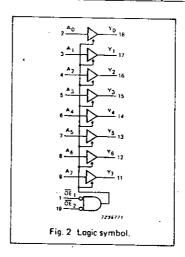

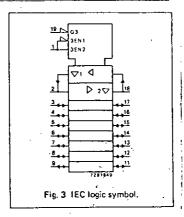

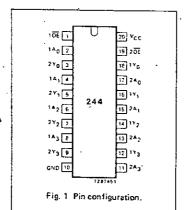

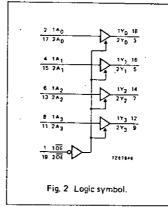

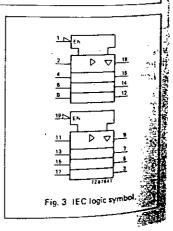

#### OCTAL BUFFER/LINE DRIVER; 3-STATE

#### **FEATURES**

- Non-inverting outputs

- · Output capability: bus driver

- I<sub>CC</sub> category: MS1

#### **GENERAL DESCRIPTION**

has non-inverting outputs,

The 74HC/HCT541 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT541 are octal noninverting buffer/line drivers with 3-state outputs. The 3-state outputs are controlled by the output enable inputs OE<sub>1</sub> and OE<sub>2</sub>. A HIGH on OEn causes the outputs to assume a high impedance OFF-state. The "541" is identical to the "540" but

| SYMBOL | PARAMETER                                             | CONDITIONS                                      | TYPICAL |     | Ī <u> </u> |

|--------|-------------------------------------------------------|-------------------------------------------------|---------|-----|------------|

|        |                                                       | CONDITIONS                                      | нс      | HCT | UNIT       |

| tPHL/  | propagation delay<br>A <sub>n</sub> to Y <sub>n</sub> | C <sub>L</sub> = 15 pF<br>V <sub>CC</sub> = 5 V | 10      | 12  | ns         |

| Cl     | input capacitance                                     |                                                 | 3.5     | 3.5 | pF         |

| CPD    | power dissipation<br>capacitance per multiplexer      | notes 1 and 2                                   | .37     | 39  | pF         |

GND = 0 V;  $T_{amb} = 25 \,^{\circ}\text{C}$ ;  $t_f = t_f = 6 \,\text{ns}$

- 1. CPD is used to determine the dynamic power dissipation (PD in  $\mu$ W):

- $P_D = C_{PD} \times V_{CC}^2 \times f_i + \Sigma (C_L \times V_{CC}^2 \times f_0)$  where:

- fi = input frequency in MHz

- $f_0$  = output frequency in MHz  $\Sigma$  (C<sub>L</sub> x V<sub>CC</sub><sup>2</sup> x  $f_0$ ) = sum of outputs

- 2. For HC the condition is V<sub>I</sub> = GND to VCC For HCT the condition is V<sub>I</sub> = GND to VCC 1.5 V

#### ORDERING INFORMATION/PACKAGE OUTLINES

PC74HC/HCT541P: 20-lead DIL; plastic (SOT-146). PC74HC/HCT541T: 20-lead mini-pack; plastic (SO-20; SOT-163A).

#### PIN DESCRIPTION

| PIN NO.                          | SYMBOL                            | NAME AND FUNCTION                |  |

|----------------------------------|-----------------------------------|----------------------------------|--|

| 1, 19                            | OE <sub>1</sub> , OE <sub>2</sub> | output enable input (active LOW) |  |

| 2, 3, 4, 5,<br>6, 7, 8, 9        | Ao to Ay                          | data inputs                      |  |

| 10                               | GND                               | ground (0 V)                     |  |

| 18, 17, 16, 15<br>14, 13, 12, 11 |                                   | bus outputs                      |  |

| 20                               | vcc                               | positive supply voltage          |  |

CL ≈ output load capacitance in pF VCC = supply voltage in V

#### OCTAL D-TYPE FLIP-FLOP; POSITIVE EDGE-TRIGGER; 3-STATE

#### **FEATURES**

- 3-state non-inverting outputs for bus oriented applications

- 8-bit positive edge-triggered register

- Common 3-state output enable input

- Independent register and 3-state buffer operation

- Output capability: bus driver

- I<sub>CC</sub> category: MSI

#### GENERAL DESCRIPTION

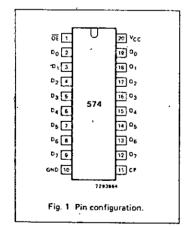

The 74HC/HCT574 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT574 are octal D-type flip-flops featuring separate D-type inputs for each flip-flop and non-inverting 3-state outputs for bus oriented applications. A clock (CP) and an output enable (OE) input are common to all flip-flops.

The 8 flip-flops will store the state of their individual D-inputs that meet the set-up and hold time requirements on the LOW-to-HIGH CP transition.

When OE is LOW, the contents of the 8 flip-flops are available at the outputs. When OE is HIGH, the outputs go to the high impedance OFF-state. Operation of the OE input does not affect the state of

The "574" is functionally identical to the "564", but has non-inverting outputs. The "574" is functionally identical to the "374", but has a different pinning.

the flip-flops.

| SYMBOL                    | PARAMETER                                 | CONDITIONS                                      | TYPICAL |                 |      |

|---------------------------|-------------------------------------------|-------------------------------------------------|---------|-----------------|------|

|                           |                                           | CONDITIONS                                      | нс      | нст             | UNIT |

| tPHL/<br><sup>T</sup> PLH | propagation delay<br>CP to Q <sub>n</sub> | C <sub>L</sub> = 15 pF<br>V <sub>CC</sub> = 5 V | 14      | 15              | ns   |

| fmax                      | maximum clock frequency                   | VCC = 5 V                                       | 123     | 76              | MHz  |

| cı                        | input capacitance                         |                                                 | 3.5     | 3.5             | pF   |

| C <sub>PD</sub>           | power dissipation capacitance per package | notes 1 and 2                                   | 22      | <sup>2</sup> 25 | pF   |

GND = 0 V;  $T_{amb}$  = 25 °C;  $t_r = t_f = 6$  ns

#### Notes

1. CPD is used to determine the dynamic power dissipation (PD in  $\mu$ W):

PD = CPD ×  $VCC^2$  ×  $f_1$  +  $\Sigma$  (CL ×  $VCC^2$  ×  $f_0$ ) where:

fi = input frequency in MHz f<sub>0</sub> = output frequency in MHz Ct = output load capacitance in pF VCC = supply voltage in V

$\Sigma$  (C<sub>L</sub> x V<sub>CC</sub><sup>2</sup> x f<sub>0</sub>) = sum of outputs

2. For HC the condition is V<sub>I</sub> = GND to V<sub>CC</sub>

For HCT the condition is V<sub>I</sub> = GND to V<sub>CC</sub> - 1.5 V

#### ORDERING INFORMATION/PACKAGE OUTLINES

PC74HC/HCT574P: 20-lead DIL; plastic (SOT-146). PC74HC/HCT574T: 20-lead mini-pack; plastic (SO-20; SOT-163A).

| PIN NO.                           | SYMBOL                           | NAME AND FUNCTION                         |

|-----------------------------------|----------------------------------|-------------------------------------------|

| 1                                 | ŌĒ                               | 3-state output enable input (active LOW)  |

| 2, 3, 4, 5,<br>6, 7, 8, 9         | D <sub>0</sub> to D <sub>7</sub> | data inputs                               |

| 10                                | GND                              | ground (D V)                              |

| 11                                | CP                               | clock input (LOW-to-HIGH, edge-triggered) |

| 19, 18, 17, 16,<br>15, 14, 13, 12 | Q <sub>0</sub> to Q <sub>7</sub> | 3 state flip flop outputs                 |

| 20                                | V <sub>CC</sub>                  | positive supply voltage                   |

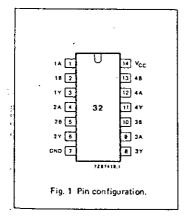

TUAD 2-INPUT OR GATE

Couput capability: standard

GENERAL DESCRIPTION

The 74HC/HCT32 are high-speed

Space CMOS devices and are pin

compatible with low power Schottky

TTL (LSTTL). They are specified in

compliance with JEDEC standard no. 7A. The 74HC/HCT32 provide the 2 input OR function.

| SYMBOL          | PARAMETER                                 | CONDITIONS                                     | TY  | TYPICAL |      |

|-----------------|-------------------------------------------|------------------------------------------------|-----|---------|------|

| 3111100         | ranameter                                 | CONDITIONS                                     | нс  | нст     | UNIT |

| фн∟/<br>¹PLH    | propagation delay<br>nA, nB to nY         | C <sub>L</sub> = 15 pF · V <sub>CC</sub> = 5 V | 6   | 9       | лs   |

| Ci              | input capacitance                         |                                                | 3.5 | 3.5     | pF   |

| C <sub>PD</sub> | power dissipation<br>capacitance per gate | notes 1 and 2                                  | 16  | 28 _    | pF   |

GND = 0 V;  $T_{amb}$  = 25 °C;  $t_r$  =  $t_f$  = 6 ns

#### Notes

1. CPD is used to determine the dynamic power dissipation (P  $\stackrel{\cdot}{D}$  in  $\mu W):$

PD = CPD ×  $VCC^2$  ×  $f_i$  +  $\Sigma$  (CL ×  $VCC^2$  ×  $f_0$ ) where:

$C_L$  = output load capacitance in pF  $V_{CC}$  = supply voltage in V

$f_i$  = input frequency in MHz  $C_L$  = or  $f_0$  = output frequency in MHz  $V_{CC}$  = su  $\Sigma$  ( $C_L \times V_{CC}^2 \times f_0$ ) = sum of outputs 2. For HC the condition is  $V_I$  = GND to  $V_{CC}$  = For HCT the condition is  $V_I$  = GND to  $V_{CC}$  - 1.5  $V_{CC}$

#### ORDERING INFORMATION/PACKAGE OUTLINES

PC74HC/HCT32P: 14-lead DIL; plastic (SOT-27). PC74HC/HCT32T: 14-lead mini-pack; plastic (SO-14; SOT-108A).

| PIN NO.      | SYMBOL   | NAME AND FUNCTION       |

|--------------|----------|-------------------------|

| 1, 4, 9, 12  | 1A to 4A | data inputs             |

| 2, 5, 10, 13 | 1B to 4B | data inputs             |

| 3, 6, 8, 11  | 1Y to 4Y | data outputs            |

| 7            | GND      | ground (0 V)            |

| 14           | Vcc      | positive supply voltage |

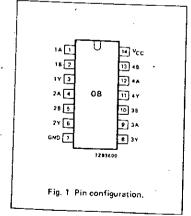

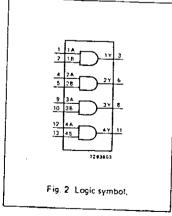

# QUAD 2-INPUT AND GATE

#### **FEATURES**

- Output capability: standard

- ICC category: SSI

#### GENERAL DESCRIPTION

The 74HC/HCT08 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT08 provide the 2-input AND function.

| SYMBOL                                | PARAMETER                                 | CONDITIONS                                      | TYPICAL |     |      |

|---------------------------------------|-------------------------------------------|-------------------------------------------------|---------|-----|------|

|                                       |                                           | COMBINIONS                                      | HC      | нст | UNIT |

| <sup>1</sup> PHL/<br><sup>1</sup> PLH | propagation delay<br>nA, nB to nY         | C <sub>L</sub> = 15 pF<br>V <sub>CC</sub> = 5 V | 7       | 11  | ns   |

| C <sub>I</sub>                        | input capacitance                         |                                                 | 3.5     | 3.5 | pF   |

| C <sub>PD</sub>                       | power dissipation<br>capacitance per gate | notes 1 and 2                                   | 10      | 20  | př   |

GND = 0 V;  $T_{amb} = 25$  °C;  $t_r = t_f = 6$  ns

#### Notes

- 1. CPD is used to determine the dynamic power dissipation (PD in  $\mu$ W):

- PD = CPD × VCC<sup>2</sup> × f<sub>1</sub> +  $\Sigma$  (CL × VCC<sup>2</sup> × f<sub>0</sub>) where:

- Ct = output load capacitance in pF VCC = supply voltage in V

- $\begin{aligned} & \text{FD} = \text{CPD} \times \text{VCC} & \text{X | } \text{Y } \text{Z | } \text{CL} \times \text{VCC} & \text{A | } \text{O | } \text{Witter} \\ & \text{f}_{0} & = \text{ input frequency in MHz} & \text{CL} & = \text{o}_{0} \\ & \text{S} \times \text{CC} \times \text{VCC}^{2} \times \text{f}_{0} \text{)} = \text{sum of outputs} \\ & \text{2. For HC} & \text{the condition is V}_{1} = \text{GND to VCC} \\ & \text{For HCT the condition is V}_{1} = \text{GND to VCC} 1.5 \text{ V} \end{aligned}$

# ORDERING INFORMATION/PACKAGE OUTLINES

PC74HC/HCT08P: 14-lead DTL; plastic (SOT-27), PC74HC/HCT08T: 14-lead mini-pack; plastic (SO-14; SOT-108A),

| PIN NO.                                         | SYMBOL                                         | NAME AND FUNCTION                                                         |

|-------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|

| 1, 4, 9, 12<br>2, 5, 10, 13<br>3, 6, 8, 11<br>7 | 1A to 4A<br>1B to 4B<br>1Y to 4Y<br>GND<br>VCC | data inputs data inputs data outputs ground (0 V) positive supply voltage |

## DUAL 2-TO-4 LINE DECODER/DEMULTIPLEXER

- Demultiplexing capability

- Two independent 2-to-4 decoders

- Multifunction capability

- Active LOW mutually exclusive outputs

- Output capability: standard

- 1<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

The 74HC/HCT139 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

The 74HC/HCT139 are high-speed, dual 1-to-4 line decoder/demultiplexers. This device has two independent decoders, each accepting two binary weighted inputs (nA0 and nA1) and providing four mutually exclusive active LOW outputs (n\(\tilde{V}\)) to n\(\tilde{Y}\)4). Each decoder has an active LOW enable input (n\(\tilde{E}\)).

When nE is HIGH, every output is forced HIGH. The enable can be used as the data input for a 1-to-4 demultiplexer

application.

The "139" is identical to the HEF4556 of the HE4000B family.

| SYMBOL          | PARAMETER                                          | CONDITIONS                                      | TY       | TYPICAL  |          |

|-----------------|----------------------------------------------------|-------------------------------------------------|----------|----------|----------|