الجمهورية الجزائرية الديمقراطية الشعبية REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التمليسم المسالي والبحث الملمسي

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

### المدرسة الوطنية للعلوم الهندسية ECOLE NATIONALE POLYTECHNIQUE D'ALGER

DEPARTEMENT D'ELECTRONIQUE

PROJET DE FIN D'ETUDES

### THEME

Etude et réalisation d'un prototype de microordinateur 1° partie Unité centrale memoire centrale

Proposé par :

Etudié par :

Dirigé par :

M. A. BOURKEB

M. D. BOUARAB Mr. A. BOURKEB

M. R. KERMOUCHE

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

# المسلامية الوطنية للعلموم الهندسية ECOLE NATIONALE POLYTECHNIQUE D'ALGER

DEPARTEMENT D'ELECTRONIQUE

PROJET DE FIN D'ETUDES

### THEME

Etude et réalisation d'un prototype de microordinateur 1° partie Unité centrale memoire centrale

Proposé par :

Etudié par :

Dirigé par :

M. A. BOURKEB

M. D. BOUARAB

Mr. A. BOURKEB

M. R. KERMOUCHE

A la mémoire de mon pére A la mémoire de ma mére A mes sœurs

Djamal.

A mes parents

A mes fréres

A mes sœurs

Rachid.

#### -o- Remerciements -o-

Nous remercions:

M.BOURKEB pour le sujet qu'il nous a proposé, pour son suivi attentif et ses conseils judicieux.

Les membres du laboratoire maintenance, M.elle AOUANOUK, M.FEGUAS; M. HADDAD pour leur esprit cooperatif

Les membres du laboratoire photogravure pour tous les services rendus.

${ t M}^{ ext{ine}}$  DJOUDI et Samia pour la méticulosite de leur travail de frappe.

M.CHEBAH qui réalisé le tirage du polycope.

Que tous les professeurs qui ont contribué à notre formation trouvent ici l'éxpression de notre gratitude.

### Sommaire

| -Introduction1                      |

|-------------------------------------|

| Géneralites                         |

| 1. Historique                       |

| 2. Applications                     |

| 3. Choix d'une configuration4       |

| 4Schéma synoptique géneral5         |

| 5. Présentation du microordinateur6 |

|                                     |

| Unité centrale                      |

| Introduction8                       |

| Synoptique CPU9                     |

| 1.MPU                               |

| 2.Interfaçage des bus               |

| 3.Interface série asynchrone/17     |

| 4. Gircuits d'initialisation23      |

| 5.CIRCUIT d'horloge24               |

| 6.Organisation du champ mémoire25   |

| 7. Logique de décodage26            |

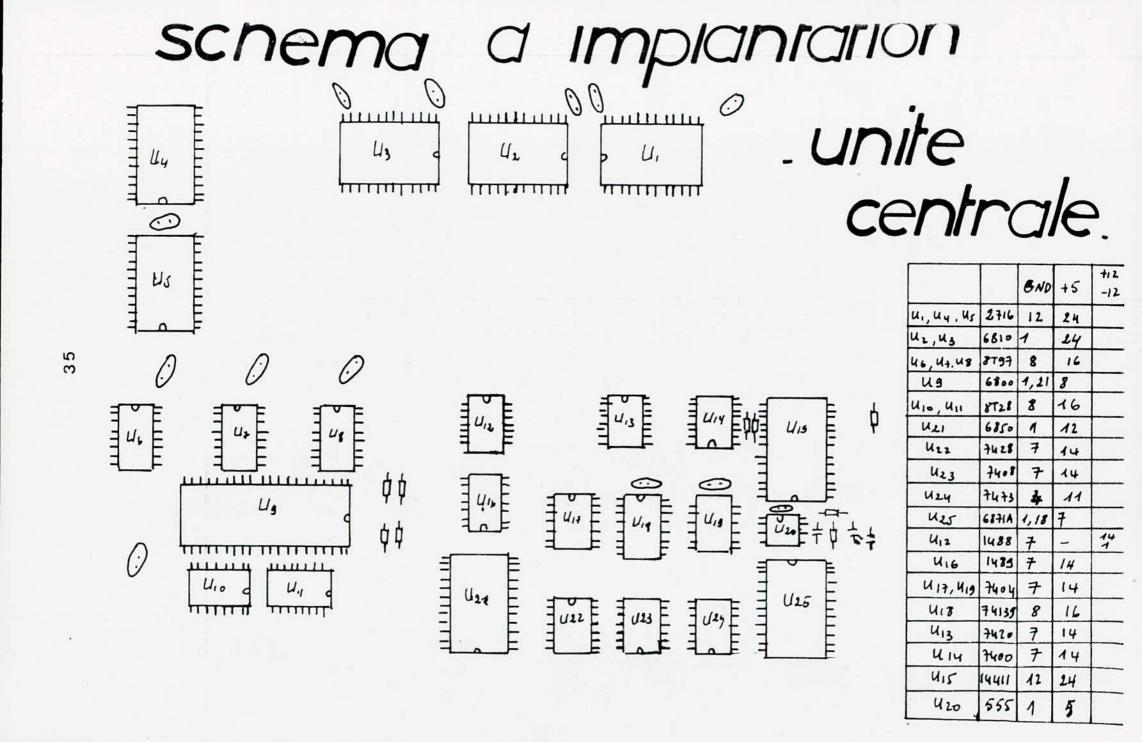

| 3. Schéma d'implatation CPU         |

| O. Conclusion                       |

|                                     |

|                                     |

| Mémoire centrale                    |

| .Introduction                       |

| 2. Géneralites38                    |

| 5. Trigger de schmitt41             |

| Synoptique mémoire centrale42       |

| Logique de décodage43               |

|                                     |

|                                     |

55

..../....

| 6.Rafrai  | chissement     | <br>• |   | • |   |     |     |   |   | e |  | 0 | . 4 | 19 |

|-----------|----------------|-------|---|---|---|-----|-----|---|---|---|--|---|-----|----|

| 7.Schéma  | d'impantation. |       |   |   | • | , , | , , |   | • |   |  | • | .5  | 55 |

| 8.Conclus | sion           | <br>• | 0 | e |   |     |     | o |   | , |  | • | .5  | 6  |

|           |                |       |   |   |   |     |     |   |   |   |  |   |     |    |

Conclusion

Annexe

-=-=000- I N T R O D U C T I O N -000=-=-

#### INTRODUCTION.

La micro - informatique exerce aujourd'hui une macro-influence sur la vie économique et sociale. Depuis la sortie du 1º microordinateur,

L'Atlair en 1975, ce secteur a connu une évolution très rapide Désormais aucun domaine de l'activité humaine ne peut échapper à l'informatisation.

Le Marché de la micro-informatique est dominé actuellement par quelques "multinationales" et aucun transfert de technologie vers les pays sous - développés ne s'est accompli.

En Algérie plusieurs réalisations de micro-ordinateurs ont été faites, mais toutes sont restées au stade du prototype.

Maquettes en Wrapping, systême modulaire nécessitant une précision accrue dans la réalisation et un prix de revient excéssivement élevé ont empêche la fabrication en série et par suite la diffusion du produit.

Le projet que nous a confié le service électronique du CEN est ambitieux. Il s'agit de réaliser un prototype de micro-ordinateur monocarte sur circuit imprimé double face. Le choix de cet te configuration permettra une fabrication en série avec un prix de revient abordable. Ce micro-ordinateur étant destiné à la petite et moyenne industrie ainsi qu'aux établissements scolaires ses caractéristiques sont celles réservées traditionnellement à ce secteur. A savoir une mémoire morte de 3 Ko contenant le moniteur, une mémoire vive de 48 Ko, une interface disque souple et une interface entrée/sortie.

Le projet a été étudié par 2 binômes et notre travail était de réaliser l'unité centrale et la mémoire de 48 Ko.

-=-=-000-= G E N E R A L I T E S =-000-=-=-

#### 1 - HISTORIQUE :

La naissance en 1970 chez Intel du 1er microprocesseur, le 4004, fût saluée come l'évenement le plus marquant de la dernière décennie. En effet jamais invention n'a bouleversé les structures sociales aussi profondément, aussi radicalement que ne le fait actuellement la micro-informatique.

Dores et déjà notre époque est baptisée "âge du microprocesseur coune on la fait pour l'âge de pièrre" et l'âge de bronze".

Le "Time" de janvier 1982 a été jusqu'à désigner coame homme de l'année .....le microordinateur.

Cette informatisation massive de la société est dûe aux immenses progrés technologiques accomplis ces dernières années et à la baisse spéctaculaire des prix.

En 1982, la Leme génération de microprocesseur, les 32 bits, a vulle jour et maintenant on pense déjà au microordinateur intégré sur une seule "puce" ?

### 2 - APPLICATIONS :

Le champ d'application des microprocesseurs ne cesse de s'etendre. En Industrie, le contrôle des processus, le filtrage numérique, la régulation des parametres, la commande d'éléctro-vannes sont confiés à un microprocesseur, le prix du métérnel étant nettement inférieur à celui du lognaiel on pretèré alors construire des potits systèmes spécialisés dans telle ou telle fonction.

Le microprocesseur a fait aussi son apparition dans les foyers. Machine i laver programmable, four à micro-ondes, microordinateur fa illial et bien d'autres "gadjets" font désormais partie intégrante de notre environnement.

#### 3 - CHOIX DU MICROPROCESSEUR :

Passer du schéma de principe à une réalisation pratique est une tâche ardue, tant elle demande des moyens matériels importants, une connaissance parfaite de l'éléctronique digital et un savoir faire dont seule l'expérience et une pratique continu peuvent l'acquérir;

L'expérience que le service électronique du CEN possède en ce domaine nous fût précieuse, a guidé notre travail et nous a évité les tatonnements.

Le choix du microprocesseur était une étape importante, entre le 16 bits 68000 de motorola, le 6809 et le 6800 nous avons préfère ce dernier.

Le 6800 est un microprocesseur très utilisé, disponible au niveau du CEN, maitrisable et plusieurs projets l'on adopté.

L'existence du système de développement du 6800 a été déterminant quant a son choix car réaliser le hardiware et le softeware en 3 mois par des personnes non initiées est une utopie.

Le but de notre projet était de réaliser un microordinateur pour la PMI, on a évité ainsi le spectaculaire dont le prix de revient est élevé et "l'original sur papier".

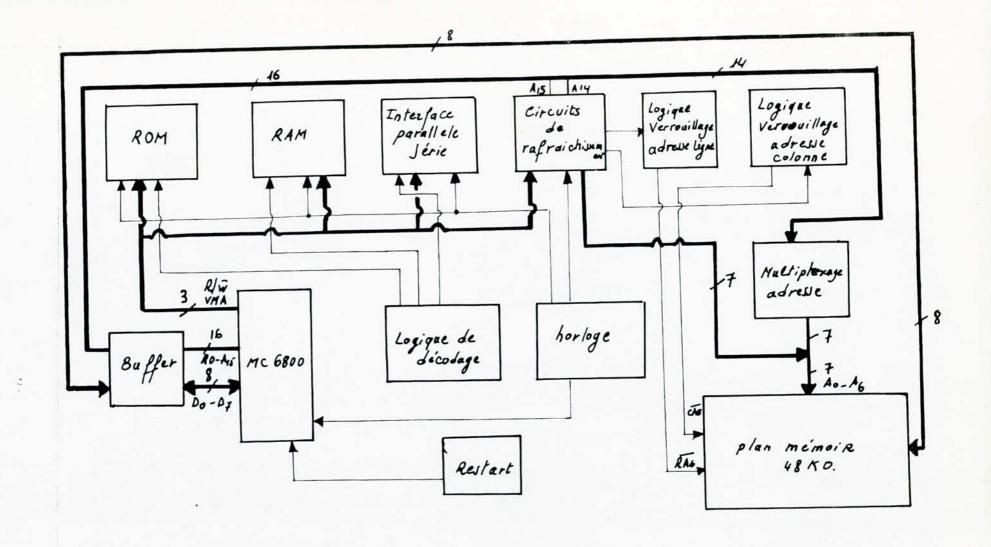

# SYNOPTIQUE GENERAL

(2)

### 4 - PRESENTATION DU MICROORDINATEUR :

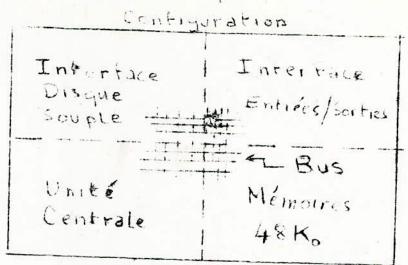

Le microordinateur dont on nous a confié la réalisation à une configuration assez particulière. C'est un "monocarte à pséudo-modularité et comprend les quatre parties essentielles, le CPU, la mémoire centrale, le controleur de disque souple et une interface entrée/ sortie.

Le système "multicartes" est un ensemble de cartes compatibles de mêmes dimensions et s'assemblent par l'intermédiaire d'un "panier". Avec ce système l'extension et le dépannage sont faciles mais sa réalisation exige une grande finition, l'achat de connecteurs onéreux et non disponibles et une main d'ocuvre qualifié, tout ceci grêffe lourdement le prix de revient du microordinateur.

Le monocarte, lui, est un système figé non évolutif difficile à dépanner.

Notre système se situe entre ces 2 cas extrêmes, ainsi on allie les avantages des deux tout en éléminant leurs inconvenients. L' étude du système a été faite carte par carte ainsi la localisation de la panne est plus facile.c'est un système évolutif, il suifit de changer la carte dont les perfomances sont insuffisantes avec une seule contrainte, ramener le bus en entier dans le "coin" de la carte.

Le système présente plusieurs avantages : économie de connecteurs, de vissérie, de panier, plus compact, gain sur le temps d'assemblage.

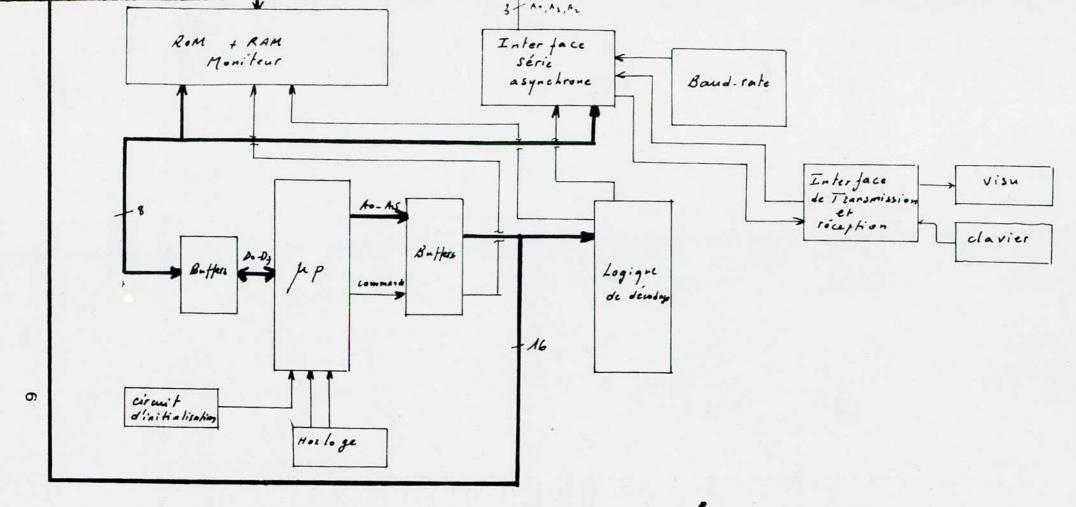

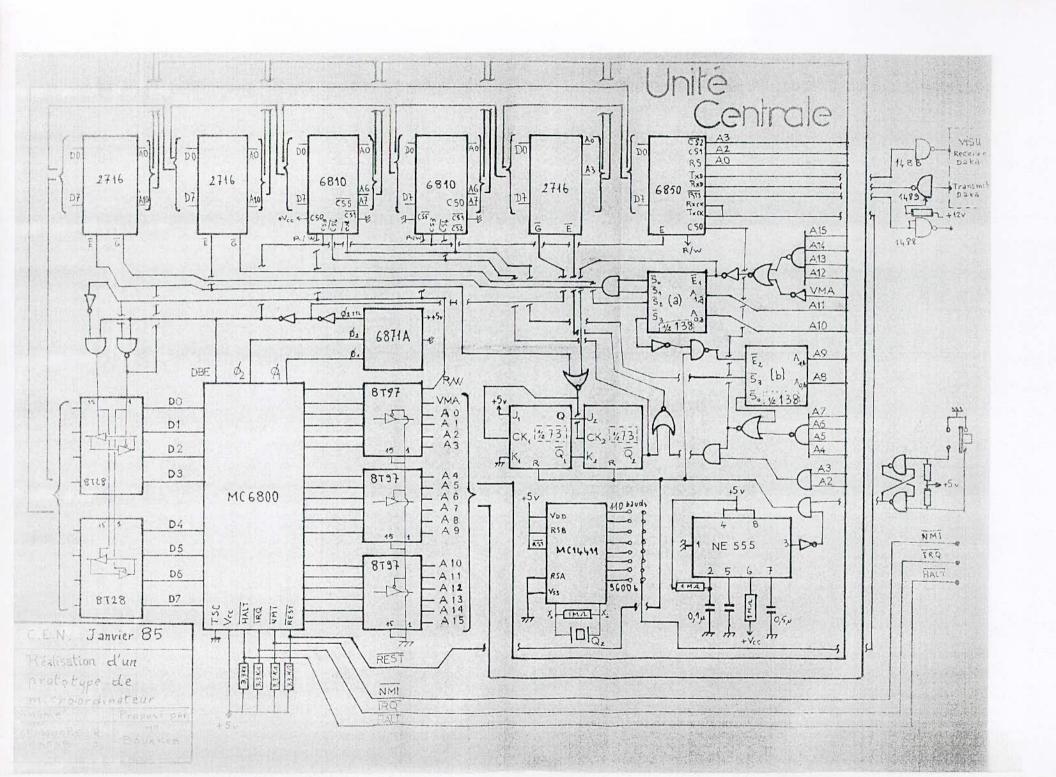

#### Introduction

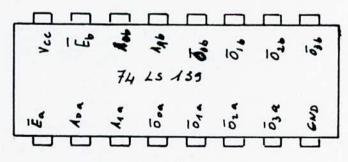

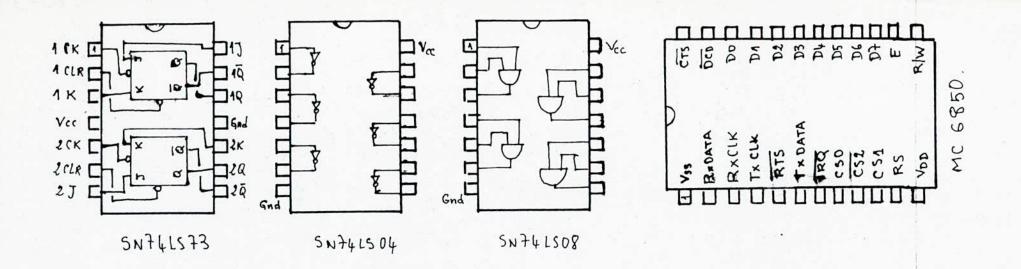

L'unitè centrale comprend outre le micropro--cesseur MC6800, des buffers d'extension, une memoire morte de 3Ko, une memoire vive de 2K bits, une logique de dècodage, une interface série asynchrone.

Elle a èté réalisée sur circuit imprime double face et permet la **gest**ion des trois autres parties, à savoir une mémoire de 48Ko, une interface disque souple, une entrée/sortie parallele/série, série/parallele.

Dans les pages qui suivent on étudiera en détail les differentes parties du CPU et on donnera le shema de principe, le circuits imprimè et le schema d'implantation.

synoptique de l'unité centrale

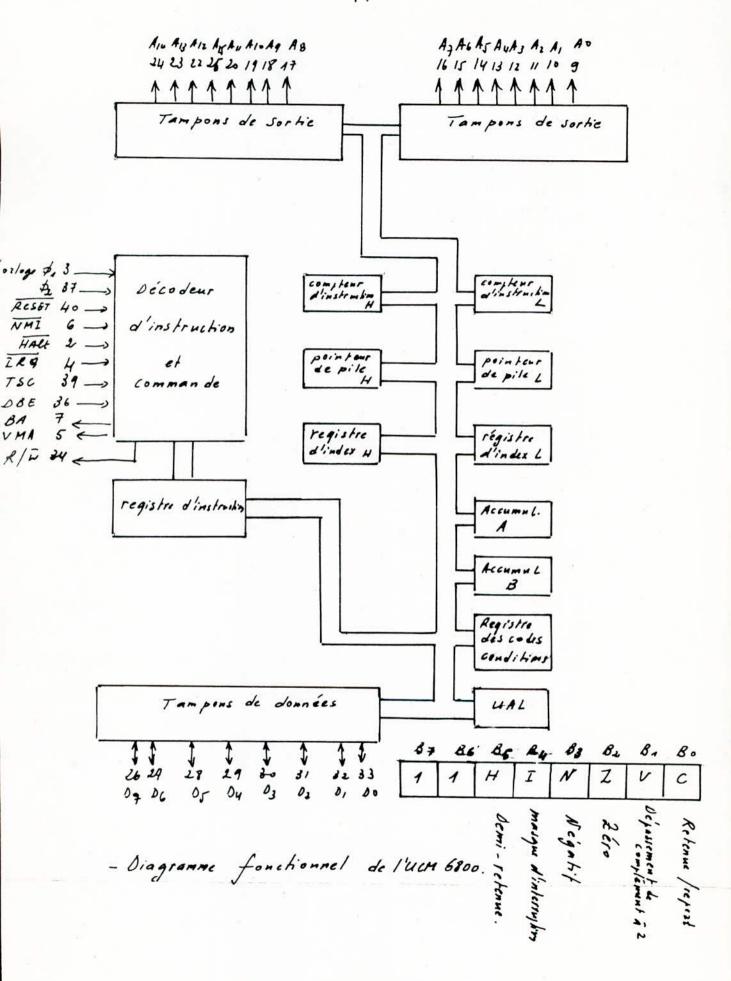

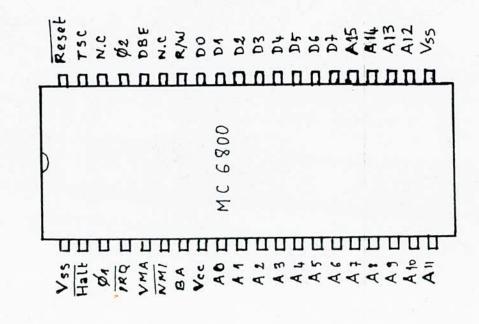

#### 1. le M.P.U

### 1.1 Z NTRODUCTION

Motorola corp. a introduit son wnicroprocesseur M.C 6800 vers le milieu des années soixante-dix. depuis ce constructeur a mis au point la famille 6800 à bases de nouvelles puces plus élaborées qui sont généralement compatibles au niveau logiciel et dans une moindre mesure au niveau matériel avec L'U.C.M 6800.

Le M.C 6800 a des performances modestes, mais il est fiable, disponible et une documentation abondante existe a son sujet. l'existence de plusieurs secondes sources est une garantie supplémentaire. Nous rappelons bievements ses différentes caractéristiques.

### 1.2 Les SIGNAUX DU 6800

Le M.C 6800 est un microprocesseur à 8 bits logé sur D.Ilà 40 broches. L'U.C.M type opère avec une fréquence d'horloge de 1 M H Z.

Il se caractérise par une

- Compatibilité T.T.L directe

- Alimentation monotension

- Capacité d'adressage 64 K.O par bus d'adresse 16

- Bus de donnée : bidirectionnel à 8 bits

- Technologie N M.O.S

#### - Halt ( broche 2)

contrée Halt est active, le 6800 entre en mode arrêt, les circuits trois états pascent à leur état haute impédance et le processeur stoppe. Elle est utilisée pour parcourir un programme pas à pas au cours de la mise au point d'un programme. Elle est dans notre unité centrale mise à l'état haut par commexion au + V cc.

### - Horloge Ø 1 , Ø 2

L'unité centrale exige deux phases d'horloge sans recouvrement.

### - V.M.A ( Validation d'adresse mémoire )

Quand la sortie V.M.A passe à 1 elle rignale aux autres unites du système que l'adresse portée par le bus d'adresse est stable.

#### - B.A ( Bus Disponible)

Quand la sortie B.A passe à 1, elle signale aux unités externes que le 6800 a stoppé l'exécution d'instruction le 5800 stoppe l'exécution par suite d'une instruction W.A.I.T on par entrée Halt. La ligne commande B.A permet de dire aux unités ecternes que les bus de données et d'adresse du 6800 sont en modes

### - Validation du bus de données D.B.E

Comme les transferts de données prennent place pendant le temps ou l'horloge Ø 2 est à l'état haut la broche D.B.E est connectée généralement à la ligne Ø=2 de l'horloge.

### T.S.C: Commande de mode trois états

Quand l'entrée T.S.C est placéen "HIGH" par une unité externe toutes les lignes d'adresse et la ligne R/W passe en mode haché impédace. Dans notre système on n'utilise pas de D.M.A et la broche T.S.C est à la masse.

### Les Commandes d'Interruption

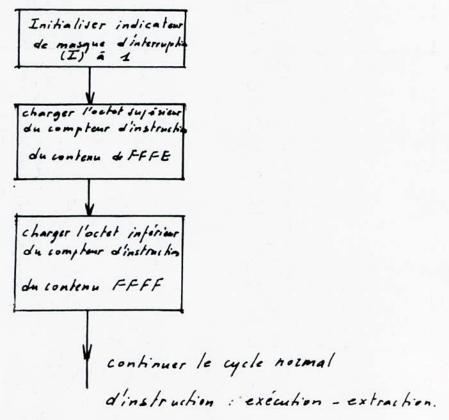

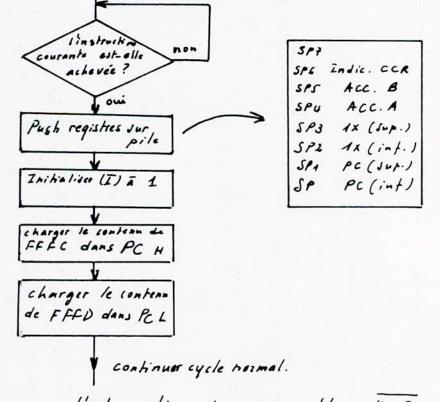

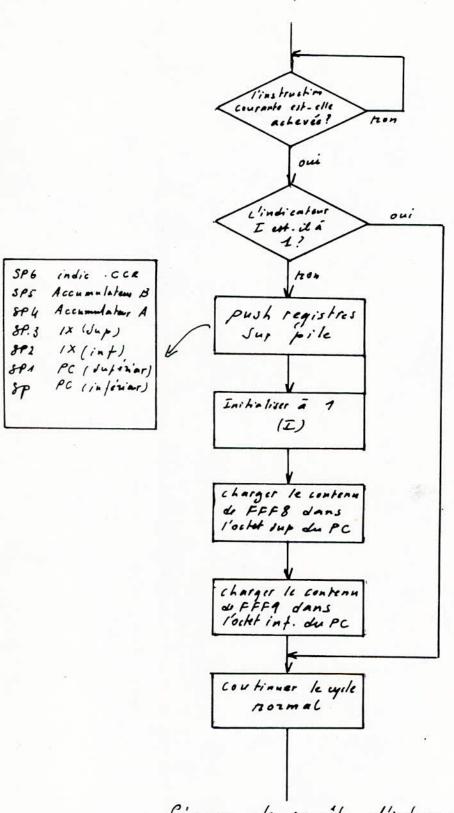

Le M.C 6000 posséde 4 types d'intérruption dont 3 matériels et une logicielle et qui sont par ordre de priorité décroissante : R.E.S.E.T , N.M.I , I.R. Ø , S.W.I . Dans les pages qui suivent on donne les organigrammes des trois interruptions matériels.

### Commande de lecture / Ecriture R/W

La sortie  $R/\bar{W}$  est une ligne de commande permettant de faire une opération de leçture (  $R/\bar{W}$  à 1 ) ou une opération d'écriture (  $R/\bar{W}$  à 0 ).

- Réquence de téinitialisation d'interruption: Reset

- Sequence d'interruption ton masquable: KMI

- l'équence de requête d'interruption

### 2 - INTERFACAGE DES BUS :

### 2 - 1 NOTION D'ENTRANCE ET DE SORTANCE

On définit ces 2 notions comme suit:

- ENTRANCE : C'est la valeur du courant de commande exprimée en une unité qui est le courant de commande typique de la famille.

- SORTANCE : C'est le rapport entre le courant maximum fourni par le circuit et le courant de commande typique.

Par exemple un circuit qui a une sortance de 2 peut commander 2 circuits qui ont une entrance de 1.

Le microprocesseur possède au niveau de toutes ses lignes de sortie une sortance faible, d'une charge T.T.L, on voit qu'il est nécessaire de "bufferiger" les signaux pour toute utilisa+u tion ou le nombre de circuits est important.

#### 2 - 2 LES BUFFERS :

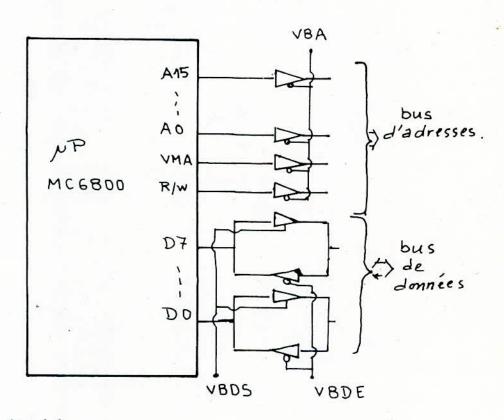

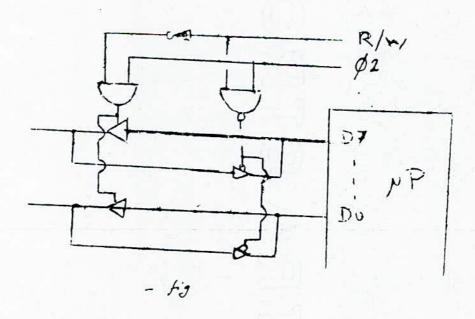

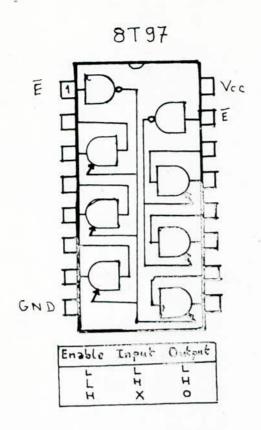

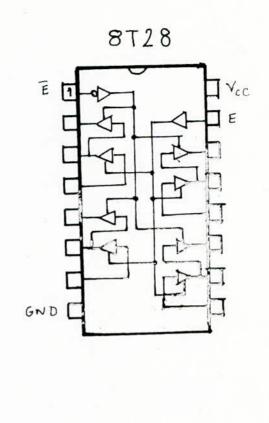

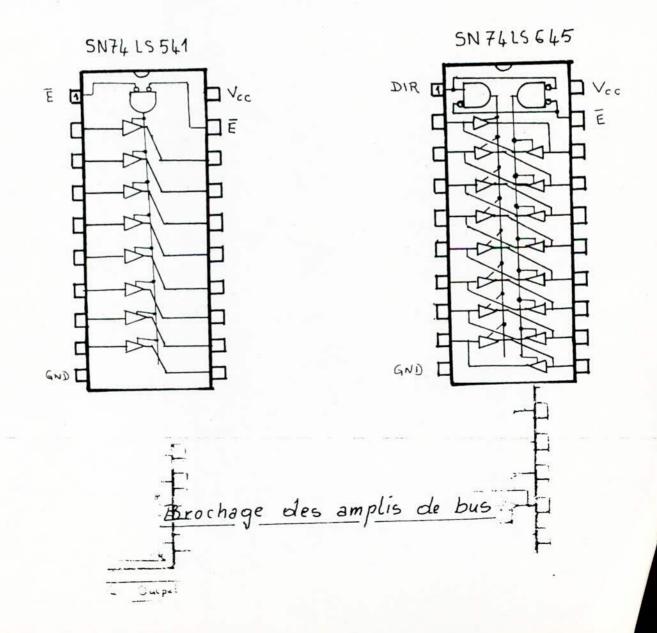

On utilise 2 sortes de buffers les unidirectionnels pour le bus d'adresses, les bidirectionnels pour le bus de données. (voir fiq2.2).

Apart V.M.A et R/W les autres signaux de commandes ne sont pas "bufferisés" car n'étant pas beaucoup utilisés.

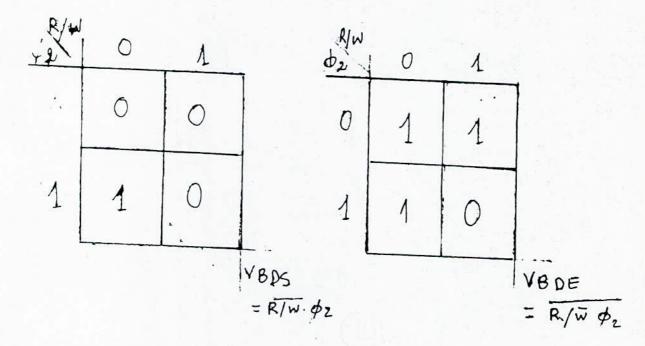

Notre système n'étant pas prévu pour un accés direct en mémoire, les buffers du bus d'adresses sont validés en permanence et V.B.A est mise à la masse!Le sens du transfert des données est déterminé par l'opération effectuée:lecture ou écriture ; 2 signaux de commande pour déterminer ce sens :

Ø2 :ne permet de valider les buffers du bus de données que pendant le transfert Ø2 = 1.

R/W; Pour differencier entre une lecture et une écriture.

fig 2.2. Validation des amplis de bus.

VBA: Validation du Bus d'Adresses.

VBDE: = = de Données Entrée.

VBDS: Sortie.

Lecture R/W = 1 et  $\emptyset$  2 = 1

Ecriture R/w = 0 et  $\emptyset$  2 = 1

Ni lecture, ni écriture  $\emptyset_{2}=0$ pas d'échange avec le micro Etat haute impédance.

D'après la figure précédente pour avoir :

Une lecture : V.B.D.S = O et V.B.D.E =

Ecriture : V.B.D.S = 1 et V.B.D.E = 1

Etat haute impédance : V.B.D.S = 0 et V.B.D.E = 1

Les circuits utilisés pour le renfircement des bus sant les 8 T 28 ( bidirectionnels ) et les 8 T 97 ( unidirectionnels), voir schémas et brochage en annexe.

#### 3.I. - INTRODUCTION :

Une interface série est nécessaire pour communiquer avec un périphérique travaillant en mode série ; tele type, clavier série, imprimente série , modem, terminal de visualisation, enregistreur à cassettes.

NORME RS 232 C.

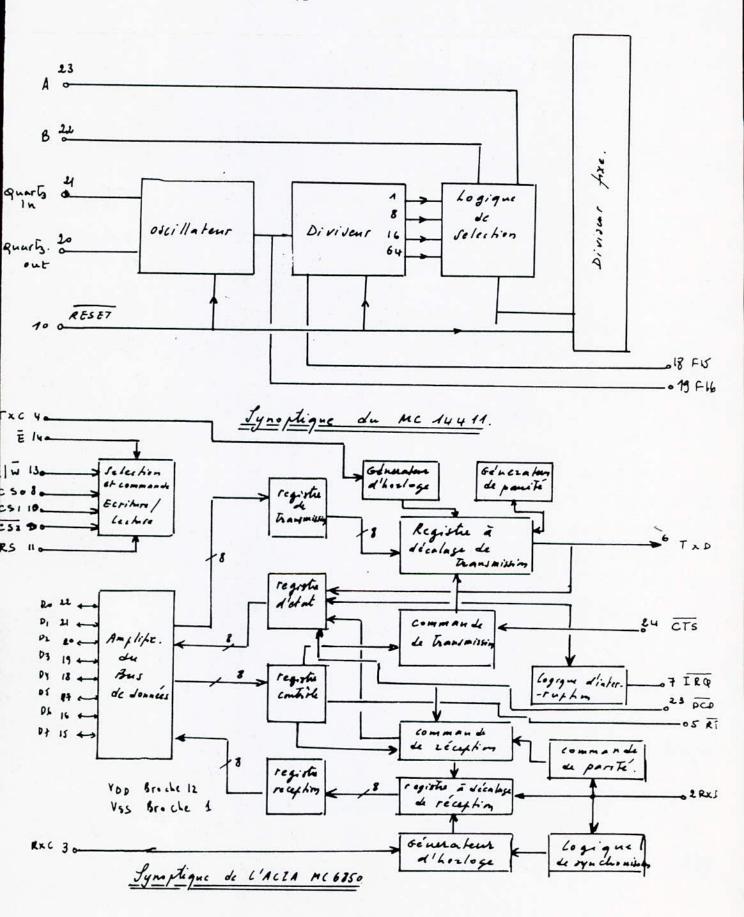

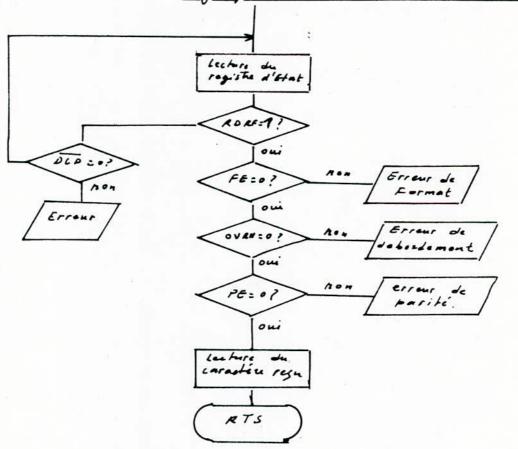

#### 3.2. - L'ACIA 6850.

Le MC 6850 est une interface série programmable asynchrone réalisée en technologie N.MOS et s'alimente sous une tencion unique +5V.Toutes les entrées/feortiles sont compatibles TTL.

L'ACIA dispose, côte microprocesseur, de trois lignes de validation de boitiers CSO, CSI, CS2, une ligne d'activation E reliée à  $\not \! D2$ , une ligne R/W, une entrée RS selection des registres internes, une ligne d'interruption IRQ et un bus de données.

Côte périphérique on trouve une sortie transmission série TXD, une entrée reception RXD, avec horloges indépendantes TXC et RXC et trois lignes contrôle modem CTS, RTS, DCD.

L'ACIA possède quatre registres internes dont deux à lectures seulement, le registre d'état SR et le registre de réception RDR, et 2 à écriture seulement. Le registre d'émission TDR, registre contrôle CR. La ligne RS et la ligne R/W déterminent le registre Selecté.

| R.S. |   | R/W |   | Registre Selecté | 9    |

|------|---|-----|---|------------------|------|

| 0    | 8 | 0   | : | C.R.             | - 00 |

| 0    | 3 | I   | 0 | S.R.             | :    |

| I    | 8 | 0   | 8 | TDR.             |      |

| I    |   | I   | 8 | RDR.             | 0    |

| lor.        | Jah<br>s d'i | ne recep                                         | hon                                                                  |                                         |            | R      | x C   | de di<br>e | 6 T                          | k c                                           |                                  |

|-------------|--------------|--------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------|------------|--------|-------|------------|------------------------------|-----------------------------------------------|----------------------------------|

| CR7         | _            | Fonch                                            |                                                                      |                                         |            | CRO    | CRI   | Rop        | post de                      | division                                      |                                  |

| 1           | pro          | de les inte<br>voquees p<br>gistre reco          | ruphims                                                              |                                         |            | -      |       | - '        |                              |                                               |                                  |

|             | .00          | gistre reu                                       | those plais                                                          |                                         |            | 0      | 0     |            | - 1                          |                                               |                                  |

|             | . Fz         | nt montan                                        | t ser oco                                                            |                                         |            | 0      | 4     |            | ÷ 16                         |                                               |                                  |

|             |              |                                                  |                                                                      |                                         |            | 1      | 0     |            | ÷ 14                         | 2.0                                           |                                  |

| 0           | Inhi         | be les in                                        | erruphons                                                            |                                         |            | 1      | 1     | ma         | ster re                      | ser.                                          |                                  |

|             | -            |                                                  |                                                                      |                                         |            |        |       |            | L.,                          |                                               |                                  |

|             |              |                                                  |                                                                      |                                         | -          |        | _     |            |                              |                                               |                                  |

|             |              | 4                                                |                                                                      |                                         |            |        | 4     |            |                              |                                               |                                  |

|             |              |                                                  |                                                                      |                                         | 1          |        | esc   | Ruc        | es CR2                       | CR1 CRO                                       | 1                                |

|             |              |                                                  |                                                                      |                                         | CRTIC      | -20161 |       |            |                              |                                               |                                  |

|             |              |                                                  |                                                                      |                                         | CR7 C      | -20 61 |       |            | 75                           | 164. 1640                                     |                                  |

|             |              |                                                  |                                                                      |                                         | CRT        | - 20   |       |            | 7.0]0                        | CAV                                           |                                  |

|             |              |                                                  |                                                                      |                                         | CR7        | - 20   |       | _1_        | 1                            | -                                             |                                  |

| co. h       | ~1/          | <b>4</b>                                         | /                                                                    | Ļ                                       | <u>-</u> - |        |       |            |                              | -                                             | ]                                |

| conti       | ~1/e :       | des interr                                       | ig kins pi                                                           |                                         | <u> </u>   |        |       |            |                              | -                                             |                                  |

| par 14      | cond         | itim regist                                      | . Transmis                                                           | sin Vide                                | <u> </u>   |        |       |            |                              | es cchang                                     | g és                             |

| de la       | a sork       | it RTS em                                        | ssion be                                                             | isim Vide<br>reak                       | <u> </u>   | Fozi   | mat . | dos c      | aractéro                     | es cchang                                     | _                                |

| de la       | sork<br>O    | itim registive RTS cm                            | Transmis<br>ssion by<br>inhibe T                                     | uin Vide<br>reak<br>DRE                 | <u> </u>   | Fozi   | mat . | dos c      | aractéro                     | -                                             | 611                              |

| de la       | o sork       | itim registic RTS em                             | a Transmis<br>serion bi<br>inhibe T<br>valide T                      | uin Vide<br>reak<br>DRE<br>DRE          | <u> </u>   | Fozi   | mat . | dos c      | Longuer                      | es cchang                                     | gés<br>bill<br>sto               |

| ar /4 de // | o sork       | RTS:0 RTS:0 RTS:0 RTS:0 RTS:1                    | a Transmis<br>ssion br<br>inhibe T<br>Valide T<br>in hibe            | oin Vide<br>reak<br>DRE<br>TDRE<br>TDRE | <u> </u>   | Fozi   | mat . | dos c      | Longuer 7                    | es cchang                                     | 611                              |

| de la       | o sork       | ikim registic RTS em  RTS:0  RTS:0  RTS:1  RTS:0 | a Transmis<br>seion br<br>inhibe T<br>valide T<br>inhibe<br>inhibe T | ORE TORE TORE                           | <u> </u>   | Fozi   | cas   | des c      | Longuer                      | parité pairc                                  | 5/0                              |

| 0 0 A       | o sork       | ikim registic RTS em  RTS:0  RTS:0  RTS:1  RTS:0 | a Transmis<br>seion br<br>inhibe T<br>valide T<br>inhibe<br>inhibe T | ORE TORE TORE                           | <u> </u>   | Fozi   | cas   | des C      | Longuer 7                    | parité  paic  impaire                         | bil<br>sto                       |

| 0 0 A       | o sork       | RTS:0 RTS:0 RTS:0 RTS:0 RTS:1                    | a Transmis<br>seion br<br>inhibe T<br>valide T<br>inhibe<br>inhibe T | ORE TORE TORE                           | <u> </u>   | Fozi   | CR3   | caz        | Longueur<br>7                | parité  paire  paire  paire                   | 5/0,<br>2<br>2                   |

| 0 0 A       | o sork       | ikim registic RTS em  RTS:0  RTS:0  RTS:1  RTS:0 | a Transmis<br>seion br<br>inhibe T<br>valide T<br>inhibe<br>inhibe T | ORE TORE TORE                           | <u> </u>   | Fozi   | CRS   | CR2        | Longueur<br>7<br>7<br>7      | parité  paire  impaire  impaire  impaire      | 5/0<br>5/0<br>2<br>2<br>1<br>1   |

| 0 0 A       | o sork       | ikim registic RTS em  RTS:0  RTS:0  RTS:1  RTS:0 | a Transmis<br>seion br<br>inhibe T<br>valide T<br>inhibe<br>inhibe T | ORE TORE TORE                           | <u> </u>   | Fozi   | CRS   | CR2        | Longueur<br>7<br>7<br>7<br>7 | parité  parité  paire  impaire  impaire  sans | 5/0,<br>5/0,<br>2<br>2<br>1<br>1 |

| o o d       | o sork       | ikim registic RTS em  RTS:0  RTS:0  RTS:1  RTS:0 | a Transmis<br>seion br<br>inhibe T<br>valide T<br>inhibe<br>inhibe T | ORE TORE TORE                           | <u> </u>   | Fozi   | CRS   | CR2        | Longueur<br>7<br>7<br>7      | parité  paire  impaire  impaire  impaire      | 5/0,<br>5/0,<br>2<br>2<br>1      |

| 580   | RORF | 5R0:1          | registre de reaption plein ; SRO=0 vide                   |

|-------|------|----------------|-----------------------------------------------------------|

| 5.81  | TORE | SR1: 1         | registre transmissim vide, SRI = 0 plein                  |

| 281   | 000  | SR2:0          | la porteuse est présente, SRZ=1 porteuse perdue           |

| 5 % 3 | 523  | 5 <b>R3</b> :/ | lemodery n'est pas prêt, ski = o modern prêt              |

| 280   | FE   | SRU: 1         | Erreur de Format , SRY = 0 Format correct                 |

| 285   | OVEN | SR5 : 1        | recouvrement des carocheres , SRS = 0 pas de recouvrement |

| 286   | 90   | SR6 = 1        | erreur de parité, SR6=0 pas d'erreur                      |

| 587   | 632  | SR7: 1         | interruption SR7=0 pas d'interruption                     |

- fonctions des bits du registre d'état.

### 3.3. - MISE EN OEUVRE DE L'ACIA.

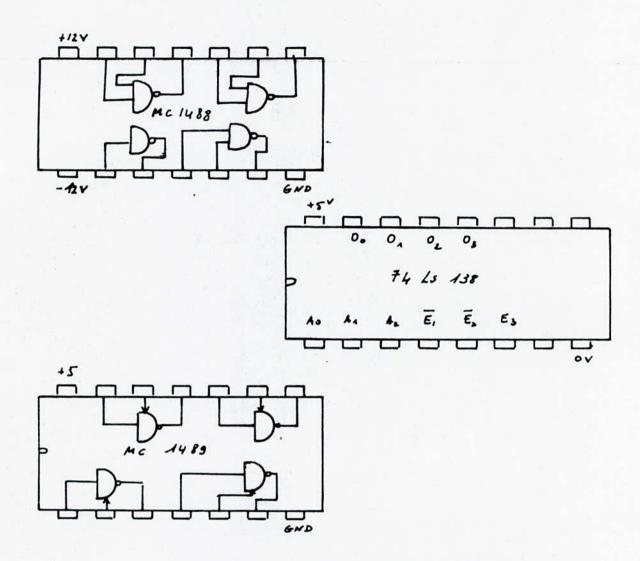

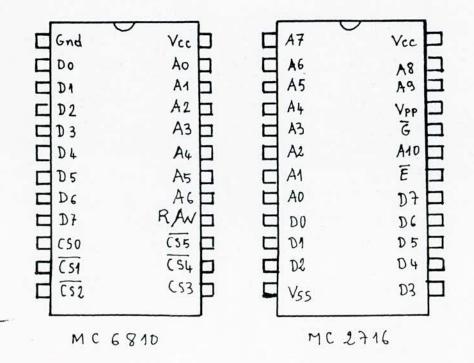

Un signal TTL est impropre à des liaisons par câble long (assimilé à um réseau RC). Deux circuits classiques les MC 1488 et MC 1489 assurent la conversion TTL RS 2326.

La RS 232C est l'une des normes la plus utilisé pour interconnecter un micro-ordinateur et un terminal, ses caractèristiques sont données en Annexe.

Les vitesses de transmission et de réception sont normalisées pour ces différents périphériques. Le circuit Band rate MC I44II permet de generer ces différentes fréquences et de piloter ainsi l'ACIA. On donne ci après les synoptiques de l'ACIA, du Band rate, Et la signification des bits du registre d'état et de contrôle.

### 3.4. - PROGRAMMATION DE L'ACIA.

La programmation de l'ACIA fait appel à 3 sous-programme, le sousprogramme d'intialisation, le sous programme d'émission et le sous-programme de réception.

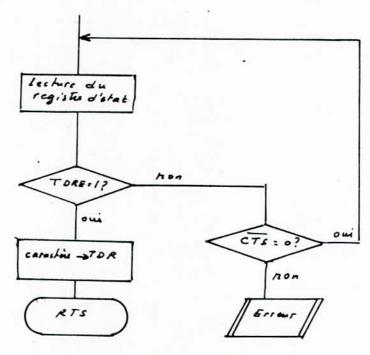

Ci-après les organigrammes des sous-programme d'émission et de réception.

organighamne de routine de transmission

organiquemme de routine de reugtion.

| Fo  | 9600      |     |         |

|-----|-----------|-----|---------|

| FI  | 7200      |     |         |

| FZ  | 4800      | (ex | bands.) |

| F3  | 3600      |     |         |

| Fu  | 2400      |     |         |

| FS  | 1800      |     |         |

| F6  | 1200      |     |         |

| F7  | 600       |     |         |

| F8  | 100       |     |         |

| F1  | 200       |     |         |

| F10 | 150       |     |         |

| FII | 134,5     |     |         |

| FIZ | 109,9     |     |         |

| FI3 | 75        |     |         |

| Fly | 921,6 K   |     |         |

| FU  | 4,8 432 H |     |         |

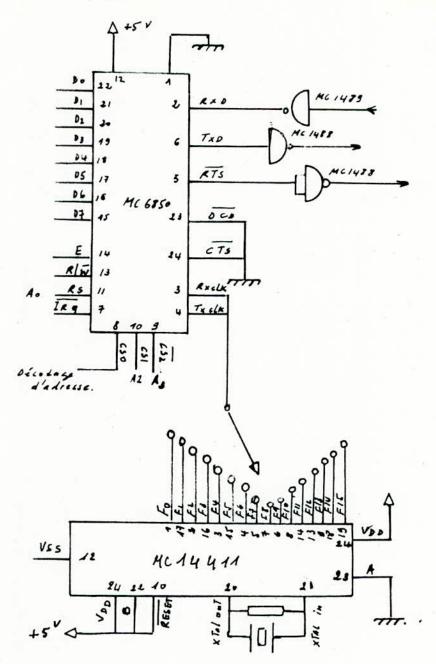

### 4- Circuits d'initialisation

Deux circuits d'initialisation sont prévus.

Un restart manuel qui permet d'initialiser le micro-processeur à tout moment et restart automatique qui

l'initialise à la mise sous tension.

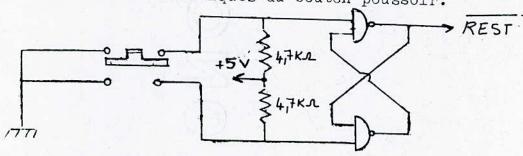

### 4.1 - Restart manuel:

A chaque préssion du bouton poussoir on obtient une impulsion négative. Une bascule RS classique élimine les rebondissemnts mécaniques du bouton poussoir.

### 4.2 Restart automatique:

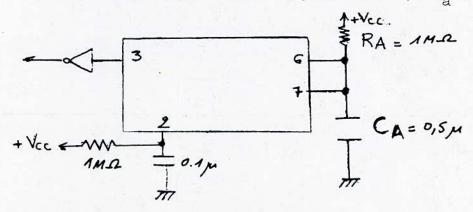

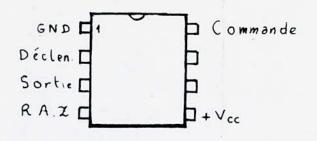

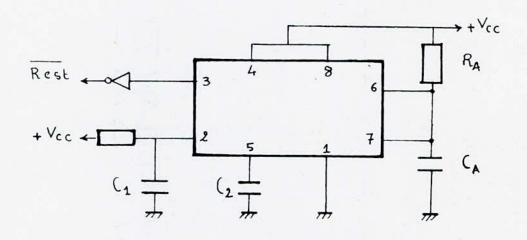

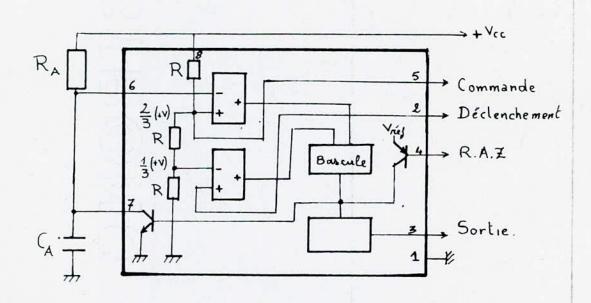

Il est conçu autour du NE555 monté en monostable.

Il envoie une impulsion sur la sortie 3 dés qu'il reçoit un niveau bas sur l'entrée 2 (donc à la mise sous tension). L'impulsion à une largeur T=1,1  $R_a \times C_a$

#### 5 - CIRCUIT D'HORLOGE.

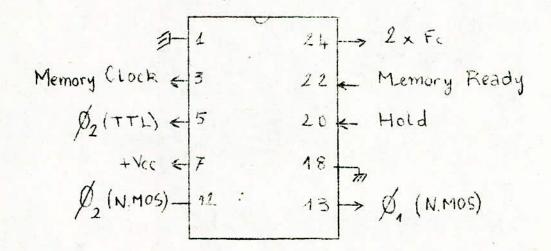

Le microprocesseur MC6800 utilise une horloge externe lui délivrant 2 signaux de fréquence 1 MHZ sans recouvrement Ø1(N.MOS) et Ø2(N.MOS) et en opposition de phase. On utilise la MC6871 A qui renferme un quartz interne et un oscillateur générant un signal de fréquence 1MHZ. En plus des signaux Ø1(N.MOS), Ø2(N.MOS) et Ø2(TTL) la MC6871 A génère les signaux suivants:

- 2 x Fc qui est deux fois la fréquence d'horloge.

- Memory ready: cette commande prolonge l'état haut de \$2(ou l'état bas de \$1).

- Memory clock: signal de selection mémoire.

- Hold : ce signal prolonge l'étendue de l'état haut Ø1.

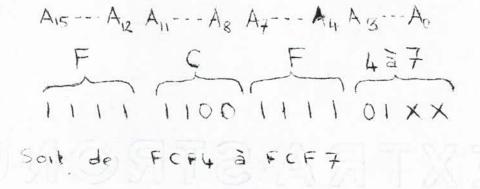

# 66 Organisation du champ mémoire de la partie C.P.U.

Le champ mémoire oxcupé par la partie C.P.U va de F000 à FFFF et il est organisé de la maniere suivante:

| CIRCUITS    | Adresses en Hexa | Commentaire                        |

|-------------|------------------|------------------------------------|

| 1ere ROM    | F000<br>F7FF     | MONITEUR: Implantation de l'Exbug. |

| 2eme ROM    | F800<br>FBFF     | 21048                              |

|             |                  | Adresses ouvertes                  |

| A.C.I.A     | FCF4<br>FCF7     | Registres internes                 |

|             |                  | Adresses ouvertes                  |

| 1ere RAM    | FF00             | MONITEUR:                          |

| <del></del> | FF7F             | Stockage intermédiaire             |

|             | FF80             | de données.                        |

| 2eme RAM    | FFFF             |                                    |

## OGIQUE DE DECODAGE

#### 7,1 - INTRODUCTION:

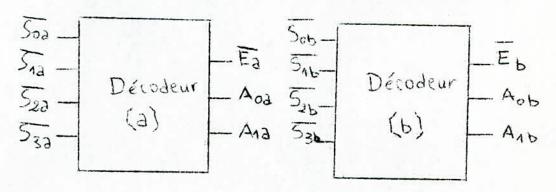

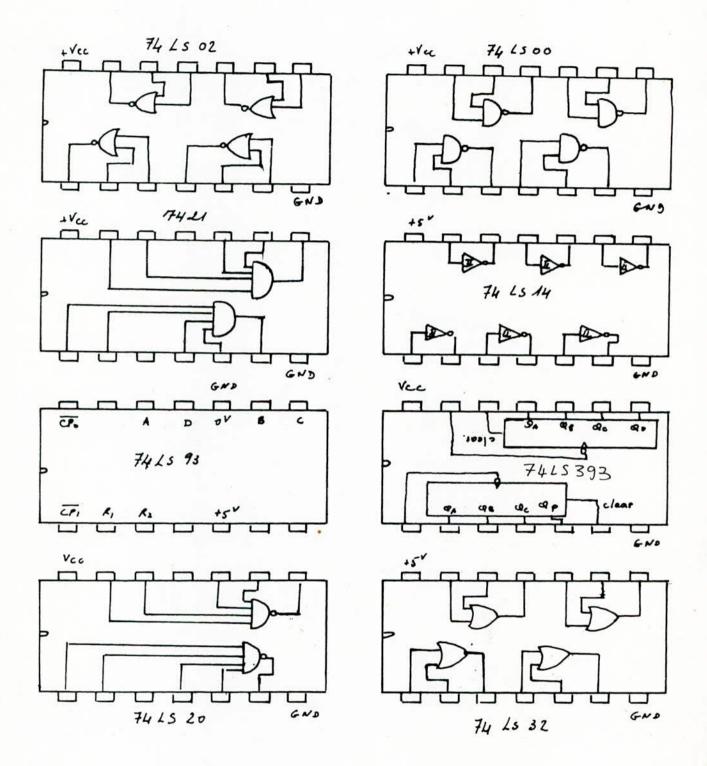

Pour adresser les différents boitiers prevus dans la partie CPU, nous avons réalisé un decodage complet du bus d'adresses par l'intermediaire de Postes et de 2 décodeurs. Le circuit utilisé est le SN 74 IS 139 qui est un double décodeur 1 parmi 4 dont le brochage est donné en annexe. Les 2 decodeurs ont chacun une entrée de validation E.

### 7-1 - VALIDATION DES 2 EPROM

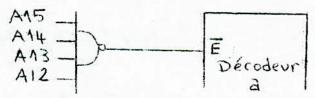

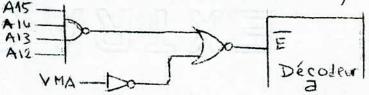

.Pour adresser la partie CPU qui comprend le groupe d'adresses de FOOO à FFFF, on utilise une Porte NAND à 4 entrées.

Le demodeur ne sema validé que si l'adresse est momprise entre F000 à FFFF. En utilisant un verrouillage par V M A: VMA étant à 1 lorsque une adresse est disponible sur le bus d'adresses, ON aura:

Le decodemr n'est validé que si A15,A14,A13,A12 et VMA sont à 1

|                | A 15 | A | A 13 | A 12 | Α,, | A 10 | Ąg  | A 8 | A7 | A٤ | A5 | IA4 | A3 | A 2 | ıA۸ | ıA. |

|----------------|------|---|------|------|-----|------|-----|-----|----|----|----|-----|----|-----|-----|-----|

| 1º ROM { 1º Ko | 1    | 1 | 1    |      | 0   | 0    | X   | X   | X  | ×  | X  | X   | X  | X   | X   | X   |

| (2º Ko         | 1    | } | 1    | 1    | 0   | 1    | X   | ×   | X  | X  | X  | X   | X  | X   | X   | X   |

| 2º ROM - 1º Ks | 1    | 1 | ı    | 1    | 1   | 0    | X   | X   | X  | X  | X  | Х   | Х  | X   | Х   | X   |

| ACIA.          | 1    | 1 | 1    | )    | ı   | 1    | 0   | 0   | l  | ı  | 1  | ١   | 0  | 1   | X   | X   |

| 1ºTE RAM.      | 1    | 1 | _1   | 1    | Ĭ   | 1    | - 1 | 1   | 0  | X  | X  | X   | X  | X   | X   | X   |

| 2º RAM.        | 1    | 1 | 1    | 1    | 1   | 1    | 1   | 1   | 1  | X  | X  | X   | X  | X   | X   | X   |

- tableau du champ mémoire en binaire.

Pour valider la 2 ROM qui lomprennent une entrée de validation chacun OS on utilise aux entrées adresses du décodeur (a) les digits AIO, AII. (voir fig.7.1).

- Soa et SM valideront la Ier ROM lorsque A II est à 0", de F 000 à F7FF

- S2a validera la 26me ROM lorsque AII est à I et AIO à O , de F 800 à FBFF S3a validera le décodeur b lorsque A II et A IO sont à I. à partir de

FCOO.

On remarquera au passage que S3a servant à valider le 26 décodeur le 26 me Ko de la 2é ROM ne pourra plus être adressé.

#### 7.2 - VALIDATION DES 2 RAM.

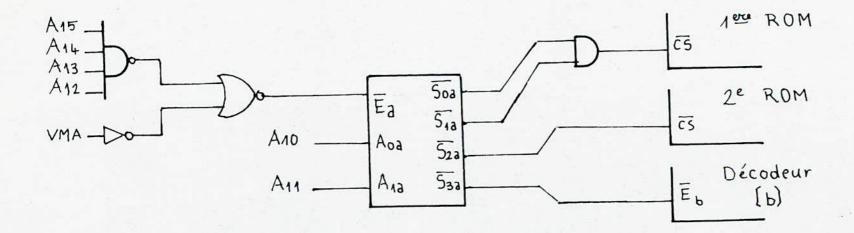

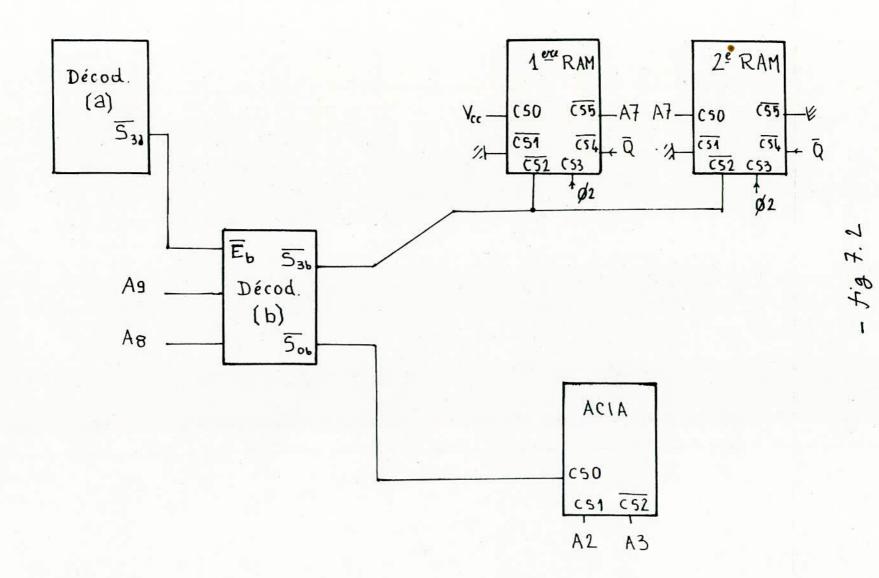

Le second décodeur va nous permettre de sélectionner l'ACIA et les 2 RAM. fig 7.2 page 31

On utilise aux entrées d'adresses du décodeur (b) les digits A8, A9.

- S 3 b nous permet de sélectionner partiellement les 2 RAM lorsque A8 et A9 sont à I, aux adresses. F F 00 à FFFF. Partiellement car les 2 RAM utilisées sont les MC 6810 qui possèdent 6 entrées de validation (select chip) CSO, C SI, C s2, C s3, C s4, C s5.

Le boitier ne sera validé que si :

|        | CSO | 551 | C51 | 653 | CSL | C55 |

|--------|-----|-----|-----|-----|-----|-----|

| Sont à |     |     |     |     | 0   |     |

Connections sur les Select Chip :

| elect Chip | RAM1     | IRAM2        |

|------------|----------|--------------|

| CEE        | A 7      | GND          |

| CSL        | Sortie G | 2 bascule TK |

| C53        |          | Ø2           |

| <u>cs2</u> | Sorties  | Décod b      |

| CS1        | G        | ND           |

| CSO        | Vcc      | A7           |

| A <sub>1</sub> a | Aoa | 530 | 528 | Sia | 500 | CS 1º Rom | CS 2º ROM | Eb |

|------------------|-----|-----|-----|-----|-----|-----------|-----------|----|

| 0                | 0   | ı   | 1   | 1   | 0   | 0         | 1         | ι  |

| 0                | 1   | 1   | 1   | 0   | 1   | 0         | LT        | ι  |

| 1                | 0   | 1   | 0   | 1   | 1   | 1         | 0         | 1  |

| 1                | 1   | 0   | 1   | 1   | 1   | 1         | 1         | 0  |

Fig 7.1

•

29

- \$2 permet de synchroniser les RAM lorsqu'il 50 échange d'instructions sur le bus :

- C S3 sélectionné lorsque Ø 2 est à I.

## d'inhiber

- La sortie  $\widehat{\mathbf{A}}_1$  de B la bascule JK permet d'intriber les 2 RAM lorsqu'on met une remise à zéro.

- Cs2 validée par le décordeur (b) lorsqu'une adresse du groupe F FOO à FFFF est disponible.

- C sI est validée en permanence et mise à la masse.

- Les 2 autres Select chip vont nous permettre d'adresser séparément les 2 RAM en utilisant A7.

connectee

Dans la Iéré RAM CSO est validée en permanence et commecrée à Vcc tandis que CS5 n'est validée que si A7 est à 0 , F FOO à RR7R. FFFF

Dans la 26me RAM CS5 est validée en permanence et commecrée à la masse et CSO ne sera validée que si A7 est à I , FF 80 à FFFF.

## 7.3 - VALIDATION DE L'ACIA :

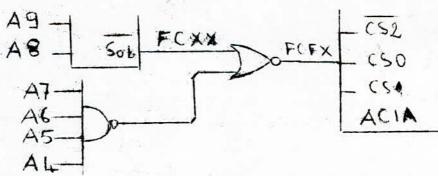

Lorsque A8 et A9 sont à 0 ; la sortie Sob du décodeur est à 0 et permettra d'adresser le groupe FCXX.

Pour adresser l'ACIA aux adresses FCFX les digits A7, A6, A5, A4 étant à I on utilise une porte à 4 entrées comme le montre la figure suivante.

L'ACIA possèdant 3 select chip CS2, CSO, CSI «le ne sera validée

On a vu que CSO est validée aux adresses FC FX.

On connecte A2 et A3 respectivement à CSI et CS2.

L'ACIA sera validé aux adresses.

## 7.4 : Chargement des vecteurs d'interruption.

Il s'agit de charger en mémoire vive (RAM 6810) à la mise sous tension ou aprés un "Reset" les vecteurs d'interruption aux adresses FFF8 à FFFF.

L'adresse du début de programme qui permet de faire ce transfert est contenue dans une 3e ROM (EPROM 2716).

Au restart, une ligne d'inhibition permet de désélectionner les boitiers du moniteur tandisque la 3e ROM est sélectionnée, le 6800 va chercher l'adresse de debut en FFFF et FFFF non pas dans les RAM du moniteur (qui sont inhibées) mais dans la 3e ROM qui est validée pendant toute la durée d'initialisation. (fig 7.4)

Lorsque "Reset" revient à 1 la 3e ROM est inhibée et les vecteurs d'interruptions sont stockés dans la RAM aux adresses FFF8 à FFFF.

Ce système nous permet au lieu d'avoir des vecteurs d'interruption stockés de manière definitive de pouvoir les modifier par programmation, mais à chaque "Reset" effectué il y aura rechargement en mémoire centrale des vecteurs d'interruption.

Une double bascule JK nous permet de valider la 3e ROM. Lorsque Reset passe à zéro les 2 bascules sont initialisées et la sortie  $\mathbb{Q}_2$  se met à "1" inversé par une porte NOR on aura "0" sur le chip select  $\overline{\text{CS}}$  de la 3e 2716 qui sera validée tandisque les 2 RAM du "moniteur" qui reçoivent la sortie  $\overline{\mathbb{Q}_2}$  sur le select chip  $\overline{\text{CS2}}$  seront inhibées.

Lorsque reset revient à"1"  $\overline{Q_2}$  ne repasse à zéro qu'aprés le 2e cycle d'horloge parcequ'une instruction comporte 2 cycles d'horloge et afin de ne pas p' turber le déroulement de l'instruction.

A remarquer que l'entrée d'horloge des 2 bascules ne reçoit 2 que si l'adresse est comprise entre FOOO et FFFF soit le champ mémoire occupé par la partie CPU.

### - CONCLUSION

Malgré quelques difficultés, la réalisation pratique de l'unité centrale fût menée à terme. Les tests ont été conclus et le cahier de charge a été scrupuleusement respecté.

L'absence de circuit imprimé double - face à trous métallisés a été à l'origine des difficultés rencontrées lors de la mise au point.

## Introduction

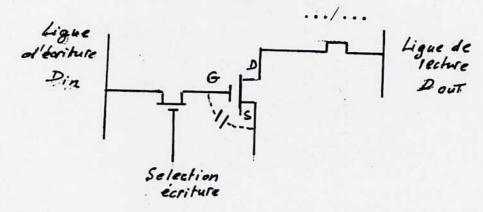

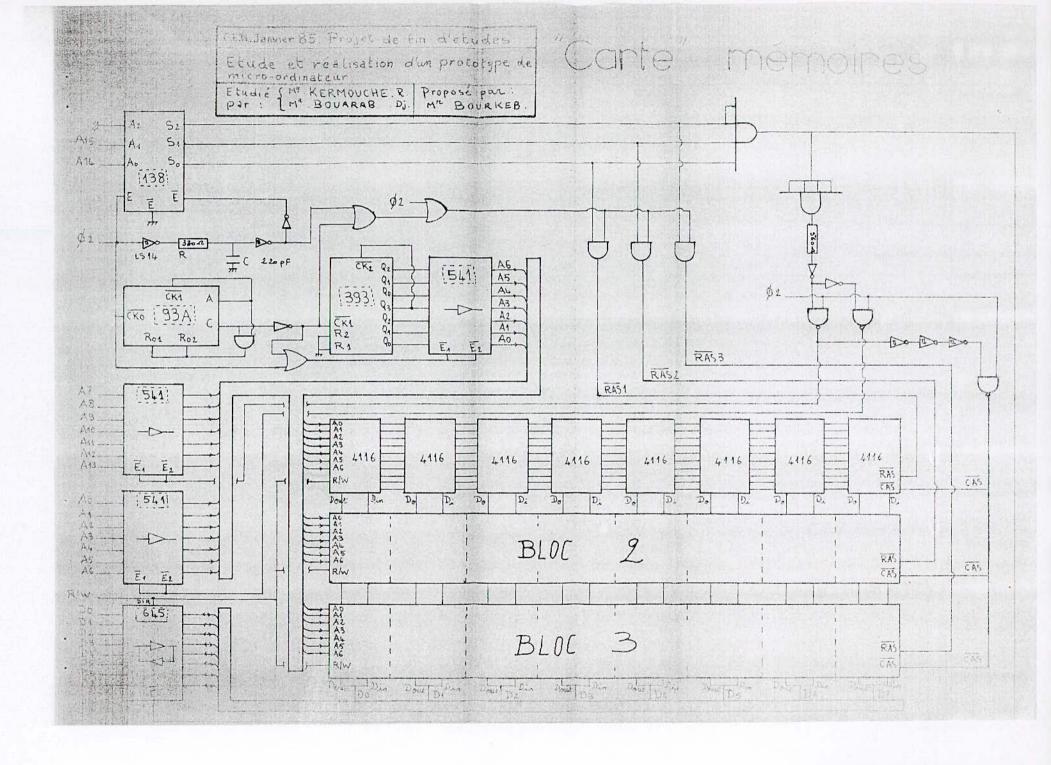

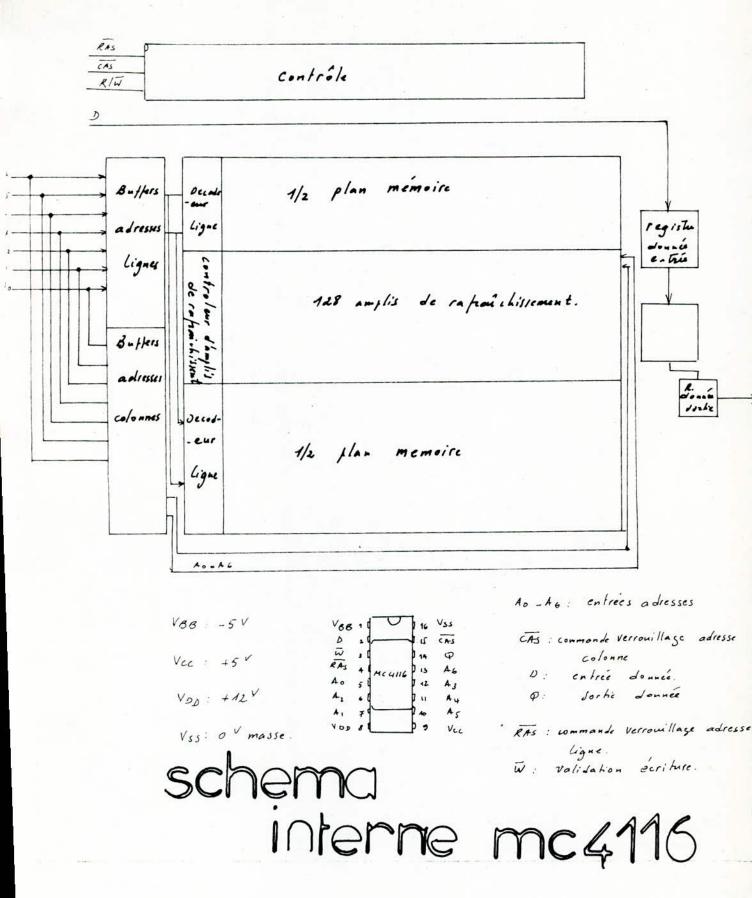

La mémoire centrale a une capacité de 48Ko.

Elle est constituée de 3blocs de 8 mémoires dynamiques

16Kbits.Elle comprend des buffers d'adresses et de

données, une logique dev décodage et des circuits de

rafraichissement.Dans les pages qui suivent on étudiera

en détail le s differentes parties.

#### 2 - GENERALITES

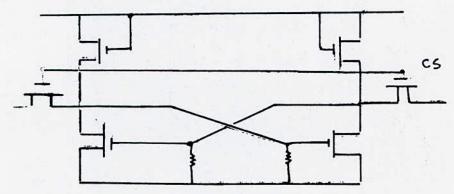

Il existe 2 types de méloires vive, les statistiques et l les dynaliques.

Les presières ont pour élément de stockage une bascule. Elles sont monotension, sans horroge, noins de logique, de support. Cependant elles présentent un coût par bit élevé une intégration limitée et une consommation excessive. Elles ne sont utilisées que pour des plans mé pares de capacité inférieure à 3 Ko.

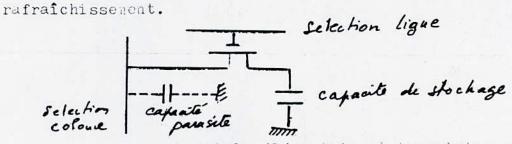

- Cellule de base d'une RAM statique en technologie MoS les RAM dynagiques, ont pour certule de stochage la capacité de gachette - source d'un transistor MOS.

La tension aux bornes de cette capacité se cécharge peu à peu et de plus le courant d'entrée du MOS, si faible soitil, charge cette capacité et modifie la tension préalablement stockée.

L'information se dégrade de plus en plus fortement avec le temps, de sorte qu'il est nécessaire de régénérer la tension initiale. On dit qu'il faut rafraîchir la mémoire. La période de rafraîchissement est de 2 a 3 millisecondes environ selon la mémoire.

Ces RAM dynamiques presente une trés grande intégration, un coût par bit faible, une consommation reduite. Mais ce sont des tri-tensions + 12 v pour le drain, - 5v pour le substrat, + 5v pour la compatabilité TTC et nécessite des circuits de

- Cellule élémentaire à transistor unique.

- Cellule de bade à 3transistors.

## TECHNIQUES DE RAFRAICHISSEMENT.

Pour ne pas augmenter le nombre de broches des circuits intégrés de 16 K ou 64 K **s**oit 1 bit, les fabricants de mémoires ont adopté la solution du multiplexage d'adresse.

L'adresse rangée et l'adresse colonne sont envoyées l'une après l'autre à la mémoire sur les mêmes fils. Bien entendu cela ne peut se faire qu'en mémorisant au moins la première adresse envoyée. Ce qui nécessite l'envoi à la mémoire d'une commande de verrouillage pour la mémorisation de l'adresse rangée. On a ainsi 2 co mandes de verrouillage l'une pour les rangées RAS (Row adress stroke) et l'autre pour les colonnes CAS (Column adress stroke).

## RAFRAICHISSE ENT GROUPE (BURST MODE)

Le rafraichissement de la 1e colonne est immédiatement suivi du rafraîchissement de la 2° colonne puis de la 3° et ainsi de suite jusqu'à la dernière. Le fonctionnement du microprocesseur est suspe du pendant ce temps, puisque la RAM est inutilisable, ce type de rafraîchissement n'est pas utilisé puisqu'il ralentit le système.

## 2-1-2 RAFRAICHISSE NT PAR " VOL DE CECLE" "

Dans cette technique le rafraichissement de N rangées est distribué sur T ( période de rafraichissement ) à raison d'une rangée toutes les  $\frac{T}{N}$ .

Le fonctionnement du microprocesseur doit être arrêté pendant chaque cycle de rafraîchissement. La perte de temps est la même que pour le "Burst mode".

# RAFRAICHISSEMENT TRANSPARENT (Câche, ou syndrone)

Une circuiterie réalise le rafraichissement d'une manière transparente vis à vis du mocroprocesseur; par exemple si les échanges des données se font sur le bus quand l'horloge \$\omega\$2 est à l'état haut, le rafraichissement pourrait avoir lieu pendant l'état bas de \$\omega\$2. Ce type de rafraichissement a été préféré aux autres car il n'introduit pas un ralentissement du système.

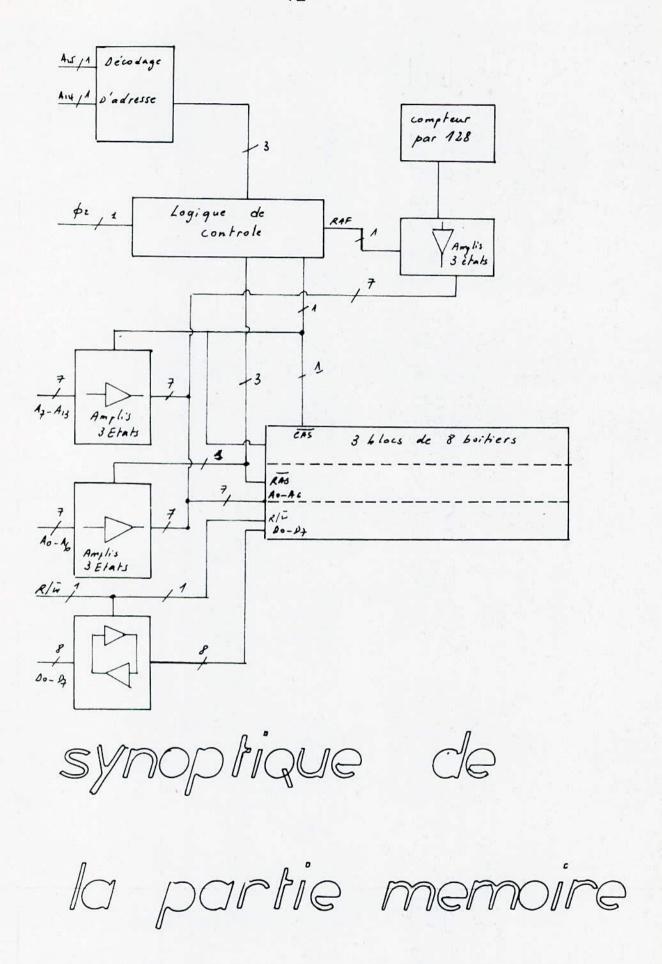

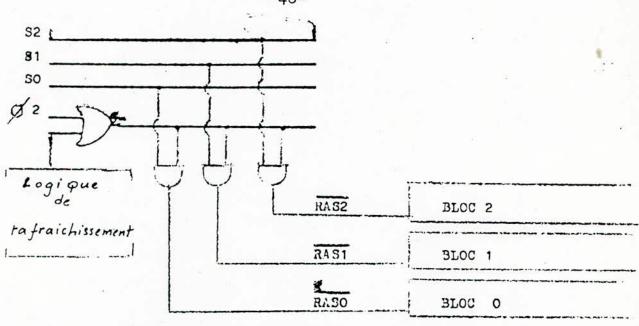

## 5 - LOGIQUE DE DECODAGE.

Notre carte comporte 48 Ko disposés en 3 blocs de 16 Ko chacun.

Le bloc 1 est adressable de 0000 à 3FFF

2 4000 à 7FFF

3 8000 à BFFF

A<sub>15</sub> A<sub>14</sub> A<sub>13</sub> A<sub>12</sub>...A<sub>0</sub>

O O X X....X ----)0000 à 3FFF

O I X X....X ----)4000 à 7FEF

I O X X....X ----)8000 à BFFF

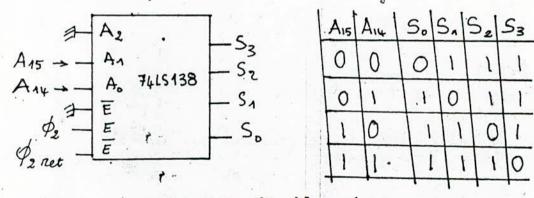

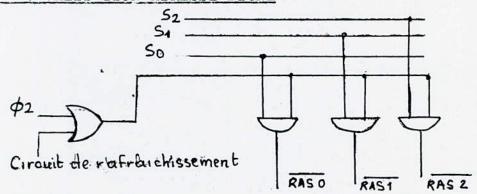

Le décodage d'adresse s'effectuera à partir de A<sub>14</sub>et A<sub>15</sub>. Le circuit utilisé pour le décodage est le SN 74LS 138 qui est un décodeur 1 parmi 4, qui comprend 3 entrées d'adresses et 3 entrées de validation.

So = 0 ----) validation du bloc 1

S<sub>3</sub> non connecté = S<sub>3</sub>= 0, (A<sub>15</sub>= 1, A<sub>14</sub> = 1) la partie mémoire n'est pas adressable.

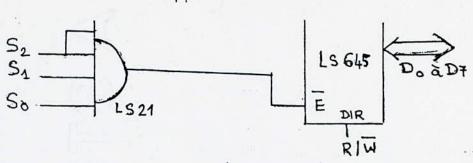

Les 3 sorties S<sub>0</sub>,S<sub>1</sub>,S<sub>2</sub> sont appliquées à une porte AND à 4 entrées qui permettront de valider l'ampli trois états du bus de données dès qu'il y a une adresse comprise entre 0000 à BFFF.

On a 0 2 l'entrée de validation  $\overline{E}$  du 645 si  $S_0 = 0$  ou  $S_1 = 0$  ou  $S_2 = 0$ .  $S_1 = 0$  ou  $S_2 = 0$ .  $S_3 = 0$  ou  $S_4 = 0$  ou  $S_5 = 0$  ou  $S_6 = 0$  ou  $S_8 = 0$  o

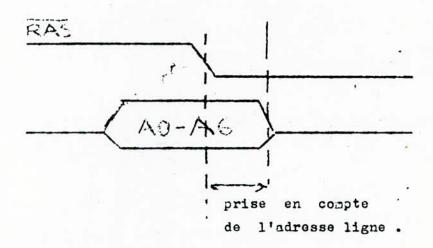

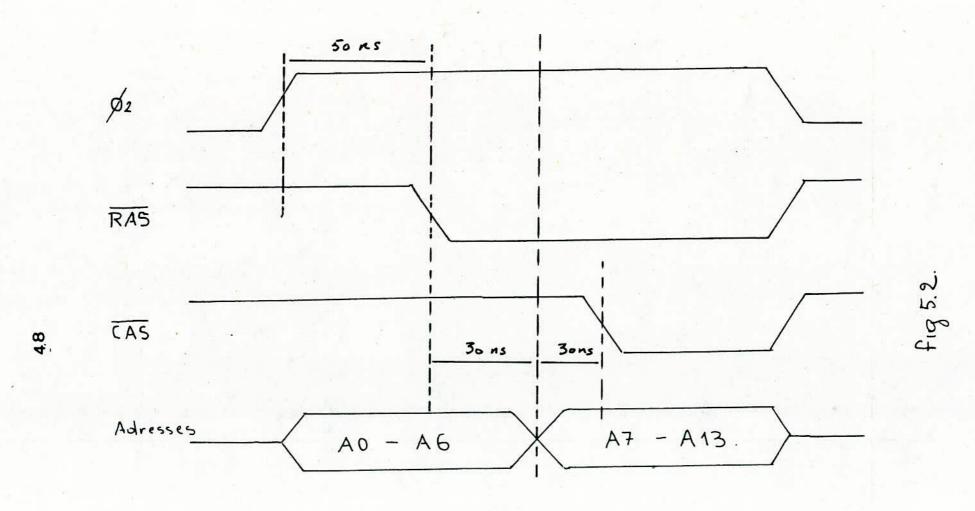

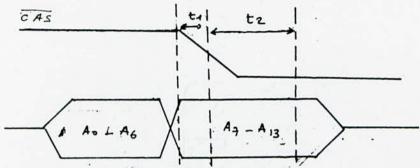

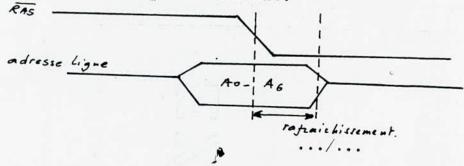

### 5 - 1 VALIDATION ADRESSE LIGNE =

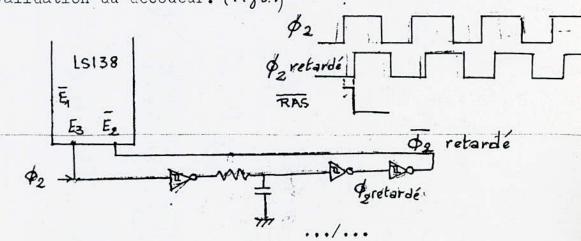

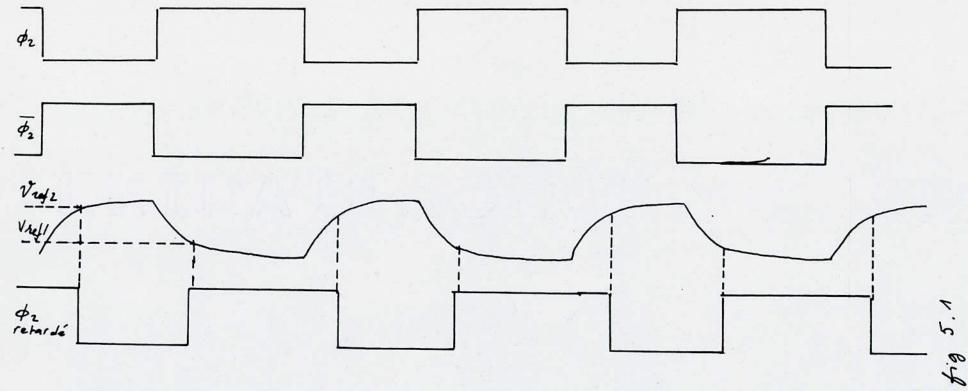

D'après les chronogrammes de lecture et d'écriture le signal  $\overline{\rm RAS}$  ne devra descendre à 0 qu'avec un certain retard après le front montant de  $\emptyset_2$

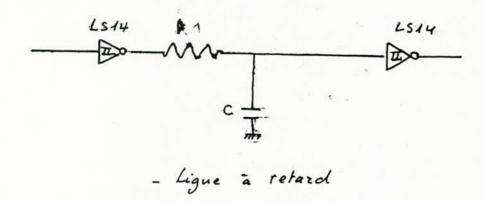

Ainsi une ligne à retard a été prévue sur les entrées de validation du décodeur. (fig5.1)

on voit que entre de et Vcz il y'a un retard dont la valeur dépend du Chrix de RetC.

Lorsque RAS descent à zéro l'adresse ligne déjà présente aux entrées d'adresse est prise en compte par le bloc dem mémoires validé.

Le retard est de quelques nanosecondes. Le principe est basé sur le basculement du trigger de Schmitt lorsqu'on atteint des tensions de référence ( Vef et vef ) fixes.

Le circuit R,C permet de retarder l'atteinte de ces seuils à la charge ou à la décharge de C.

Le circuit, utilisé est le SN 74 LS 14 qui comprend 6 inverseurs triggers de schmitt dont les seuils de référence sont  $V_{ref_2} = \frac{et \cdot V_{ref_2}}{}$

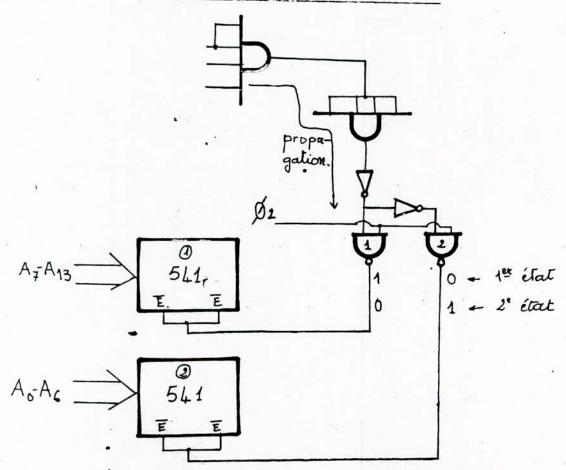

## 5 - 2 VALIDATION DES AMPLIS DE BUS D'ADRESSES.

Lorsque pomonte le signal issu du décordeur met un certain temps de propagation pour arriver aux entrées des 2 portes NAND et on a à la sortie de la porte 2 un état bas qui valide l'amplitrois états du bus d'adrecses lignes (Ao - AS) l'autre ampli étant désactivé lorsque le signal arrive fg u. Misus et fig 5.2

# Chronogrammes Validation advesses.

l'inverse se produit et c'est l'ampli d'adresses colonnes qui est validé.

Pour que les mémoires prennent en compte les adresses colonnes, CAS doit descendre quelques instants après la validation de l'ampli trois états du bus d'adresses colonnes

ti est obtenu à l'aide du temps de propægation de trois inverseurs.

t2 : prise en compte de l'adresse colonne.

Pour rafraichir les mémoires il su lit de faire une lecture de tous les bits des positions mémoires ce qui revient à présenter l'adresse ligne aux entrées d'adresses des mémoires et de faire descendre RAS un instant après en suivant le chronogramme suivant.

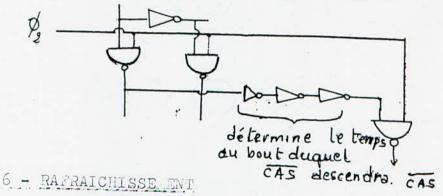

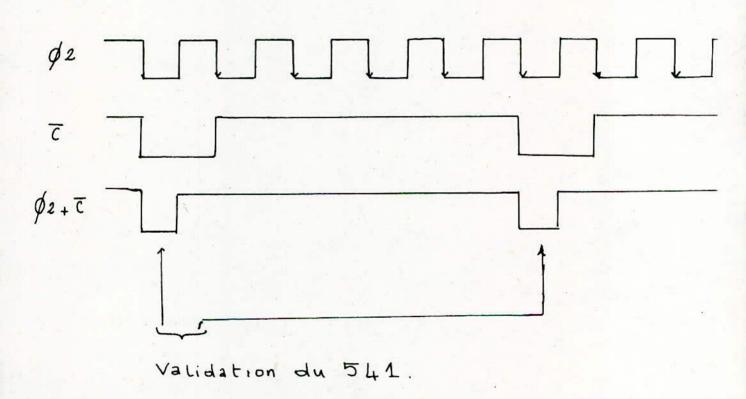

Le rafraichissement réalisé sur notre carte est un rafraichissement transparent c'est à dire pendant que \$2 est à l'état bas.

Pour réduire la consommation des mémoires, il ne sera autorisé que tous les 5  $\emptyset_2$ .

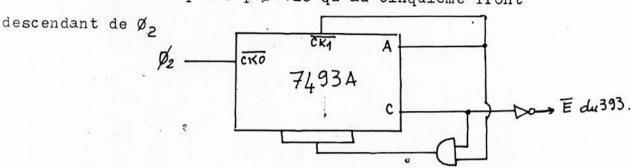

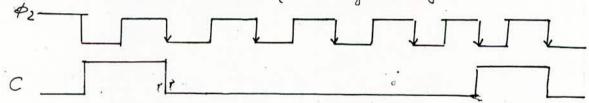

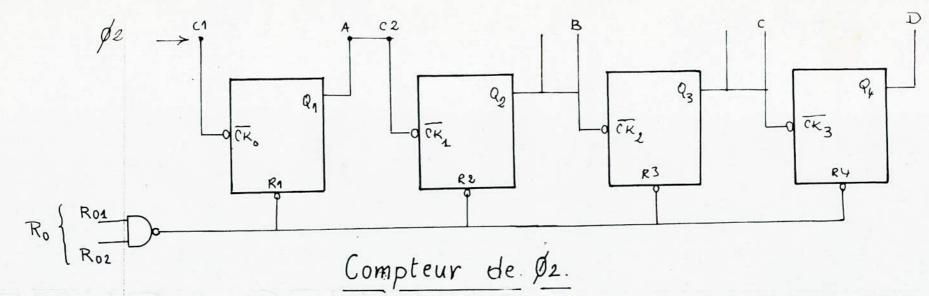

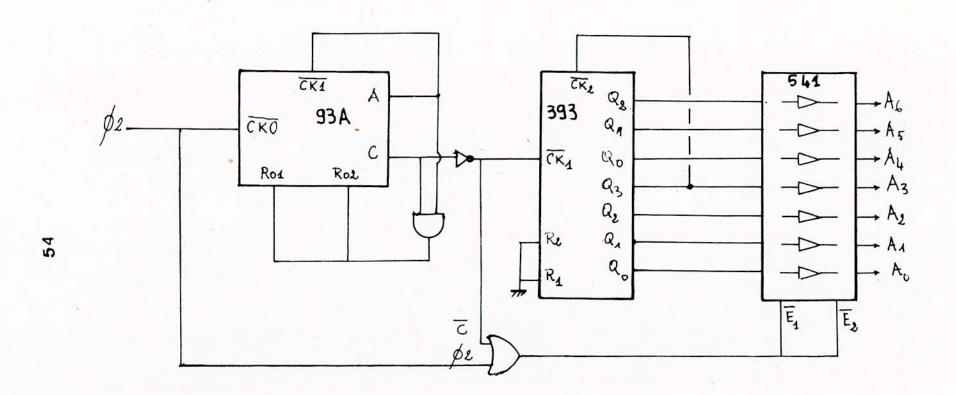

Pour cela un compteur de  $\emptyset_2$  est ajouté et qui ne permettra ll'avance du Compteur par 128 qu'au cinquième front

on n'aura une impulsion positive sur la sortie C qu'au cinquième front descendant de Ø2 et elle est remise à zero au front descendant suivant. (voir fig 6.a page 51)

La sortie C commande un autre compteur qui a pour but de présenter l'adresse ligne aux entrées des mémoires.

Le circuit utilisé est le SN 74 LS 393 qui est un double compteur 4 bits.

## Autorisation de rafraichissement

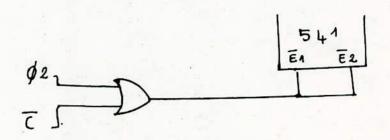

Pour que le rafraichissement ne soit fait que pendant que Ø2 soit à l'état bas et seulement au cinquième front descendant de Ø2, le 541 ne sera validé qu'à ce moment.

Le compteur est à remise à géro prematurée: à la 1<sup>the</sup> impulsion il pl , met à géro. On relie de à C1, à chaque front descendant de de le compteur avance d'1 pas, à la 5<sup>e</sup> il pe remet à géro.

| a | C | В | 1 A |                          |

|---|---|---|-----|--------------------------|

| 0 | 0 | 0 | 0   | Remise à zéro du compte  |

| 0 | 0 | 0 | 1   | Δ                        |

| 0 | 0 | 1 | 0   | $\bigcap R_{01}, R_{02}$ |

| 0 | 0 | 1 | 1   |                          |

| 0 | ı | 0 | 0   |                          |

| 0 | 1 | 0 | 1   |                          |

ET SEULEMENT AU CINQUIÈME FRONT DESCENDANT DE \$2, LE 541 NE SERA VALIDE QU'À CE MOMENT PRÈCIS .

- fig 6.b-

Pour valider l'adresse ligne RAS doit descendre à zéro un certain temps aprés le front descendant de Ø2. Pour cela une ligne à retard est utilisée.

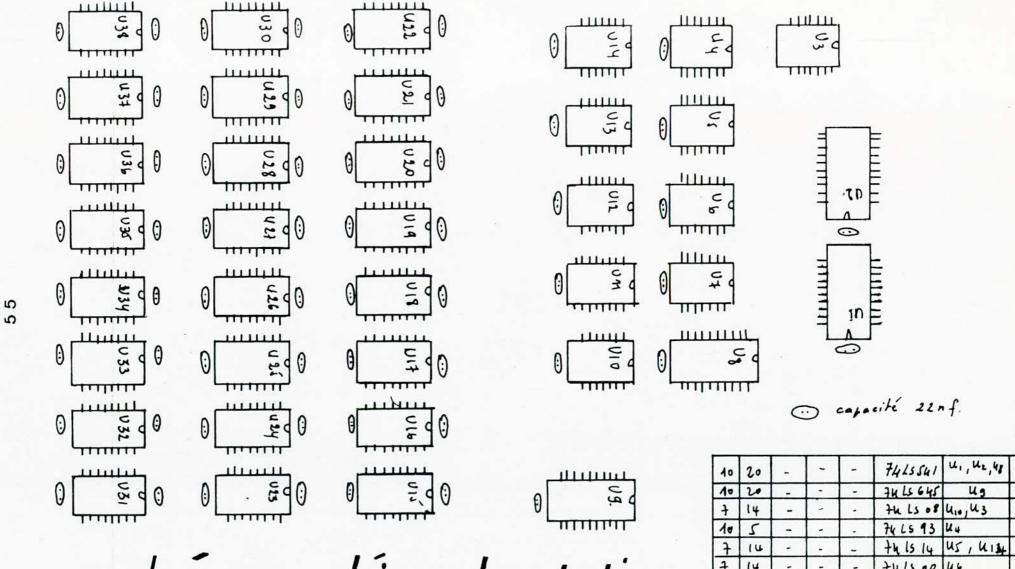

schéma d'implantation -partie mémoire -

| 10  | 20  |      | ,    | -  | 7415541   | u, , uz, 48 |  |

|-----|-----|------|------|----|-----------|-------------|--|

| 10  | 20  | _    | -    | -  | 74 LS 645 | us          |  |

| 7   | 14  | -    | 1    |    | the Ls of | 4,0,43      |  |

| 10  | 5   | -    |      |    | 74 LS 93  | U4          |  |

| 7   | 14  | -    | -    | _  | th 15 14  | US, U134    |  |

| 7   | 14  | -    | -    | -  | 74 LS 00  | 46          |  |

| 7   | 14  | -    | -    | -  | 74 65 393 | 47          |  |

| 3   | 16  | -    | -    | -  | tu 138    | un          |  |

| 7   | 14  | -    | -    | -  | tu LS 21  | 412         |  |

| 7   | 14  | -    | -    | -  | 746532    | 413         |  |

| 16  | 9   | 8    | -    | 1  |           | 415 - 438   |  |

| GND | +50 | 4124 | -124 | -1 |           |             |  |

#### - CONCLUSION

Faute d'un circuit intégré, le double compteur 74 LS 393, réalisant le rafraîchissement la carte mémoire n'a pas été testée complètement. Malgré cela, elle fût réalisée dans les normes avec la capacité de 48 Ko et un rafraîchissement transparent qui nécessite un respect absolu des chronogrammes de la mémoire, donc difficulté de synchronisation.

Les tests sur les autres parties ont été conclus.

-=-=-000-= C O N C L U S I O N =-000-=-=-

#### CONCLUSION

La réalisation en série d'un produit est confronteé à divers problémes qui paraissent, de prime a bord, sans importance; mais qui en verité, conditionne dans une large mesure la rentabilité de l'opèration.

Notre projet a pour but de concevoir un microordi--nateur pour une fabrication en série.

Il s'agissait alors d'optimiser les paramètres suivants:nombres de composants, temps de fabrication d'une unité, prix de revient, possibilité d'extension du système, facilité du dépannage.

Les solutions proposées vont dans ce sens et permettent d'arriver au but.

## 1) Nombre de composants

La configuration utilisée permet de supprimer les circuits de validation des cartes et de diminuer le nombres de buffers.

## 2) Temps de réalisation

L'architecture moncarte nous dispense de connecteurs, de glissiers, de visseries et un travail fini de grande précision ; d'où un gain sur le temps de fabrication.

## 3) Prix de revient

Les deux points étudies précedemment influent directement sur le prix de revient du microordinateur et leur minimisation entraîne celle du prix de revient.

## 4) Extension du système

La pseudo-modularité permet de faire évoluer les capacités du microordinateur suivants les besoins.

Il suffit pour cela de changer le "scotch" de la partie incriminée.

## 5) Dépannage

Là aussi, il est facile de localiser une panne du microordinateur, car étant conçu de façon modulaire.

La réalisation par étape du microordinateur, l'unité centrale en premier, la partie mémoire ensuite nous a pormis l'éffectuer les tests sans un matériels specialisé Un oscilloscope a suffi pour l'unité centrale et cette dernière pour la partie mémoire.

Enfin le projet est encore perfectible, mais déja on peut envisager la fabrication en série de la version de base.

-=000=- A N N E X E -=000=-

Brochage, schéma interne du NE 555.

# Caracléristiques de la Norme E.I.A (Electrical Industrie Association) La RS 232C

Mode: 1 fil

Longueur moximale du câble : 17 mêtres

Debit maximum: 20 K bands.

Tension minimale de dortie en charge : ± 0,5 à ± 15

Tension maximale en circuit ouvert: ± 25"

Résistance de dortée minimale : Ro = 300 A

Courant maximal de court-circuit : ± 0,5 A

Seuil maximal du récepteur : +3 a -3 v

Tension maximale à l'intez-récepteur: -25 à 25

Lecture. RAS CAS A7-A13 Adresses R/W Données DO D0-D7 (Dout.) Ecriture. RAS CAS Adresses A7 - A13

CHRONOGRAMMES DES SIGNAUX DE LECTURE ET D'ECRITURE DE LA MEMOIRE DYNAMIQUE MC4116.

## Bibliographies

- Microprocesseur: du 6800 au 6809 D'interfaçage

par G. REVELLIN Dunod 1981

- Les systèmes à Microprocesseurs

par M. Aumieux Masson 1982

- Aide à la conception de Bystemes Micro-ordinateurs thèse ingénierat d'état ENP juin 1983

- De la logique cablée aux microprocesseurs, £4

par J.M Bernard, J. Hubon Eyrolles 1980

- haut parleur juillet 82.

- Document Motozola.

- Data Prook TTL.