REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique Ecole Nationale Polytechnique Département Electronique

CDTN

المدرسة الوطنية المتعددة التقنيات Ecole Nationale Polytechnique

> End of studies project To obtain the diploma of State Engineer in Electronics

> > Theme:

Contribution to the design and implementation of the Bio-inspired Firefly algorithm on FPGA circuit

<u>By:</u>

#### BENKHIRA Fayçal DJEMAI Narimane

#### Examiners:

| • | Mme Nour El Houda BENALIA | MCB, ENP         | President  |

|---|---------------------------|------------------|------------|

| • | Mme Sabrina TITRI         | MRB, CDTA        | Supervisor |

| • | Mme Hadjer AZLI           | PhD Student, ENP | Supervisor |

| • | Mr. Cherif LARBES         | Professor, ENP   | Supervisor |

| • | Mr. Mohamed Oussaid TAGHI | MAT, ENP         | Examiner   |

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique Ecole Nationale Polytechnique Département Electronique

CDTN

المدرسة الوطنية المتعددة التقنيات Ecole Nationale Polytechnique

> End of studies project To obtain the diploma of State Engineer in Electronics

> > Theme:

Contribution to the design and implementation of the Bio-inspired Firefly algorithm on FPGA circuit

<u>By:</u>

#### BENKHIRA Fayçal DJEMAI Narimane

#### Examiners:

| • | Mme Nour El Houda BENALIA | MCB, ENP         | President  |

|---|---------------------------|------------------|------------|

| • | Mme Sabrina TITRI         | MRB, CDTA        | Supervisor |

| • | Mme Hadjer AZLI           | PhD Student, ENP | Supervisor |

| • | Mr. Cherif LARBES         | Professor, ENP   | Supervisor |

| • | Mr. Mohamed Oussaid TAGHI | MAT, ENP         | Examiner   |

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique Ecole Nationale Polytechnique Département Electronique

CDTN

المدرسة الوطنية المتعددة التقنيات Ecole Nationale Polytechnique

> Projet de fin d'Etudes Pour l'obtention du diplôme d'Ingénieur d'Etat en Electronique

> > <u>Thème:</u>

Contribution à la conception et l'implémentation de l'algorithme bio-inspiré Firefly sur circuit FPGA

Réalisé Par:

BENKHIRA Fayçal DJEMAI Narimane

#### Composition du Jury :

| • | Mme Nour El Houda BENALIA | MCB, ENP        | Président   |

|---|---------------------------|-----------------|-------------|

| • | Mme Sabrina TITRI         | MRB, CDTA       | Rapporteur  |

| • | Mme Hadjer AZLI           | Doctorante, ENP | Rapporteur  |

| • | M. Cherif LARBES          | Professeur, ENP | Rapporteur  |

| • | M. Mohamed Oussaid TAGHI  | MAT, ENP        | Examinateur |

ملخص: لتعزيز الطاقة الموردة من النظام الكهروضوئي ، فإن تتبع نقطة الحد الأقصى للطاقة أو MPPT هو الطريقة المناسبة للقيام بذلك. هناك العديد من العوامل التي يمكن أن تؤثر على الطاقة المنتجة من الأنظمة الكهروضوئية ، مثل درجة الحرارة و شدة و الإشعاع الشمسي و التظليل الجزئي.يتم تغيير خاصية المصفوفة الكهروضوئية عند حدوث تظليل كلى أو جزئي عليها بسبب السحب و الأشجار العالية وترسب الغبار والمباني المحيطة أو الظل الناتج عن إحدى المصفوفات الكهروضوئية للأخرى المحيطة. سيؤدي فو الأشجار العالية وترسب الغبار والمباني المحيطة أو الظل الناتج عن إحدى المصفوفات الكهروضوئية للأخرى المحيطة. سيؤدي ذلك إلى ظهور العديد من القيم الحدية القصوى في منحنى الطاقة. مما يؤدي الى ضياعها .عند حدوث التظليل الجزئي ، طرق تتبع ذلك إلى ظهور العديد من القيم الحدية القصوى في منحنى الطاقة. مما يؤدي الى ضياعها .عند حدوث التظليل الجزئي ، طرق تتبع نقطة القيمة الحدية القصوى لي منحنى الطاقة. مما يؤدي الى ضياعها .عند حدوث التظليل الجزئي ، طرق تتبع نقطة القيمة الحدية القصوى لي منحنى الطاقة. مما يؤدي الى ضياعها .عند حدوث التظليل الجزئي ، طرق تتبع نقطة القيمة الحدية القصوى لي منحنى الطاقة. مما يؤدي الى ضياعها .عند حدوث التظليل الجزئي ، طرق تتبع نقطة القيمة الحدية القصوى لي منحنى الطاقة. مما يؤدي الى ضياعها .عند حدوث التظليل الجزئي ، طرق تتبع نقطة العدية العروى لي معان من الراعة هي الطريقة الأساسية لوحدة التحكم MPPT ، من أجل تحسين خوارزمية تتبع نقطة الحد الأقصى للطاقة. ستكون خوارزمية اليراعة هي الطريقة الأساسية لوحدة التحكم MPPT ، من أجل تحسين خوارزمية تتبع نقطة الحد الأقصى للطاقة. ستكون هنالك العديد من الاختبارات والتحليلات من خلال تغيير درجة الحرارة و قوة الإشعاع ، إلى جانب المقارنة مع خوارزمية المرب أو POP ، التي تنتهي بتحميل الخوارزمية في بطاقة FPGA ، هذا سيبين مدى تفوق الخوارزمية المترو قوق الإشعاع ، إلى جانر ، ولاميوزمية وي المتوحة المستوحاة من السرب أو POP ، التي تنتهي بتحميل الخوارزمية في بطاقة FPGA ، هذا سيبين مدى تفوق الخوارزمية المستوحة من السرب الحيوية في الطبيعة وكفاءيا.

الكلمات المفتاحية: النظام الكهروضوئي ، تتبع نقطة الحد الأقصى للطاقة (MPPT) ، الخوارزميات المستوحاة من الحياة الحيوية ، خوارزمية اليراعة ، التصميم المستند إلى النموذج (MBD)، FPGA.

Résumé : Pour améliorer la puissance fournie par un système photovoltaïque, le suivi du point de puissance maximale ou MPPT est le moyen d'y parvenir. Plusieurs facteurs peuvent influencer la puissance produite par un système photovoltaïque, tels que la température, l'irradiation et l'ombrage partiel. Les caractéristiques d'un réseau photovoltaïque sont modifiées lorsque la totalité ou certaines parties de ce système sont ombragées par des nuages, de grands arbres, des dépôts de poussière, des bâtiments environnants ou l'ombre créée par l'un des réseaux photovoltaïques sur d'autres dans des environnements extérieurs. Cela entraînera l'apparition de plusieurs maximums dans la courbe photovoltaïque. Ce qui provoque des pertes superflues. Lorsque l'ombrage partiel se produit, les méthodes MPPT conventionnelles seront incapables de détecter le point maximum global de la puissance, par conséquent, dans ce document, l'algorithme de Luciole sera la méthode basée pour le contrôleur MPPT, afin d'améliorer le suivi du point de puissance maximale. Plusieurs tests et analyses en faisant varier la température et l'irradiation, ainsi que la comparaison avec l'algorithme Optimisation par essaims de particules (PSO), et enfin l'implémentation de l'algorithme en FPGA, démontreront la suprématie de l'algorithme bio-inspiré proposé et son efficacité.

**Mots-clés :** Système photovoltaïque, suivi du point de puissance maximale (MPPT), algorithmes bio-inspirés, algorithme Luciole, conception basée sur un modèle (MBD), FPGA.

**Abstract:** To enhance the supplied power from a photovoltaic system, the maximum power point tracking or MPPT is the way to do so. there are several factors that can influence the produced power from a Photovoltaic system, such as the temperature, irradiation and the partial shading. Photovoltaic array characteristic gets altered when complete or some parts of this system are shadowed by clouds, tall trees, deposition of dust, and surrounding buildings or shadow created by one of the Photovoltaic arrays to others in outside environments. This will lead to the appearance of several maximums in the Photovoltaic curve. That cause superfluous losses. When the partial shading occurs, the conventional MPPT methods will be uncapable to detect the global maximum point of the power, therefore, in this document, the Firefly Algorithm will be the based method for the MPPT controller, in order to improve the maximum power point tracking. Several tests and analysis by variating the temperature and the irradiation, beside the comparison with Particle Swarm Optimization (PSO) algorithm, ending with algorithm implementation in FPGA, will demonstrate the supremacy of the proposed Bio-Inspired Algorithm and its efficiency.

**Keywords:** Photovoltaic system, Maximum Power Point Tracking (MPPT), bioinspired algorithms, Firefly Algorithm, Model Based Design (MBD), FPGA.

# Acknowledgements

We would like to thank Mr. LARBES Cherif, Professor at the National Polytechnic School of Algiers, and we particularly express our gratitude to him for having made us benefit from his scientific skills, his human qualities and his constant availability.

We would like to thank Mrs. Sabrina TITRI, Doctor and Researcher at the Research Centre for Advanced Technologies, who offered us the possibility to realize this thesis under her direction.

We would also like to thank Miss AZLI Hadjer, doctoral student at the National Polytechnic School of Algiers for her advice and her help during the work period.

We would also like to thank the members of the jury for their interest in this project by agreeing to examine it and to enrich it with their proposals.

Our thanks go to all the teachers of the Electronics Department of the National Polytechnic School.

Praise to ALLAH Almighty who gave me the strength and patience to complete this work

I dedicate this modest work to those who gave me everything without asking me anything and to whom I owe a lot and to whom I will never thank never enough:

My dear parents.

My friends during my entire academic career.

To everyone who gave me support.

Fayçal BENKHIRA

Every challenging work needs self-efforts as well as Guidance of elders especially those who were very close to your heart. My humble effort I dedicate to my sweet and loving Mother & Father Two brothers Whose affection, love, encouragement and prays make me able to get such Success and honour. Along with all my friends, all hard working and respected Teachers

Narimane DJEMAI

# **Table of Contents**

| Table of fig   | ures                                                  |    |

|----------------|-------------------------------------------------------|----|

| Tables         |                                                       |    |

| Abbreviatio    | on List                                               |    |

| General In     | troduction                                            | 15 |

| 1. Photovo     | oltaic Electrical Energy                              |    |

| 1.1 Introduc   | tion                                                  | 18 |

| 1.2 Photovo    | Itaic Systems                                         | 18 |

| 1.3 The Pho    | otovoltaic Cell reviews                               | 19 |

| 1.3.1 Defi     | nition                                                | 19 |

| 1.3.2 Defi     | nition                                                | 19 |

| 1.3.3 Cha      | racteristic Curves                                    | 20 |

| 1.4 Photovo    | Itaic Cell Shading                                    | 20 |

| 1.5 Effects of | of Climate Variations on the photovoltaic Module      | 22 |

| 1.5.1 Influ    | ence of the illumination                              | 22 |

| 1.5.2 Influ    | ence of temperature                                   | 23 |

| 1.6 MPPT       |                                                       | 23 |

| 1.7 Conclusi   | on                                                    | 24 |

| 2. Maximu      | m power point tracking methods. State of the art      | 26 |

| 2.1 Introduc   | tion                                                  | 26 |

| 2.2 Perform    | ance criteria of MPPT algorithm                       | 26 |

| 2.3 Classific  | ation of MPPT methods                                 |    |

| 2.3.1 Con      | ventional methods                                     |    |

| 2.3.2 Adv      | anced methods                                         |    |

| 2.3.2.1        | AI-Based Methods                                      | 29 |

| 2.3.2.2        | Bio-Inspired (BI) methods                             |    |

| 2.4 The Fire   | fly algorithm                                         | 33 |

| 2.4.1 Bas      | ic concepts                                           | 34 |

| 2.4.2 Step     | os of the Firefly Algorithm [31]                      | 35 |

| 2.4.2.1        | Initialization                                        | 35 |

| 2.4.2.2        | Exploration                                           | 35 |

| 2.4.2.3        | Checking the convergence criteria                     |    |

| 2.4.3 Algo     | prithm parameters                                     | 40 |

| 2.5 Applicat   | ion of the Firefly Algorithm (FA) for MPPT controller | 40 |

| 2.6 Applicat | ion of the PSO algorithm for MPPT controller               | 44 |

|--------------|------------------------------------------------------------|----|

| 2.7 Conclus  | ion                                                        | 45 |

| 3. Softwar   | e Implementation of FA-MPPT Controller                     | 47 |

| 3.1 Introduc | -<br>tion                                                  |    |

| 3.2 Simulati | on Methodology of the proposed MPPT controller             |    |

| 3.2.1 Mod    | delling of the photovoltaic system                         |    |

| 3.2.1.1      | PV array                                                   |    |

| 3.2.1.2      | MPPT controller block                                      |    |

| 3.2.1.3      | Buck-Boost converter                                       |    |

| 3.2.2 Para   | ameterization of FA and PSO                                |    |

| 3.2.2.1      | FA parameterization                                        | 50 |

| 3.2.2.2      | Parameterization of the PSO algorithm                      |    |

| 3.2.3 Sim    | ulation of the FA controller                               |    |

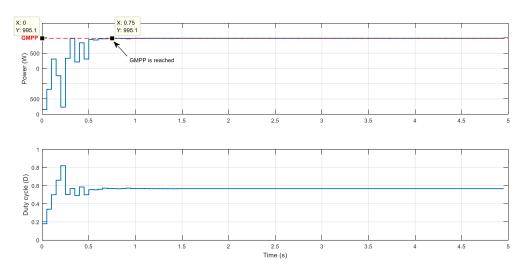

| 3.2.3.1      | Study of the convergence criteria                          | 53 |

| 3.2.3.2      | Study of stability, accuracy and robustness criteria       | 54 |

| a. I         | Rapid variation of the irradiation for a fixed temperature | 54 |

| b. I         | Rapid temperature change at fixed irradiation              | 55 |

| 3.2.3.3      | Effect of partial shading                                  | 56 |

| 3.3 Conclus  | ion                                                        | 63 |

| 4. Hardwa    | re Implementation of FA-MPPT Controller                    | 65 |

| 4.1 Introduc |                                                            |    |

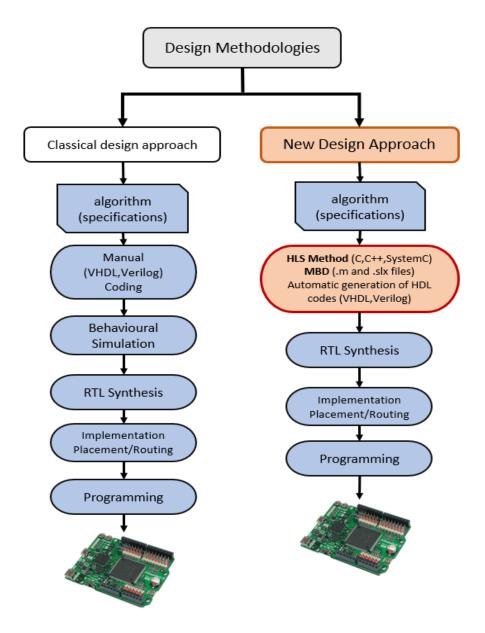

| 4.2 Hardwa   | re Design Methodologies                                    | 66 |

|              | GA                                                         |    |

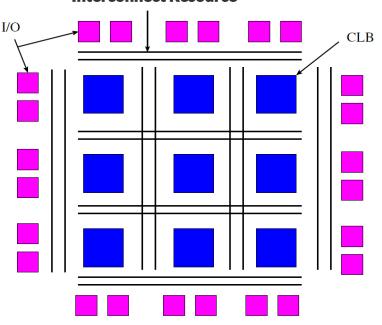

| 4.2.2 FPC    | GA Architecture                                            | 66 |

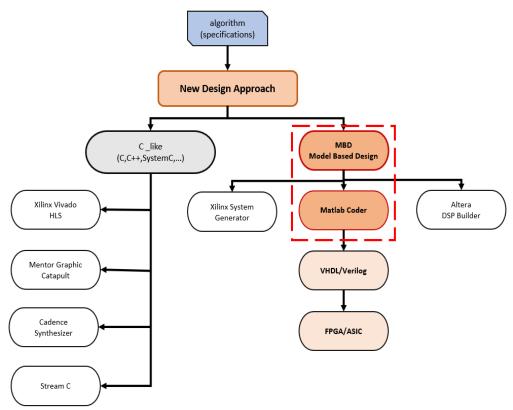

| 4.2.3 Evo    | lution of co-design methodologies                          | 67 |

| 4.2.3.1      | Bottom-Up methodology                                      | 67 |

| 4.2.3.2      | Top-Down methodology                                       | 67 |

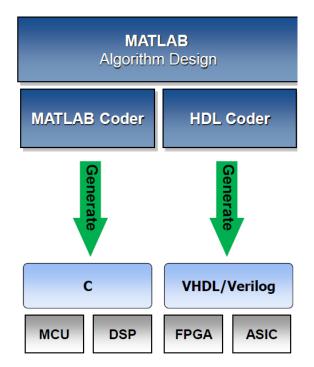

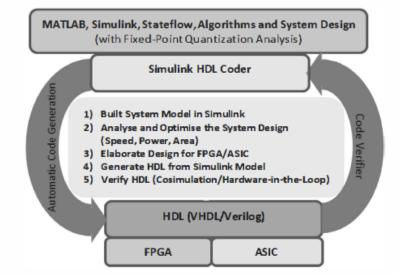

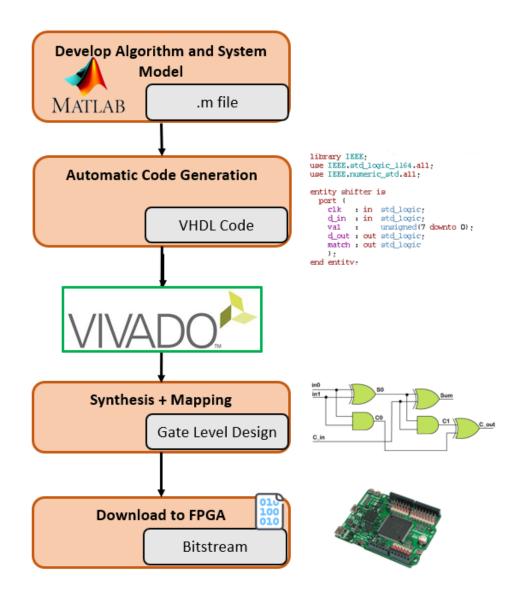

| 4.3 Model b  | ased design conception                                     | 71 |

| 4.3.1 HDI    | _ Coder                                                    |    |

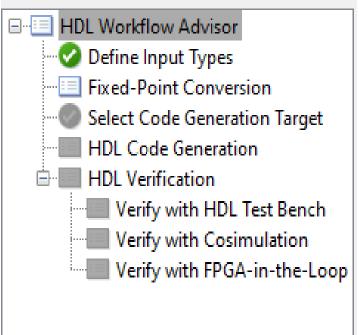

| 4.3.1.1      | HDL Workflow Advisor                                       | 73 |

| 4.3.1.2      | Fixed-Point Conversion                                     | 73 |

| 4.3.1.3      | HDL Verification                                           | 74 |

| 4.3.1.4      | HDL Synthesis                                              | 74 |

| 4.3.2 Viva   | ado Xilinx                                                 | 75 |

| 4.4 Applicat | ion of the MBD approach for the FA-MPPT controller         | 76 |

| 4.4.1 Intro  | oduction                                                   |    |

| 4.4.1 Worl   | kflow Advisor in MATLAB                            | 76 |

|--------------|----------------------------------------------------|----|

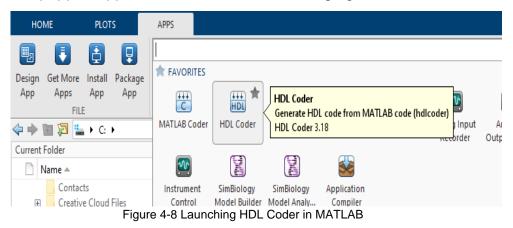

| 4.4.1.1      | Launching HDL Coder                                | 77 |

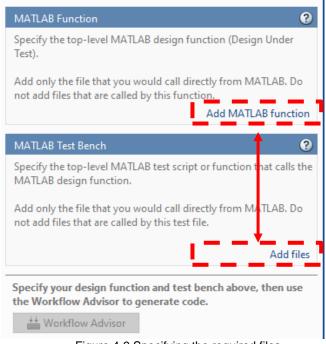

| 4.4.1.2      | Targeting .m Function and Test Bench               | 77 |

| 4.4.1.3      | Defining input types                               | 78 |

| 4.4.1.4      | Converting to fixed point and targeting the device | 78 |

| 4.4.1.5      | Generate HDL Code                                  | 79 |

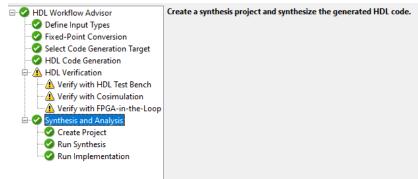

| 4.4.1.6      | Synthesis HDL Code                                 | 79 |

| 4.4.2 Worl   | kflow Advisor in Simulink                          | 79 |

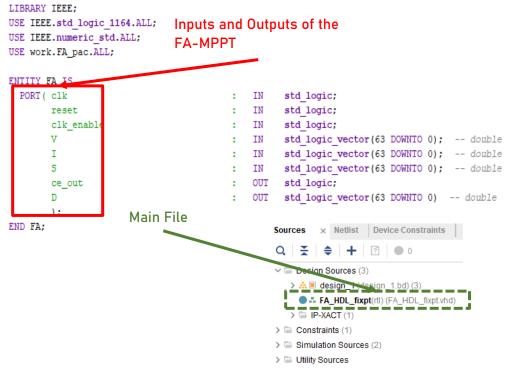

| 4.4.2.1      | Setting HDL Library                                | 79 |

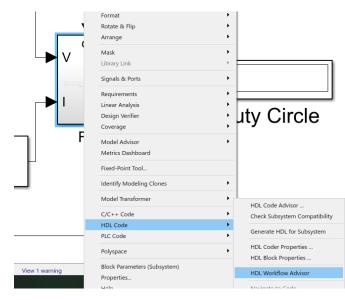

| 4.4.2.2      | Launching HDL Workflow Advisor                     | 80 |

| 4.4.2.3      | Set target device and Synthesis Tool               | 81 |

| 4.4.2.4      | Set target frequency                               |    |

| 4.4.2.5      | Check model settings                               | 81 |

| 4.4.2.6      | Set HDL Options                                    | 82 |

| 4.4.2.7      | Generate RTL code and testbench                    | 82 |

| 4.4.2.8      | Create project                                     | 83 |

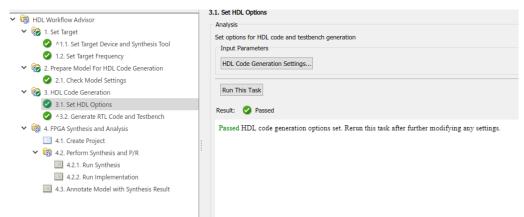

| 4.4.2.9      | Perform Synthesis and P/R                          | 83 |

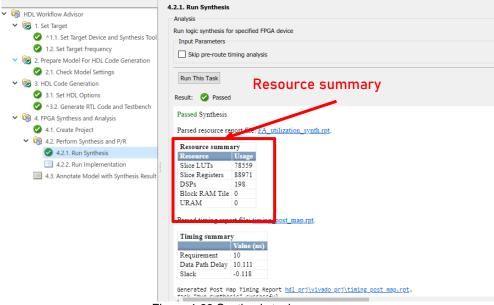

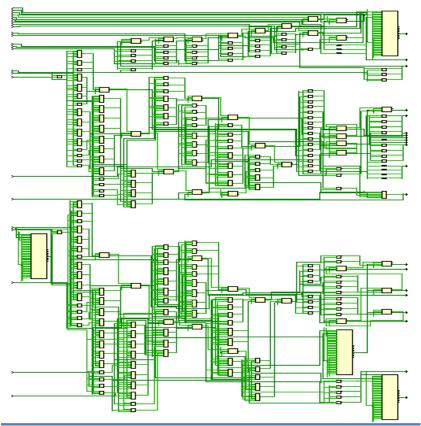

| 4.4.3 The    | generated HDL                                      | 84 |

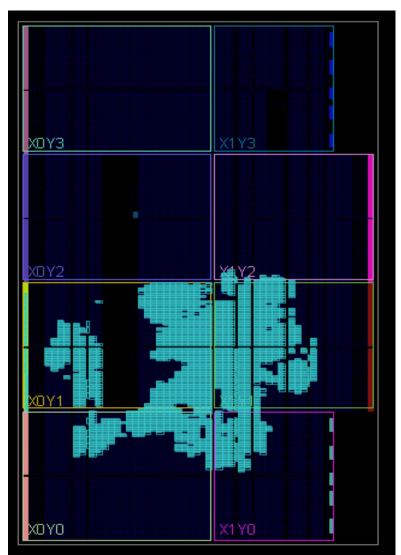

| 4.4.4 Synt   | hesis & implementation                             | 84 |

| 4.4.5 Gen    | erating bitstream file using Xilinx Vivado         | 87 |

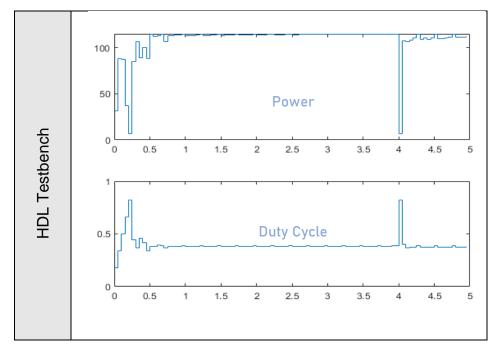

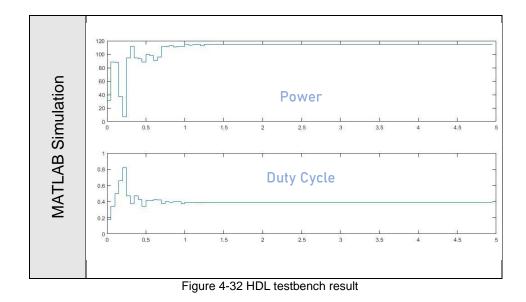

| 4.4.6 FPG    | A in the loop                                      |    |

| 4.5 Conclusi | on                                                 | 90 |

| General con  | clusion                                            | 92 |

| References   |                                                    | 94 |

|              |                                                    |    |

# Table of figures

| Figure 1-1 Four-inch polycrystalline silicon photovoltaic cell [7].                                                                                                                                                                                                                                                                                                                                  | 19                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Figure 1-2 Characteristic Curves [9]                                                                                                                                                                                                                                                                                                                                                                 |                                        |

| Figure 1-3 Shaded PV Cell [10]                                                                                                                                                                                                                                                                                                                                                                       |                                        |

| Figure 1-4 Shaded PV Cell with Bypass Diode Protection [10]                                                                                                                                                                                                                                                                                                                                          |                                        |

| Figure 1-5 Illumination influence [13]                                                                                                                                                                                                                                                                                                                                                               |                                        |

| Figure 1-6 Temperature influence [13]                                                                                                                                                                                                                                                                                                                                                                |                                        |

| Figure 1-7 Schematic diagram of the MPPT converter [15]                                                                                                                                                                                                                                                                                                                                              | 24                                     |

| Figure 2-1 Classification of Soft-Computing methods [27]                                                                                                                                                                                                                                                                                                                                             |                                        |

| Figure 2-2 Bio-inspired methods used with MPPT techniques in a PV system [4]                                                                                                                                                                                                                                                                                                                         |                                        |

| Figure 2-3 Fireflies                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

| Figure 2-4 Initial locations for 12 fireflies                                                                                                                                                                                                                                                                                                                                                        |                                        |

| Figure 2-5 Firefly position update shown with vectors                                                                                                                                                                                                                                                                                                                                                |                                        |

| Figure 2-6 After one iteration Figure 2-7 After five iterations                                                                                                                                                                                                                                                                                                                                      | 38                                     |

| Figure 2-8 Pseudo code of firefly algorithm                                                                                                                                                                                                                                                                                                                                                          | 39                                     |

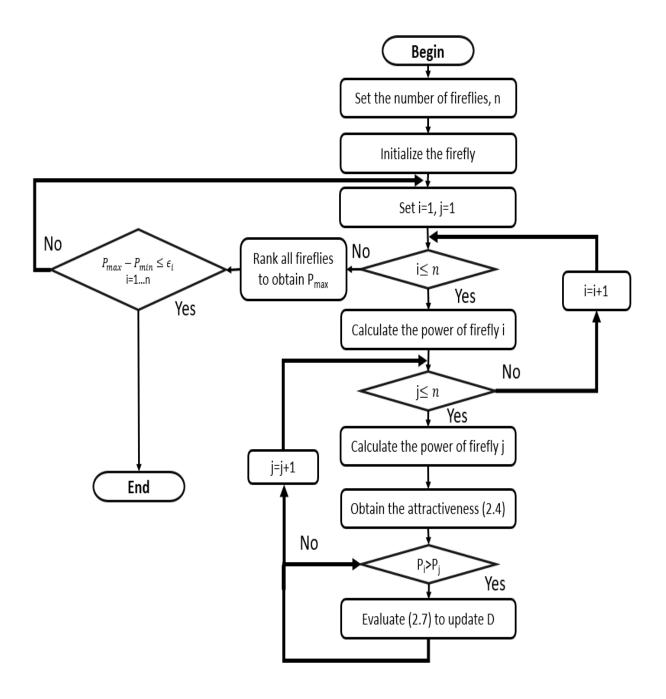

| Figure 2-9 Flow chart of the firefly algorithm [2]                                                                                                                                                                                                                                                                                                                                                   | 43                                     |

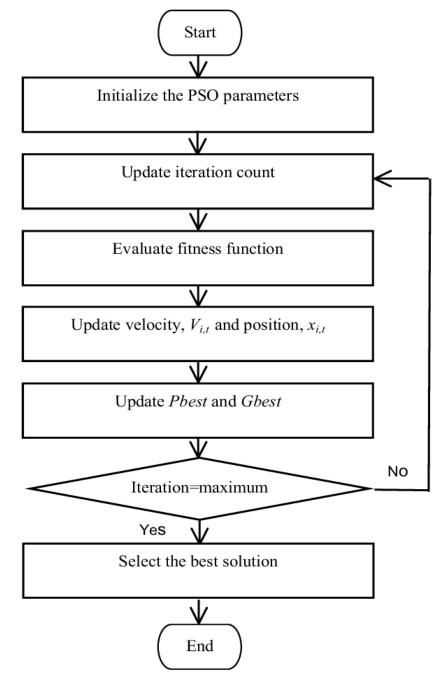

| Figure 2-10 Flow chart of the PSO algorithm [2]                                                                                                                                                                                                                                                                                                                                                      | 44                                     |

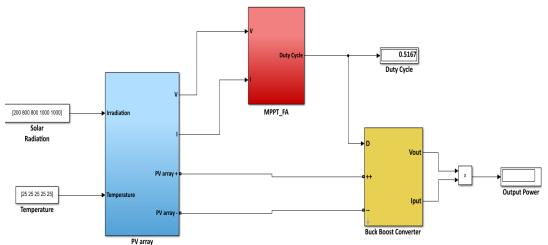

| Figure 3-1 Block diagram for PV system simulation                                                                                                                                                                                                                                                                                                                                                    |                                        |

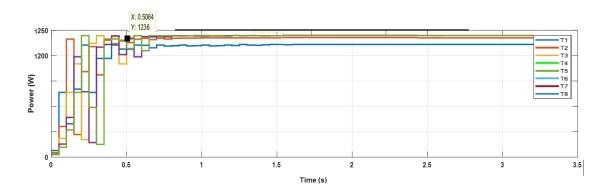

| Figure 3-2 Simulation for different values of the controller parameters. FA_MPPT                                                                                                                                                                                                                                                                                                                     | 50                                     |

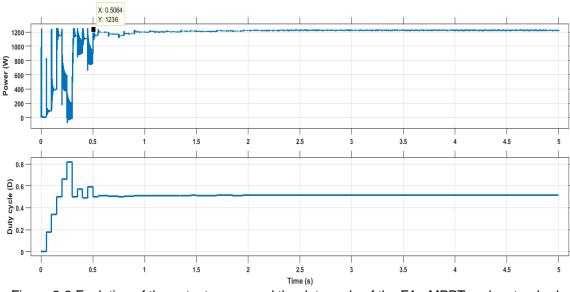

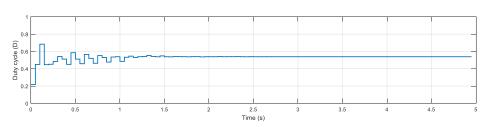

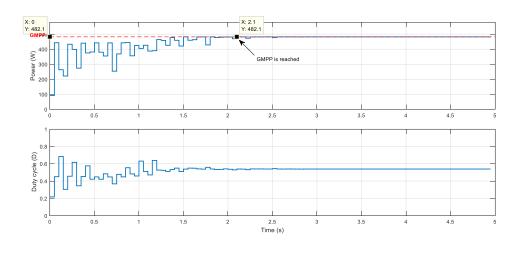

| Figure 3-3 Evolution of the output power and the duty cycle of the FA_MPPT under                                                                                                                                                                                                                                                                                                                     |                                        |

| standard conditions (Irr=1000 W/m^2,T=25 °C))                                                                                                                                                                                                                                                                                                                                                        | 53                                     |

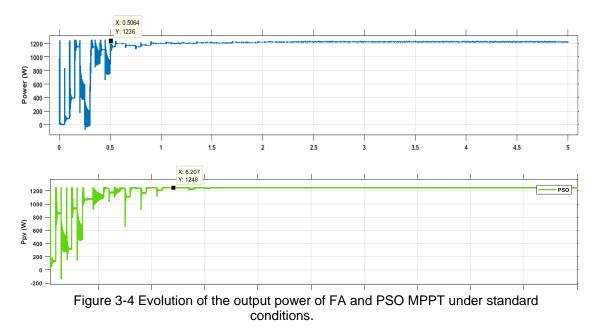

| Figure 3-4 Evolution of the output power of FA and PSO MPPT under standard conditions                                                                                                                                                                                                                                                                                                                | 3.53                                   |

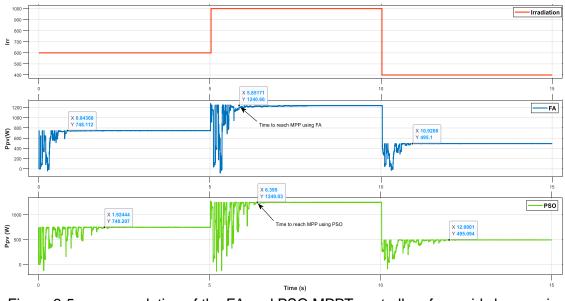

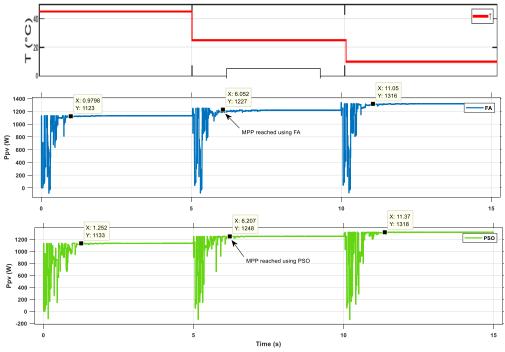

| Figure 3-5 power evolution of the FA and PSO MPPT controllers for rapid changes in                                                                                                                                                                                                                                                                                                                   |                                        |

| irradiation.                                                                                                                                                                                                                                                                                                                                                                                         | 54                                     |

| Figure 3-6 power evolution of the FA and PSO MPPT controllers for rapid changes in                                                                                                                                                                                                                                                                                                                   |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

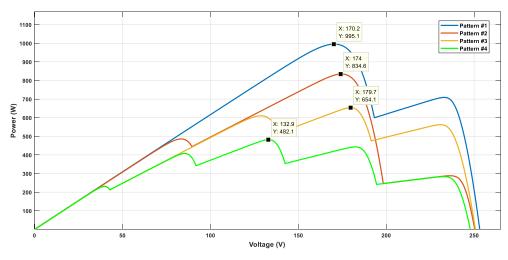

| Figure 3-7 P-V characteristic for different shading patterns.                                                                                                                                                                                                                                                                                                                                        | 57                                     |

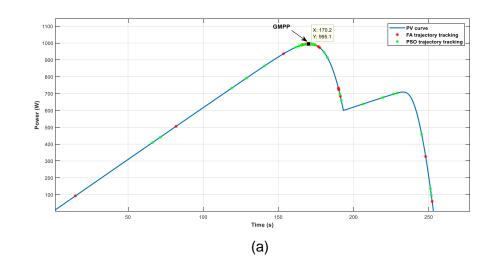

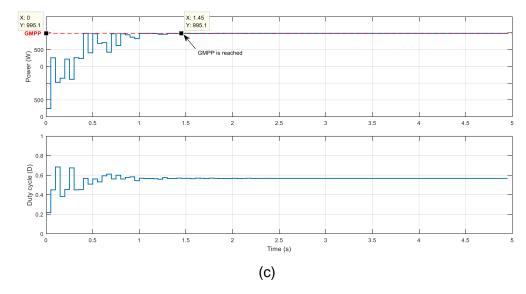

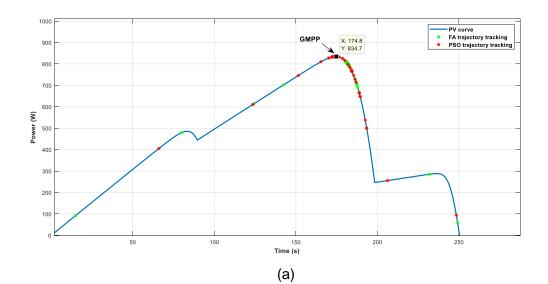

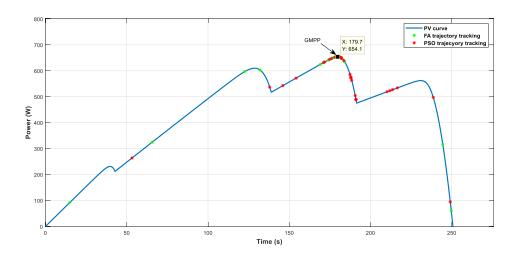

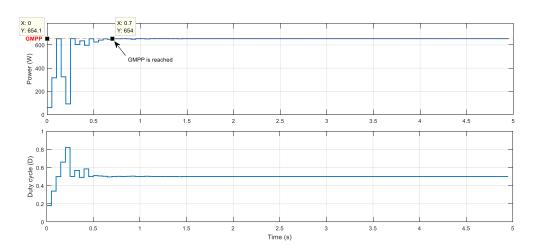

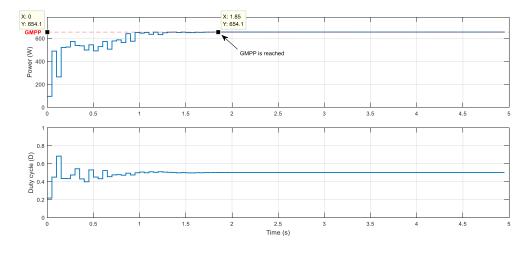

| Figure 3-8 The extracted power during the shading pattern #1 with, (a) P-V Trajectory tracking, (b) FA, (c) PSO.                                                                                                                                                                                                                                                                                     | 58                                     |

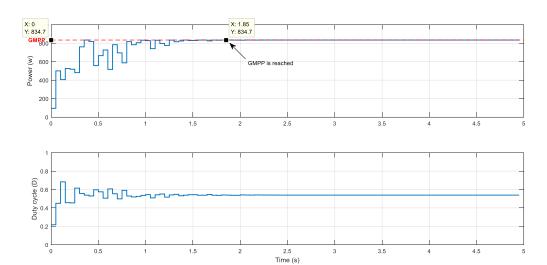

| Figure 3-9 The extracted power during the shading pattern #2 with, (a) P-V Trajectory                                                                                                                                                                                                                                                                                                                |                                        |

| tracking, (b) FA, (c) PSO.                                                                                                                                                                                                                                                                                                                                                                           | 59                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

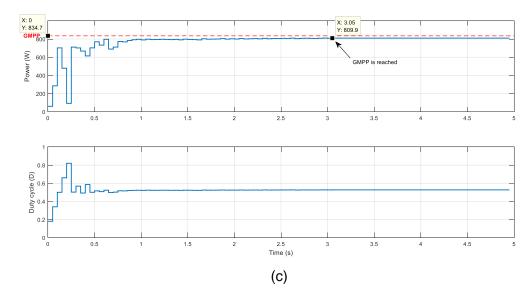

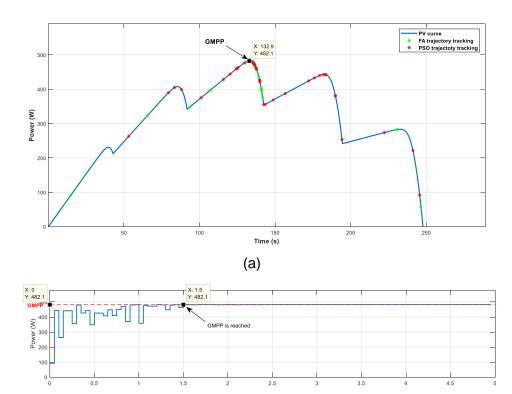

| Figure 3-10 The extracted power during the shading pattern #3 with, (a) P-V Trajectory                                                                                                                                                                                                                                                                                                               |                                        |

| tracking, (b) FA, (c) PSO.                                                                                                                                                                                                                                                                                                                                                                           | 60                                     |

| tracking, (b) FA, (c) PSO<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory                                                                                                                                                                                                                                                                                  |                                        |

| tracking, (b) FA, (c) PSO.<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory<br>tracking, (b) FA, (c) PSO.                                                                                                                                                                                                                                                   | 61                                     |

| tracking, (b) FA, (c) PSO.<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory<br>tracking, (b) FA, (c) PSO.<br>Figure 4-1 Architecture of an FPGA [32]                                                                                                                                                                                                        | 61<br>66                               |

| tracking, (b) FA, (c) PSO.<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory<br>tracking, (b) FA, (c) PSO.<br>Figure 4-1 Architecture of an FPGA [32]<br>Figure 4-2 design approaches.                                                                                                                                                                       | 61<br>66<br>68                         |

| tracking, (b) FA, (c) PSO.<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory<br>tracking, (b) FA, (c) PSO.<br>Figure 4-1 Architecture of an FPGA [32]<br>Figure 4-2 design approaches.<br>Figure 4-3 New Design Approach                                                                                                                                     | 61<br>66<br>68<br>70                   |

| tracking, (b) FA, (c) PSO.<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory<br>tracking, (b) FA, (c) PSO.<br>Figure 4-1 Architecture of an FPGA [32]<br>Figure 4-2 design approaches.<br>Figure 4-3 New Design Approach<br>Figure 4-4 HDL Coding methods for FPGA Programming [34].                                                                         | 61<br>66<br>68<br>70<br>72             |

| tracking, (b) FA, (c) PSO.<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory<br>tracking, (b) FA, (c) PSO.<br>Figure 4-1 Architecture of an FPGA [32]<br>Figure 4-2 design approaches.<br>Figure 4-3 New Design Approach<br>Figure 4-4 HDL Coding methods for FPGA Programming [34]<br>Figure 4-5 Method to generate HDL Code from MATLAB and Simulink [35]. | 61<br>66<br>68<br>70<br>72<br>72       |

| tracking, (b) FA, (c) PSO.<br>Figure 3-11 The extracted power during the shading pattern #4 with, (a) P-V Trajectory<br>tracking, (b) FA, (c) PSO.<br>Figure 4-1 Architecture of an FPGA [32]<br>Figure 4-2 design approaches.<br>Figure 4-3 New Design Approach<br>Figure 4-4 HDL Coding methods for FPGA Programming [34].                                                                         | 61<br>66<br>68<br>70<br>72<br>72<br>75 |

| Figure 4-8 Launching HDL Coder in MATLAB7    | 17      |

|----------------------------------------------|---------|

| Figure 4-9 Specifying the required files7    | 17      |

| Figure 4-10 Input types                      | 18      |

| Figure 4-11 running fixed-point conversion7  | 18      |

| Figure 4-12 The target device7               | /8      |

| Figure 4-13 HDL Code Generation7             |         |

| Figure 4-14 Synthesis and Analysis7          | 79      |

| Figure 4-15 HDL Documentation Blocks8        | 30      |

| Figure 4-16 target device and synthesis tool | 81      |

| Figure 4-17 Target frequency                 |         |

| Figure 4-18 Check model settings             |         |

| Figure 4-19 Set HDL Options                  |         |

| Figure 4-20 Generate RTL code and testbench8 | 32      |

| Figure 4-21 Create Project                   | 33      |

| Figure 4-22 Synthesis task                   | 33      |

| Figure 4-23 The generated VHDL in Vivado8    | 34      |

| Figure 4-24 Vivado's report                  | 35      |

| Figure 4-25 The synthesized FA-MPPT8         |         |

| Figure 4-26 Synthesis design8                | 36      |

| Figure 4-27 Artix7                           |         |

| Figure 4-28 PROGRAM AND DEBUG8               | 37      |

| Figure 4-29 auto connect option in Vivado8   |         |

| Figure 4-30 Programmed Device8               | 38      |

| Figure 4-31 Verify Code with HDL Test Bench8 |         |

| Figure 4-32 HDL testbench result             | <i></i> |

# Tables

| Table 1 Parameter and notation of FA                                      | 34 |

|---------------------------------------------------------------------------|----|

| Table 2 Terminologies in FA and PV system                                 | 40 |

| Table 3 GPV characteristics                                               | 48 |

| Table 4 Simulation results for different parameter values                 | 51 |

| Table 5 Irradiation setup of the four shading patterns (W/m^2)            | 56 |

| Table 6 Simulation results of the tracking speed, accuracy and efficiency | 63 |

# Abbreviation List

PVG: Photovoltaic Generator PSO: Particle Swarm Optimization **PV:** Photovoltaic FA: Firefly Algorithm MPP: Maximum Power Point **GMPP: Global Maximum Power Point** LMPP: Local Maximum Power Point MPPT: Maximum Power Point Tracking D: Duty Cycle DC: Direct Current P: Output Power of the photovoltaic module FLC : Fuzzy Logic Controller AFLC : Adaptative Fuzzy Logic Controller **INC:Incremental Conductance** BSO: Bat Swarm Optimization GWO: Gray Wolf Optimization **GPS:Generalized Pattern Search** SFL:Shuffled Frog Leaping PC:Parasitic Capacitance P&O:Perturb And Observe ANN: Artificial Neural Network PWM: Pulse Width Modulation. AI: Artificial Intelligence ACO: Ant Colony Algorithm ABC: Artificial Bee Colony CSA: Cuckoo Search Algorithm FPA: Flower Pollination Algorithm **PSC:Partial Shading Conditions** SI:Swarm Intelligence HDL: Hardware Description Languages DUT: Design Under Test FPGA: Field-Programmable Gate Array MBD: Model Based Design FIL: FPGA In the Loop

# **General Introduction**

#### **General Introduction**

The modern civilization with all its manifestations is based on the consumption of energy, a large part of which is from fossil sources. This consumption, which is reaching frighteningly high levels, is reducing the reserves of this type of energy for future generations, leading to the intensification of efforts and calls to seek new sources of inexhaustible energy. Hence the alternative solution of renewable energies that has been emerging since the sixties of the twentieth century. Among these renewable energies we find solar energy, wind energy, hydrogen and biomass.

Considering its geographical location, Algeria has an exceptional solar deposit, thanks to its large surface which exceeds ten hours per day during several months. The duration of insolation on almost the entire national territory exceeds 2000 hours annually and reaches 3900 hours (highlands and Sahara). The energy received daily on a horizontal surface of 1 m2 is about 5 kWh on most of the national territory, that is to say nearly 1700 kWh/m²/year in the North and 2263 kWh/m²/year in the South of the country. Therefore, the installation of large-scale solar panels in the south of the country can provide a sufficient amount of energy that fulfil to public needs and also contributes in reducing carbon footprint and the greenhouse gases (GHG).

The discovery of the photovoltaic effect, which consists of the conversion of light into electricity through sensors or photovoltaic cells, has allowed the development of this axis. This new source of electricity can produce energy ranging from a few milliwatts to megawatts.

Among the major problems encountered within photovoltaic (PV) systems is the random changes in solar energy received by the cells, which is due to the variation of atmospheric conditions (temperature and radiation) or to the non-uniform radiation. This latter is called partial shading condition PSC, and it is the result of having a shadowed panel. This shadow comes from moving clouds, a flock of birds moving, building or dust on the surface of the panels. During those conditions the photovoltaic system power generation decreases.

These different findings have motivated us to work on the optimization and control of the photovoltaic system using maximum power point tracking MPPT. This latter ensures a better exploitation of the solar energy source while ensures a robust control of the fluctuation encountered due to the partial shading effect and the temperature variations. The phenomena of partial shading in recall, causes high power losses. From an economic view point, these hindrances reduce the profitability of the production of photovoltaic systems.

Many works found in the literature have proposed technical solutions to reduce, or even eliminate, these phenomena. The ultimate goal is to operate photovoltaic systems at their maximum power points under any environmental conditions.

Several peaks occur in the power-voltage curve under partial shading conditions. Under such conditions, many conventional maximum power point tracking methods such as the P&O may be invalid due to blocking in a local maximum power point. These methods lack the intelligence to distinguish between a local maximum (LMPP) and a global maximum (GMPP) when the P-V characteristic is multimodal. Al methods such as the ANN, can achieve satisfactory results in global MPP tracking, but in the other hand they suffer from drawbacks. They need a lot of adjustments and training to obtain the optimal MPP. In order to overcome this problem, during the last decade, several researchers have proposed new methods based on algorithms inspired by nature: bio-inspired algorithms. This latter showed an astonishing result in finding MPP compared to conventional methods and AI, with regards of their simplicity, low computational time and less necessity of external equipment. We can mention some of popular bio-inspired algorithms in the field MPPT are: Ant Colony Algorithm (ACO) [1], Particle Swarm Optimization (PSO) [2], Artificial Bee Colony (ABC) [3], Firefly Algorithm (FA) [4]...

Thus, in our final project, we will present firefly (FA) algorithm for maximum power point tracking MPPT in a photovoltaic system. This algorithm is inspired by the social behaviour of Fireflies, namely the firefly (FA) algorithm.

In order to highlight the performance of the proposed algorithm, it will be compared with a Particle Swarm Optimisation (PSO) algorithm using MATLAB software. The simulation results will be detailed and discussed

To get the targeted algorithm in presence, the implementation of the generated HDL of the FA algorithm will be achieved using the MATLAB HDL Coder software, beside Xilinx Vivado in order to deploy it onto an ARTIX7 board.

This brief is organised into four chapters.

- Chapter 1 presents a brief description of the electrical energy in the world generally, and Algeria specifically, it also presents the basic concepts related to photovoltaic systems and the maximum power point tracking.

- Chapter 2, introduces the different maximum power point tracking methods and then presents the main features of the Firefly (FA) algorithm as a bioinspired optimization method. The application of the proposed algorithm and the Particle Swarm Optimization (PSO) algorithm as MPPT is discussed. The PSO technique is used to perform a comparative study in terms of performance.

- Chapter 3 presents a MATLAB-SIMULINK simulation of the realized photovoltaic system. The tracking and search performance of the MPP using FA and PSO algorithms are evaluated and compared in terms of tracking speed, accuracy and the ability to handle partial shading conditions.

- Chapter 4 presents the model-based design (MBD) conceptions and the different approaches of HDL generation for the FA-MPPT, mainly by targeting the HDL Coder and presenting the required steps until the deployment in the target device, beside simulating the generated HDL Code [5].

# **Chapter 1**

# Photovoltaic Electrical Energy

# **1.1 Introduction**

Currently in the world, electrical energy is produced, for the most part, through the combustion of fossil fuels (coal, oil and natural gas) or radioactive elements. The harmful impact of these processes of electricity production on the terrestrial environment is very important due to the emission of greenhouse gases and the generation of radioactive waste. For ecological considerations and to remedy the harmful effects of pollution due to fossil fuels, mankind is increasingly moving towards the use of clean and renewable resources, including solar energy.

The production of electricity by photovoltaic systems using solar energy is attracting greater interest, is growing significantly and is finding more and more new applications. Hence, the interest to study in detail this energy resource including its photovoltaic component. The constituent elements of photovoltaic systems and their functions.

Algeria, given its geographical position, has one of the highest solar deposits in the world. On the whole national territory, the global solar energy received per day on a horizontal surface of one square meter varies between 5.1 KWh in the North and 6.6 KWh in the Great South.

# **1.2 Photovoltaic Systems**

A photovoltaic panel transforms the Sun's energy into renewable electricity.

In concrete terms, a solar panel is composed of photovoltaic cells (made from crystalline silicon) that have the ability to transform the Sun's rays into direct current.

However, the appliances work with alternating current. That's why the electricity produced by the solar panel will be sent to an inverter whose role is to transform the direct current into alternating current.

A grid-connected PV system is composed of a set of components starting from the PV panels and ending with the grid. Several factors affect the performance of the grid-connected PV system. These factors can be: [6]

- Natural: such as weather conditions like solar radiation, ambient temperature and wind speed.

- Artificial: based on the different topologies of the conditioning devices (DC/DC converters and DC/DC converters and DC/AC converters), input and output filters and transformers.

## **1.3 The Photovoltaic Cell reviews**

#### 1.3.1 Definition

Photovoltaic cells (photon: grain of light and volt: unit of voltage) are semiconductor electronic components (usually made of silicon in its different forms).

They directly convert light energy into low voltage direct current electricity (photovoltaic effect). Since the light energy is the sun, they are referred to as solar cells.

Figure 1-1 Four-inch polycrystalline silicon photovoltaic cell [7].

#### 1.3.2 Definition

The solar cell, round or square, is the basic element of a solar system. A set of cells forms a solar module, in a module the cells are electrically connected to each other and encapsulated, thus protected from external agents. Several modules form a solar panel. Several panels form a system or solar field, to which are added protections, a regulator, an energy storage system (battery), control and measurement devices, an inverter [8].

The term PVG photovoltaic generator is used to refer to a PV module or panel, depending on the application. However, it can refer to the entire PV system.

#### **1.3.3 Characteristic Curves**

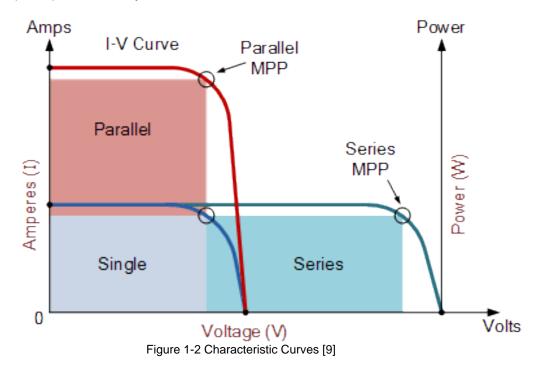

Photovoltaic panels can be wired or connected together in either series or parallel combinations, or both to increase the voltage or current capacity of the solar array. If the array panels are connected together in a series combination, then the voltage increases and if connected together in parallel then the current increases.

The electrical power in Watts, generated by these different photovoltaic combinations will still be the product of the voltage times the current, ( $P = V \times I$ ). However, the solar panels are connected together, the upper right-hand corner will always be the maximum power point (MPP) of the array.

## **1.4 Photovoltaic Cell Shading**

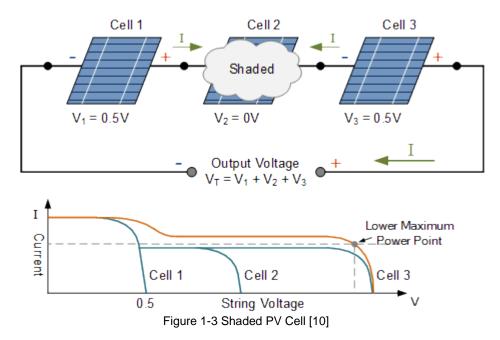

The solar Cell No.2 in the figure below in the string is either partially or fully shaded while the remaining two cells in the series connected string are not, that is they remain in full sun. When this occurs, the output of the series connected string will reduce dramatically with less current as shown.

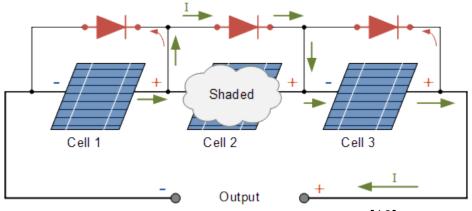

The forced current is therefore "pushed", so that the shaded solar cells heat up enormously. this can damage the solar cells, or even deform or shatter the glass plate of the panels. To prevent this, bypass diodes are incorporated into a solar panel, when there are solar cells that produce less energy, the current that must flow through these cells is diverted by a bypass diode. Thus, the panel is protected when there is shade on a part because the panel has several bypass zones, the electricity from the solar cells that have enough light is not lost.

Under this condition, cell two stops producing electrical energy and behaves like a semiconductive resistance. Due to the shaded cell generating reverse power, it forward biases the parallel connected bypass diode (i.e., it turns it "ON") diverting current flow of the two good cells through itself as shown [10].

Figure 1-4 Shaded PV Cell with Bypass Diode Protection [10]

As we have said PV array characteristic gets altered when complete or some parts of this system are shadowed by clouds, tall trees, deposition of dust, and surrounding buildings or shadow created by one of the PV arrays to others in outside environments. This

consequently leads to nonuniform irradiance conditions and results in superfluous losses in cells of the module in the form of overheating commonly known as hot spot. Hot spot phenomenon causes detrimental effects on partially shaded cells/modules, reducing the overall efficiency greatly. However, shunt resistance is taken as one of the parameters correspond to the shading effect in the mathematical modeling of a solar cell. All the three modules of the string receive uniform irradiance, thus corresponding P-V characteristics exhibit one MPP as depicted in the next Figure with the blue line. PSC occurred due to all the three modules receive different insolation. P-V characteristic gets altered and is not as smooth as in case of the uniform condition and exhibits multiple peaks under partial shading condition as shown in Figure below with the green line. PV characteristic shows a very complex behavior as a bypass diode (BD) is connected across each module to suppress the hot spot effect. Available output power across string under PSC is reduced as conventional MPPT gets trapped in one of the local peaks [11].

## 1.5 Effects of Climate Variations on the photovoltaic Module

#### 1.5.1 Influence of the illumination

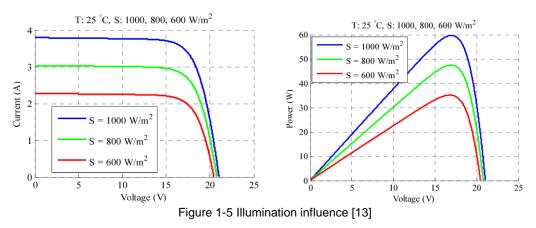

The brightness has a considerable influence on the performance of the cells.

As shown in this graph, the short-circuit current (Isc) increases proportionally with the illumination, while the open-circuit voltage (Voc) varies very little (about 0.5 V), thus, the greater the cloud cover, the lower the current generated [12].

#### 1.5.2 Influence of temperature

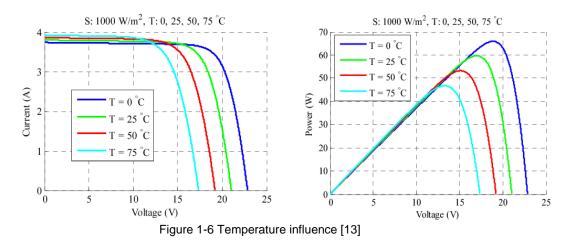

The temperature has a considerable influence on the behavior of the cell and therefore on its performance. This influence is mainly reflected by a decrease in the voltage generated (and a very slight increase in current) [14].

According to the models, this behavior induces, per degree, a loss of 0.5 % of the output compared to the maximum output of the cell. We can therefore understand the importance of a correct ventilation at the back of the panels!

### **1.6 MPPT**

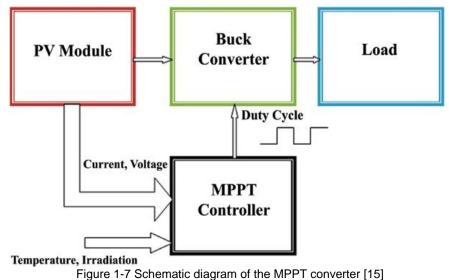

The power delivered by a PVG depends strongly on the level of sunlight, the temperature of the cells, the shading and also on the nature of the load fed. It is therefore very unpredictable. As we have already seen previously, the PV power characteristic curve has a maximum power point (MPP) corresponding to a certain operating point with coordinates  $V_{MPP}$  for the voltage and  $I_{MPP}$  for the current (see figure below). Since the position of the MPP depends on the level of sunlight and the temperature of the cells, it is never constant over time.

Figure 1-22 shows the schematic diagram of a typical MPPT converter. The MPPT control varies the duty cycle of the DC/DC converter which has three types, Buck-Boost converter, Buck converter: and Boost converter: in order to extract at each moment, the maximum power available at the PVG terminals and to transfer it to the load, this matching stage DC/DC converter is used. This stage acts as an interface between the two elements. It ensures, through a control action, the transfer of the maximum power supplied by the generator. The MPPT algorithm can be more or less complicated to find the MPP. In general, it is based on the variation of the duty cycle of the converter according to the evolution of the input parameters of the latter (I and V and consequently of the power of the PVG) until the MPP is reached. Several algorithms are present in the literature, such as the Bio-Inspired Algorithms whose are beside others: Practical Swarm Optimization (PSO), Differential Evolution (DE), Artificial Bee Colony (ABC) and the Firefly Algorithm (FA) which will be our main subject in the coming chapters.

## 1.7 Conclusion

In this chapter, we began by giving a brief description of the state of the art of electricity generation in general and renewable electricity generation in particular in the world and Algeria. Then, we introduced the general terms and concepts related to the field of photovoltaics and the principle of conversion of solar energy into electricity through the photovoltaic effect. It describes the role and characteristics of the photovoltaic cells. Finally, the effects of varying climatic conditions on the operation of these systems are described. This leads to the principles of finding the maximum power point MPP used for better solar energy conversion. And in the following sections, we will present the firefly algorithm by analyzing and simulating it in different conditions.

# **Chapter 2**

# Maximum power point tracking methods. State of art

## **2.1 Introduction**

The output power produced by a solar PV is not stable, it depends strongly on solar irradiation, temperature and load. As explained in Chapter 1, this variation is nonlinear and the power generated from the PV array is hardly predictable. When the solar panel is coupled directly to the load, it does not operate at the maximum power point (MPP) unless the load is properly matched to the PV system, but this matching won't last because of the continuous variation of environmental conditions.

Therefore, an MPPT control algorithm is needed to get superior efficiency and continuously extract the maximum power available from the PV module under static, varying and partial shading weather conditions.

To solve this MPPT optimization problem, many algorithms have been proposed in the literature. These methods react differently in different situations, each has its own advantages and disadvantages and varies in terms of complexity, efficiency, cost, convergence speed, hardware implementation etc.

In this chapter, we will first present the performance criteria of an MPPT controller. Then, we will adapt the Firefly bio-inspired algorithm to be implemented in an MPPT controller, present the basic concepts, describe the mathematical model and the different steps of algorithm. Moreover, in order to compare the performances of the studied controller, we have chosen to use a controller based on another bio-inspired algorithm, the PSO algorithm.

## 2.2 Performance criteria of MPPT algorithm

There are large numbers of the applied MPPT control techniques available to date that have been developed by researchers to maintain the PV array at its MPP. In order to compare between these techniques and to know which one better to implement for particular application, the followed specifications should be taken in consideration [16].

It should be noted that in the literature, it is difficult to find standard evaluation factors, some of which cannot even be measured accurately, which is an approximation.

#### • Tracking accuracy and efficiency:

High-performance MPPT algorithm has the ability to find the global MPP (GMPP) precisely at the right time and under rapidly changing working conditions. To demonstrate the performance of a technique, tracking accuracy and efficiency are important factors to evaluate.

Tracking accuracy is defined as the difference between the estimated power  $(P_{MPP\_est})$  of the PV array tracked by the algorithm and the theoretical power  $(P_{MPP\_theor})$  during the same period. It is considered as the error (ERR), which is expressed as [17]:

$$ERR(\%) = \left(1 - \frac{P_{MPP_{est}}}{P_{MPP\_true}}\right) * 100$$

Tracking efficiency is assessed in terms of the percentage of energy generated from the PV array during the simulation period, the equation below mathematically defined the tracking efficiency as [18]

$$\eta_{MPPT}(\%) = \frac{E_{MPPT}}{E_{MPP\_true}} = \frac{\int P_{MPPT}dt}{\int P_{MPP\_true}dt} * 100$$

#### Tracking speed (convergence time)

MPPT control algorithms must converge fast to MPP under rapidly changing weather conditions. The faster the dynamic response of the MPPT algorithm, the more solar energy is used.

#### Steady-state error

In steady-state, the algorithm should set the duty cycle to a constant value and minimize the oscillation of the operating point around the found GMPP. High steady state oscillations cause a loss of power and presumably reduce the PV system efficiency.

## **2.3 Classification of MPPT methods**

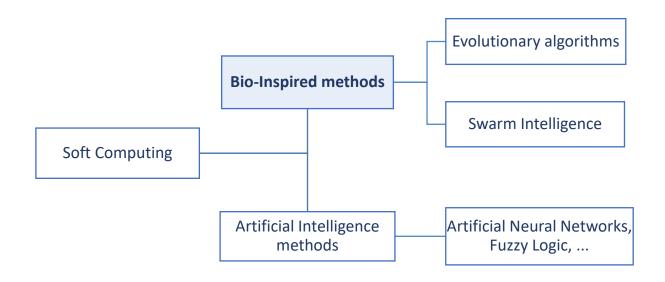

In literature, MPPT controllers have been classified as conventional methods and advanced (soft computing) methods. Conventional methods use very simple algorithms with low cost and they were initially employed for the PV systems. Contrary to the conventional methods, advanced methods are relatively complex and require high computation capacity [27].

## 2.3.1 Conventional methods

MPPT conventional techniques are widely used due to their simplicity, low cost and easy hardware implementation. Under uniform insolation conditions or slow irradiance changes, they provide a good tracking performance. However, these methods fail to find the GMPP under partial shading conditions (PSCs), even if they converge to the GMPP, they take a long time with low accuracy and with large steady state oscillation.

The most applied conventional MPPT methods are:

- Perturb and Observe (P&O) [19] [20]

- Incremental Conductance (INC) [19] [20]

- Parasitic Capacitance (PC) [21]

- Constant Voltage [22]

- Constant Current [23]

#### 2.3.2 Advanced methods

Advanced methods known as soft computing methods have been proposed as alternative approaches to solve the conventional methods obstacles. They have shown superior tracking performance under dynamic weather and partial shading conditions due to their robustness, flexibility, and reliability. Advanced methods can be classified into two subcategories as artificial intelligence (AI) and Bio-inspired (BI) methods. The figure below illustrates a classification of soft computing methods [27].

Figure 2-1 Classification of Soft-Computing methods [27].

As illustrated in the figure above, soft computing techniques include a number of methods, ranging from those based on artificial intelligence, such as neural networks, fuzzy logic, hybrid algorithms, etc., to newly introduced methods, namely bio-inspired methods.

These last ones have been very popular in the scientific community. In the following we will list the existing MPPT methods based on AI and bio-inspired.

#### 2.3.2.1 AI-Based Methods

Several studies have been proposed in the literature working on MPPT methods based on artificial intelligence. Among these, the most commonly used in MPP research, we can cite:

- Artificial neural networks (ANN) [24]

- Fuzzy logic controller (FLC\_MPPT) [25]

- Adaptive Fuzzy logic Controller (AFLC\_MPPT) [25].

- Genetic Algorithms combined with Fuzzy Logic (GA\_FLC\_MPPT), or with Artificial Neural Networks (GA\_ANN\_MPPT) [26]

Al methods achieve satisfactory results in accurately tracking GMPPs under PSCs. But they suffer from drawbacks such as the fact that the ANN requires a lot of effort to be adjusted to obtain the optimal MPP, and also needs to be well trained using a large number of measurements before its actual operation in the MPPT control unit to get accurate results. FLC controllers depend on rule base training and membership functions. There is no standard way to precisely define the controller parameters. FLC with constant parameters is inappropriate in an application where the operating conditions change over a wide range and

the available expert knowledge is unreliable. The solution to this problem is the use of an adaptive fuzzy logic controller (AFLC). The AFLC has the ability to readjust its parameters to achieve the best performance.

Moreover, these methods are very computationally intensive. This is a major drawback for them. This has led the scientific community to propose new intelligent methods to overcome the limitations of traditional artificial intelligent methods. These methods are based on the concept of bio-inspired. In what follows, we will focus on these new methods.

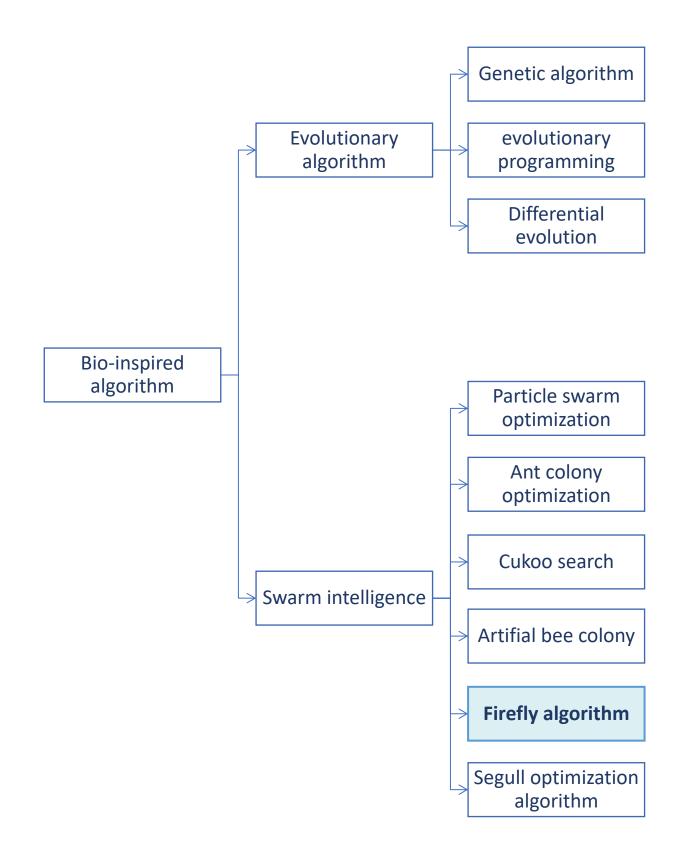

#### 2.3.2.2 Bio-Inspired (BI) methods

Recently, BI methods have attracted much attention due to their potential to find optimal solutions in complex optimization problems (such as multimodal objective functions). These methods are based on iterative improvement of a population of solutions or a single solution (e.g., Tabu Search) and mainly use randomization and local search to solve a given optimization problem [27].

As illustrated in Figure 2.2, the two most predominant classes of bio-inspired algorithms are evolutionary algorithms and swarm intelligence-based algorithms [4]. These algorithms are derived from the study of natural evolution and the swarming behaviour of living beings.

Figure 2-2 Bio-inspired methods used with MPPT techniques in a PV system [4].

In view of the advantages of Bio-Inspired methods, and the enthusiasm of the scientific community, they have a promising future in the field of renewable energies, given the number of existing works that still remains below.

Among the controllers designed based on bio-inspired algorithms, we can mention:

- MPPT controller based on the Ant Colony Algorithm (ACO), [1]

- MPPT controller based on the Particle Swarm Optimization (PSO) algorithm, [2]

- MPPT controller based on the Artificial Bee Colony (ABC) algorithm, [3]

- MPPT controller based on the Cuckoo Search Algorithm (CSA), [28]

- MPPT controller based on the Firefly Algorithm (FA), [4]

- MPPT controller based on the Bat Swarm Optimization Algorithm (BSO), [29]

- MPPT controller based on the Flower Pollination Algorithm (FPA), [29]

- MPPT controller based on the Gray Wolf Optimization (GWO) algorithm, [29]

- MPPT controller based on the Generalized Pattern Search (GPS) algorithm, [29]

- MPPT controller based on the Shuffled Frog Leaping Algorithm (SFL) [29].

Through the various works proposed in the literature on MPPT controllers designed around bio-inspired methods, and in view of their advantages, this motivated us to choose one of these methods in the context of our PFE, namely, Firefly algorithm (FA).

This latter has shown a good performance to find optimal solutions to complicated optimization issues faced in many applications, such as, optimization routing in wireless sensor networks, optimization antenna design, optimization scheduling, feature extraction in digital image processing, feature selection and detection of fault diagnostics and localizing the defects, etc.

In the context of power optimization in photovoltaic systems, this algorithm is recently being developed. in what follows, we will target mainly this algorithm in order to optimize the produced power. In the following section, we will focus on applying this algorithm in Maximum Power Point Tracking (MPPT) controller for PV systems through the implementation of its mathematical model to find the MPP of a photovoltaic generator.

## 2.4 The Firefly algorithm

The firefly algorithm, which was first developed by Xin-She Yang in late 2007 and 2008 at Cambridge University [30], is a population-based optimization that belongs to metaheuristic and stochastic swarm intelligence (SI) techniques.

This nature-inspired algorithm depends on the group behaviour of lightning bugs- commonly known as fireflies, it mimics their flashing pattern in the summer sky in the tropical temperature regions.

#### Figure 2-3 Fireflies

The basic idea of formulation of the FA is the attractiveness of fireflies, that fireflies attract each other according to the brightness (the less bright one will be attracted to the brighter one). Based on that, FA simulates the movement of fireflies to perform the position iteration, finds the optimal position and completes the optimization process.

#### 2.4.1 Basic concepts

To simplify the description of FA, various aspects of fireflies in nature must be idealized. First, real fireflies flash in discrete patterns, whereas modelled fireflies will be considered always bright. Second, the three following rules are considered to govern the algorithm and create the behaviour of a modelled firefly [30].

- All fireflies are unisex so the attraction between them is nor according to their gender.

- Attractiveness is proportional to their brightness and they both decrease as their distance increases. Thus, the lower bright firefly will move towards the brighter one. If there is no brighter one than a particular firefly will move randomly.

- Objective function which being optimized determines the brightness of Firefly.

When comparing the brightness of any two fireflies, the locations of the fireflies must be considered. It is known that the intensity of light (I) keeps on decreases as the distance (r) increase from the light source, it follows the inverse square law ( $I \propto 1/r^2$ ). In addition, the air absorbs the light and affects its intensity at a given distance from the light source. Due to these limiting factors, fireflies are visible within limited range, usually within several hundreds of meters that they can communicate.

| <b>Parameter</b><br>Brightness<br>Beta (β) | Notation in algorithm<br>Objective Function<br>Attractiveness |

|--------------------------------------------|---------------------------------------------------------------|

| 0                                          | ·                                                             |

| Beta (β)                                   | Attractiveness                                                |

|                                            |                                                               |

| Alpha (α)                                  | Randomization parameter                                       |

| Gamma (γ)                                  | Absorption coefficient                                        |

| Number of generations (G)                  | Iteration                                                     |

| Number of Fireflies (N)                    | Population                                                    |

| Problem Dimension (D)                      | Dimension                                                     |

|                                            | Number of generations (G)<br>Number of Fireflies (N)          |

Table 1 Parameter and notation of FA

### 2.4.2 Steps of the Firefly Algorithm [31]

#### 2.4.2.1 Initialization

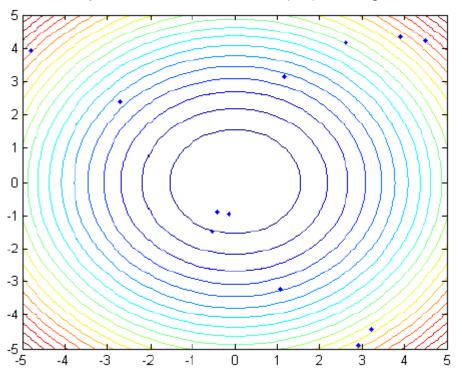

FA starts by assigning the fireflies to random positions, the position of a firefly refers to the values of the parameters of the objective function to be optimized. The objective function is then evaluated from the newly acquired position of each firefly. The light intensity (or brightness) is related to the evaluation. For a maximization problem, the brightness of a firefly *I* at a particular position *x* can be defined as  $I(x) \sim f(x)$ , where I(x) is the brightness and f(x) is the value of objective function at this position.

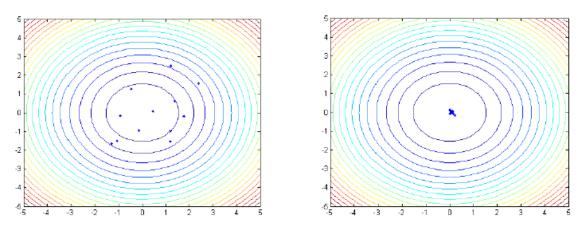

For a demonstration of initialization, shown in figure 2.4 is the initial location of twelve fireflies, in the 2-dimensional sphere function problem. The global minimum for this problem is 0 at the location (0,0), the origin.

#### 2.4.2.2 Exploration

After initialization, each firefly's brightness is compared against all the rest in the population, and the movement will be towards every brighter firefly it encounters. First, the distance between the fireflies, r, has to be calculated. For the general case the Cartesian distance is appropriate. The Cartesian distance that separates any two fireflies i and j at  $x_i$  and  $x_j$ , respectively, in ddimensional space is given as:

$$r_{ij} = ||x_i - x_j|| = \sqrt{\sum_{k=1}^d (x_{i,k} - x_{j,k})^2}$$

The attractiveness  $\beta$  is relative to the position of other fireflies. So, after the distance between two fireflies is known, the attractiveness  $\beta$  can be determined. To simplify the formulation, the attractiveness of a firefly is determined as a function of the light intensity. Thus, the attractiveness will vary with the degree of absorption of light [31]. Light intensity I(r) changes according to the inverse square law shown in equation (2.1).

$$I(r) = I_s/r^2$$

(2.1)

where  $I_s$  is the source intensity. Given a medium with a constant light absorption coefficient  $\gamma$ , the light intensity *I* will change with distance *r* as shown in equation (2.2) [31].

$$I = I_0 e^{-\gamma r} \quad (2.2)$$

where  $I_0$  is the original light intensity. In the expression  $I_s/r^2$  singularity at r = 0 can be avoided by the combined effect of both equation (2.1) and absorption can be estimated by the Gaussian form that controls the decrease of light intensity

$$I(r) = I_0 e^{-\gamma r^2} \quad (2.3)$$

Since the firefly attractiveness varies linearly to the intensity experienced by adjacent fireflies. Attractiveness of a firefly can now be obtained by

$$\beta(r) = \beta_0 \, e^{-\gamma r^2} \quad (2.4)$$

where  $\beta_0$  is the initial attractiveness at r = 0. Equation (2.4) defines a characteristic distance  $r = 1/\sqrt{\gamma}$  over which the attractiveness varies significantly from  $\beta_0$  to  $\beta_0 e^{-1}$ .

The attractiveness function  $\beta(r)$  is selected to be a monotonically decreasing function. Equation (2.5) shows the basic form.

$$\beta(r) = \beta_0 e^{-\gamma r^m}$$

,  $(m \ge 1)$  (2.5)

where *m* is an integer greater than 1. For a constant  $\gamma$ , the characteristic length is:

$$r = \gamma^{-1/m} \rightarrow 0, m \rightarrow \infty$$

(2.6)

The movement of a firefly towards more attractive (brighter) firefly is determined by the attractiveness  $\beta(r)$  and a random parameter. The random parameter is key for all metaheuristic algorithms; it allows the algorithm to escape from local optimums and to find the global optimal solution. A simple way to create a random walk distance is to use a uniform distribution in the range of [0.5, 0.5]. The movement can be either forward or backward, as both

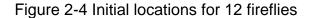

positive and negative values are possible. However, if two parameters of the objective function have different ranges of possible values, a fixed range of random numbers would cause different relative randomness for each dimension. To solve this problem, the random numbers generated can be multiplied by the scale of the function dimension, S, to produce a vector of scaling values. With all the terms together, the position update equation for a firefly being attracted to firefly becomes [20]:

$$x_i = x_i + \beta_0 e^{-\gamma r_{ij}^2} (x_i - x_j) + \alpha S(rand - 0.5)$$

(2.7)

Where the first term is the current position of a firefly, the second term is used for considering a firefly's attractiveness to light intensity seen by adjacent fireflies, and the third term is used for the random movement of a firefly in case there are no brighter ones. Where *rand* is a set of uniformly distributed random numbers in the range of [0, 1], and  $\alpha$  is a parameter controlling the amount of randomness. The randomness parameter  $\alpha$  is typically in the range [0, 1], where 0 corresponds to no randomness and 1 corresponds to being highly random.

Figure 2.5 shows the position update of the fireflies from their initial locations as shown in figure 2.1.

Figure 2-5 Firefly position update shown with vectors

After a firefly has been moved towards all brighter fireflies, its brightness is updated by evaluating the objective function in the new position. The new evaluation is also compared against the best found so far. If it is better, that position becomes the new best. In this way, if a firefly passes through a location better than any other found, but for whatever reason it or any other firefly does not end up there by the last iteration of the algorithm, that best location is still recorded. After re-evaluation, the given firefly is updated, and the algorithm moves on to the next firefly. One generation of the algorithm is performed after this continues for every firefly.

Figure 2.6 shows the sphere function example after one complete generation.

Figure 2-6 After one iteration

Figure 2-7 After five iterations

#### 2.4.2.3 Checking the convergence criteria

After each generation, it must be determined if the algorithm is complete or not. The simplest method for deciding when to stop is to run for a set number of generations and see if it is enough for fireflies to converge to the optimal position. This method is commonly used for its simplicity, but it can be inefficient. Another method is to check how much better the results are getting. Since the best firefly is stored, the previous best can also be stored. If the difference between the best and previous best is very small, then likely the fireflies have converged on the optimal location. This method is more complicated, however, since the value cannot be too large, as the global optimum may not have been reached yet, but it cannot be too small, because even when the fireflies converge, there are still small movements being made, and thus the algorithm would never end. A third approach to ending the algorithm is to set a value that is "good enough," so if the best firefly is as good or better than a given threshold value, we do not need to proceed any farther. This method is also easy to use, but it requires the knowledge of what is a good solution for the given problem.

Now that the entire algorithm has been covered, a summary in pseudocode is given in figure 2.8 below.

## Firefly Algorithm

Given:

Objective function f(x), where  $x = (x_1, x_2, ..., x_d)$  for d dimensions.

Light intensity  $I_i$  at  $x_i$  is determined by  $f(x_i)$

Define  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\delta$

Give random locations for N fireflies in D dimensions

Initial evaluation of all N fireflies

while (End condition not met)

Increment t

for i = 1 to NumFireflies

for j = 1 to NumFireflies

if  $(I_j > I_i)$

Move firefly *i* towards *j* in d-dimension

end if

end for j

Evaluate new solution and update light intensity

Check if the best position found so far

end for *i*

Reduce alpha

Sort the fireflies

end while

Find the best firefly

Figure 2-8 Pseudo code of firefly algorithm

### 2.4.3 Algorithm parameters

Proper tuning of the FA parameters is very necessary for global optimum searching. The most important parameter in firefly algorithm is  $\gamma$ , it characterizes the variation of the attractiveness and it plays a very crucial role of how fast the algorithm converges and how the algorithm behaves. The parameter  $\alpha$  allows the search process to escape the local search and search on the global scale.

As we will see in the next chapter, the implementation of this algorithm needs to set these parameters that guarantees a quick convergence to the optimal solution.

# 2.5 Application of the Firefly Algorithm (FA) for MPPT controller

The performance of the FA is exploited for the design of an MPPT controller to search for the optimal MPP in different working conditions.

In the implementation of this algorithm in MPPT, the position of the firefly (the regulated variable) represents the duty cycle that controls the DC-DC converter, and the objective function is chosen as the PV output power. The table 2 below shows how the FA terminologies match those of the PV systems.

| Firefly Algorithm               | PV system                                     |  |  |  |

|---------------------------------|-----------------------------------------------|--|--|--|

| Firefly position                | Duty cycle of DC-DC converter (d)             |  |  |  |

| Distance                        | Duty cycle difference $(\Delta d)$            |  |  |  |

| Attractiveness                  | Exponential function of distance $(\Delta d)$ |  |  |  |

| Brightness                      | Power $(P_{pv})$                              |  |  |  |

| Brightest Firefly               | Global maximum power $(P_{Gbest})$            |  |  |  |

| Dimension (number of variables) | one                                           |  |  |  |

Table 2 Terminologies in FA and PV system

The proposed method works as follow: