Admin Hahr

### UNIVERSITE D'ALGER ECOLE NATIONALE POLYTECHNIQUE

1/71

Département Télécommunications

THESE DE

BIBLIOTHEQUE

FIN D'ETUDES

Electronique

# Etude et Réalisation d'une Unité de Calcul à Circuits Intégrés

#### **JURY**

Président : Mr A. BENTCHIKOU Maître de Conference

Promoteur : Mme G. MONDON Ingénieur

Assesseur : Mr P. FLORET Ingénieur

Invité Mr Y. FLAMANT Professeur à l'Université d'Alger

Proposée par :

Etudiée et Réalisée par :

Mme G. MONDON

Mr B. Ahmed Bey

PROMOTION 71

#### UNIVERSITE D'ALGER ECOLE NATIONALE POLYTECHNIQUE

DEPARTEMENT TELECOMMUNICATIONS

### THESE DE FIN D'ETUDES

# ETUDE ET REALISATION D'UNE UNITE DE CALCUL A CIRCUITS INTEGRES

JURY:

Président: Mr. A. BENTCHIKOU:

Promoteur: Mnc. G. MONDON: Ingénieur

Assesseur: Mr. P. FLORET: Ingénieur

Invite: M-Y. FLAMANT:

Professeur à l'Université d'Alger.

Proposée par: Mme. G. MONDON

Etudiée et réalisée par:

Mr. B. AHMED-BEY

PROMOTION 1971

à mes parents

#### AVANT-PROPOS

Je tiens à remercier vivement Mme Georgette MONDON pour tous les conseils judicieux qu'elle a bien voulu me donner durant toute l'étude du projet et qui m'ont permis d'aboutir à sa réalisation.

Je ne manquerai pas d'exprimer aussi ma gratitude et ma reconnaissance à tous mes professeurs et assistants qui ont contribué à ma formation.

Que Mr.Y.FLAMANT trouve ici mes vifs remerciements pour l'aide précieuse qu'il m'a apportée lors du tirage du circuit imprimé.

Mes remerciements vont également à Mæ.DRIOUCHE techni--cien au laboratoire de Télécommunications pour sa précieuse collaboration lors de la réalisation pratique.

B. AHMED-BEY

| SOMMAIRE                                                    | Pages       |

|-------------------------------------------------------------|-------------|

| INTRODUCTION                                                |             |

| 1 PARTIE: NOTIONS FONDAMENTALES                             |             |

| Chap 1. Organisation générale d'un calculateur numérique .  |             |

| Chap 2. Eléments de logique                                 | 9           |

| Chap 3. Système de numération et de codage                  |             |

| Chap 4. Circuits logiques intégrés                          | 16          |

| 2 <sup>ème</sup> PARTIE: CIRCUTS DE CALCULS                 | 21          |

| Chap 1.Additionneur-soustracteur binaire                    |             |

| Chap 2.Multiplieur binaire                                  | 30          |

| Chap 3.Diviseur binaire                                     | 35          |

| Chap 4.Comparateur binaire                                  | 39          |

| 3 <sup>ème</sup> PARTIE: SYSTEME D'ENTREE - SORTIE          | 42          |

| Chap 1 Etude des régistre SN 7475 N                         |             |

| Chap 2.Circuits de commande de sortie des opérations        | 46          |

| 4 PARTIE: CONSTRUCTION DE L'UNITE DE CALCUL                 | 49          |

| ANNEXE 1: UNITE ARITHMETIQUE ET LOGIQUE ( Cas des nombres   | refrésentés |

| en valeur absolue et signe )                                | 54          |

| ANNEXE 2 : UNITE ARITHMETIQUE ET LOGIQUE EN VIRGULE FLOTTAI | NTE;67      |

| BIBLIOGRAPHIE                                               | 68          |

#### INTRODUCTION

Il existe actuellement deux grandes familles de calculateurs (lectroni--ques :

- CALCULATEURS ANALOGIQUES: ce sont des machines électroniques servant à l'étude des phénomènes où interviennent des grandeurs physiques à variation continue. Ils permettent de réaliser des similateurs c'est-à-dire de des appareils qui sont en correspondence étroite avec le phénomène qu'ils représentent. Mais ils sont si étroitement spécialisés qu'ils ne se prê-tent pratiquement qu'à un seul genre d'étude, voire même une seule étude particulière. Par exemple, les analyseurs différentiels servent à résoudre les équations différentielles alors que les calculateurs de tir permet-tent de déterminer la position d'une cible à une certaine époque. Leur précision est très limitée.

- CALCULATEURS NUMERIQUES: ils sont à la base de la "révolution informati-que ".Ils mettent en meuvre les principes fondamentaux du calcul arith-métique et assurent ainsi des fonctions logiques plus ou moins importan-tes et qui font d'ailleurs que l'on voit en eux des émules du cerveau

humain, capables d'activités apparentées à l'intelligence. Un des attributs

des calculateurs numériques est leur universalité; Parther des machines à

traduire, à établir des factures et bulletins, etc, c'est laisser croire

qu'il existe un grand nombre de types différents. Or, de par sa construction

même, le propre d'un calculateur numérique ou" ordinateur "est de ne pouvoir accomplir certaines opérations arithmétiques et logiques très élémen-taires. C'est la combinaison ordonnée d'une multitude de telles opérations

successives qui lui permet de traiter tel ou tel problème.

L'attribut majeur de l'ordinateur est cependant sa rapidité d'action qui a véritablement révolutionné le traitement de l'information. Cette rapidité il la doit à l'électronique qui a permis d'éliminer totalement dans son fonctionnement interne les éléments mécaniques doués d'inertie.

En dix ans, nous avons vu se succéder trois générations de calculateurs électroniques :

<sup>- 1</sup> ère génération : numération décimale, tubes, mémoires à tambour magnétique ( IBM 650 ).

- $2^{\rm ème}$  génération : numération décimale, transistors, mémoires à ferrite ( IBM 1401 ).

- 3<sup>ème</sup> génération : numération à la fois décimale et binaire, mémoire à ferrite dont la technologie est diversifiée, circuits intégrés.

De ce fait, les opérations y sont effectuées à une vitesse prodigieuse. Avec les semi-conducteurs, sous forme de diodes ou de transistors, une multipli-cation no prenait guère qu'une mulliseconde, il y a peu de temps encore. Avec les circuits intégrés des micromodules on atteint la microseconde. La durée se réduit aux limites de l'imaginable cer actuellement on chiffre les commutations en nanosecondes.

A sa souplesse d'adaptation à des problèmes de traitements variés, à sa remarquable rapidité d'exécution des opérations arithmétiques et logiques, à sa capacité de mémorisation, l'ordinateur ajoute une qualité précieuse : Fiabilité.

Il est à peine besoin de mentionner les services irremplaçables des calculateurs électroniques dans le domaine scientifique et technique.

Cependant, notre étude ne se basera que sur la partie centrale d'un cal--culateur numérique : L'UNITE DE CALCUL.Celle-ci permet d'effectuer une des opérations arithmétiques quelconques sur des nombres de quatre bits.

L'étude de cette unité de calcul se divisera en quatre parties :

- 1. Notions fondamentales

- 2. Circuits de calcul

- 3. Système d'entrée-sortie

- 4. Construction de l'unité de calcul.

NOTIONS

FONDAMENTALES

#### CHAPITRE 1 : ORGANISATION GENERALE D'UN CALCULATEUR NUMERIQUE

#### 1.Généralités:

#### 1.1.Définition d'un algorithme:

On appelle algorithme l'ensemble des prescriptions précises qui indi--quent d'exécuter, dans un ordre déterminé, une certaine succession d'opéra--tione permettent d'obtenir la résolution de tous les problèmes d'un type donné. Il se présente comme un mode opératoire. Pour exécuter un algorithme, on définit d'abord un mode de codage de l'information.

#### 1.2.Programme et structure d'une instruction:

On appelle programme la suite d'instructions nécessaires à l'exécution d'une opération. Ces instructions indiquent à chaque intaant les opérations que doit exécuter le calculateur. Ce programme est enregistré dans le calculateur avant son utilisation et peut être modifié suivant les besoins et les applications à traiter.

Une instruction est une opération de base que le calculateur est capa-ble de déclencher en une seule fois.On distingue des instructions à plu-sieurs ad esses(1,2,3,et 4).L'instruction à une simple adresse se compose

de deux mots; le premier étant réservé au code opératoire (indiquant la nature

de l'opération à effectuer) et le second à l'adresse de l'opérande.

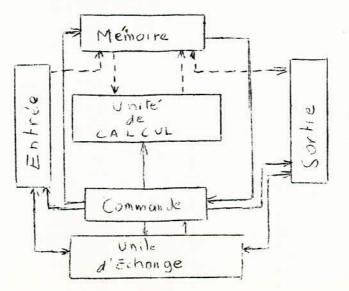

#### 2.Blocs fonctionnels d'un calculateur numérique:

D'une façon générale, le bloc-diagramme d'un calculateur numérique peut se présenter comme suit :

transfert des données

transfert d'ordres

ou d'information de contrôle.

Les fonctions d'un calculateur sont exercées par six organes principaux: les circuits d'entrée-sortie, la mémoire, l'unité de calcul, les circuits de com---mande et de contrôle et l'unité d'échange.

#### 2.1Les circuits d'entrée:

Ils permettent au calculateur d'ingérer l'information en provenance de l'extérieur et servent de traducteur du langage extérieur vers le langage interne à la machine.

Information lue sur le dispositif d'entrée.

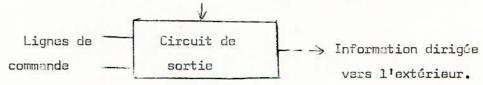

#### 2.2.Les circuits de sortie:

Ils jouent le même rôle que les circuits d'entrée et délivrent l'infor--mation traitée vers l'extérieur.

Information à écrire sur le dispositif de sortie.

#### 2.3.La mémoire:

Elle sert à contenir le programme et les données. Elle se présento comme un certain nombre de positions ayent un accès unique. Chaque position est affec -fectée d'un numéro constituant l'adresse de l'information qui s'y trouve enre-gistrée. L'adressage de la mémoire permet la localisation et la sélection des informations.

Dans une mémoire, il y a deux fonctions à réaliser:

- stockage de l'information

- sélection de la position choisie extérieurement.

D'autre part, cette mémoire est caractérisée par:

- se vitesse de fonctionnemnt qui se mesure par le temps de cycle de la mé--moire : c'est le temps minimum qui sépart deux opérations consécutives à des adresses arbitraires soit de lecture soit d'écriture. - le temps d'accès séparantl'instant où l'on présente une demande de lecture à l'entrée de l'instant auquel l'information est disponible sur les connections de sortie.Ce temps d'accès est fonction de la technologie employée.

Le support de l'information en mémoire est constitué, dans la plupart des machines actuelles, par des ferrites ou tores magnétiques.

#### 2.4.Unitó de calcul:

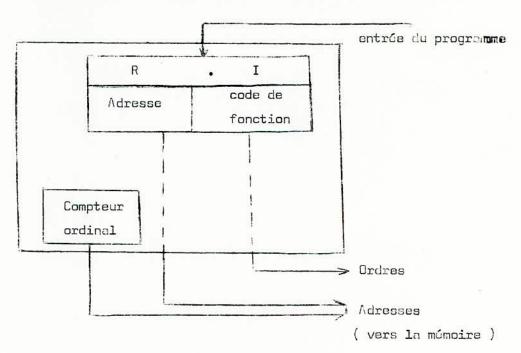

C'est le bloc où s'effectue le calcul proprement dit ( voir pagraphe 3). 2.5.Unité de commande et de contrôle:

C'est le bloc qui organise et coordonne le déroulement d'un programme. Il comporte une entrée instruction, envoyée de la mémoire, placée dans un régis—tre instruction R.I.Celui—ci contient l'adresse et le code de fonction. A par—tir de ces informations, le bloc de commande et de contrôle fournit des ordres à la mémoire et aux autres organes leur indiquant les opérations qu'il y a lieu d'exécuter et les adresses des informations sur lequelles portent ces opéra—tions. Un compteur ordinal permet de retenir à chaque instant le numéro de la position de lá mémoire d'où a été extraite l'instruction en cours de traite—ment. Le bloc de commande et de contrôle peut être représenté comme suit :

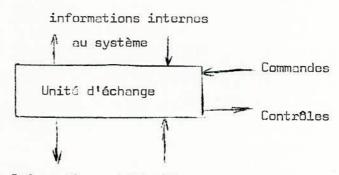

#### 2.6.L'unité d'échange:

C'est une unité qui ne modifie pas l'information mais opère un change-ment de nature physique sur le mode de codage de l'information.Par exemple, si

un calculateur est construit pour calculer en numération binaire, il faut évidemment que les données parviennent en binaire dans les circuits de calcul.

Mais l'opérateur les fournit généralement en numération décimale.L'unité

d'échange réalise cette conversion binaire-décimule.Elle peut se présenter

comme suit :

Informations utilisables extérieurement au système

#### 3.L'unité de calcul :

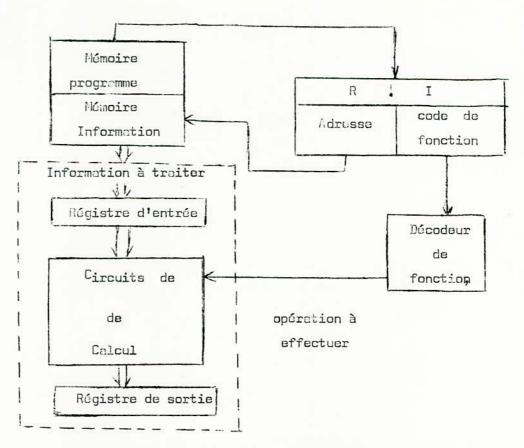

L'unité de celcul est la pertie centrale du calculateur numérique qui effectue les calculs nécessaires au déroulement d'un programme donné. Elle doit être en mesure de résoudredles quatre opérationsélémentaires: addition, sous-traction, multiplication et division. Ces opérations se réduisent en général à une succession d'additions. L'unité de calcul comprend un régistre d'entrée qui reçoit les informations à traiter sous forme d'un ou de deux mots simul-tanés contenent les opérandes, un régistre de sortie qui emmagasine le résul-tat de l'opération et les circuits de calcul.

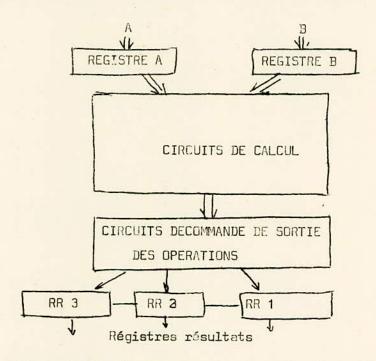

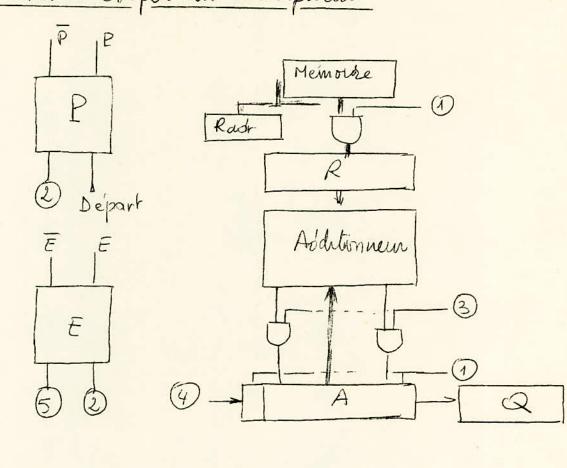

Le schime de l'unité de calcul est représenté comme suit : Suivant le code opératoire, délivré par l'unité de commande, l'unité de calc

Suivant le code opératoire délivré par l'unité de commande, l'unité de ca calcul met en coordination toutes les portes nécessaires à l'opération demandée. La construction de cette unité est indépendante de la nature des opérations à effectuer. Seul le nombre des régistres utilisés et leur fonctionnement diffère suivant la complexité des opérations.

On distingue deux types d'unité de calcul:

- l'unité de calcul série :comporte un seul circuit de calcul pour chaque fonction; tous les éléments binaires successifs des nombres traités passent successivement en série dans ce circuit unique C'est une machine lente mais économique.

- l'unité de calcul parallèle:comporte autant de circuits de calcul à fonctionnement simultané qu'il y a d'éléments binaires dans les mots traités. C'est une machine rapide mais très coûteuse.

#### CHAPITRE 2 . ELEMENTS DE LOGIQUE

#### 1.Rappels sur l'algèbre de BOOLE :

#### 1.1.Postulats:

$$a + a = a$$

$a \times a = a$

$a + 0 = a$   $a \times 0 = 0$

$a + 1 = 1$   $a \times 1 = a$

#### 1.2.Propriétés:

$$a = a a(b+c) = ab + ac$$

$$a + a = 1 (a + b)(a + b) = a$$

$$a \cdot a = 0 a + a \cdot b = a + b$$

#### 1.3. Théorèmes de DE MORGAN:

\*

$$a_1 a_2 \cdots a_n = \sum_{i=1}^{n} a_i$$

\*

$$a_1 + a_2 + \cdots + a_n = \prod_{i=1}^{n} a_i$$

#### 2.Opérations arithmétiques:

| Addition                | Soustraction             |

|-------------------------|--------------------------|

| 0 + 0 = 0               | 0 - 0 = 0                |

| 0 + 1 = 1               | 0 - 1 = 1  ( retenue 1 ) |

| 1 + 0 = 1               | 1 - 0 = 1                |

| 1 + 1 = 0 ( retenue 1 ) | 1 - 1 = 0                |

#### 3.Niveaux logiques:

En général, les circuits logiques comportent des bornes d'entrée et des bornes de sortie. Les tensions appliquées aux bornes d'entrées et recueillies aux bornes de sortie peuvent prendre deux niveaux logiques:

- niveau haut H auquel correspond le plus fort voltage

- niveau bas B " " faible voltage.

La présence du niveau H caractérise la <u>logique dite positive</u>. Ainsi le niveau H exprime le "1" logique et le niveau bas B exprime le "0" logique.

Si le O logique correspond au niveau H et le 1 logique au niveau B, la logique est dite négative.

En général, avec les circuits logiques intégrés, on préfère utiliser la logique positive. En effet, la borne de sortie des citcuits logiques intégrés est, dans la plupart des cas, constituée par le collecteur d'un transistor NPN, monté en émetteur commun(à la masse) et saturable. Dans ces conditions, le niveau bas de sortie correspond à la tension de saturation V<sub>CE</sub> très voisine de 0 volt. Ce 0 Volt évoque donc le "0" logique et on est tenté de faire coîcider ces 2 zéros. Pour des transistors PNP, le 0 Volt correspond au niveau haut.

Exp:

$$R_B$$

$R_C$

$R$

Par application des théorèmes de De Morgan, un circuit réalisant la fonction ET en logique positive, réalise la fonction OU en logique négative et inversement. Il en est de même pour les fonctions NOR et NAND.

#### Remarque:

Dans toute la suite de l'étude, on raisonnera toujours avec la logique positive.

#### CHAPITRE 32. . SYSTEME DE NUMERATION ET DE CODAGE

#### 1.Généralités:

Dans le système de numération décimale, auquel nous sommes habitués, la représentation physique d'un chiffre qui peut prendre une valeur quelconque de D à 9, nécessite l'emploi d'un organe susceptible de prendre dix états distincts caractérisant chacun l'un des dix chiffres de numération . Mais les organes des calculateurs numériques qui sont de nature électrique, magnétique, cu électronique ne permettent en effet de distinguer que deux états. Ainsi les premières machines utilisaient des relais mécaniques. Un relai ne peut être qu'ouvert ou fermé. Plutard, les relais ont été remplacés par des tubes électroniques et des transistors qui ne peuvent également prendre que deux états distincts: un tube ou un transistor est saturé ou bloqué. L'arithmétique et les calculs effectués par la machine seront donc tributaires de cette nature particulière des circuits.

Ceux-ci ne connaissant et ne prenant que deux états on leur attribue les valeurs 10' et '1' qui correspondent à un circuit ouvert ou fermé. C'est de cette constatation qu'est née l'idée d'utiliser dans les calculateurs numériques le système de numération à base 2 ou " système binaire ".

#### 2. Système binaire:

On appelle bit ou digit l'un des symboles 0 ou 1 utilisés pour représenter un nombre sous sa forme binaire .La base du système binaire étant 2, on affecte à chaque bit les poids correspondants  $2^0, 2^1, \ldots, 2^n$ , le poids  $2^n$  correspond au bit le plus à droite.Ainsi, le nombre 110110 s'écrit :

$$110110 = 1.2^{5} + 1.2^{4} + 0.2^{3} + 1.2^{2} + 1.2^{1} + 0.2^{0} = 54$$

soit (110110)<sub>2</sub> = (54)<sub>10</sub>

Dans le cas des nombres fractionnaires, on attribue aux bits de la partie fractionnaire des poids inférieurs à 1 soit 2<sup>-1</sup>,2<sup>-2</sup>,...,2<sup>-n</sup>.On utilise un point pour séparer la partie entière de la partie fractionnaire.Ainsi, le nombre 110.11 s'écrit :

$$110.11 = 1.2^{2} + 1.2^{1} + 0.2^{0} + 1.2^{-1} + 1.2^{-2} = 6,75$$

soit:  $(110.11)_{2} = (6,75)_{10}$

D'une façon générale, dans un système de numération à base 2, un nombre quelconque s'écrit :

$$X_{n}X_{n-1}\cdots X_{0}\cdot X_{-1}X_{-2}\cdots X_{-m} = X_{n}2^{n}+\dots+X_{0}2^{0}+X_{-1}2^{-1}+\dots+X_{-m}2^{-m}$$

#### Remarque:

Outre le système binaire,ontrouve les systèmes de numération à base 3 ( ternaire), à base 8 (octal) et à base 16 (sexadécimal).Notons que le système à base 60 est encore utilisé dans la mesure du temps et de la température.

#### 3.Conversion décimal-binaire:

Etant donné que les nombres traités dans les calculateurs numériques sont des nombres binaires, il est nécessaire de pouvoir convertir un nombre déci-mal en un nombre binaire.

Dans le cas des petits nombres, on soustrait successivement d'un nombre quelconque les plus hautes puissances de 2 et on attribue le bit 1 à ces puisrances si elles existent et le bit 0 si elles n'existent pas.

Exp: soit à convertir le nombre décimal 29.

$$29 - 2^4 = 13$$

d'où:  $2^4 2^3 2^2 2^1 2^0$

$13 - 2^3 = 5$  1 1 1 0 1

$5 - 2^2 = 1$  (29)  $10 = (11101)_2$

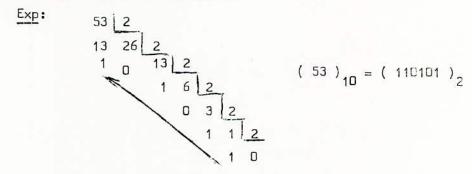

Dans le cas des grands nombres, il suffit de diviser un nombre donné suc--cessivement par 2.La succession des restes donne le nombre binaire.Le dernier reste correspond au plus fort poids.

Pour convertir un nombre décimal fractionnaire, on décompose ce nombre en une partie entière et une partie décimale dont on calcule séparément leur représentation binaire. Puis les deux parties converties seront juxtaposées côte à côte.

Pour des nombres fractionnaires de faible longueur, en retrenche successi-vement du nombre à convertir les plus hautes puissances négatives de 2 jusqu'à

épuisement du reste ou de la précision désirée.

Exp:

$$0.943 - (1.2^{-1}) = 0.443$$

$0.443 - (1.2^{-2}) = 0.193$

$0.193 - (1.2^{-3}) = 0.068$

$0.068 - (1.2^{-4}) = 0.004$  (0.943)  $0.943$

Pour des nombres fractionnaire de grandes longueur, on multiplie par 2 la partie décimale. Si un 1 apparaît à gauche du point décimal, on place un 1 juste àprès le point décimal du nombre binaire en formation. Si après multipli-cation par 2 un 0 apparaît à gauche du point décimal du nombre à convertir, on marque un 0 à droite du point décimal du nombre en formation.

| Exp: | $0.843 \times 2 =$ | 1.686           | 0.1           |

|------|--------------------|-----------------|---------------|

|      | $0.686 \times 2 =$ | 1.372           | 0.11          |

|      | 0.372 x 2 =        | 0.744           | 0.110         |

|      | $0.744 \times 2 =$ | 1.488           | 0.1101        |

| so   | oit ( 0.843 )      | 10 = ( 0.1101 ) | a par défaut. |

#### 4. Représentation des nombres quelconques :

Il existe deux modes de représentation des nombres:

#### 4.1. Représentation en virgule fixe :

La convention de représentation des nombres entiers consiste à supposer que la virgule séparant la partie entière de la partie fractionnaire d'un nombre est toujours située immédiatement à droite du dernier chiffre de ce nombre. Si l'ordre de grandeur des informations traitées reste toujours le même, il est possible de supposer la virgule placée à un endicit quelconque du mot. Dans ce cas les circuits de calcul sont indépendents de l'endroit de la virgule. Pour un câlblage donné de l'unité de calcul, on pourra considérer que la virgule peut être à un endroit ou à un autre; mais une fois fixée, toute la suite du programme devra se dérouler en respectant la même convention.

#### 4.2. Représentation en virgule flottante:

Pour éviter les difficultés de cadrage des informations et également pour accroître la capacité des régistres, certains calculateurs sont équipés d'unité arithmétique fonctionnant en virgulæ flottante. Le principe consiste à séparer en deux termes différents l'ordre de grandeur et les chiffres significatifs d'un nombre, ce qui aboutit à une représentation par mantisse et exposant.

Une grandeur A s'écrit sous la forme :  $A = M \times b^{E}$

La mantisse M est toujours normalisée dans un intervalle donné, délimité par deux valeurs extrêmes  $M_0$  et  $M_1$  telles que  $M_0/M_1$  = b . En pratique, il est commode de choisir b égal à une puissance entière de la base de numération dans laquelle M est exprimée.

En décimal :

$$A = M \times 10^{E}$$

avec  $0.1 \le M \le 1$  exp:  $272 = 0.272 \times 10^{3}$

En binaire pur :  $A = M \times 2^{E}$  avec  $0.5 \le M \le 1$  exp:  $12 = 0.11 \times 2^{100} = 0.75 \times 2^{4}$

En binaire pur :

$$A = M \times 2^{E}$$

avec  $0.5 \le M \le 1$

exp:  $12 = 0.11 \times 2^{100} = 0.75 \times 2^{4}$

La représentation est dite ' normalisée ' lorsque la valeur de l'exposant E a été ajustée de façon que la mantisse M soit comprise dans l'intervalle de variations qui lui a été assigné.

#### 5.Représentation des nombres algébriques:

Il existe plusieurs systèmes de représentation des nombres algébriques ayant chacun leurs avantages spécifiques.

#### 5.1.Représentation en valeur absolue et signe:

Elle consiste à associer à la représentation des valeurs absolues, un élément binaire égal à O pour les nombres positifs et à 1 pour les nembres né— -gatifs.

Exp:

$$(+10)_{10} = (01010)$$

$(-4)_{10} = (10100)$

Commo en algèbre ordanaire, on effectue les opérations sur les modules et les signes sont traités àséparément.

Considérans un nombre supérieur à un, possédant m bits pour la partie fractionnaire et (n—1)bits pour la partie entière,le signe étant affecté à la position n.Le nombre s'écrit sous la forme :

$$2^{n} \cdot 2^{n-1} 2^{n-2} \dots 2^{0} \cdot 2^{-1} 2^{-2} \dots 2^{-m}$$

$X_{n} \quad X_{n-1} X_{n-2} \dots X_{0} \cdot X_{-1} X_{-2} \dots X_{-m}$

La valeur algébrique du nombre X s'obtient par la formule :

$$X = (-1)X_{n} = \begin{pmatrix} x_{k-m} \\ x_{k-m} \end{pmatrix} = \begin{pmatrix} x_{k-m} \\ x_{k-m} \end{pmatrix} = \begin{pmatrix} x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \end{pmatrix} = \begin{pmatrix} x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \end{pmatrix} = \begin{pmatrix} x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \end{pmatrix} = \begin{pmatrix} x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \end{pmatrix} = \begin{pmatrix} x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \\ x_{k-m} \end{pmatrix} = \begin{pmatrix} x_{k-m} \\ x_{k-m}$$

#### 5.2.Représentation des nombresnégatifs par le complément vrai :

Le principe consiste à changer les 0 par les 1 et les 1 par les 0 et à ajouter un 1 au plus faible poids;

Exp:

$$X = -7 = 10111$$

$CV = 01000 + 1 = 01001$

La somme du nombre et de son complément vrai donne un nombre formé uni--quement de O.En effet, si n set le nombre d'éléments binaires traités dans le système, cette somme donne (O) et un 1 à la position (n+1) qui n'existe pas.

$CV + X = 2^4.6$ 'est pour cette raison qu'on denne au complément vrai le nom de complément à  $2^n$ .

#### 5.3. Représentation par le complément restreint:

Le complément restreint ou complément à 1 s'obtient en changeant tous les 6 par les 1 et tous les 1 par les 0.

Exp: 100101 CR = 011010

Le complément à 1 est égal au complément à 2 moins 1.

Avec ces deux dernières représentations, on peut réduire la soustraction à une addition du complément .

6.Codage:

Pour représenter les nombres décimaux, on utilise le code binaire purteutefois, ce code a l'inconvevient d'entrainer l'écriture de très longues suites de bits 0 ou 1 pour les nombres importants. On a donc très généralemnt recours aujourd'hui à un système mixte: le système décimal codé binaite (800) dans lequel chaque chiffre est représenté séparément par son équivalent binaire:

$$(57)_{10} = (101 111)(800)$$

En fait, le 8 et le 9 s'écrivent en binaire 1000 et 1001 et 4 positions binaires sont nécessaires dans le système BCD :  $(57)_{10}$ =( 0101 0111 )(BCD).

Cependant, les calculateurs doivent être capables de représenter et de traiter bien d'autres informations que des valeurs numériques. Ainsi utilise-t--on les codes 2 parmi 5, le code de Gray, le code biquinaire, etc.

Le choix de la combinaison de 0 et de 1 qui représentera une information donnée est en principe arbitraire. Il est toutefois nécessaire que les codes soient normalisés pour les différents organes d'un même calculateur, pour les différents calculateurs d'un même constructeur ou pour l'ensemble des cons-tructeurs.

#### CHAPITRE CIRCUITS LOGIQUES INTEGRES

#### 1.Circuits logiques:

On appulle circuits logiques, des circuits qui permettent d'accomplir certaines opérations relevant de l'algèbre de Boole qui est liée étroitement à l'arithmétique binaire. On distingue deux types de circuits logiques: les circuits logiques combinatoires et les circuits logiques séquentiels.

#### 1.1.Circuits logiques combinatoires:

Ce sont des circuits dont les commandes antérieures qui ont été appli--quées sur les bornes d'entrée sont sans influence sur le résultat observé, à l'instant considéré, sur les bornes de sortie.

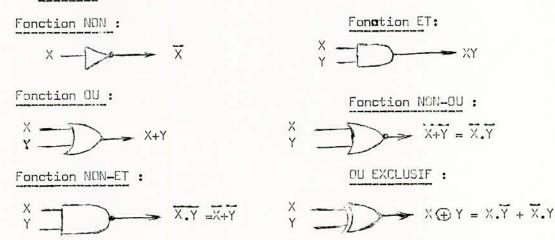

Ces circuits comportent :

- des circuits élémentaires:NON,OU,ET (NOT,OR,AND)

- des circuits du 1 er degré: NON-DU.NON-ET (NOR, NAND)

- et des circuits complexes : OU EXCLUSIF, ET-OU-NON, Circuits d'addition et de retenue.

Tableau de vérité:

| Х | Y | X NON | NON<br>Y | ET | OU<br>X+Y | NON-OU<br>X+Y | NON-ET<br>XY | OU-EKCLUSIF |

|---|---|-------|----------|----|-----------|---------------|--------------|-------------|

| 0 | 0 | 1     | 1        | 0  | 0         | 1             | 1            | D           |

| 0 | 1 | 1     | 0        | 0  | 1         | 0             | 1            | 1           |

| 1 | 0 | 0     | 1        | 0  | 1         | 0             | 1            | 1           |

| 1 | 1 | 0     | 0        | 1  | 1         | 0             | 0            | 0           |

#### Symboles:

#### 1.2.Circuits logiques séquentiels:

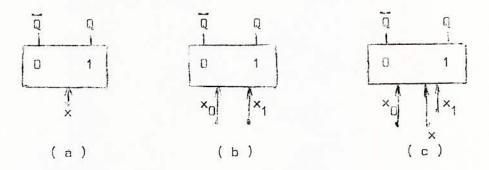

Ces circuits délivrent des niveaux de sortie qui dépendent des commandes qui avaient été appliquées à l'entrée, antérieurement à l'instant considéré. Ils possèdent la qualité de mémorisation des étâts antérieurs. L'élément de base en est la BASCULE. Celle-ci possède deux états stables et est susceptible de changer d'état sous l'effet de signaux de commande appropriés. Les signaux de commande sont généralement des impulsions délivrées par une HORLOGE.

Chaque bascule possède 2 sorties complémentaires Q et Q et une, deux ou trois entrées. Pour la bascule à une entrée ou bascule à commande symétrique(a) l'impulsion x commande le changement d'état quelque soit l'état initial. Pour la bascule à deux entrées(b), l'impulsion x provoque le passage dans l'état 1 si la bascule se trouvait initialement dans l'état 0 et est sans effet si elle se trouvait dans l'état 1. L'impulsion x commande de même l'état 0. Enfin ces deu deux modes de commande sont combinés dans la bascule à trois entrées(c).

L'association de plusieurs bascules de même type forme un REGISTRE.

Celui-ci est capable de mémoriser un mot. Suivant la nature du couplage entre

ces bascules et suivant leurs entrées et sorties, on aura des registres compteurs,

des régistres de décalage ou des régistres arithmétiques: Additionneur-Soustrac

-teur, accumulateurs.

#### 2. Classification des circuits logiques intégrés:

Deux grandes classes peuvent être dégagées :

- les circuits fonctionnant en saturation

- et les circuits fonctionnant hors saturation.

Pour les circuits fonctionnant hors saturation, la commutation des élé-ments se fait entres deux points situés dans la zone d'amplification ou entre

le point de blocage et un point situé dans la zone d'amplification. Les circuits

réalisés sont très rapides du fait de la réduction du temps de blocage et de

la non saturation des transistors.

Parmi les circuits fonctionnant en saturation, on peut distinguer :

- les circuits où la fonction logique est assurée par des résistances,

- ceux où elle est assurée par des transistors,

- et ceux où elle est assurée par des diodes.

#### 2.1.Circuits DCTL(Direct Coupled Transistor Logic):

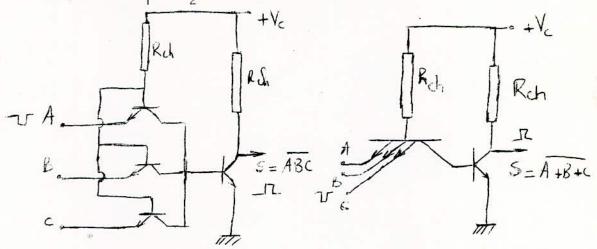

Ces circuits comportent uniquement des transistors et des résistances de charge Suivant le couplage des transistors, on réalise soit la fonction NOR

soit 10 function NAND.

$$S = ABC$$

#### 2.2.Circuits RTL(Resistor Transistor Logic):

Les circuits RTL sont moins sensibles aux variations des courants de base des transistors que les circuits DCTL.Les grandes amplitudes possibles des impultions de commutation donne une grande immunité aux bruits.L'inconvé—nient des circuits RTL,c'est que les résistances de base augmentent les temps de commutation.

#### 2.3.Circuits RCTL(resistor Capacitor Transistor Logic):

Pour diminuer les temps de commutation, on charge les bases des transistors par des montages accélérateurs RC.

Rch  $S = \overline{ABC}$   $S = \overline{A+B+C}$

Inconvenient:en hautes fréquences,les capacités représentant des court--circuits,laissent passer les composantes HF du bruit,ce qui rend les circuits RCTL sensibles aux bruits HF.

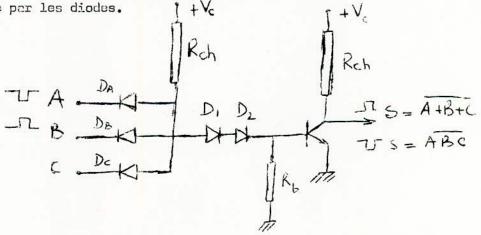

#### 2.4.Circuits DTL(Diode Transistor Logic):

Ils comportent des diodes et des transistors. La fonction logique est assurée par les diodes.  $1+V_c$   $1+V_c$

Les diodes  $D_{\Lambda}$ ,  $D_{B}$ et  $D_{C}$  réalisent la fonction ET en logique positive et la fonction BU en logique négative.Le transistor réalise la fonction de complémentation.Les circuits BTL présente une excellente immunité au bruit.

#### 2.5.Circuits TTL(Transistor Transistor Logic):

ce sont des circuits dérivés du DTL.Les diodes d'entrée  $D_A$ , $D_B$ et  $D_C$  sont remplacées par les diodes de jonctions émuttrices des transistors et les diodes de transposition  $D_A$  et  $D_C$  par la jonction collectrice.

Le circuit obtenu est très rapide du fait que le transistor à émetteur multiple est pratiquement toujours saturé; par conséquent, il n'introduit aucun retard de commutation.

#### Avantages:

- la construction des circuits logiques est simplifiée

- l'absence de la résistance de base R<sub>b</sub> permet d'augmenter la vitesse de commutation.

#### Inconvénients:

- -l'amplification d'un transistor à émetteur multiple donne la possibilité de naissance de l'effet " current robbing ", ce qui limite la valeur de l'en-trance.

- l'immunité au bruit est faible par rapport aux autres circuits.

#### Remarque:

Pour la réalisation de l'unité de calcul, on utilisera des circuits TTL.

CIRCUITS DE

CALCULS

#### CHAPITRE 1 . ADDITIONNEUR-SOUSTRACTEUR BINAIRE

Dans toute machine numérique, les quatre opérations arithmétiques fonda-mentales que sont l'addition, la soustraction, la m:ltiplication et la division

peuvent être réalisées à partie d'une seule:l'addition. En effet, la soustraction

peut être ramenée à l'addition du complément (vrai ou restreint); la multiplica-tion n'est qu'une suite d'addition. Quant à la division, ce n'est qu'une répéti-tion de soustractions donc d'additions. Il est plus simple, lorsqu'on parle de

circuits arithmétiques, de raisonner sur les additionneurs.

Comme notre étude concerne seulement les machines parallèles, nous allons détailler l'additionneur parallèle.

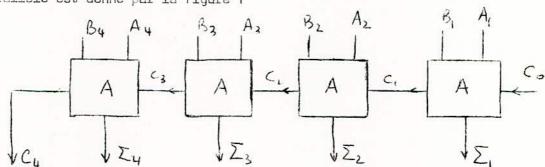

Dans un additionneur parallèle, tous les bits des deux nombres entrent simultanément et tous les bits de la somme sont formés simultanément. Ainsi, le nombre de cellules est égal au nombre de bits des deux nombres à additionner. Chaque cellule délivre un bit somme et un bit retenue qui se propage en cascade. Ce mode de fonctionnement est très rapide mais très coûteux au point de vue circuits. Pour des nombres de quatre bits, le schéma synoptique de l'additionneur parallèle est donné par la figure 1

Fig 1.Additionneur parallèle 4 bits.

Cette juxtaposition de quatre étages(cellules) suppose que les signaux de retenue issus d'un étage sont présentés à l'étage suivant.Donc, la rapidité de l'additionneur est limitée par le temps de propagation de la retenue.Nous examinerons le problème de la retenue au paragraphe 2.

#### 1. Additionneur binaire à retenue en cascade:

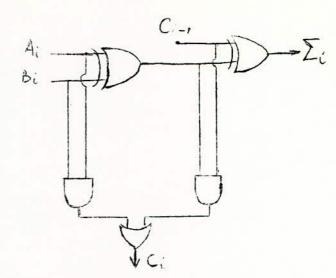

#### 1.1.Etude d'une cellule:

Un suppose qu'on désire effectuer la somme de deux bits A. et B i i d'ordre i et d'une retenue éventuelle  $C_{i-1}$  d'ordre immédiatement inférieur(i-1).

| A<br>i | Bi | C <sub>i</sub> | $ \sum_{i}$ | C <sub>i</sub> |

|--------|----|----------------|-------------|----------------|

| G      | 0  | 0              | 0           | 0              |

| 0      | 0  | 1              | 1           | 0              |

| 0      | 1  | 0              | 1           | 0              |

| U      | 1  | 1              | 0           | 1              |

| 1      | 0  | 0              | 1           | 0              |

| 1      | 0  | 1              | 0           | 1              |

| 1      | 1  | 0              | 0           | 1              |

| 1      | 1  | 1              | 1           | 1              |

Fig 2. Tableau de vérité et schéma logique d'une cellule. Le tableau de vérité nous donne :

$$\sum_{i} \overline{A}_{i} \overline{B}_{i} \overline{C}_{i-1} + \overline{A}_{i} \overline{B}_{i} \overline{C}_{i-1} + \overline{A}_{i} \overline{B}_{i} \overline{C}_{i-1} + \overline{A}_{i} \overline{B}_{i} \overline{C}_{i-1}$$

$$\sum_{i} \overline{A}_{i} \oplus \overline{A}_{i} \oplus \overline{A}_{i} \oplus \overline{A}_{i-1}$$

$$C_{i} \overline{A}_{i} \overline{B}_{i} + C_{i-1} \overline{A}_{i} \overline{\oplus B}_{i} = \overline{A}_{i} \overline{B}_{i} + \overline{A}_{i} \overline{C}_{i-1} + \overline{B}_{i} \overline{C}_{i-1}$$

$$\overline{C}_{i} = \overline{A}_{i}\overline{B}_{i}\overline{C}_{i-1} + \overline{A}_{i}\overline{B}_{i}\overline{C}_{i-1} + \overline{A}_{i}\overline{B}_{i}\overline{C}_{i-1} + \overline{A}_{i}\overline{B}_{i}\overline{C}_{i-1}$$

Multiplions les deux membres par (  $A_{i} + B_{i} + C_{i-1}$  ):  $C_{i}(A_{i} + B_{i} + C_{i-1}) = A_{i}B_{i}C_{i-1} + A_{i}B_{i}C_{i-1} + A_{i}B_{i}C_{i-1}$

Le bit somme peut s'écrire alors :

$$\sum_{i} = A_{i}\overline{C}_{i} + B_{i}\overline{C}_{i} + C_{i-1}\overline{C}_{i} + A_{i}B_{i}C_{i-1}$$

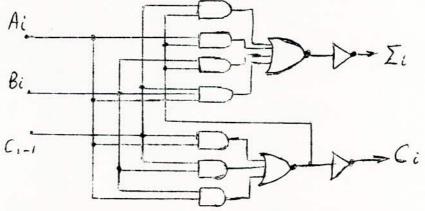

Le schéma logique d'une cellule délivrant le bit somme  $\sum_{i}$  et le bit retenue  $C_{i}$  est donné par la figure 3.

Fig 3. Schéma logique d'une cellule d'addition.

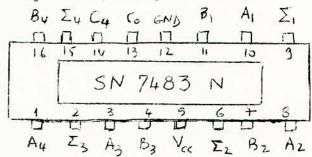

## ADDITIONNEUR BINAIRE 4 BITS 5N 7483 N B1 A1 Co A3 83 , Σ, Fig . 7

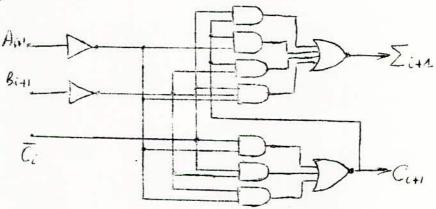

#### 1.2 Etude de la cellule immédiatement supérieure:

Normalement, la cellule immédiatement supérieure est identique à la première. On profite du fait que celle-ci peut fournir le bit retenue complémen-té. Si on complémente les deux bits  $A_{i+1}$  et  $B_{i+1}$  on aura :

$$C_{i+1} = \overline{A}_{i+1} \overline{B}_{i+1} + \overline{A}_{i+1} \overline{C}_{i} = + \overline{B}_{i+1} \overline{C}_{i}$$

$$C_{i+1} = \overline{A}_{i+1} \overline{B}_{i+1} + \overline{A}_{i+1} \overline{C}_{i} + \overline{B}_{i+1} \overline{C}_{i}$$

Le bit somme s'écrit :

$$\sum_{i+1} = \overline{A_{i+1}B_{i+1}C_i + A_{i+1}\overline{C}_{i+1} + B_{i+1}\overline{C}_{i+1} + C_i\overline{C}_{i+1}}$$

On n'aura pas à complémenter ni le bit retenue, ni le bit somme à la sortie des opérateurs NOR. Le schéma logique de la seconde cellule est donné par la figure 4.

Fig 4. Schéma logique de la seconde cellule.

L'association de ces deux cellules nous donne un additionneur à deux bits. Il est représenté par la figure 5.

Fig 5.Additionneur parallèle 2 bits.

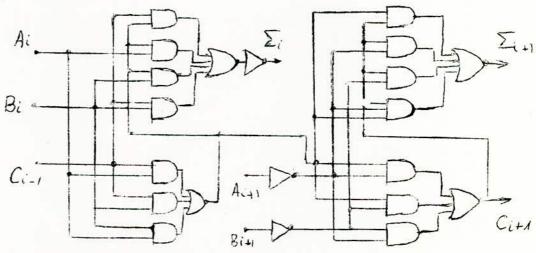

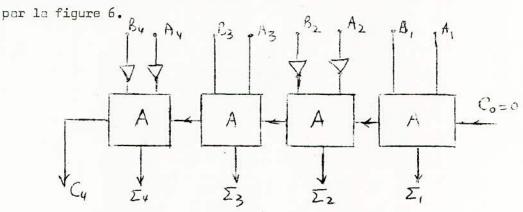

#### 1.3.Additionneur complet 4 bits :

Le schéma synoptique de l'additionneur parallèle 4 bits est donné

Fig 6.Additionneur parallèle 4 bits.

On aboutit ainsi au circuit intégré: SN 7483 N capable d'effectuer la somme de deux hombres à 4 bits.Le circuit est représenté par la figure 7.La figure 8 donne le brochage du SN 7483 N.

Fig 8.Brochage du circuit intégré SN 7483 N .

#### 2. Problème de la retenue: retenue anticipée:

On a vu qu'une cellule d'ordre i ne peut effectuer la somme de deux bits A et B d'ordre i que si la retenue délivrée par la cellule d'ordre(i-1)soit présente et que le temps d'attente soit égal au temps de propagation de cette retenue. Ainsi le temps d'addition est fonction du nombre de cellules placées en cascade et la retenue de l'addition se trouve réduite. Pour améliorer la vitesse de l'addition, on utilise la méthode de la retenue anticipée.

Le tableau de vérité de l'addition binaire donne : ( voir fig 2)

$$C_{i} = \bigwedge_{i} B_{i} + \bigwedge_{i} C_{i-1} + B_{i} C_{i-1}$$

ou

$$C_{i} = \bigwedge_{i} B_{i} + (\bigwedge_{i} + B_{i}) C_{i-1}$$

Il y a une retenue générée par la cellule i si :

1 er cas: les  $A_i$  et  $B_i$  valent 1 quelque soit la valeur de la retenue  $C_{i-1}$  2 ème cas:  $A_i$  (ou  $B_i$ ) et  $C_{i-1}$  valent 1 .

Le 1 er cas traduit le fait qu'au niveau de la cellule d'addition,il y a une élaboration d'une retenue quand  $A_i$  et  $B_i$  ont la valeur 1;on dit qu'il y a génération d'une retenue propre à la cellule. Ainsi  $A_iB_i$  est appelé terme de génération.

Le  $2^{\text{ème}}$  cas fait intervenir la notion de propagation de la retenue à travers la cellule et fait intervenir la somme  $P_i = A_i + B_i$ , appelé terme de propagation. La retenue  $C_i$  peut s'écrire alors :

$$C_{i} = G_{i} + P_{i}C_{i-1}$$

On suppose qu'on a un additionneur à 4 cellules avec les termes de gé--nération et de propagation suivants :

1ère cellule: G<sub>0</sub> P<sub>0</sub>

2ème cellule: G<sub>1</sub> P<sub>1</sub>

3ème cellule: G<sub>2</sub> P<sub>2</sub>

4ème cellule: G<sub>3</sub> P<sub>3</sub>

Pour les différentes cellules, on peut écrire :

1ère cellule:

$$C_1 = G_0 + P_0C_0$$

2ème cellule:  $C_2 = G_1 + P_1C_1 = G_1 + P_1(G_0 + P_0C_0)$

3ème cellule:  $C_3 = G_3 + P_2C_2 = G_2 + P_2(G_1 + P_1(G_0 + P_0C_0))$

4ème cellule:  $C_4 = G_3 + P_3C_3 = G_4 + G_3 + G_4 + G_5 + G_5 + G_5 + G_6 + G_$

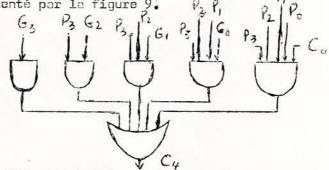

Cette expréssion montre qu'il est possible de remplacer un étage d'ad--dition à 4 bits à retenue en coscade (retenue qui doit se propager à travers 4 niveaux logiques) par un circuit qui ne requiert qu'un seul niveau logique. Ce circuit est représenté par la figure 9.

Fig 9. Représentation logique de  $C_4$  ( SN 74H ).

A l'aide de ce circuit de retenue anticipée, on a amélioré de 4 fois la vitesse d'addition, au prix d'une légère complexité du circuit.

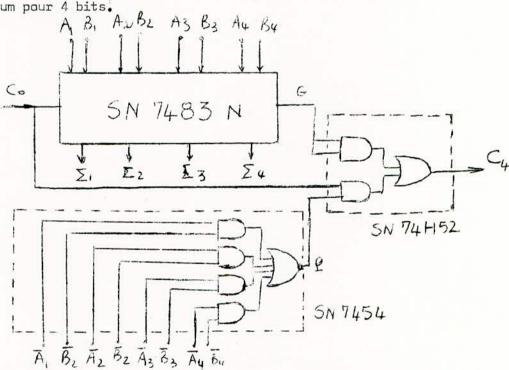

#### Additionneur 4 bits SN 7483 N à retenue anticipée:

Cet additionneur élabore une retenue C<sub>4</sub> soit à partir d'une retenue pro--pre à la cellule et apparaissant en sortie du SN 7483 N, soit à partir de la retenue présente à l'entrée ( et se propageant à travers l'étage ) grâce à la sortie P du circuit intégré SN 7454 N puisque :

$$P = A_{1}B_{1} + A_{2}B_{2} + A_{3}B_{3} + A_{4}B_{4} = (A_{1}+B_{1})(A_{2}+B_{2})(A_{3}+B_{3})(A_{4}+B_{4})$$

P traduit bien un terme de propagation

$$C_{4} = C_{4} + C_{6}P$$

Donc, la retenue C<sub>O</sub> au lieu de se propager à travers 4 cellules du l'ad-ditionneur SN 7483 N, transite par un seul niveau lequel a été choisi dans la série T.T.L rapide (SN 74H52 N) pour réduire le temps de propagation à 10 ns au maximum pour 4 bits.

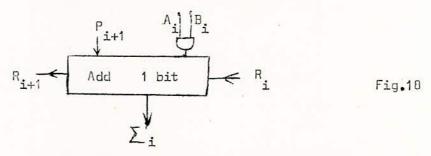

Fig 10.Additionneur 4 bits SN 7483 N avec circuit extérieur de retenue anticipée.

#### 3. Soustracteur binaire:

Par soustracteur, on entend un dispositif effectuent la différence de 2 bits  $A_i$  et  $B_i$  d'ordre i et d'une retenue  $C_{i-1}$  d'ordre (i-1) immédiatement inférieur. Le tableau de vérité de la figure 11 donne:

$$\sum_{i} = \overline{A}_{i} \overline{B}_{i} \overline{C}_{i-1} + A_{i} \overline{B}_{i} \overline{C}_{i-1} + \overline{A}_{i} \overline{B}_{i} C_{i-1} + A_{i} B_{i} C_{i-1}$$

$$\sum_{i} = A_{i} + B_{i} + C_{i-1}$$

| Ai | Bi | C <sub>i-1</sub> | $ \Sigma_{i} $ | Cį   | Ci-1                   |

|----|----|------------------|----------------|------|------------------------|

| 0  | 0  | 0                | 0              | 0    | A. The Desire          |

| D  | 0  | 1                | 1              | 1    | 1 Bi - + 1 1 1 1 1 1 1 |

| 0  | 1  | 0                | 1              | 1    | 1                      |

| 0  | 1  | 1                | 0              | 1    | Y                      |

| 1  | 0  | 0                | 1              | Ci . |                        |

| 1  | 0  | 1                | .0             | 0    |                        |

| 1  | 1  | 0                | 0              | D    | 1                      |

| 1  | 1  | 1                | 1              | 1    | $\vee$                 |

Fig 11. Tableau de vérite et schéma logique d'un soustracteur.

Le bit retenue s'écrit :

$$C_{\mathbf{i}} = \overline{A_{\mathbf{i}}B_{\mathbf{i}}} + C_{\mathbf{i}-1}(\overline{A_{\mathbf{i}}+B_{\mathbf{i}}}) = \overline{A_{\mathbf{i}}B_{\mathbf{i}}} + (A_{\mathbf{i}}+B_{\mathbf{i}})C_{\mathbf{i}-1}$$

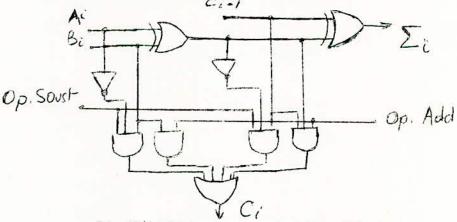

D'après les équations logiques, on remarque que la soustraction sans re-tenue  $\sum_{i}$  des 2 bits A et B est identique à la somme sans repport de ces

mêmes bits. La seule différence réside dans l'expression logique de la retenue  $C_{i}$ . De ce fait, on peut grouper les deux circuits logiques en un seul qui fait,

suivant une commande d'opération, soit une addition soit une soustraction. Le

schéma de l'additionneur-soustracteur est donné par la figure 12.

Fig 12 Additionnour-soustracteur binaire.

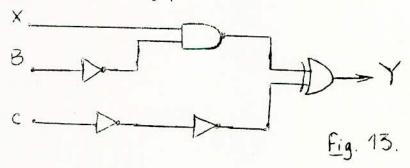

Etant donné que la soustraction peut être ramenée à une addition, on va essayer d'élaborer un circuit logique de complémentation. Pour cela, on impose deux entrées de contrôle B et C telles que :

$$B = 0 \begin{cases} C = 0 & \text{le bit est complémenté à 1} \\ C = 1 & \text{le bit n'est pas complémenté} \end{cases}$$

$$B = 1 \begin{cases} C = 0 & \text{le bit est égal à 1} \\ C = 1 & \text{le bit est égal à 0} \end{cases}$$

#### Tableau de vérité:

| В | С | X | Υ |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| С | 0 | 1 | O |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | G |

La fonction de complémentation s'écrit:

$$Y = \overline{B \cdot X \cdot C} + \overline{B \cdot C \cdot X} + B \cdot \overline{C \cdot X} + B \cdot \overline{C \cdot X}$$

$$Y = \overline{C \cdot X} + \overline{B \cdot C \cdot X} + B \cdot \overline{C \cdot X}$$

$$Y = \overline{C}(\overline{X} + X \cdot B) + \overline{B \cdot C \cdot X}$$

d'où:

$$Y = C(\overline{B}_{\bullet}X) + \overline{C}(\overline{B}_{\bullet}X)$$

$$Y = C + \overline{B}_{\bullet}X$$

On en déduit le schéma logique de la fonction Y :

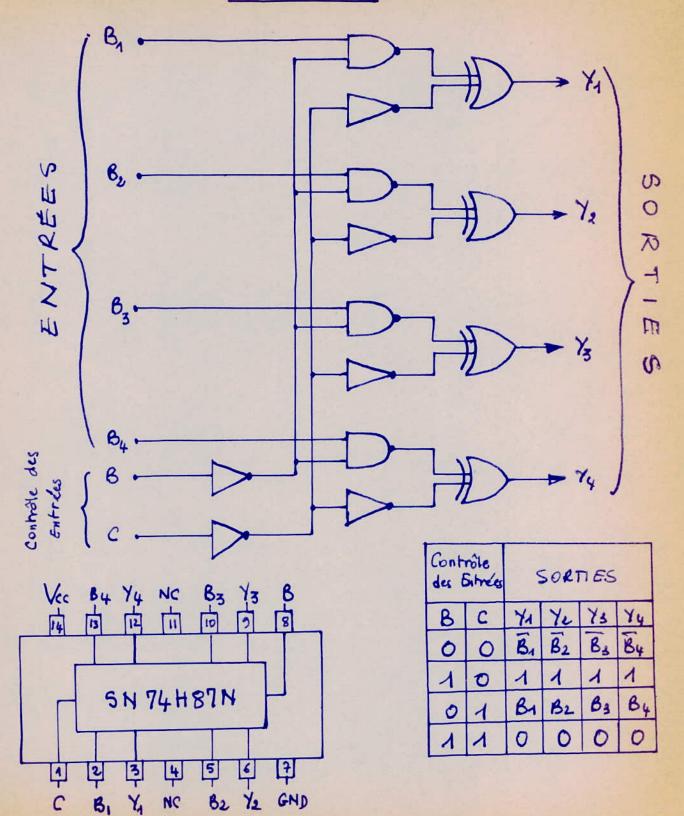

Pour des nombres de 4 bits, on aura 4 circuits logiques identiques au précédent. On aboutit ainsi au générateur de complément: le SN 74H87 N.Le cir-cuit complet est représenté par la figure 13.

Le circuit intégré SN 74H87 N donne le complément à 1 d'un nombre bi-naire à 4 bits. Pour avoir l'addition en complément à 2, il suffit d'ajouter

un 1 au résultat; ce qui revient à avoir une retenue initiale égale à 1 Le

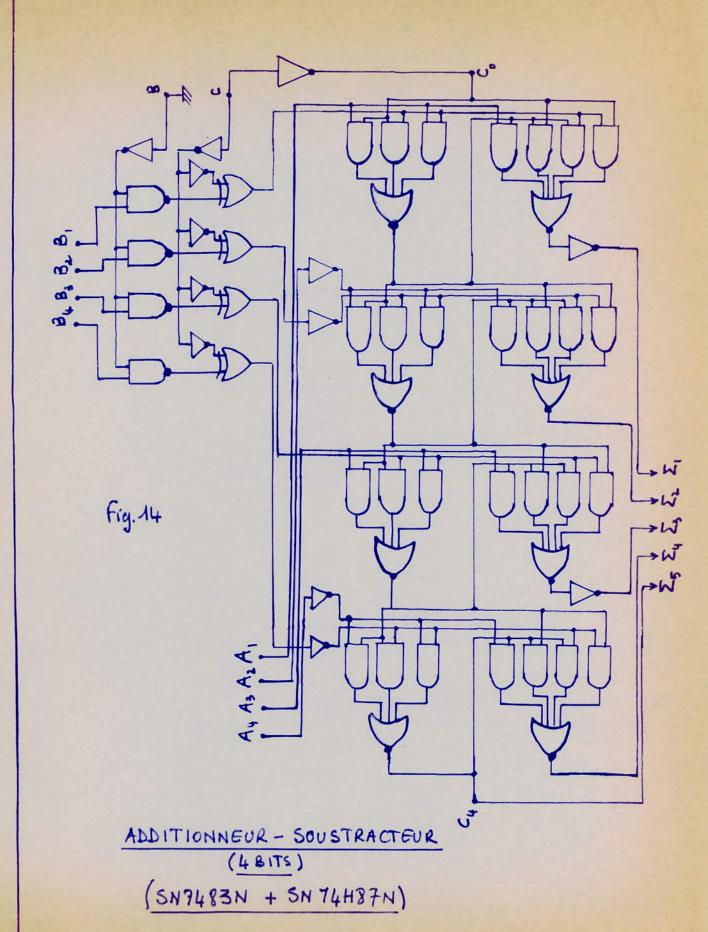

circuit logique complet de l'additionneur-soustracteur parallèle à 4 bits est

représenté par la figure 14 .

#### GENERATEUR DE COMPLEMENT SN 74 H 87 N

fig: 13

#### CHAPITRE 2 . MULTIPLIEUR BINAIRE

La présence ou l'absence d'un code opératoire pour la multiplication de nombres entiers marque une frontière entre les puissances des unités arithmétiques des ordinateurs. A partir des opérations d'additions, de décalage logique et de branchement conditionnel, on peut évidemment programmer la multiplication mais cela oblige à appeler plusieurs fois dans l'unité arithmétique une quantité inscrite en mémoire, ce qui allonge beaucoup le temps d'exécution.

La multiplication "cablée" peut se faire de plusieurs manières; par additions répétées, par additions et décalages de façon dite simultanée. Ce dernier

mode de multiplication vise avant tout la rapidité. Le produit se forme en très

peu de temps d'horloge au prix évidemment d'une complication des circuits.

#### 1.Multiplication par additions répétées:

En général, un additionneur complet est organisé pour recevoir trois élé-ments binaires(2 opérandes et la retenue issue de l'étage précédent) et pour

fournir deux éléments binares(la somme et la retenue). La propagation de cette re

retenue alloge considérablement l'addition. Pour éviter ce retard, on peut faire

l'addition en ne prenant les retenues en considération qu'au cycle suivant de

l'addition. On aura donc un régistre supplémentaire destiné à recevoir le mot

constitué par l'ensemble des retenues à transfér d'une addition à la suivante.

Mais le contenu du régistre supplémentaire ne doit être pris en considération

qu'après avoir été décalé d'un rang vers les poids les plus forts.

| I CIOA ODO DO I | 1011 ) <sub>2</sub> par ( 13 ) <sub>10</sub> = ( 1101 ) <sub>2</sub> 01001111 Rés   00100000 RR   001000000 RR   001000000 Décl.Gh 001000000 Décl.Gh 0010001111 Rés  0011111) <sub>2</sub> =1.7 + 1.2 + 1.2 + 1.2 + 1.2   0011111) <sub>2</sub> = 128 + 8 + 4 + 2 + 1 = (143) <sub>2</sub> |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### 2.Multiplication par addition et décalage:

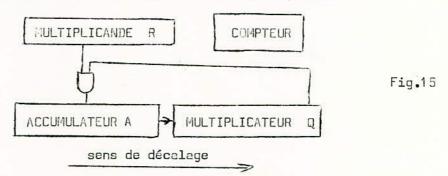

La multiplication de deux nombres de n bits donne un résultat de é2n bits. Il faut donc prévoir deux régistres pour contenir le résultat.L'unité de calcul utilise trois régistres pour la multiplication:

- Régistre R qui contient le multiplicande

- Régistre Q qui contient le multiplicateur

- Régistre accumulateur qui élabore chaque somme partielle.

Le schéma de principe est donné par la figure 15.

Le résultat de la multiplication apparaît dans l'ensemble des deux ré--gistres A et Q qu'on désigne par AQ.

Le fpnctionnemnt se fait en deux temps :

- Selon que le bit du plus faible poids du multiplicateur est 1 ou 0 , le multiplicande ou 0 est transmis et additionné au contenu de l'accumulateur. Pendant le transfert, A n'est pas effacé ou si cela est, réinscrit automatiquement.

- Le contenu de AQ est décalé d'un rang vers la droite.Le bit du plus faible poids du multiplicateur est perdu et le bit du plus faible poids du ré-sultat partiel s'écrit dans la position du plus fort poids (qui vient d'être libérée par le décalage à droite ) du régistre A.

L'opération se continue avec tous les bits du multiplicateur. Simultané-ment à ces opérations d'additions to de décalages, un compteur progresse d'une

unité après chaque décalage. L'opération se termine après n décalages, n étant

le nombre de bits du multiplicateur.

Exp: soit à multiplier :

$$A = (13)_{10} = (1101)_{2}$$

par  $B = \{11\}_{10} = (1011)_{2}$

$$A \times B = (10001111)_2 = (143)_{10}$$

#### 3.Multtiplieur cellulaire:

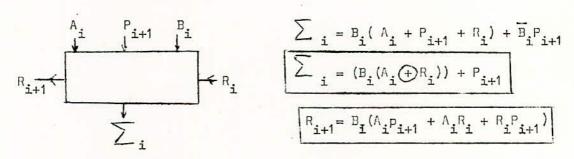

Etant donné que dans l'algorithme de la multiplication par addition et décalage tous les pas sont identiques(Add-Dcl), on effectue sur une ligne le produit (A.B.) et en ajoute à ce produit le résultat partiel précédemment dé-calé. Chaque cellule d'une ligne possède donc 4 entrées:  $^{\Lambda}_{i}$ ,  $^{B}_{i}$ ,  $^{R}_{i}$  et le bit re-tenue partiel décalé  $^{P}_{i+1}$ ; et 2 sorties: le bit somme et le bit retenue  $^{R}_{i+1}$ .

La cellule se présente comme suit:

Fig.16

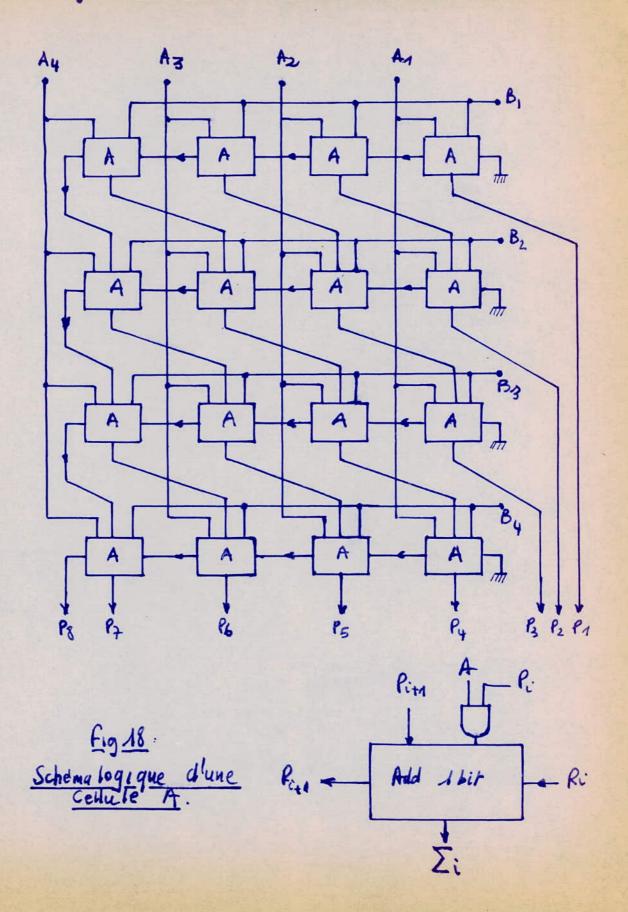

fy 17: Réseau cellulaire du Multiplieur 4 bits

# MULTIPLIEUR CELLULAIRE

La commande B peut se matérialiser par une porte ET. Etant donné que pour les cellules de la première ligne, les produits partiels et les retenues sont nuls, elles se réduisent simplement à des portes ET.

Or, si le bit B, du multiplicateur est égal à 1, la cellule fonctionne en étage d'additionneur d'un poids précisé. Si B = 0, la cellule transmet le bit du même poids du résultat partiel P d'ordre inférieur décalé. Le réseau cellulaire est donné par la figure 17.

La cellule peut se présenter comme suit:

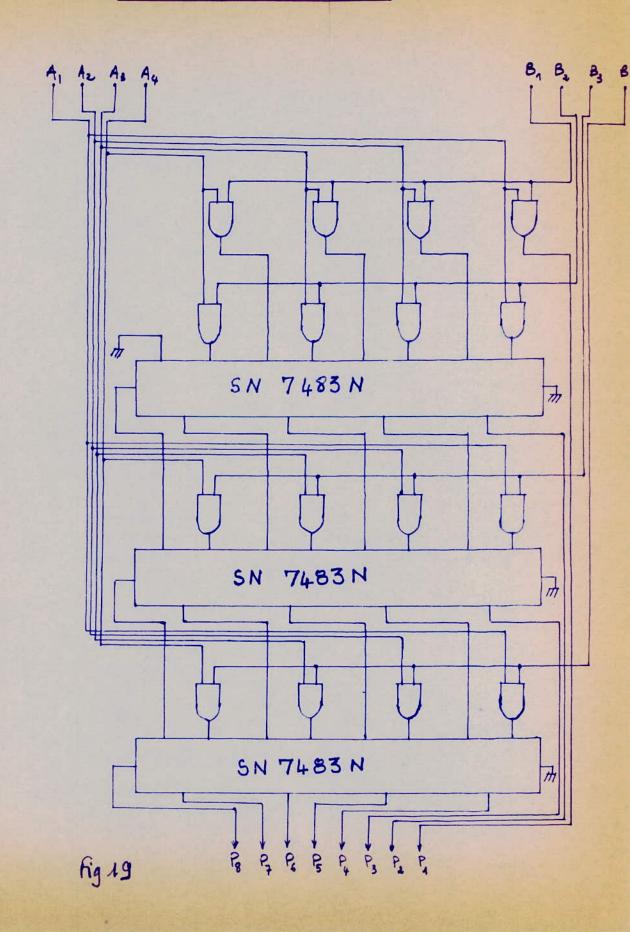

On peut grouper les 4 cellules d'addition 1 bit pour former l'addition--neur complet (4 bits):le SN 7483 N .Le schéma global du multiplieur cellulaire est donné par la figure 1 .

On remarque aussi qu'on peut grouper les 4 portes ET en un seul circuit intégré:le  $5N7408\ N$  .

#### 4. Autres móthodes:

De nombreuses méthodes sont mises en œuvre pour diminuer le temps d'exécution de la multiplication.

#### 4.1.Méthode de BOOTH :

Elle est applicable à des nombres représentés en valeur et signe.Les nombres négatifs sont représentés par leur complément à 2 et la multi-plication s'effectue en considérant le bit signe comme un bit ordinaire.

La machine examine successivement les poids du multiplicateur pris 2 à 2 en commençant par les plus faibles poids.Suivant les 4 possibilités:

00,01,10 et 11,elle effectue les opérations suivantes:

00 -> Décalage du produit d'un rang à droite

01 -> Add du multiplicande puis Décl d'un rang à droite du produit

10 - Sous " " " " " " "

11 - Décl du produit partiel d'un rang à droite.

#### 4.2. Hultiplication multidigitale:

Avec cette méthode, on peut faire la multiplication simultanée de plusieurs bits du multiplicateur par le multiplicande. Suivant que les deux derniers bits du multiplicateur sont : 00,01,01 et 11,1a machine effectuere les opérations suivantes:

- GO → Pas d'addition du multiplicande

- 01 -> Addition du multiplicande, Décalage à droite de deux rangs

- 10 -> Addition de 2 fois le multiplicande , décalage de deux rangs à droite.

- 11 Addition de 3 fois le multiplicande, décalage de deux rangs à droite.

Si l'on dispose au préalable dans deux régistres des valeurs doubles ou triples du multiplicande ,on diminue le nombre d'additions et on augmente la vitesse de la multiplication.

#### CHAPITRE 3 .DIVISEUR BINAIRE

Comme pour la multiplication, la division de deux nombres de n bits donne pour résultat un mot de 2n bits:le Quotient et le Reste.Il existe deux méthodes.

#### 1.Méthode par soustractions successives:

C'est l'opération inverse de la multiplication par addition répétées. Pour des nombres entiers, elle consiste à retrancher le diviseur du dividende jusqu'à celui-ci devient négatif ou nul.Le comptage du nombre d'opérations fournit le quotient.Le reste est ce qu'est devenu le dividende.

Cette méthode est simple mais très lente.

#### 2.Méthode par Add/Sous et décalage:

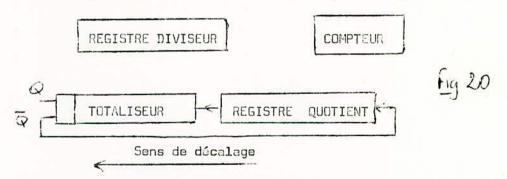

L'unité de calcul comporte trois régistres comme pour la multiplication:

- Régistre Diviseur D

- Régistre Quotient Q

- Régistre totaliseur qui contient le dividende T.

Le schéma synoptique du diviseur est donné par la figure 20.

On suppose que le diviseur et le dividende sont inférieurs à l'unité et que le diviseur est supérieur au dividende.

Lorsque la soustraction du diviseur au dividende est impossible, le bit quotient est égal à 0.Il faut donc diviser le diviseur par la base(2) et essayer à nouveau de soustraire.Or, la multiplication par 2 revient à un décalage vers la gauche.On décale alors l'ensemble Dividende-Quotient d'une position vers la gauche.Ce décalage libère la case la plus à droite du régistre quotient; ce qui permettra d'y inscrire le résultat de la soustraction suivante.La division s'arrête en comptant le nombres de bits établis 0 ou 1 du quotient, ce qui re-vient à compter les décalages opérés.Plutôt que d'effectuer un décalage vers

la gauche, ce décalage sera circulaire. Le bit de la position la plus à gauche du régistre T s'inscrit dans la position la plus à droite du régistre Q.De plus, lorsque la soustraction est impossible, le bit résultat est égal à 1 ( résultat négatif ) alors que le bit quotient doit être égal à O.Donc, on doit complémenter le bit de la position la plus à gauche du régistre T.Or, un élément du régistre ( ou Bascule ) possède une sortie directe et une sortie complémentée. Il suffit de relier la sortie complémentée à la position la plus à droite du régistre quotient.

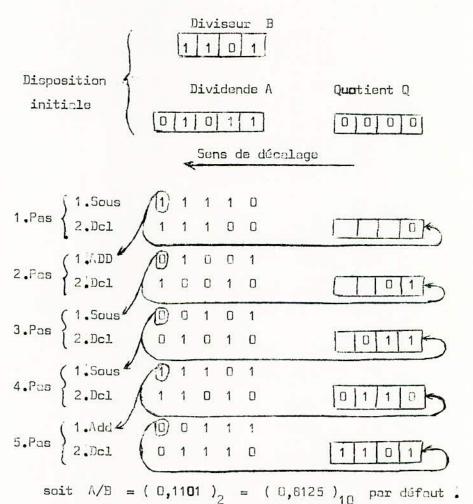

Exp: soit à diviser  $A = (0,1011)_2 = (0,6875)_{10}$  par  $B = (0,1101)_2 = (0,8125)_{10}$

On remarque que le 1 commande l'addition et le 0 commande la soustraction.

fig 22. Réseau Cellulaire du Diviseu binaire 4bib

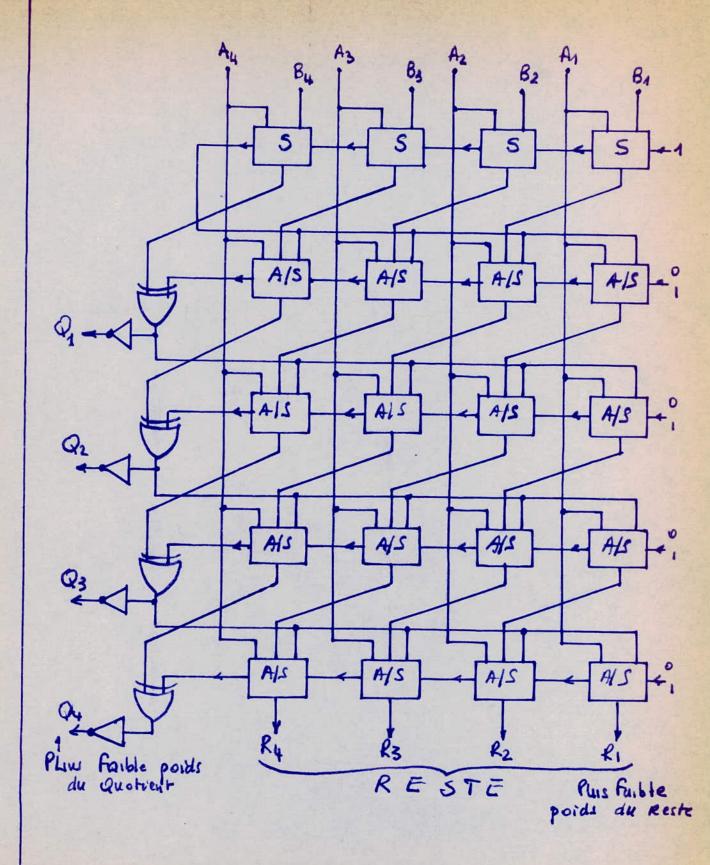

#### 3 .Diviseur cellulaire:

Etant donné que dans l'algorithme de la division par Add/Sous et décala-ge, tous les pas sont identiques, le réseau sera constitué de plusieurs cellules chacune d'elles pourra effectuer soit une addition soit une soustraction sui-vant que le reste partiel est négatif(1) ou positif(0). Le réeultat décalé vers les plus forts poids.

Or, on sait que le nbit de la soustraction est identique au bit de l'ad--dition.De plus, le bit  $\mathbb Q$  de la position la plus à gauche du régistre T comman--de soit une addition( $\mathbb Q=1$ ) soit une soustraction( $\mathbb Q=0$ ).

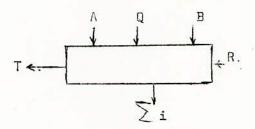

Une cellule peut se présenter comme suit :

Fig.21

Pour une addition, la retenue d'ordre supérieur R est égal à :

$$R_{i+1} = A_iB_i + A_iR_i + R_iB_i$$

Pour la soustraction  $R_{i+1}$  s'écrit :

$$R_{i+1} = \overline{A}B_{i} + \overline{A}R_{i} + RB_{i}$$

La cellule délivre donc une retenue T telle que :

$$T = Q(A.B + A.R + B.R) + Q(A.B + A.R + B.R)$$

addition ou soustraction

On remarque que les cellules de la première ligne n'effectuent qu'une soustraction.Le réseau cellulaire est représenté par la figure 22.

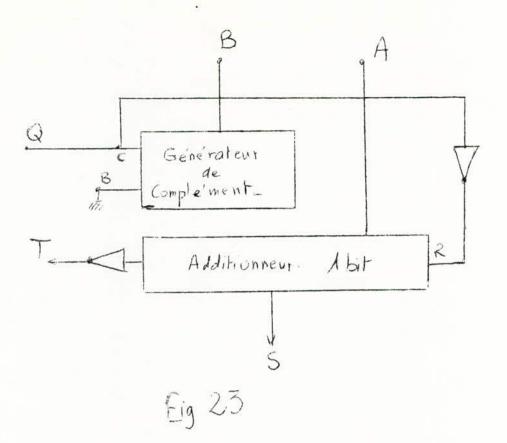

Pour satisfaire à ces conditions, on utilise le bloc Additio neur-Sous--tracteur dont l'entrée C est reliée à la sortie Q.Le schéma détaillé de la cellule est donné par la figure 23.

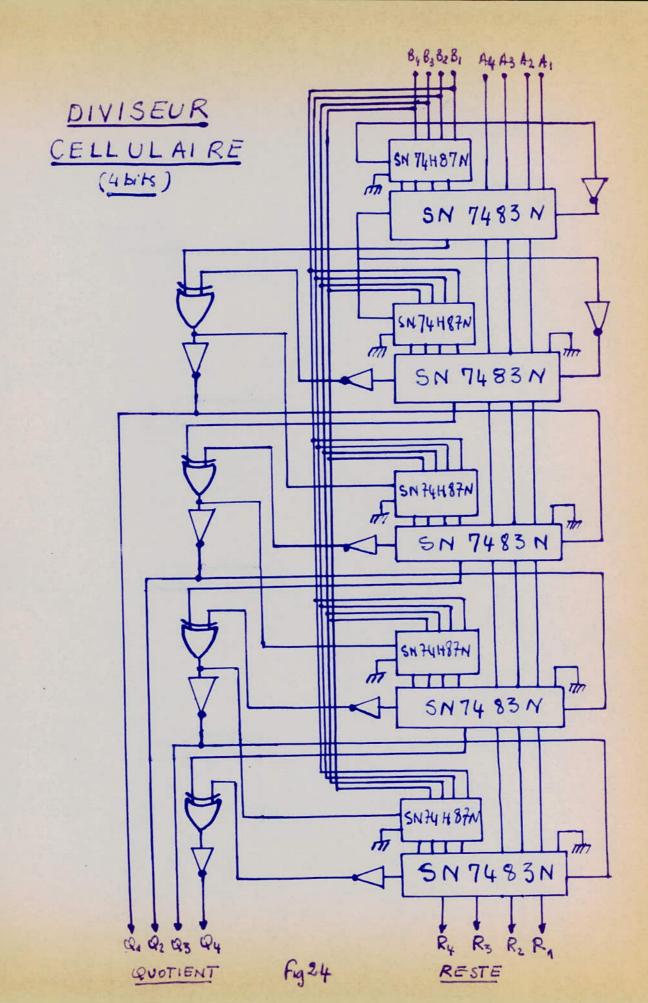

Le divideur cellulaire complet pour dos nombresde 4 bits est représenté par la figure 24.

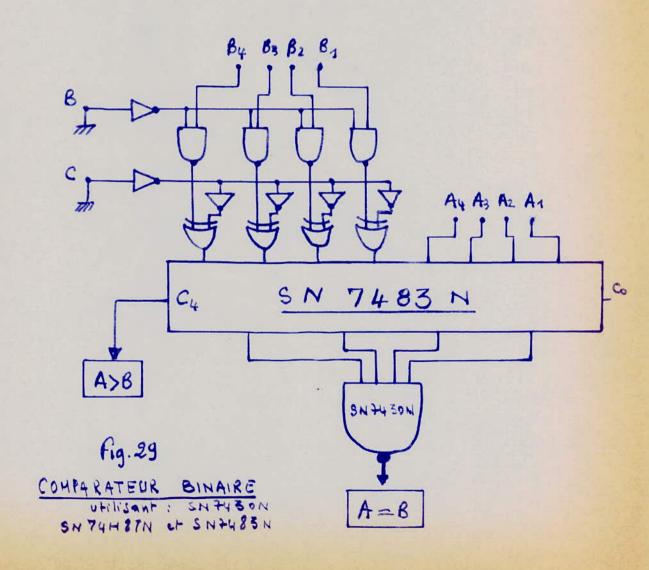

#### CHAPITRE 4. COMPARATEUR BINAIRE

Par comparateur, on entend un dispositif susceptible de comparer deux nombres binaires A et B entre eux.Il doit être capable de déterminer si A est inférieur, égal ou supérieur à B.On distingue deux types de comparateurs: le comparateur parallèle et le comparateur série.Dans le premier cas, il s'agit de comparer deux nombres qui restent figés dans deux régistres; dans le second cas, l'information contenue dans les deux régistres est décalée et les deux nombres sont comparés poids par poids.

Etant donné que notre calculateur numérique est du type parallèle, on étudiera simplement les comparateurs parallèles.

Les comparateurs parallèles sont conçus suivant deux méthodes:

# 1.1 ère méthode: utilibation des circuits de coîncidence:

#### 1.1.Circuit de coîcidence:

Ce circuit réalise la fonction inverse du circuit OU EXCLUSIF, c'est-à-dire qu'il délivre un 1 en sortie lorsque les deux entrées sont identiques.

#### Tableau de vérité:

| Α | В | A 🕀 B | ∧ <b>⊙</b> B |

|---|---|-------|--------------|

| 0 | 0 | 0     | 1            |

| 0 | 1 | 1     | 0            |

| 1 | 0 | 1     | 0            |

| 1 | 1 | 0     | 1            |

$$A \cdot \mathbf{P} B = A \cdot \mathbf{P} B = A \cdot B + A \cdot B =$$

$$= (A + B)(A + B)$$

Fig 25 Tableau de vérité du circuit de coîcidence

#### 1.2.Comparateur parallèle:

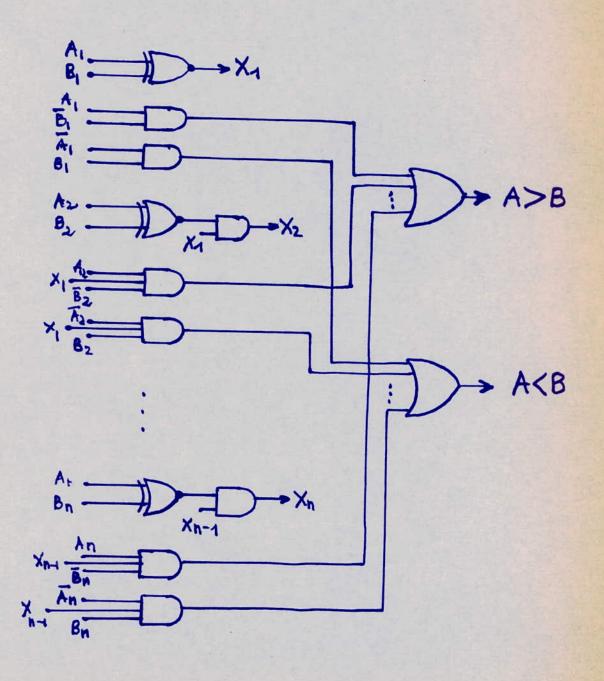

On concidère deux nombres bineires A A n n-1 ··· A 1 et B B n n-1 ··· B 2 1 · On réalise la coîcidence de tous les bits:

$$X_1 = A_1 \odot B_1$$

,  $X_2 = A_2 \odot B_2$ , ...,  $X_n = A_n \odot B_n$

La fonction logique de la sortie du comparateur s'écrit:

$$Z = X_{n-1}, X_{n-1}, \dots X_{1} = (A_{n-1}, B_{n-1}, A_{n-1}, A_{n$$

D'où:

$$Z = 1$$

si  $A = B$

# COMPARATEUR PARALLELE Utilsant les circuits de Coici dence.

fig 27.

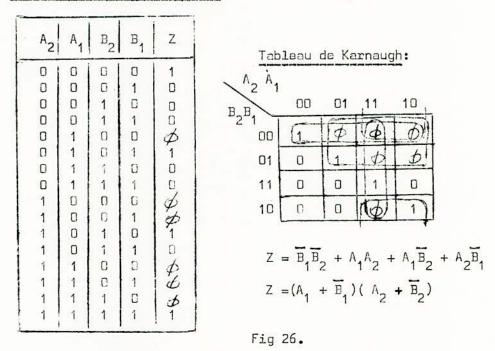

Pour établir le schéma logique du comparateur, on suppose que la sortie Z répond aux conditions suivantes;

$$Z=0$$

si A  $\Big<$  B,  $Z=1$  si A = B et  $Z=\phi$  si A  $\Big>$  B Tableau de vérité pour n = 2 :

Il est possible de généreriser pour des nombres d'ordre n :

$$Z = (\Lambda_1 + \overline{B}_1)(\Lambda_2 + \overline{B}_2) \cdot \cdot \cdot (\Lambda_n + \overline{B}_n)$$

Avec catte fonction, on vérific simplement que le nombre  $\Lambda$  est inférieur au nombre B.Dans le cas où l'on ne fait aucune hypothèse sur  $\Lambda$  et B, on compare alors successivement tous les poids des deux nombres en commençant par les poids les plus élevés à l'aide d'un circuit de coîcidence. Si les nombres sont identiques, tous les poids sont successivement examinés. S'ils sont différents, il existe une position où deux bits ne coîcident pas. Il n'est pas alors nécessaire de continuer la comparaison des plus faibles poids, mais de s'assurer lequel des deux bits est égal à 1. Si  $B_i = 1$  et  $A_i = 0$ , A > B; si  $A_i = 1$  et  $A_i = 0$  alors A < B. Le schéma du comparateur est donné par la figure 27. Pour des nombres binaires très grands, le circuit devient très complexe. Surtout on sera limité par l'entrance des portes.

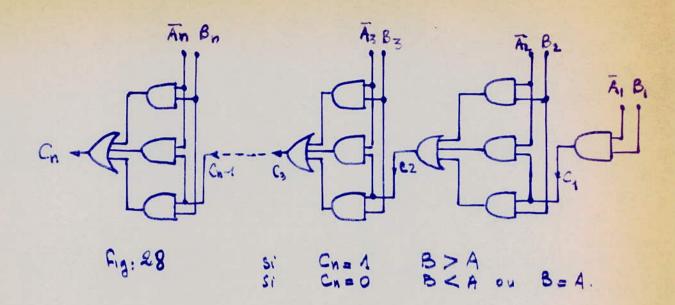

## 2. 2ème méthode:Comparaison par soustraction:

Elle consiste à soustraire un des deux opérandes et d'examiner l'existence éventuelle d'une retenue au delàsdu plus fort poids du module du résultet. On suppose qu'on dépire effectuer (A - B).

Donc, l'opération consiste à effectuer la différence sans se préoccuper du résultat; mais on tient compte simplement des retenues dans chaque étage.

On sait que, dans le cas d'une soustraction, le bit retenue s'écrit:

$$C_{i} = \overline{A}_{i}B_{i} \div \overline{A}_{i}C_{i-1} + B_{i}C_{i-1}$$

Le schéma du comparateur est donné par la figure 28.

Une autre méthode consiste à additionner au nombre A le complément à 1 du nombre B.Pour des nombres de 4 bits, on utilise l'additionneur 4SN 7483 N et le générateur de complément SN 74H87 N .

Si les deux nombres sont égaux, tous les bits'somme' i sont égaux à 1. En reliant tous ces bits à un opérateur NAND ( SN 7430 N ) à 4 entrées, le signal logique 0 apparaît sur la sortie de cet opérateur. Par contre, le niveau logique 1 apparaît sur la sortie  $\mathsf{C}_4$  de l'additionneur quand le nombre A est supérieur au nombre B.Le bloc ADDITIONEUR-SOUSTRACTEUR fonctionne en soustracteur; donc:  $\mathsf{C} = \mathsf{D}$  et  $\mathsf{B} = \mathsf{1}$ .

Le schéma logique du comparateur binaire est donné par la figure 29.

SYSTEME

DIE NTREE-SORTIE

3 ème PATTE

#### CHAPITRE 1 . ETUDE DES REGISTRES : SN 7475N

#### 1.Généralités sur les bascules:

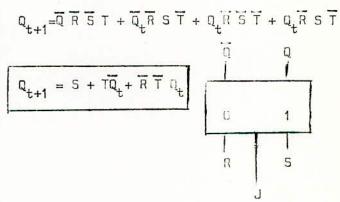

Dans l'unité de calqui,il est nécessaire de conserver en mémoire, pendant un certain temps, les données présentes à l'entrée d'un circuit. La réalisation de co ciacuit repose sur l'utilisation des bascules électroniques. En distingue plusieurs types de bascules suivant le nombre de ses entrées : RS,RST,DT,ou D, T,JKT ou JK.

#### 1.1.Bascule T :

Elle possède une entrée T et deux sorties Q et Q.Elle change d'état lorsqu'on applique un 1 sur son entrée quel que soit son état antérieux et conserve cet état indéfiniment. Elle ne change pas d'état lorsqu'on applique un D sur son entrée T .

Tableau de vérité :

$$Q_{t+1} = \overline{Q}_t T + Q_t \overline{T}$$

$$Q_{t+1} = Q_t + T$$

#### 1.2.Bascule JK:

Elle possède deux entrées J et K et deux sorties Q et Q.L'entrée J est destinée à la remise à 1 et la borne K à la remise à 0.

Tableau de vérité :

| Q <sub>t</sub> | J | K | Q <sub>t×+1</sub> |

|----------------|---|---|-------------------|

| 0 1            | 0 | 0 | 0                 |

| C              | 0 | 1 | 0                 |

| 0 0            | 1 | 0 | 1                 |

| 0              | 1 | 1 | 1                 |

| 1              | 0 | 0 | 1                 |

| 1              | 0 | 1 | 0                 |

| 1              | 1 | 0 | 1                 |

| 1              | 1 | 1 | 0                 |

$$Q_{t+1} = \overline{Q}_{t} \overline{JK} + \overline{Q}_{t} JK + Q_{t} \overline{JK} + Q_{t} \overline{JK}$$

$$Q_{t+1} = J \overline{Q}_{t} + \overline{K} Q_{t}$$

#### 1.3.Bascule RS:

C'est une bascule JK avec une condition interdite RS = G .

Ta bleau de vérité:

| Qt  | R | S | Q <sub>t+1</sub> |

|-----|---|---|------------------|

| 0   | 0 | 0 | 0                |

| 0 0 | 0 | 1 | 1                |

| 0   | 1 | 0 | 0                |

| 1   | 0 | D | 1                |

| 1   | 0 | 1 | 1                |

| 1   | 1 | 0 | 0                |

$$Q_{t} = \overline{Q_{t}} \overline{R} S + Q_{t} \overline{R} S + Q_{t} \overline{R} S \qquad Q \qquad Q$$

$$Q_{t+1} = S + \overline{R} Q_{t} \qquad D \qquad 1$$

$$R \qquad S$$

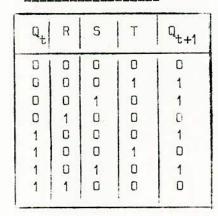

#### 1.4.Bascule RST:

C'est une bascule RS à laquelle on a ajouté une borne T.Lorsqu'on ap--plique un 1 en T, la bascule change d'état quel que soit son état an--térieur.Les conditions interdites sont :

$$RST = 0$$

$RS = 0$   $ST = 0$   $RT = 0$

Tableau de vérité:

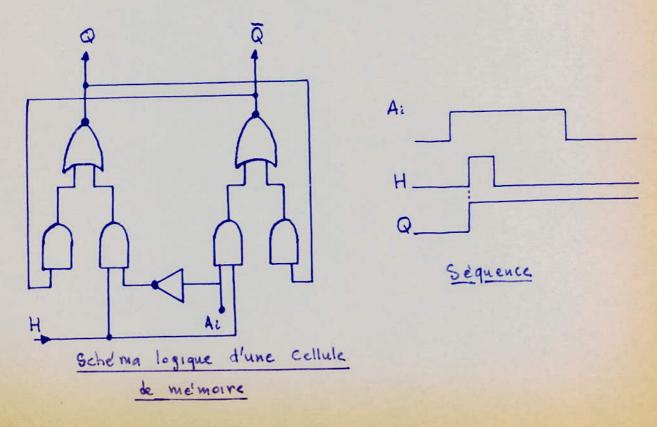

## 2. Etude d'une cellule de mémoire: bascule D:

Elle possède deux entrées D et H et deux sorties Q et Q.Le fonctionnement de la bascule est le suivant:

au repos,on a Q qui est égal à 1 ou à 0 et donc Q est égal à 1 ou 0. Le signal d'horloge H n'est pas appliqué(H=0). Si D=1 et H=0,il ne pas-se rien. Mais si on maintient D à 1 et qu'on envoie une impulsion po-sitive sur H, après cette impulsion on aura Q=1 et Q=0 quel que soit l'état de Q avant l'impulsion. Après l'impulsion, on peut changer la valeur de D,il ne se passe rien. Mais si on maintient D à 0 et qu'on envoie une impulsion sur H, après l'impulsion on aura Q=0 et Q=1.

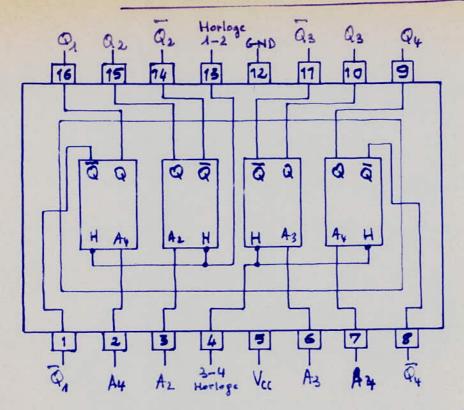

# MEMOIRE 4 BITS = SN 7475N

tableau de Ve'nile

| tn | t <sub>n+1</sub> |

|----|------------------|

| Ai | Q                |

| 1  | 1                |

| 0  | 0                |

fig 35: Brochage du SN7475N. Schema logique d'une cellule de mémoire et sa sequence.

Si on recommence l'opération en laissant D à D, D restera à U car il y était déjà.On aura donc, après l'impulsion d'horloge, sur la borne D ce que l'on avait sur D avant l'impulsion.

Le changement d'état de D en dehors des impulsions d'horloge n'a aucune importance; la valeur de Q avant l'impulsion d'horloge n'influe pas sur le ré-sultat final. Ainsi, tant que l'horloge est au niveau haut, l'information sur l'entrée D ne peut être modifiée.

L'information présente sur l'entrée D est enregistrée au moment du front de montée de l'impulsion d'horloge et cette information doît être maintenue pendant tout le temps où l'horloge reste au niveau logique 1.

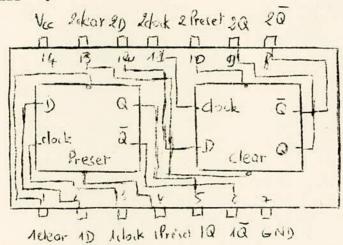

Le schéma logique de la cellule de mémoire est donné par la figure 35. Le circuit intégré SN 7474 N comprend deux cellules de mémoire.Il est capable de mémoriser un mot de deux bits.Le schéma du SN 7474 N est représenté par la figure 36.

Tableau de vérité

| tn | t<br>n+1 |   |

|----|----------|---|

| D  | Q        | Q |

| 0  | 0        | 1 |

| 1  | 1        | 0 |

Fig 36 . Circuit intégré SN 7474 N

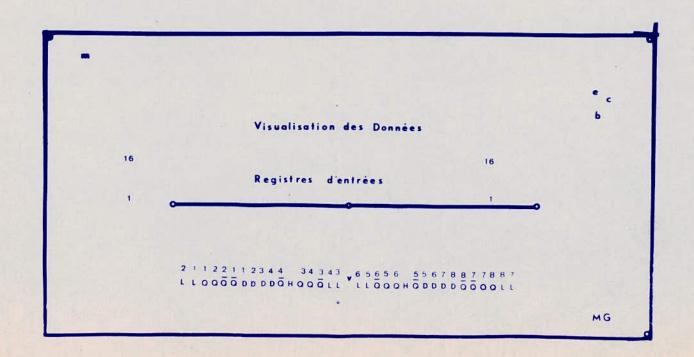

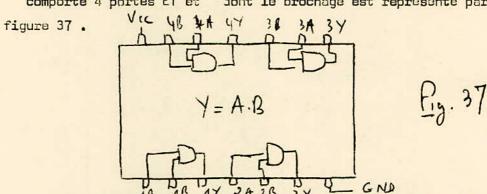

Etant donné que notre unité de calcul opère sur des mots de 4 bits, on utilise alors le circuit intégré SN 7475 N .Ce circuit comprend 4 bascules reliées deux à deux.Chaque couple est commandé par le même signal d'horloge. Le schéma logique du SN 7475 N est donné par la figure 35 .

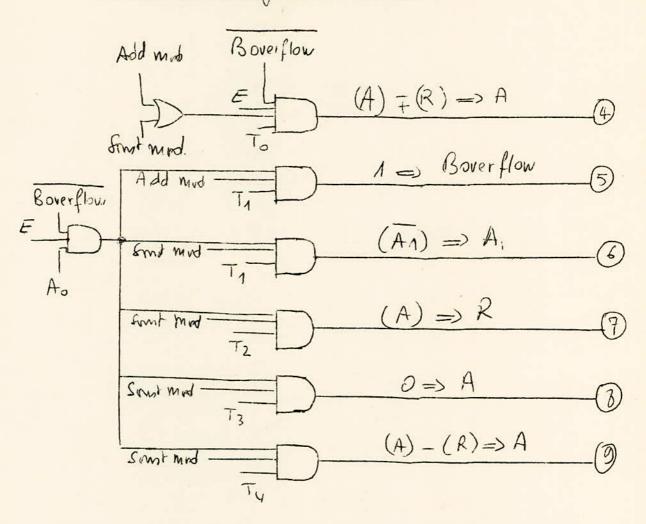

#### CHAPITRE 2:CIRCUITS DE COMMANDE DE SORTIE DES OPERATIONS

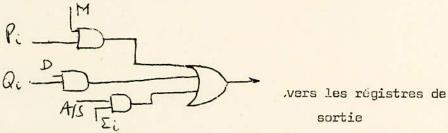

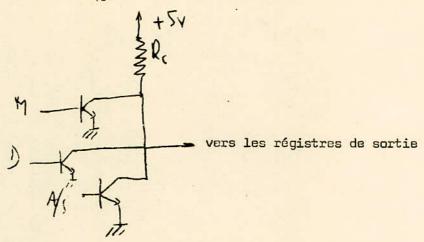

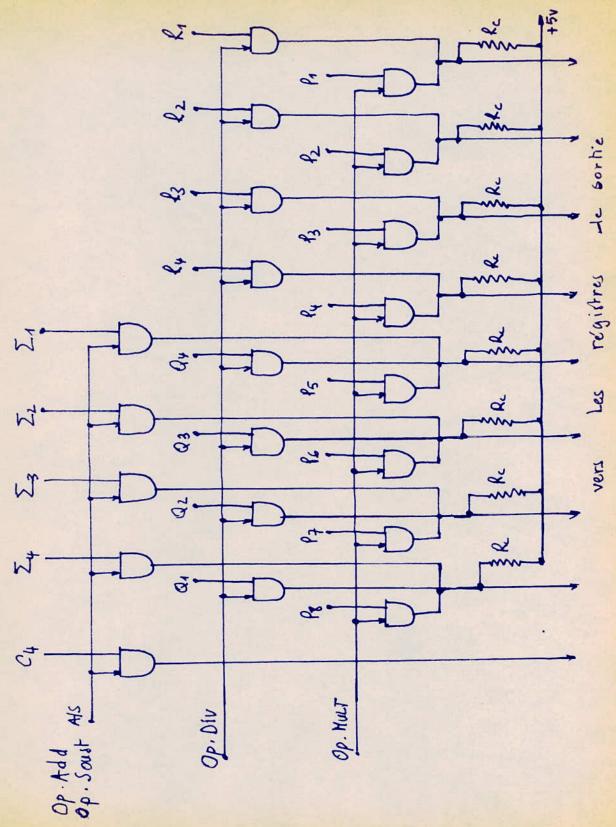

Ces circuits permettent de transférer le résultat de l'opération des circuits de calcul vers les régistres de sortie Ce transfert s'effectue sui-vant une commande d'opération. Il peut se patérialiser par des portes ET.

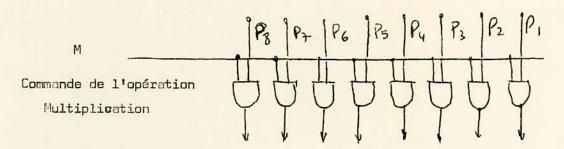

Pour la multiplication, on utilise 8 portes ET. Une commande de multipli-cation ouvre les 8 portes et le résultat est transmis aux régistres de sor-tie.

vers les régistres de sortie

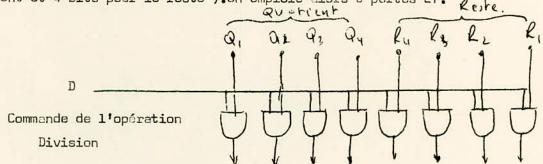

On sait que la division donne un résultat de 8 bits (4 bits pour le quotient et 4 bits pour le reste ).On emploie alors 8 portes ET. Reste.

vers les régistres de sortie

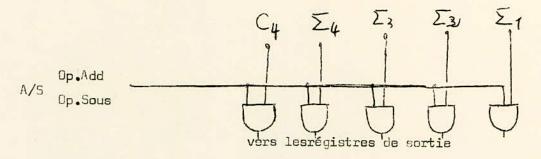

L'addition ou la soustraction donne un résultat de 5 bits au maximum. Pour l'addition, le résultat apparaît en clair . Mais pour la soustraction , il faut complémenter la retenue d'ordre supérieur  $\mathbf{C}_4$  . Ceci provient du fait qu'on a réduit la soustraction à une addition de complément à 2.0n utilise 5 portes ET .

Pour effectuer une addition ou une soustraction, on doit agir sur deux commandes :

- une commande A/S permettent d'ouvrir les 5 portes ET ,

- et la commande C de l'étage Additionneur Soustracteur.

( C=0 Op. Sous , C=1 Op. Add )

Suivant la nature de l'opération, les registres de sortie emmagasinent le résultat de l'opération désirée. On peut réunir les bits de même poids à l'aide d'une porte OU à 3 entrées au maximum.

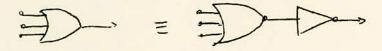

Etant donné qu'on n'a pas commandé des portes OU, on peut réaliser une porte OU : NOR suivie d'un inverseur:

à l'aide d'une porte

Cette méthode utilise beaucoup de portes et complique la circuiterie. Pour réduire au munimum le nombre de po $\epsilon$ tes utilisées ,on utilise une méthode moderne celle du OU CABLE .

Si l'on regarde, la constitution d'une porte ET du circuit intégré SN 7409 N, on constata que le collecteur du transistor de sortie est à l'état ouvert. On recueille sur le collecteur le bit résultat d'une opération quelconque. En reliant les collecteurs de sortie entre-eux à travers une résistance de charge, on réalise le OU CABLE.

Pour les opérations, on utilise le circuit intégré SN 7409 N qui comporte 4 portes ET et dont le brochage est représenté par la

Le schéma logique de la partie commande de sortie des opérations est donné par la figure 38.

fig 38

CODSTRUCTION DE

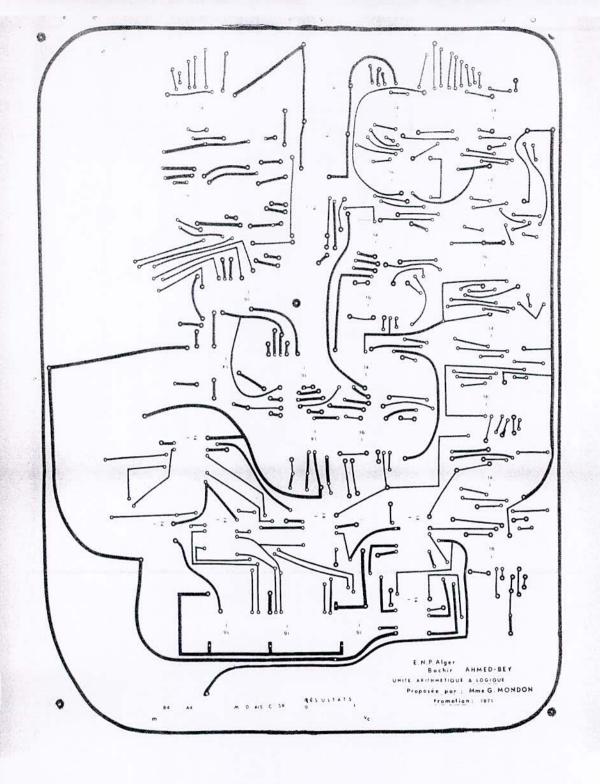

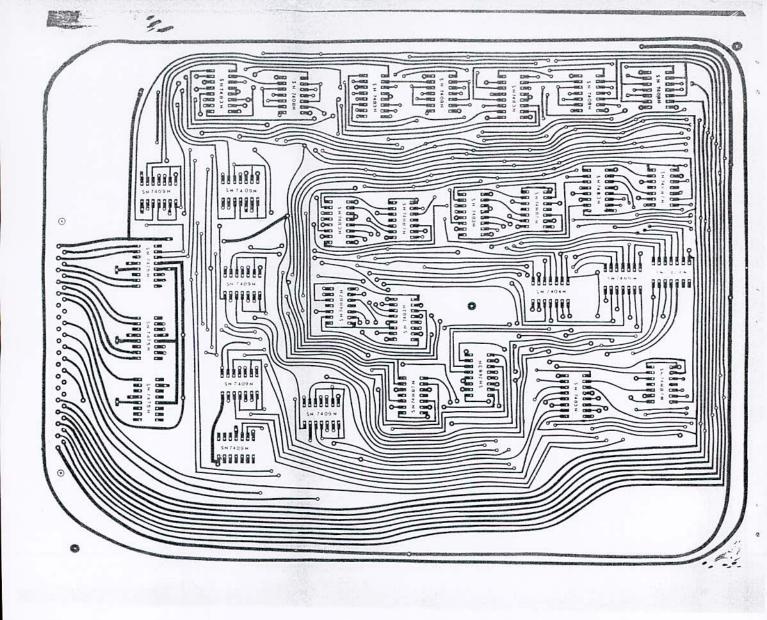

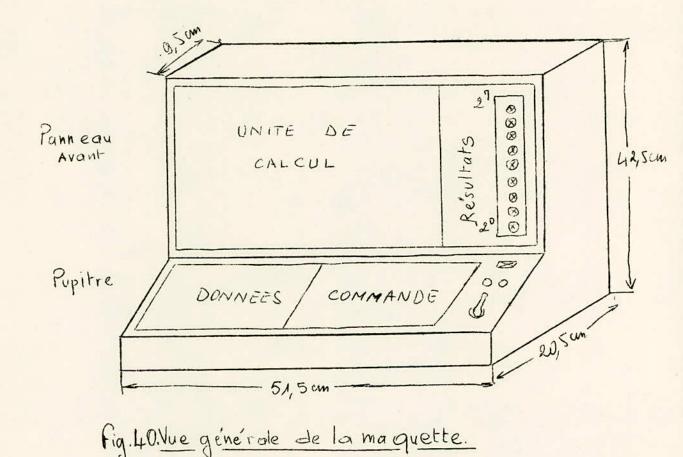

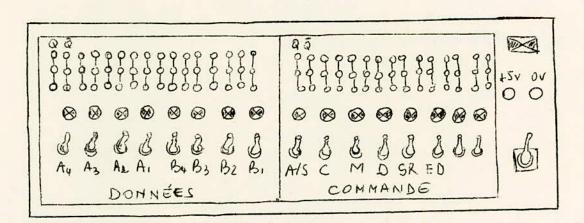

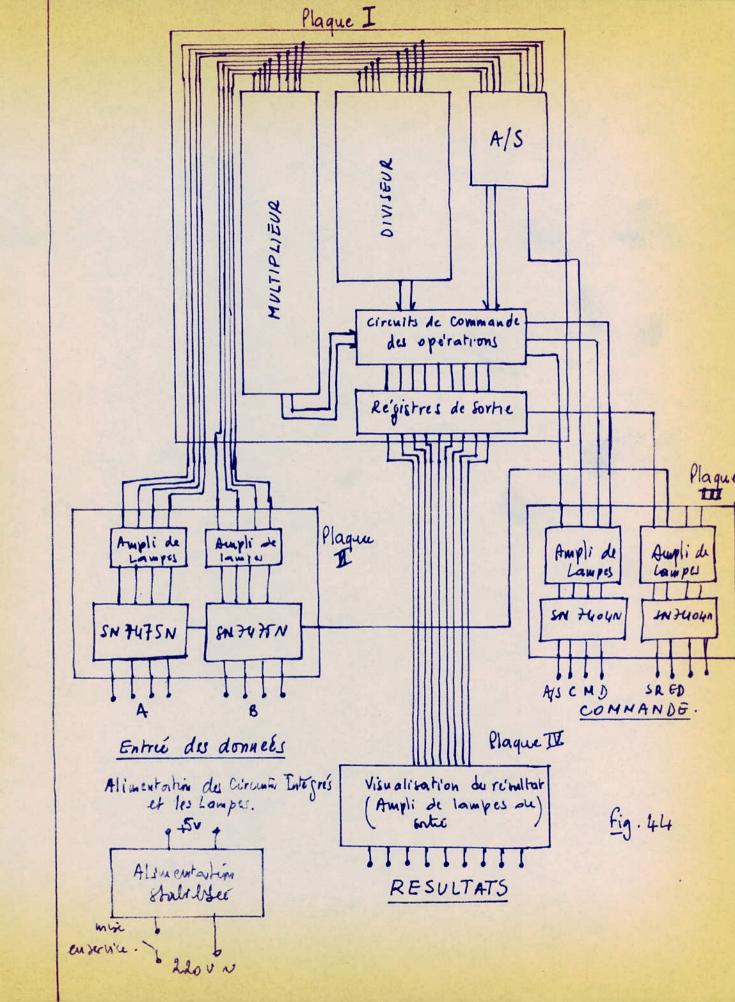

#### 1. Caractéristiques de l'unité de calcul:

L'unité de calcul qu'on veut réaliser est du type parallèle. Elle doit effectuer les 4 opération élémentaires : addition, soustraction, multiplica--cation et division; sur des nombres d'une longueur de 4 bits au maximun. Les nombres à traiter sont des nombres binaires positifs représentés en vir-gule fixe. Le résultat est donné es code binaire.

Le schéma synoptique de l'unité de calcul est donné par la figure 39

Le régistre résultat RR 1 emmagasine le reste de la division  $R_4R_3R_2R_1$  et les 4 bits  $P_4P_3P_2P_1$  de la multiplication. Le régistre RR 2 emmagasine le quotient  $Q_1Q_2$   $Q_3Q_4$ , les 4 bits  $P_8P_7P_5P_5$  de la multiplication et les 4 bits  $\sum_4\sum_3\sum_2\sum_1$  de l'addition ou de la soustraction. RR 3 reçoit simplement le bit  $C_4$ .

L'aspect extérieur de la maquette est représenté par la figure 40. Pour la construction de cette unité, on utilisera uniquement des circuits intégrés du type T.T.L.

## 2. Caractéristiques des circuits intégrés T.T.L:

- Tension d'alimentation 5 Volts ( 4,5 V à 5,5 V)

- Courant d'entrée au niveau logique 1 = 40 mmA à 2,4V;1mA à 5,5V.

- Courant de sortie au niveau logique 0=1,6 mA à 5,5 V .

- Fan-out ( ou sortance ) = 10 .

fig.41. <u>Vue de Face</u> <u>du pupitre</u>. SR: sortie du Résultat

ED = Entrée des Données.

- une entrée en l'air correspond au miveau logique 1 .

- Boîtier enfichable type TO 116

#### 3.Circuits intégrés utilisés:

- 3.1.Addition-Soustraction:

- 1 SN 7483 N

- 1 SN 74H87 N

- 1/6 SN 7404 N .

- 3.2. Multiplieur:

- 3 SN 7483 N

- 4 SN 7408 N .

- 3.3.Diviseur:

- 5 SN 7483 N

- 2 SN 7404 N

- 5 SN74H87 N

- 1 SN 74 86 N

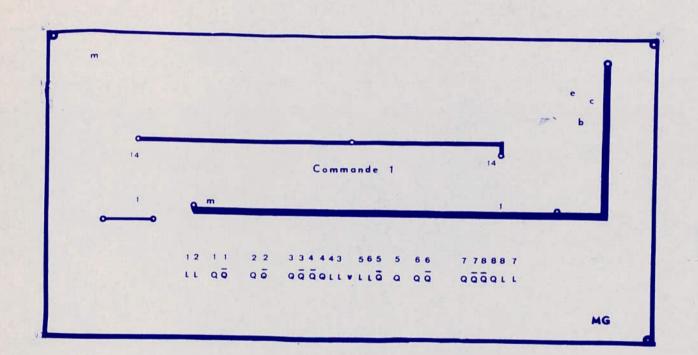

- 3.4. Circuits de commande de sortie des opérations:

- 5 SN 7409 N

- 3.5.Régistres d'entrée:

- -2 SN 7475 N

- 3.6. Registre de sortie:

- 3 SN 7475 N

- 3.7.Commande:

- 2 SN 7404 N

# 4. Visualisation des données et du résultat:

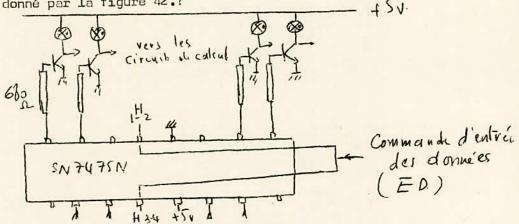

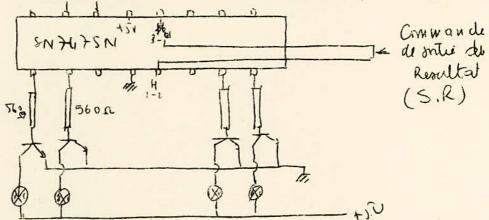

L'affichage des données se fait manuellement à l'aide d'interrupteurs.La sortie 1Q du registre SN 7475 N attaque la base d'un transistor 2N 2222 à tra-vers une résistance de 680 \( \Omega \).Le collecteur est chargé par une lampe (6,5V-70mA)

Le schéma est donné par la figure 42.?

Fig 42 . Visualisation des données;

Pour la visualisation du résultat, on utilise le même montage, sauf qu'ici ceux-sont les bits délivrés par le circuit de commande de sortie des opérations qui attaquent le registre SN 7475 N.Le schéma est représenté par la figure 43.

#### 5.Câblage:

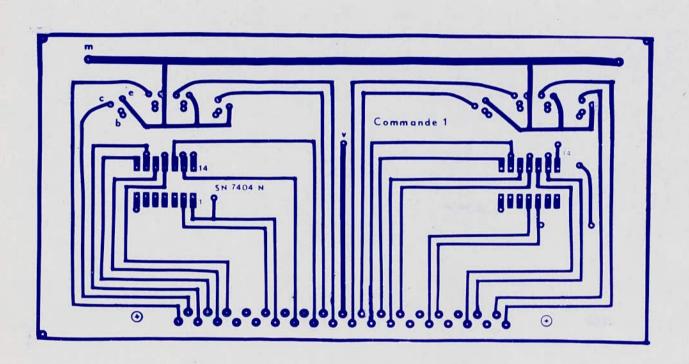

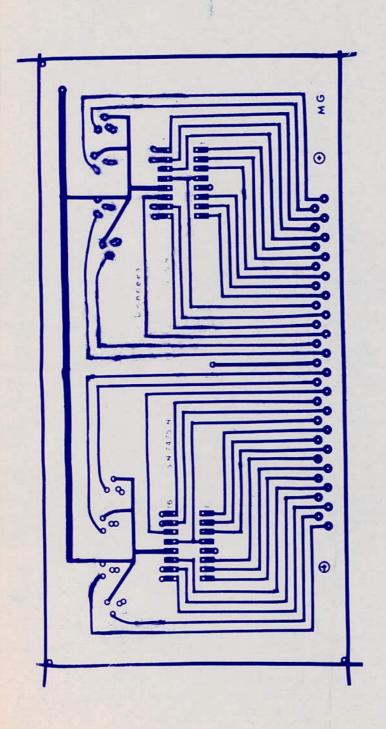

Les différents logiques sont réalisés sur circuit imprimé à double face. Différentes plaques :

\* Plaques IA IB comprend le bloc A/S,le multiplieur,le diviseur,le bloc de commande de sortie des opérations et les 3 régistres de sortie.

Plaque IA : face avant sur laquelle sont fixés les circuits intégrés.

Plaque IB : envers (face de soudure ).

\* Plaque IIA visualisation des données.

\* Plaque IIIA Commande de sortie des opérations.

\* Plaque IV Amplificateurs des lampes de sortie .

Le schéma global de l'unité de calcul est repéésenté par la figure 44.

## 6.Alimentation:

On utilise une alimentation stabilisée délivrant 5 Volte nécessaire pour l'alimentation des circuits intégrés et des lampes.

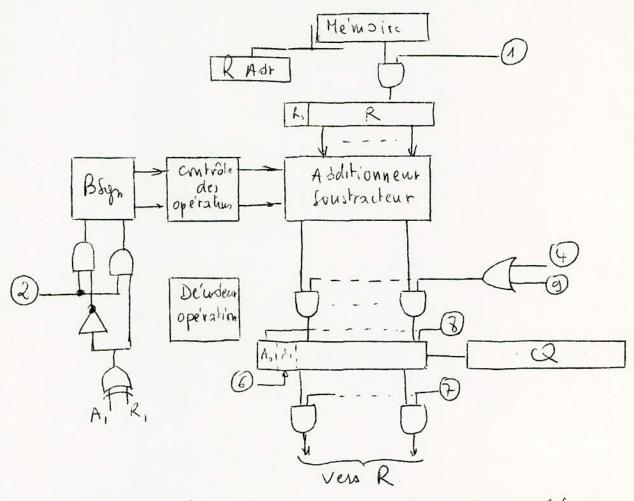

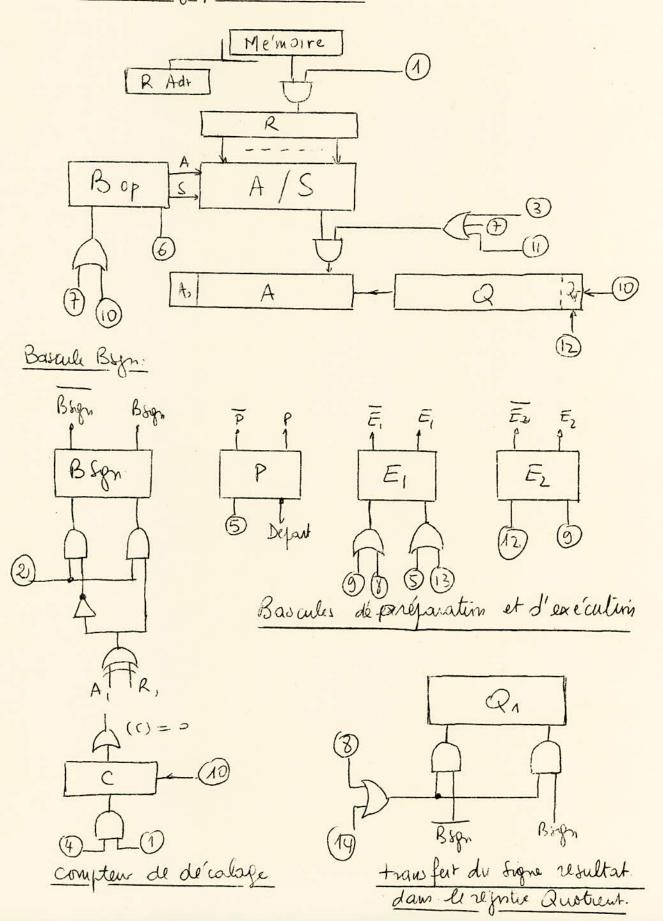

# ANNEXE 1

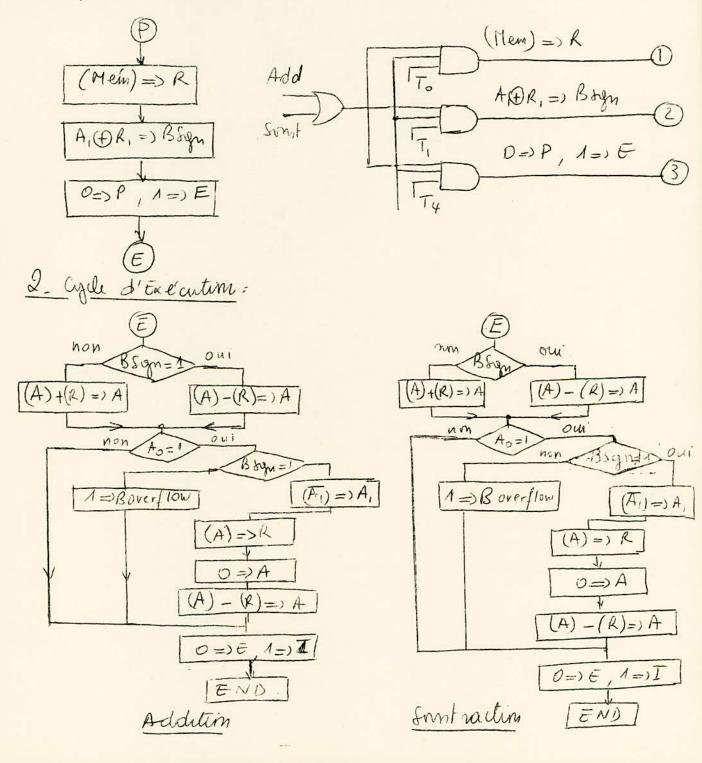

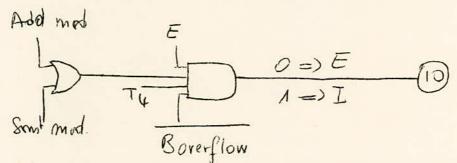

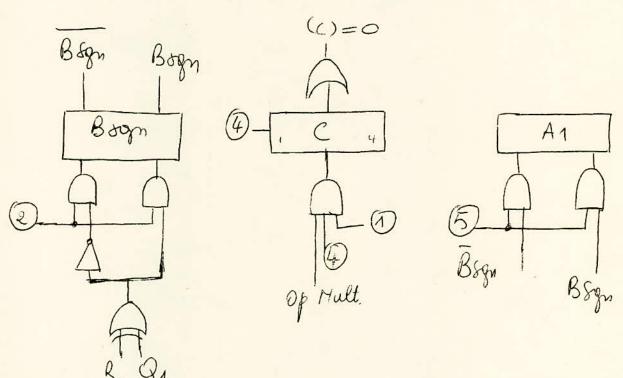

(Cas des nombres représentes en valeur abolie et signe) Organisation de l'unité arithmetique-Elle . comprend: \_ un régistre accumulateur A qui contient un des 2 oférandes en début d'opération dinsi que les résultats intermédiaires en como d'opération. - Un régistre multiplicateur - quotient Q relié au précédent pour former le régistre AQ qui contient le résultat de la multiflication et selvi de la division. - Un registre R qui contreut l'autre oférande fendant toute la durée de l'ofération. - elle additionnem-sonitraiteur du type parallèle. - lue bascule Boverflow qui indique l'inivalidaté des operations. Basale Bover flow R1 R2 R3 R4 R5 Addition Additionneur-Smst. CompteurC Soustroutin Ao A A A A A Au As Q, Q2 Q3 Q4 Q5 Abréviations et symboles: (A) = Contenu du régistre A (C) contenu du compteu C (A) => B transfert du contenu de A dans B. (C)-1=> C compteur C durine d'une unité. (A)+(B) => Somme logique du contenu de A et B fuis transféréé dans B. Bop = Bascule operation.

Bopin = Basule opération invalide.

# ADDITIONNEUR - SOUSTRACTEUR.

Ses nombres troites ent une longueur fisee de 5 lit. Ses lits A, et R, mont réser vés aux signes des 2 nombres. Pour em vension, en outribre au bit 0 le signe plus (+) et au bit 1 le signe moins (-). La comparaison de signis des 2 nombres est donnée par le circuit OU EXCLUSIF qui délivre un O si les 2 signes sont iden--tiques et un 1 s'ils pont différents. Le résultat de la Compa--raisin est memorisé dans une basaile siègne Bsgn. Suivant le code opération ( ouddition ou soustroution) et le contenu de Bogn, l'unité arithmétique effectue les opérations suivant le tableau survaut:

| RA | A       | Bagn  | opération  <br>effectuée | Opération sur les<br>modules.                                                                         |

|----|---------|-------|--------------------------|-------------------------------------------------------------------------------------------------------|

| 00 | 0-0-    | 0 - 0 | Addition                 | Addition des modules<br>Sonstraction des modules<br>Sonstraction des modules<br>Addition des modules. |

| 00 | 0 - 0 - | 00    | Soustradim               | Soustraction des moduls<br>Addition des moduls<br>Addition des moduls.<br>Sonstraction des moduls     |

Se tableau donne:

Add mid = B som. Add + B som. Sount. Sunst mid = B som. Add + B som. Soust

Se résultat de l'opération apparaît dans le régistre accumulateur s'il n'existe pas de report au delà der plus fort poisse du module, le résultat est exact. S'il existe un report dans la position Ao, il fout.

- change le signe du régistre acumulateur

- Complémenter à 2 le module du résultat.

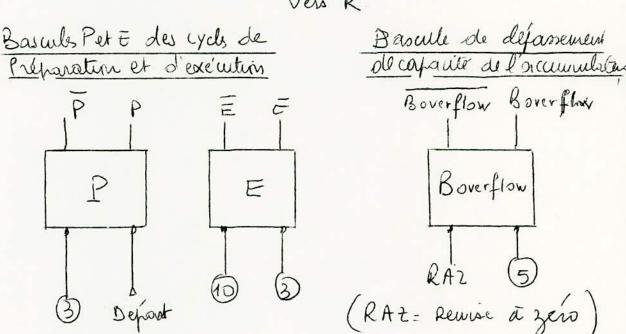

Cette complémentation à 2 s'obtient par un transfert du conterm de A (mons le vière) sland Re par une relivée à 0 des 4 positions du module de l'acum unlateur et par une sous-traction du contem de R etu conterm de A. Une bossule Boverflow signal un résultat misolide. Pour effectuer une opération, on procède en 2 cycls:

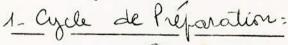

1- Cycle de préparation : il est identique pour les 2 opérations.

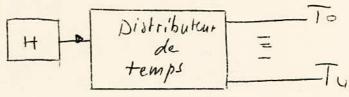

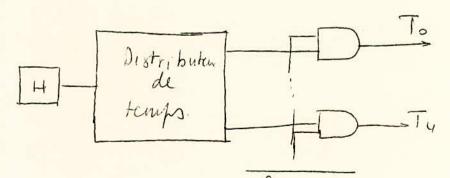

Les signaux To at 4 sont délivés par un distributeir de temps. Commandé par une horloge H.

Le rebelha général de l'additionnem-sonstracteur avec ses criants associés se présente comme sont:

#### MULTIPLIEUR BINAIRE

absolue et signe s'effectue en deux temps=

- signe du résultat

- produit des deux mobiles.

du multiplicateur et du multiplicande.

Boom = An +R1

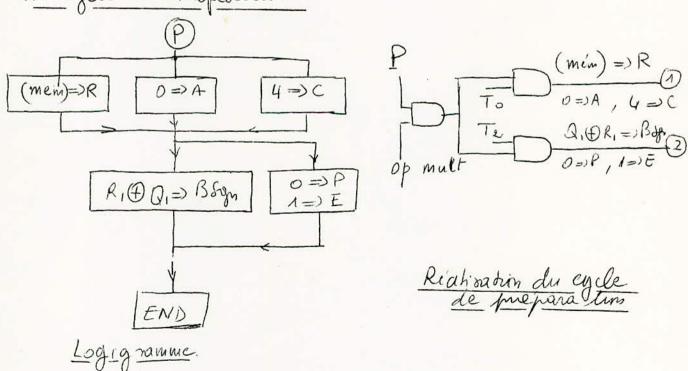

estégal au rembre de bits du multiplicateur.

si Q5=0 on ne fait aucune opération si Q5=1 on ordditionne le contenu du régistre R à celui de A.

en 2 cycles: effectuer la multiplication de 2 nombrs, on puriede

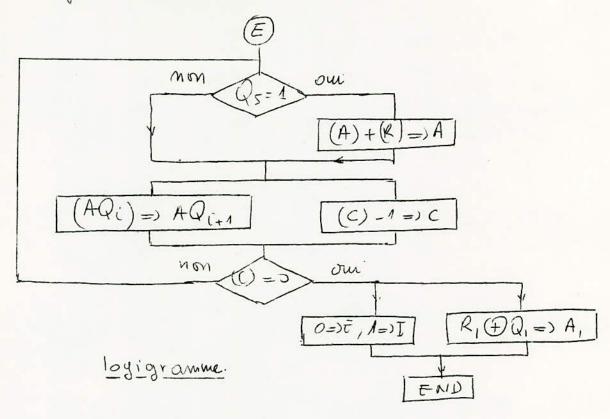

## 2. Cycle d'exécution:

Réalization du cycle d'exécution

# Scheina complet du multiplieur

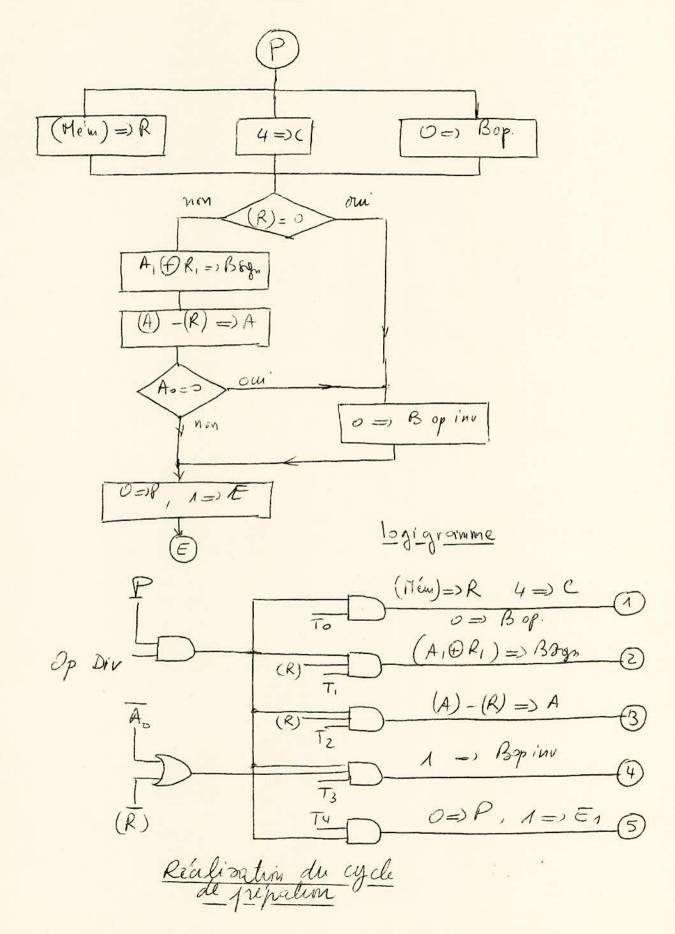

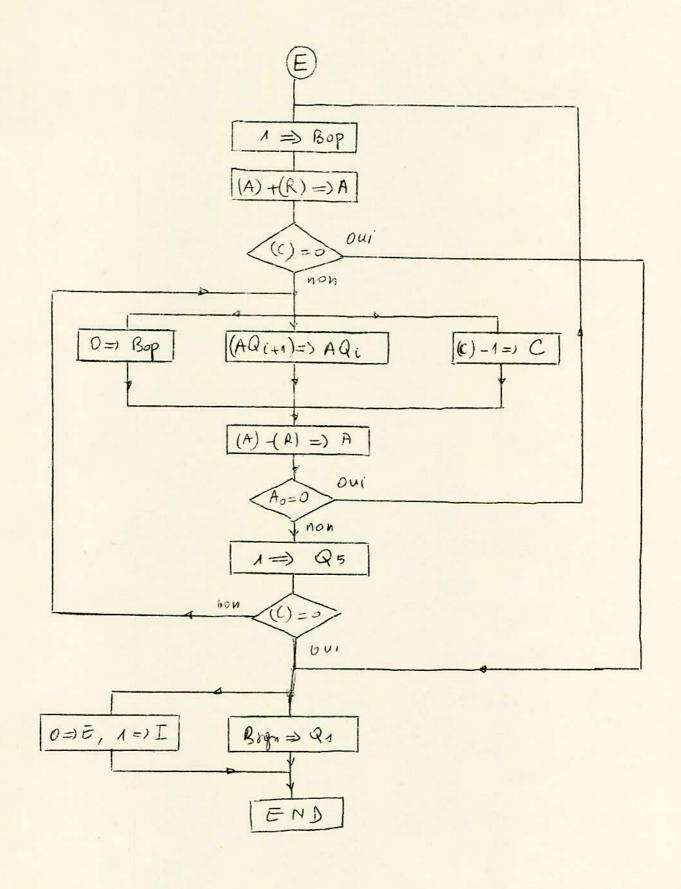

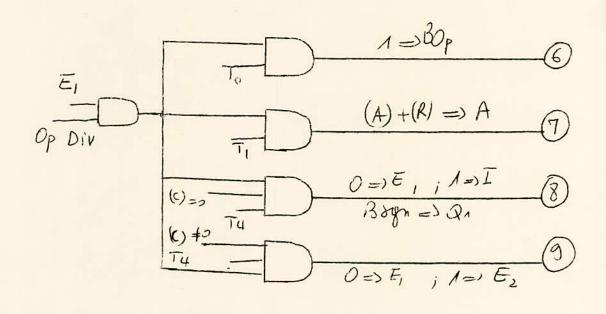

#### DIVISEUR BINAIRE

Comme pour la multiplication, le signe du résultait lest élabore about le début de l'opération et pris en mémore par la bascule sière on effectue ensuite les sontractions du mondule du diviséent dés plus fonts prids du mondule du diviséent dés plus fonts préalablement de colors d'un rang à ganthe on restaine le dividende chaque fois que la soit traction du diviseur sonne un résultat négatif (A = 1) cette réstauration s'obtient par une addition du diviseur it chaque reste partiel mégatif. Le sière de chaque rêste partiel impore la matture de l'opération su voule suivoi que le diçit correspondant

si Ao = 1, le let quitient est écal à 0 et l'ofératione suivante en une s'addition.

> Si Ao = 0, le lit quolient est egal à 1 et l'ofération sui voustel est rune sonstractioni.

Une boseule Bop inv midique une division modifie.

Jes signans To à Ty sont delives pou le distributeur

de temps lorsique l'opération est valide.

Les mipulsius To à Ty sont mihibés si Bop inv=1

5 ofération de division s'effectuéen deux cycles. 1- Cycle de préparation:

## 2. Cycle d'execution-

## Réalisation du Cycle d'execution:

Scheine logique du diviseur:

## ANNEXE 2. U-A et L en Virgule flottante

- neutille comportant à partie : la moutine et l'exprount. S'UAL dist réalise de aperation on le mantine et als opératim our le exproduts. Etant donné que l'unte de calcul étudiés feut troites de nombres in le viens et 1, un utilise cette unité forme la missimipulation des maintires. Il fourt donc un blor sey-plémentaire pour le traitement des exposants.

1. Addition amphautini: onew: A = a.2° et B = 6.2° on commence d'about par emparer les exposunts et à la colubant ex-B=d. On applite le plus faible sur le plus frant en décalant la muntione de d'Arango à droite. On effectué lu mite, l'add on la sonst des mantions. C'exposant du résultant est l'exposant le plus élevé. Enfin, on normalise la mantione n'cela est né des aire. Exp: 1500= 0 > B A + B = (a + 62-d) 2 d

$\frac{2 \omega_{\text{N}}}{\alpha} = \alpha < \beta$  A ± B =  $(\alpha.2^{-6} \pm 2) 2^{\text{B}}$

#### 2. Hultiplication et diniam:

on multiplie les mout per et en foit l'oddition de expreus.  $A \times B = (a, b), 2^{\alpha + \beta}$

fait la sontraction des exposurs

$\frac{A}{C_0} = \left(\frac{a}{b}\right), 2^{\alpha - \beta}.$

virgule flottante comprendra:

- une vinte operant m le mautines

- in add-smit pour les ofération our le corporants

- et un dispositif de contrôle de la normalisation du résultant.

#### BIBLIOGRAPHIE

- A.PROFIT : Structure et technologie des ordinateurs.

- BOULAYE ; Logique et organe des calculatrices numériques.

- R.LYON-CAEN : Circuits logiques intégrés.

- A.PETIT-CLERC :Traité des ordinateurs ( tome I et II ).

- J.SLOSIAR et N.LANNELONGUE : technologie des compodants II.

Calculs des bobines.Bobinage.Micromodules.Circuits intégrés.

- P.VOLMER : Calculateurs numériques ;

- H.BOUCHER :Organisation et fonctionnement des machines arithmétiques.

- Revue : Electronique Industrielle ( 1968-69-70 ).