#### RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR ET DE LA RECHERCHE SCIENTIFIQUE

#### ÉCOLE NATIONALE POLYTECHNIQUE

#### Département Electrotechnique

#### Mémoire de projet de fin d'études

Pour l'obtention du diplôme d'ingénieur d'état en Electrotechnique

Étude et implémentation de la MLI vectorielle d'un onduleur triphasé en utilisant les circuits FPGA

Présenté par : HAIDRA Ali et SIAD Mohamed

# Sous la Direction de **Pr.BERKOUK El Madjid** et **Pr.IMARAZENE Khoukha**

Présenté et soutenu publiquement le (02/07/2025)

#### Composition du jury :

Président : Pr.MO.Mahmoudi ENP

Examinateur : Pr.S.Hadji ENP

Encadrant : Pr.BERKOUK El Madjid ENP

Encadrante : Pr.IMARAZENE Khoukha USTHB

#### RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR ET DE LA RECHERCHE SCIENTIFIQUE

#### ÉCOLE NATIONALE POLYTECHNIQUE

#### Département Electrotechnique

#### Mémoire de projet de fin d'études

Pour l'obtention du diplôme d'ingénieur d'état en Electrotechnique

Étude et implémentation de la MLI vectorielle d'un onduleur triphasé en utilisant les circuits FPGA

Présenté par : HAIDRA Ali et SIAD Mohamed

# Sous la Direction de **Pr.BERKOUK El Madjid** et **Pr.IMARAZENE Khoukha**

Présenté et soutenu publiquement le (02/07/2025)

#### Composition du jury :

Président : Pr.MO.Mahmoudi ENP

Examinateur : Pr.S.Hadji ENP

Encadrant : Pr.BERKOUK El Madjid ENP

Encadrante : Pr.IMARAZENE Khoukha USTHB

#### ملخص

يعرض هذا العمل تنفيذ خوار زمية للتحكم بالتقنية الشعاعية من أجل قيادة محول ثلاثي الطور بثلاثة مستويات، وذلك باستخدام لوحة إلكترونية قابلة للبرمجة ميدانيًا، ولغة وصف العتاد. الهدف من هذا العمل هو توليد توتر ذو خرج عالي الجودة في الزمن الحقيقي. تظهر نتائج المحاكاة أن هذه الطريقة تتيح تحكمًا دقيقًا، وتقليلًا كبيرًا في معدل التشوه التوافقي، وتحسينًا في شكل الموجة، وذلك بفضل توليد سبعة وعشرين شعاعا للتوتر.

الكلمات المفتاحية :التحكم الشعاعي، محول بثلاثة مستويات، لوحة إلكترونية قابلة للبرمجة، لغة وصف العتاد، الزمن الحقيقي، معدل التشوه التوافقي.

#### Abstract

This work presents the implementation of a vector modulation algorithm to control a three-phase three-level inverter, using an FPGA board and the VHDL language. The objective is to generate a high-quality output voltage in real time. The simulation results show that this method allows precise control, a significant reduction of the THD, and a better waveform, thanks to the generation of 27 voltage vectors.

**Keywords:** Space Vector Modulation, Three-Level Inverter, FPGA, VHDL, Real-Time, Total Harmonic Distortion.

#### Résumé

Ce travail présente la mise en œuvre d'un algorithme de modulation vectorielle pour contrôler un onduleur triphasé à trois niveaux, en utilisant une carte FPGA et le langage VHDL. L'objectif est de générer une tension de sortie de haute qualité en temps réel. Les résultats de simulation montrent que cette méthode permet un contrôle précis, une réduction significative du THD et une meilleure forme d'onde, grâce à la génération de 27 vecteurs de tension.

Mots clés: Modulation vectorielle, onduleur à trois niveaux, FPGA, VHDL, temps réel, Taux de Distorsion Harmonique.

#### Remerciements

Nous tenons tout d'abord à exprimer notre profonde gratitude à Monsieur BER-KOUK El Madjid et Madame IMARAZENE Khoukha, nos encadrants, pour la qualité de leur accompagnement, leurs précieux conseils et leur disponibilité tout au long de ce travail. Nous adressons également nos sincères remerciements aux membres du jury pour l'honneur qu'ils nous font en acceptant d'évaluer notre travail, ainsi que pour l'intérêt et l'attention qu'ils ont portés à ce mémoire.

Nos remerciements vont aussi à toutes les personnes qui, de près ou de loin, nous ont apporté leur aide, leurs conseils ou leurs encouragements durant cette période. Nous remercions également nos collègues de l'École Nationale Polytechnique pour leur soutien, leur solidarité et les moments de partage qui ont marqué ces années d'études.

Enfin, nous tenons à exprimer toute notre reconnaissance à l'ensemble de nos professeurs pour la qualité de leur enseignement et leur engagement tout au long de notre parcours académique.

SIAD Mohamed et HAIDRA Ali.

## Table des matières

#### Liste des tableaux

#### Table des figures

| In | Introduction générale 12 |         |                                               |    |

|----|--------------------------|---------|-----------------------------------------------|----|

| 1  | Mo                       | délisat | ion et commande de l'onduleur à deux niveaux  | 12 |

|    | 1.1                      | Introd  | luction                                       | 12 |

|    | 1.2                      | La str  | ucture de base de l'onduleur à deux niveaux   | 12 |

|    |                          | 1.2.1   | Fonctions de commutation                      | 13 |

|    |                          | 1.2.2   | Etats d'un bras de l'onduleur                 | 13 |

|    |                          | 1.2.3   | Tensions de sortie                            | 14 |

|    | 1.3                      | Straté  | gies de commande                              | 16 |

|    |                          | 1.3.1   | La commande pleine onde                       | 16 |

|    |                          | 1.3.2   | Résultats de simulation et interprétations    | 17 |

|    |                          | 1.3.3   | La modulation de largeur d'impulsion (MLI)    | 19 |

|    |                          | 1.3.4   | Résultats de simulation et interprétations    | 20 |

|    | 1.4                      | Concl   | usion                                         | 26 |

| 2  | Mo                       | délisat | ion et commande de l'onduleur à trois niveaux | 27 |

|    | 2.1                      | Introd  | luction                                       | 27 |

|    | 2.2                      | La str  | ucture de base de l'onduleur à trois niveaux  | 27 |

|    |                          | 2.2.1   | Fonctions de commutation                      | 28 |

|    |                          | 2.2.2   | Etats d'un bras de l'onduleur                 | 29 |

|    |                          | 2.2.3   | Tensions de sortie                            | 32 |

|    | 23                       | Strató  | ries de commande                              | 33 |

|   |      | 2.3.1  | La commande pleine onde                                             | 33 |

|---|------|--------|---------------------------------------------------------------------|----|

|   |      | 2.3.2  | Résultats de simulation et interprétations                          | 34 |

|   |      | 2.3.3  | La modulation de largeur d'impulsion (MLI)                          | 36 |

|   |      | 2.3.4  | Résultats de simulation et interprétations                          | 36 |

|   | 2.4  | Concl  | usion                                                               | 42 |

| 3 | Stra | atégie | de modulation vectorielle d'un onduleur à trois niveaux (SVM)       | 43 |

|   | 3.1  | Introd | luction                                                             | 43 |

|   | 3.2  | Princi | pe général de la modulation par vecteur spatial (SVM)               | 44 |

|   |      | 3.2.1  | Vecteur tension de sortie et diagramme vectoriel                    | 45 |

|   |      | 3.2.2  | Détermination du secteur                                            | 46 |

|   |      | 3.2.3  | Détermination de la région                                          | 46 |

|   |      | 3.2.4  | Définition de la période d'échantillonnage dans la MLI vectorielle  | 47 |

|   |      | 3.2.5  | Séquence des états de l'onduleur                                    | 47 |

|   |      | 3.2.6  | Résumé de l'algorithme SVM pour l'onduleur triphasé à trois niveaux | 52 |

|   |      | 3.2.7  | Résultats de simulation et interprétations                          | 53 |

|   | 3.3  | Concl  | usion                                                               | 63 |

| 4 | Imp  | olémen | tation de la stratégie SVM sur un circuit FPGA                      | 64 |

|   | 4.1  | Introd | luction:                                                            | 64 |

|   | 4.2  | Métho  | odologie de conception                                              | 65 |

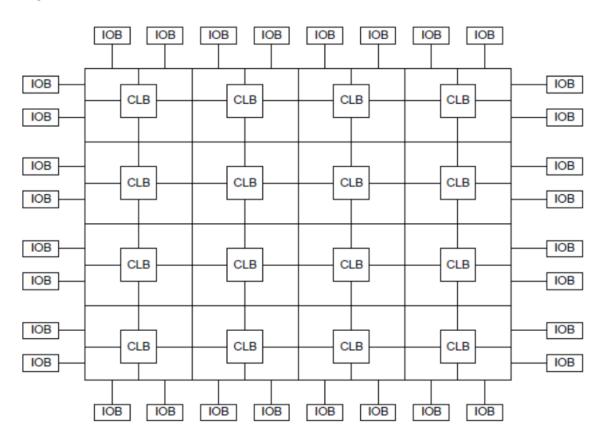

|   | 4.3  | Qu'est | t-ce qu'un FPGA?                                                    | 65 |

|   | 4.4  | Doma   | ines d'application de l'FPGA                                        | 66 |

|   | 4.5  | Avanta | ages et inconvénients des FPGA                                      | 66 |

|   | 4.6  | Archit | tecture interne des FPGA                                            | 67 |

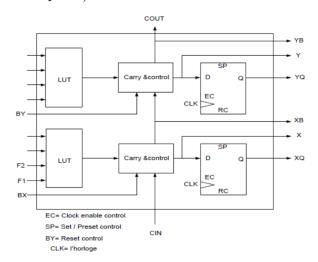

|   |      | 4.6.1  | Structure des CLB                                                   | 68 |

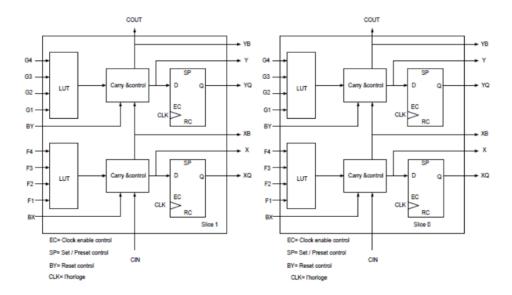

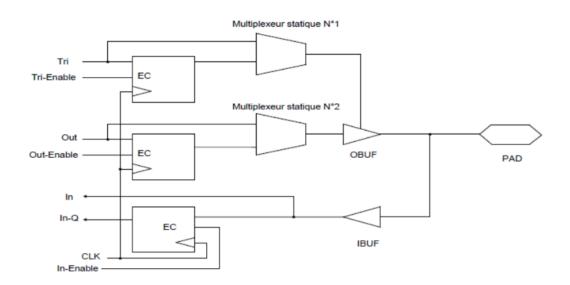

|   |      | 4.6.2  | Structure des IOB                                                   | 69 |

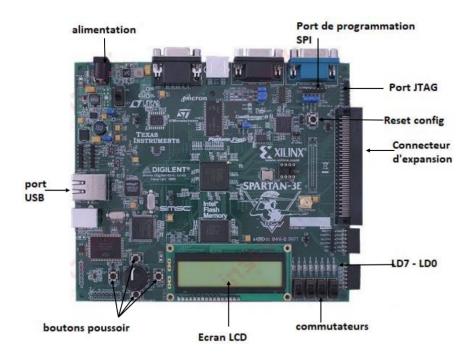

|   | 4.7  | Descri | ption de la carte :                                                 | 70 |

|   |      | 4.7.1  | Caractéristiques de la carte SPARTAN-3E :                           | 70 |

|   |      | 4.7.2  | Les spécifications de la carte :                                    | 71 |

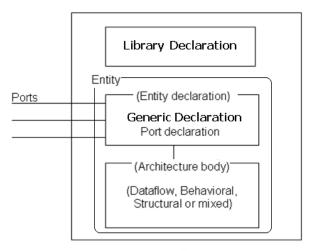

|   | 4.8  | Le lan | guage VHDL                                                          | 71 |

|   |      | 4.8.1  | Structure du langage VHDL                                           | 72 |

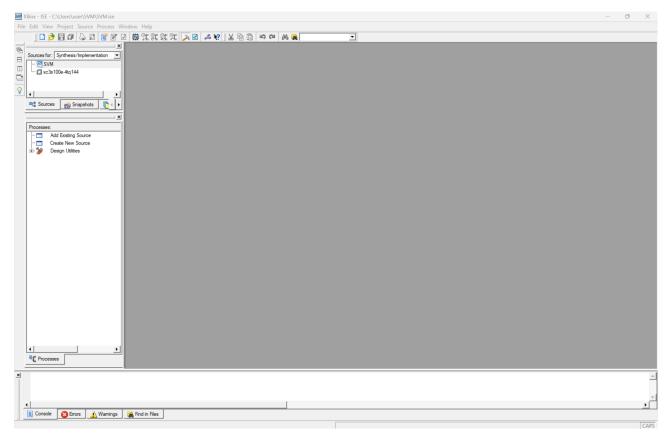

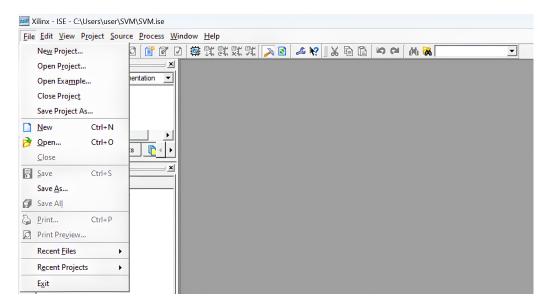

| 4.9     | Le log                            | iciel Xilinx ISE                                         | 73 |  |  |

|---------|-----------------------------------|----------------------------------------------------------|----|--|--|

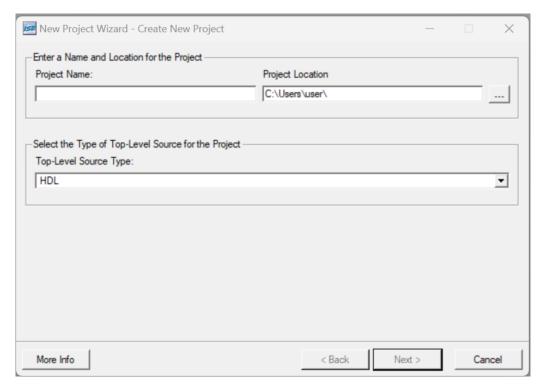

|         | 4.9.1                             | Création d'un nouveau projet                             | 74 |  |  |

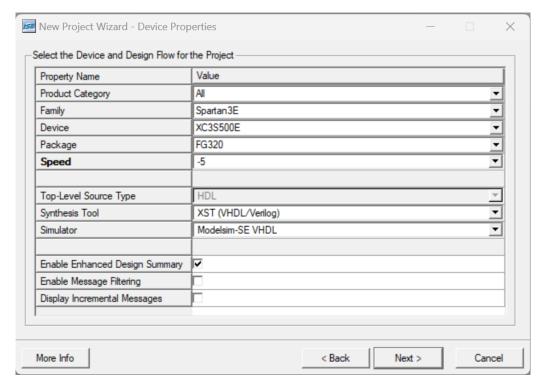

|         | 4.9.2                             | Sélection du FPGA et des outils de développement         | 75 |  |  |

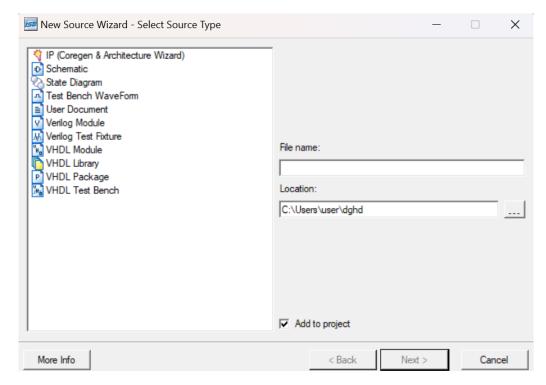

|         | 4.9.3                             | Les différents types de fichiers utilisés dans un projet | 76 |  |  |

| 4.10    | Imple                             | nentation de la commande MLI vectorielle sur FPGA        | 77 |  |  |

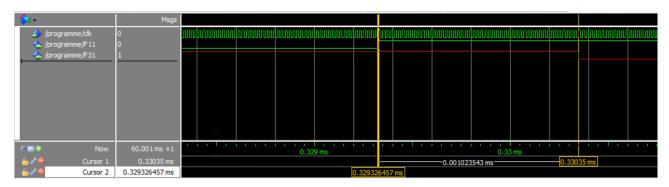

| 4.11    | Visual                            | isation des signaux avec ModelSim                        | 77 |  |  |

| 4.12    | Config                            | guration de la carte FPGA - SPARTAN-3E                   | 80 |  |  |

|         | 4.12.1                            | Etapes de la configuration                               | 80 |  |  |

|         | 4.12.2                            | Résultats expérimentaux et interprétations               | 81 |  |  |

| Conclu  | ısion g                           | énérale                                                  | 87 |  |  |

| Bibliog | graphie                           |                                                          | 90 |  |  |

| Annex   | Annexe A : les charges utilisé 99 |                                                          |    |  |  |

| Annex   | e B : le                          | es charges utilisé                                       | 93 |  |  |

## Liste des tableaux

| 1.1 | Table d'excitation pour N=2                                                                         | 14 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 2.1 | Etats d'un bras de l'onduleur                                                                       | 30 |

| 3.1 | Décomposition par région pour la SVM d'un onduleur à trois niveaux                                  | 49 |

| 3.2 | Temps de commutation $T_x$ , $T_y$ et $T_z$ pour chaque région du SVM d'un onduleur à trois niveaux | 49 |

| 3.3 | Séquences des états dans les différentes régions du diagramme vectoriel                             | 50 |

| 3.4 | Durées de fermeture des interrupteurs dans le cas du premier secteur                                | 52 |

| 4.1 | Les domaines d'applications                                                                         | 66 |

| 4.2 | Les avantages et les inconvénients                                                                  | 66 |

| 4.3 | Caractéristiques techniques de la carte FPGA Spartan-3F                                             | 70 |

# Table des figures

| 1.1  | Structure de base de l'onduleur à deux niveaux                                                     | 13 |

|------|----------------------------------------------------------------------------------------------------|----|

| 1.2  | Etats d'un bras de l'onduleur à deux niveaux.                                                      | 14 |

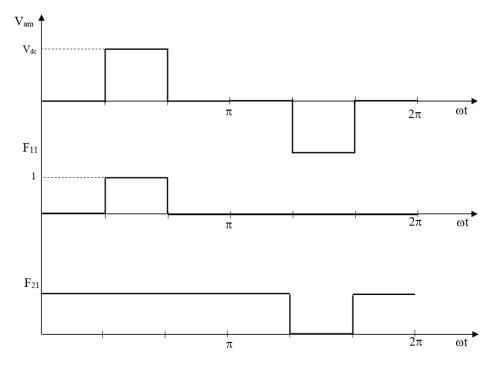

| 1.3  | La forme des signaux de commande F11 et F21 pour l'onduleur à deux niveaux .                       | 17 |

| 1.4  | La forme des signaux de commande de F11 et F21 pour l'onduleur à deux niveaux                      | 18 |

| 1.5  | La tension de sortie Vam de l'onduleur à deux niveaux                                              | 18 |

| 1.6  | La tension composée Uab de l'onduleur à deux niveaux                                               | 18 |

| 1.7  | La tension simple Van                                                                              | 19 |

| 1.8  | Analyse harmonique de Van (V)                                                                      | 19 |

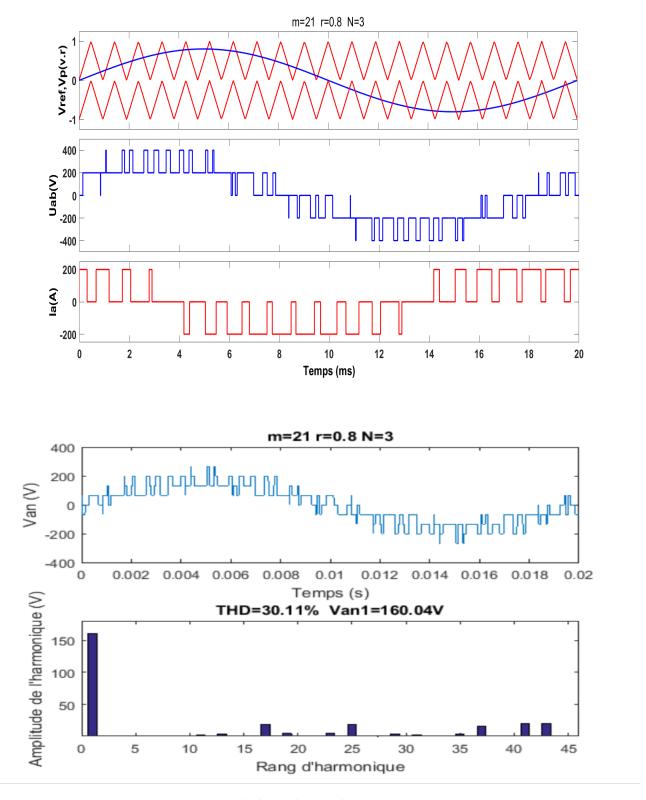

| 1.9  | Résultats de simulation pour m=9 et r=0.8                                                          | 21 |

| 1.10 | Résultats de simulation pour m=21 et r=0.8                                                         | 22 |

| 1.11 | Résultats de simulation pour m=36 et r=0.8                                                         | 23 |

| 1.12 | Résultats de simulation pour m=36 et r=0.4                                                         | 24 |

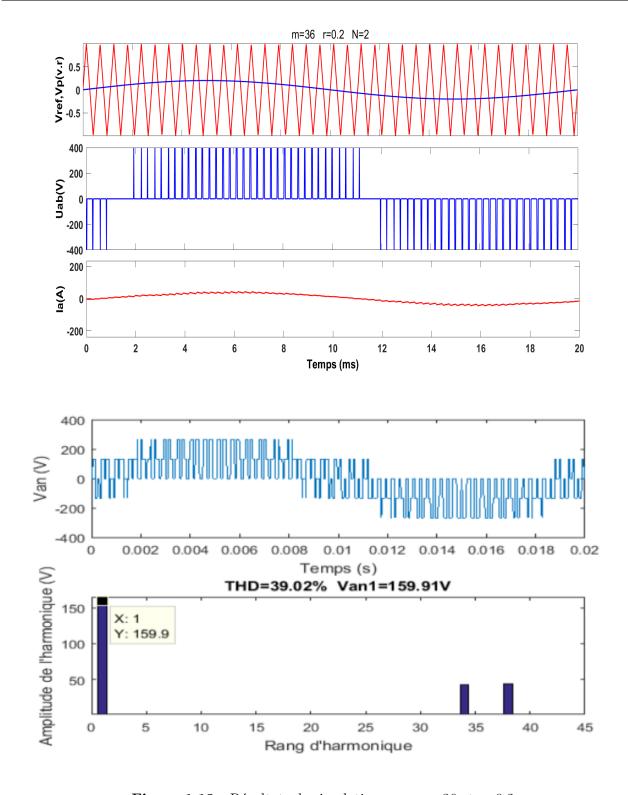

| 1.13 | Résultats de simulation pour m=36 et r=0.2                                                         | 25 |

| 2.1  | Structure NPC de l'onduleur à trois niveaux                                                        | 28 |

| 2.2  | Etats d'un bras de l'onduleur à trois niveaux                                                      | 29 |

| 2.3  | Etats de l'onduleur                                                                                | 31 |

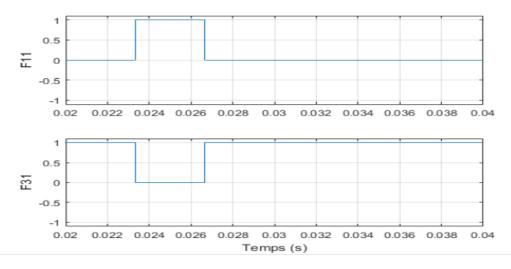

| 2.4  | La forme des signaux de commande $F_{11}$ et $F_{21}$ pour l'onduleur à trois niveaux $$ .         | 34 |

| 2.5  | La forme des signaux de commande des interrepteurs de premier bras pour l'onduleur à trois niveaux | 35 |

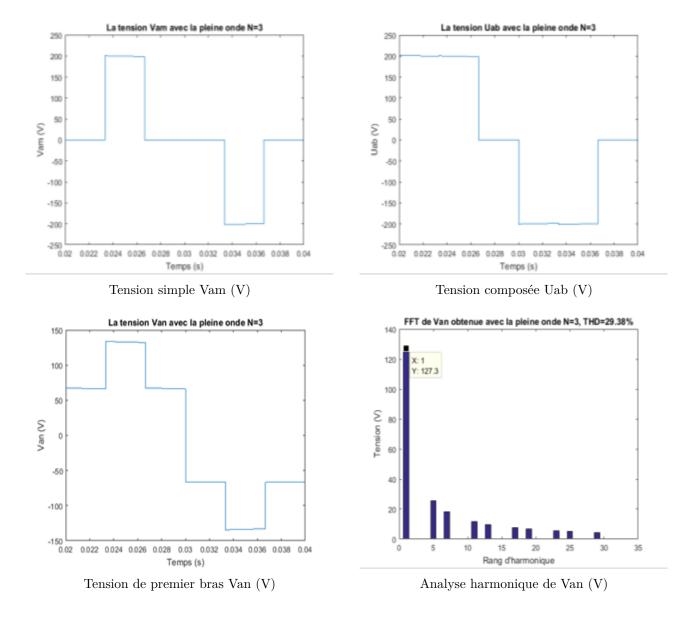

| 2.6  | Résultats de fonctionnement de l'onduleur à 3 niveaux avec la commande pleine onde                 | 35 |

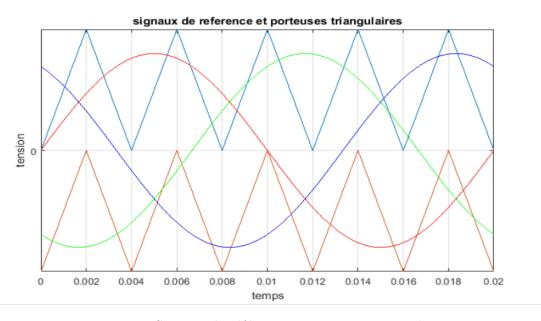

| 2.7  | Signaux de référence et porteuses triangulaires                                                    | 36 |

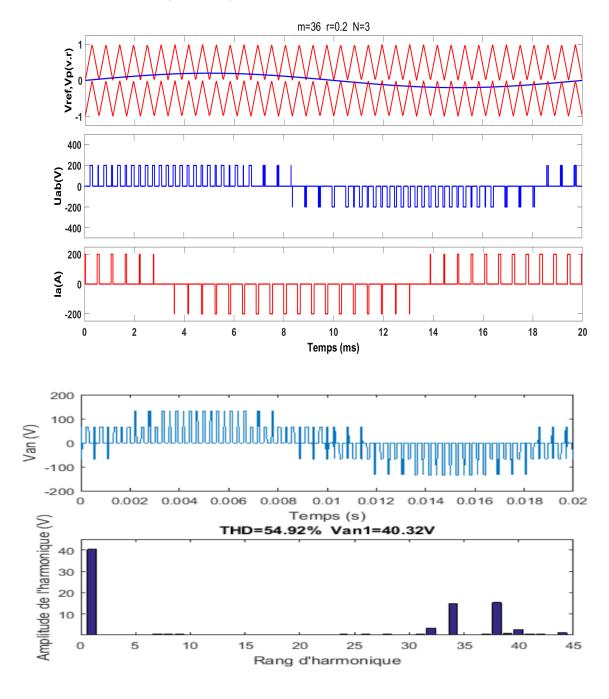

| 2.8  | Résultats de simulation pour m=36 et r=0.2                                                         | 37 |

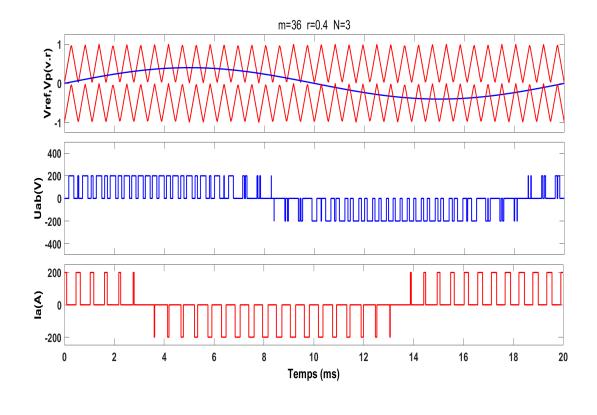

| 2.9  | Résultats de simulation pour m=36 et r=0.4                                                         | 38 |

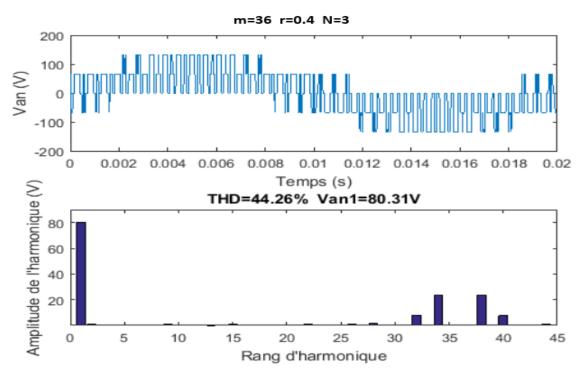

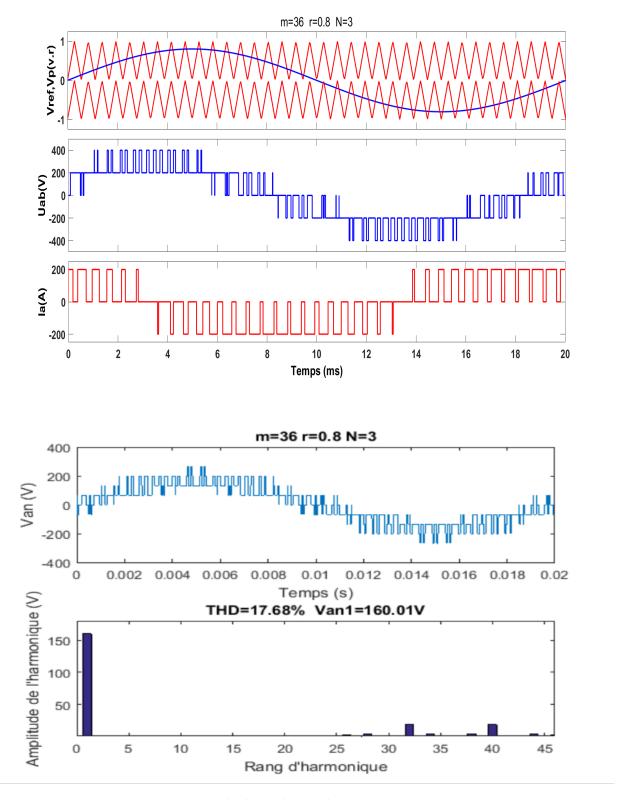

| 2 10 | Résultats de simulation pour m=36 et r=0.8                                                         | 39 |

| 2.11 | Résultats de simulation pour m=21 et r=0.8                                     | 40 |

|------|--------------------------------------------------------------------------------|----|

| 2.12 | Résultats de simulation pour m=9 et r=0.8                                      | 41 |

| 3.1  | Vecteur tension de référence.                                                  | 45 |

| 3.2  | Secteurs et régions du diagramme vectoriel                                     | 47 |

| 3.3  | Etats X, Y et Z pour les différentes régions du diagramme vectoriel            | 48 |

| 3.4  | Fonctions logiques $F_{ij}$ dans les quatre régions du premier secteur $\dots$ | 51 |

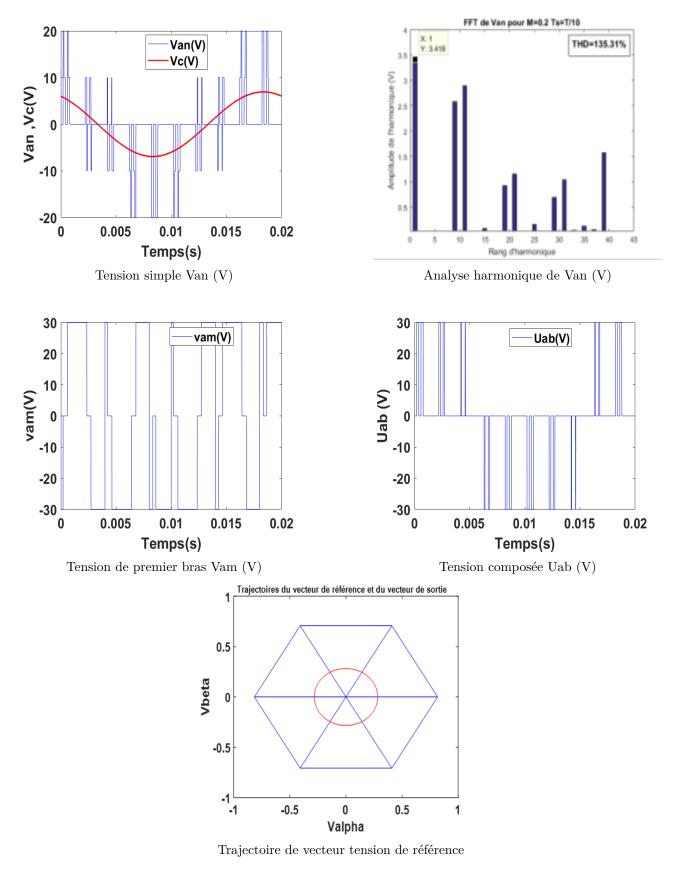

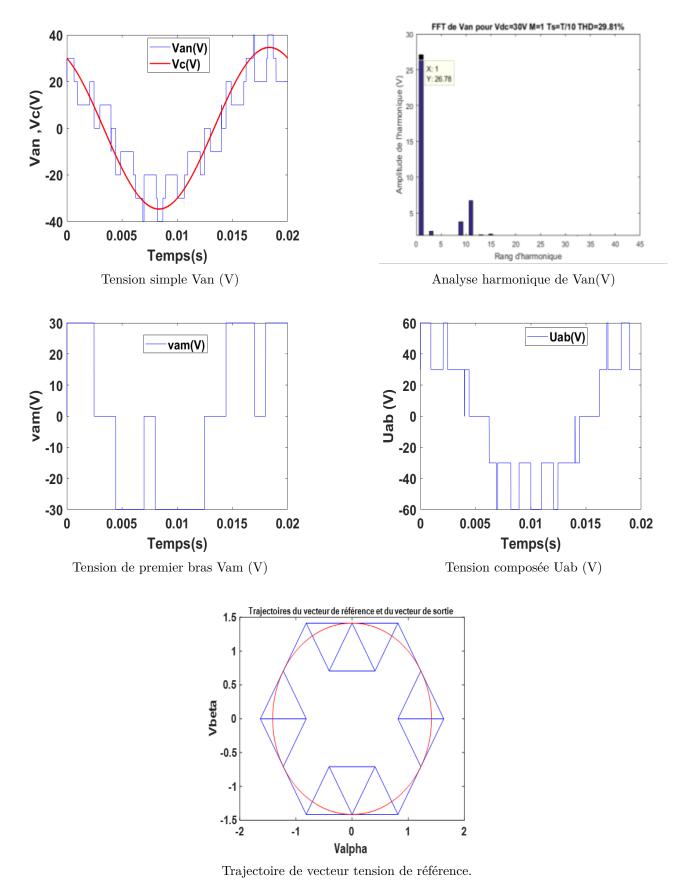

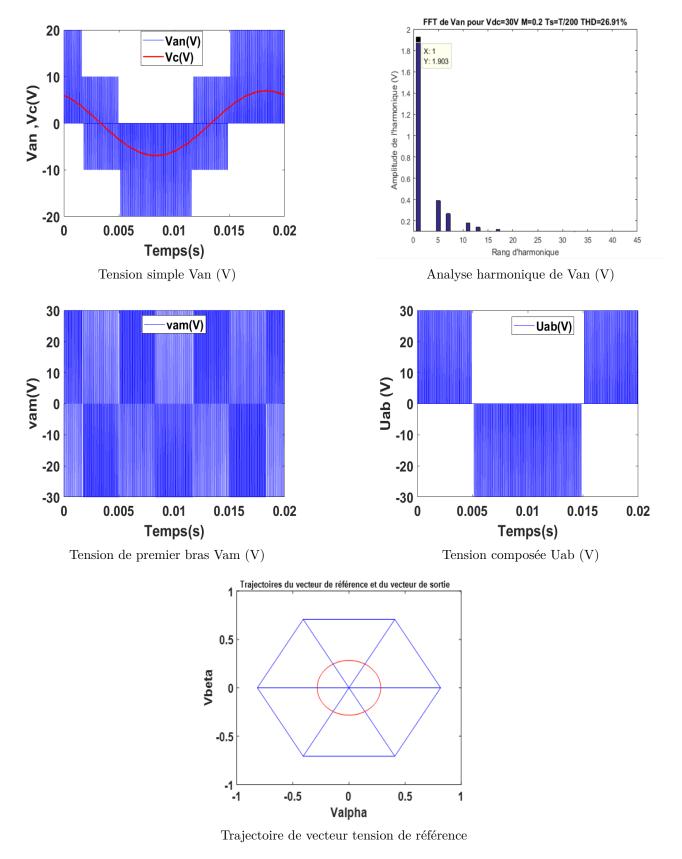

| 3.5  | Résultats de simulation pour Ts=T/10 et m=0.2                                  | 54 |

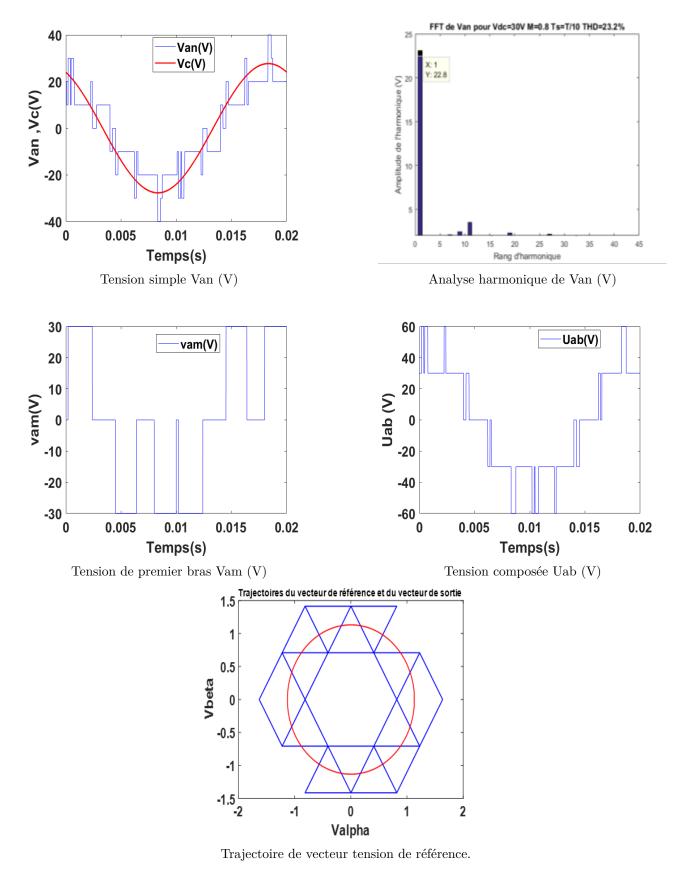

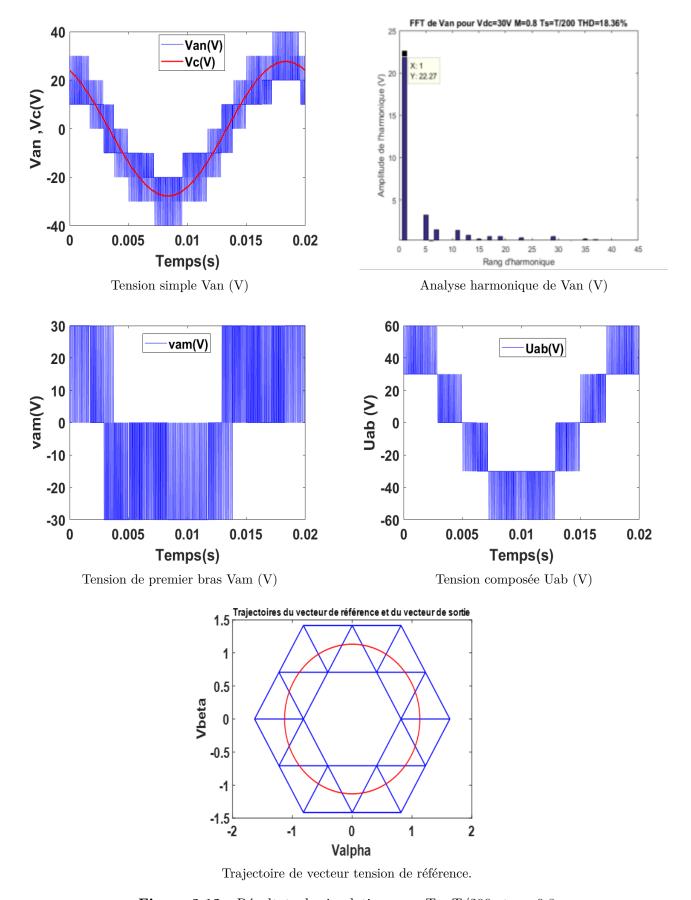

| 3.6  | Résultats de simulation pour Ts=T/10 et m=0.8                                  | 55 |

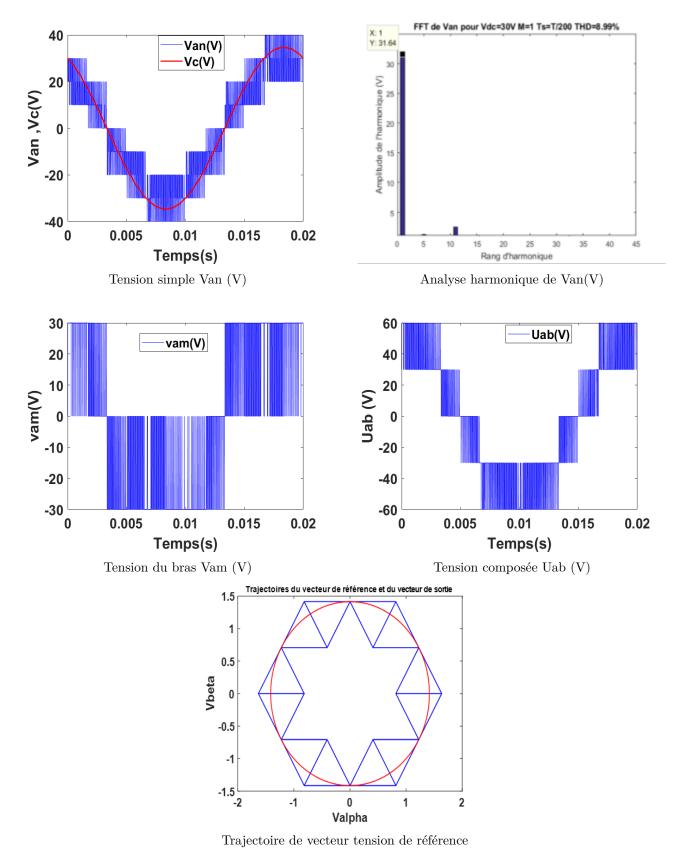

| 3.7  | Résultats de simulation pour Ts=T/10 et m=1                                    | 56 |

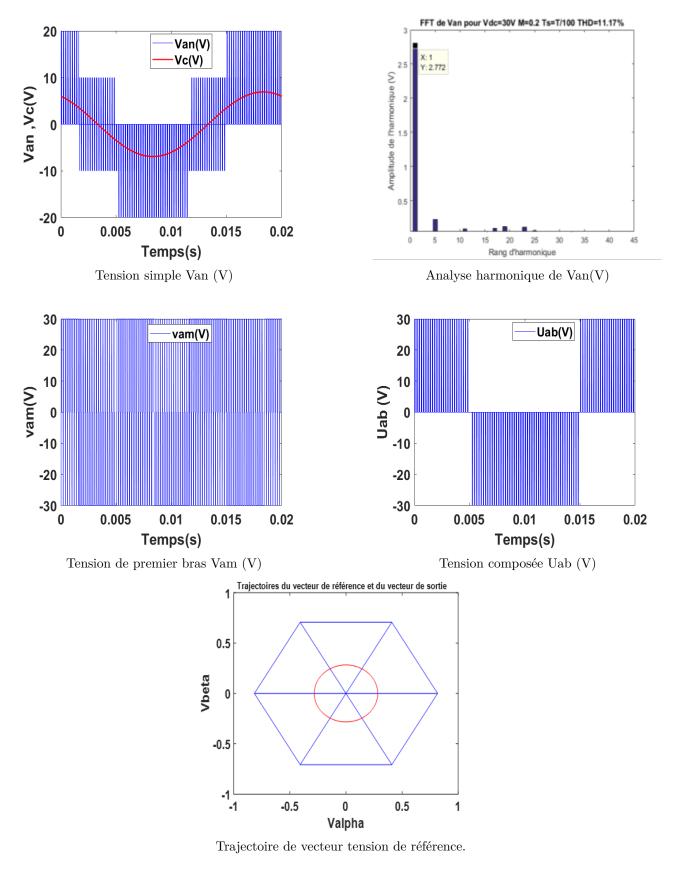

| 3.8  | Résultats de simulation pour Ts=T/100 et m=0.2                                 | 57 |

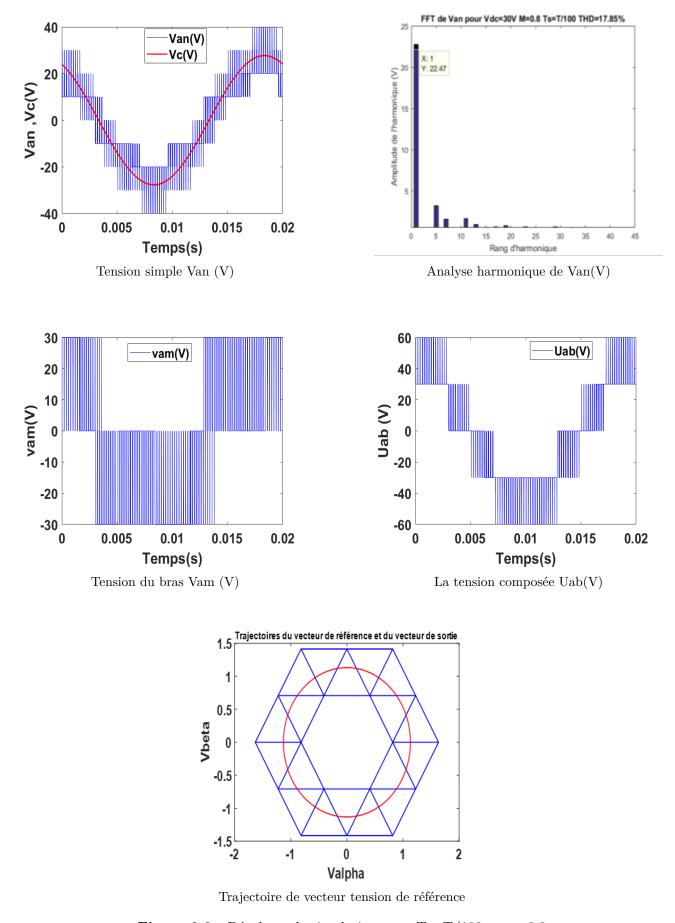

| 3.9  | Résultats de simulation pour Ts=T/100 et m=0.8                                 | 58 |

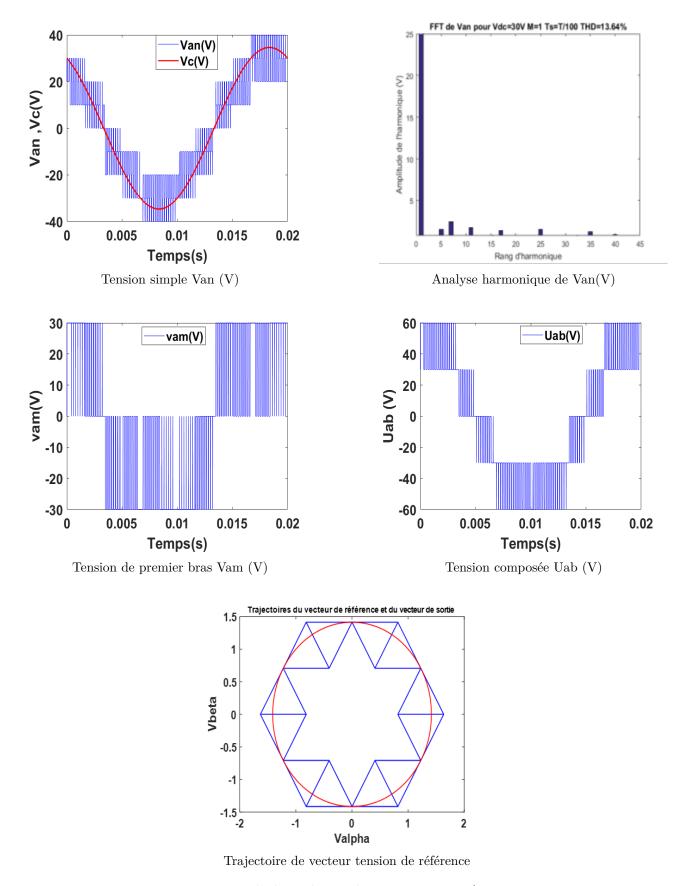

| 3.10 | Résultats de simulation pour Ts=T/100 et m=1                                   | 59 |

| 3.11 | Résultats de simulation pour Ts=T/200 et m=0.2                                 | 60 |

| 3.12 | Résultats de simulation pour Ts=T/200 et m=0.8                                 | 61 |

| 3.13 | Résultats de simulation pour Ts=T/200 et m=1                                   | 62 |

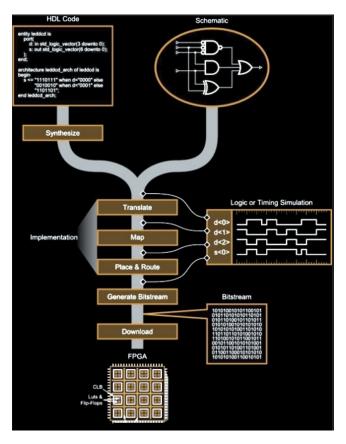

| 4.1  | Méthodologie de conception d'un FPGA                                           | 65 |

| 4.2  | L'architecture interne d'un FPGA                                               | 67 |

| 4.3  | Architecture d'un SLICE de famille Virtex                                      | 68 |

| 4.4  | Architecture d'un CLB de famille Virtex                                        | 68 |

| 4.5  | Architecture d'un IOB de famille Virtex                                        | 69 |

| 4.6  | Carte FPGA SPARTAN-3E                                                          | 70 |

| 4.7  | La structure d'une entité                                                      | 72 |

| 4.8  | La structure d'une architecture                                                | 72 |

| 4.9  | La structure d'un code VHDL                                                    | 73 |

| 4.10 | L'interface de logiciel Xilinx ISE                                             | 73 |

| 4.11 | Création d'un nouveau projet Xilinx ISE                                        | 74 |

| 4.12 | Le choix de modéle                                                             | 75 |

| 4.13 | Les paramètres de projet                                                       | 76 |

| 4.14 | Les différents types de fichiers utilisés dans un projet                       | 77 |

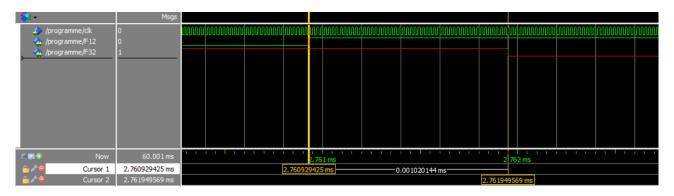

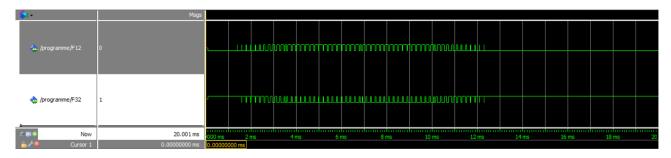

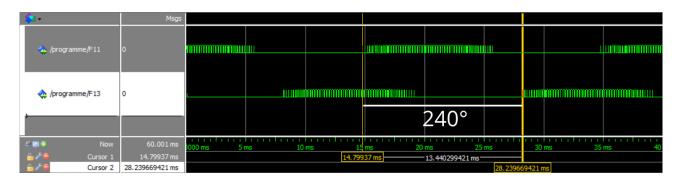

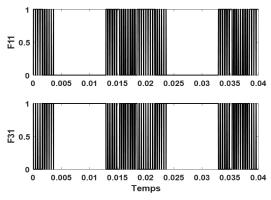

| 4.15 | Le temps mort entre F11 et F31                                                 | 78 |

| 4.16 | Temps mort entre F12 et F32                              | 78 |

|------|----------------------------------------------------------|----|

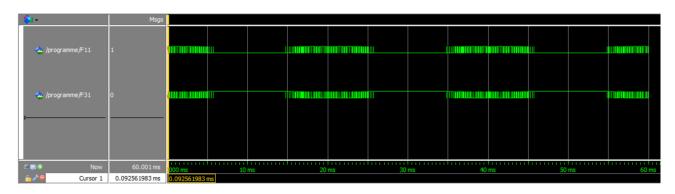

| 4.17 | Les signaux de commande de F11 et F31 sur 3 périodes     | 78 |

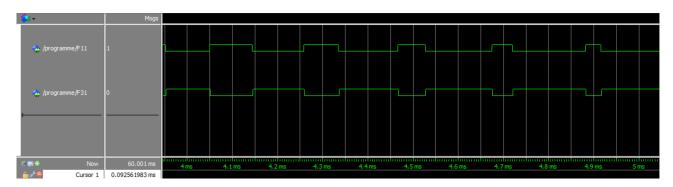

| 4.18 | Les signaux de commande de F12 et F32 sur 3 périodes     | 78 |

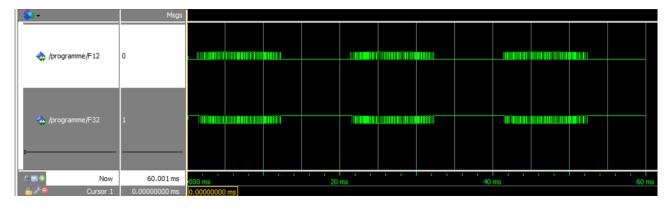

| 4.19 | Les signaux de commande de F11 et F31 sur une période    | 79 |

| 4.20 | Les signaux de commande de F12 et F32 sur une période    | 79 |

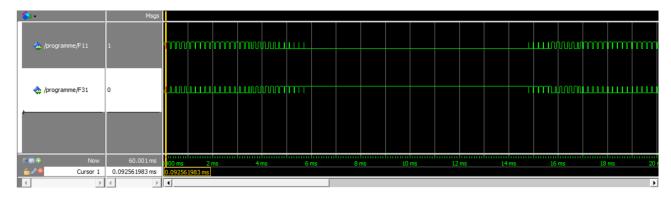

| 4.21 | Les signaux de commande de F11 et F31 sur $T/4$          | 79 |

| 4.22 | Les signaux de commande de F12 et F32 sur $T/4$          | 79 |

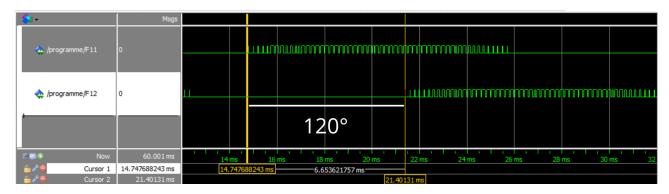

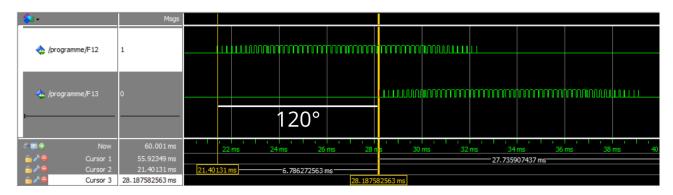

| 4.23 | Le déphasage 120° entre F11 et F12                       | 80 |

| 4.24 | Le déphasage 120° entre F12 et F13                       | 80 |

| 4.25 | Le déphasage 240° entre F11 et F13                       | 80 |

| 4.26 | Le tableau de correspondance des broches                 | 81 |

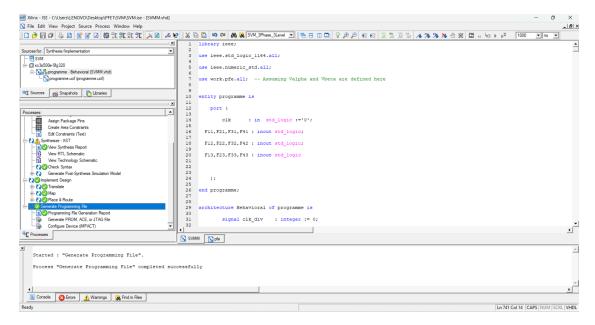

| 4.27 | Validation et implémentation du programme VHDL           | 81 |

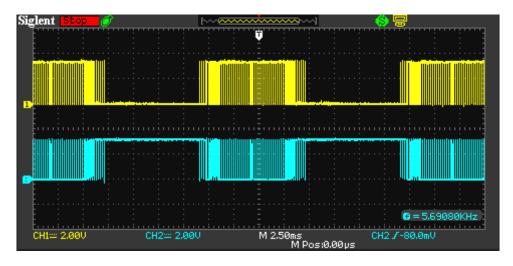

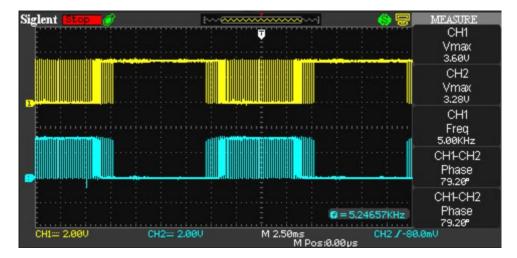

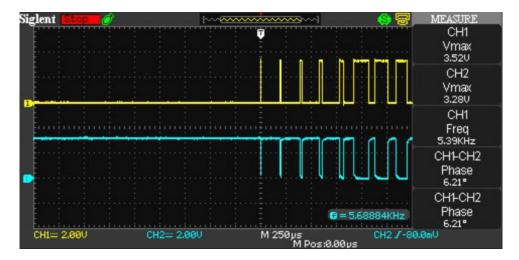

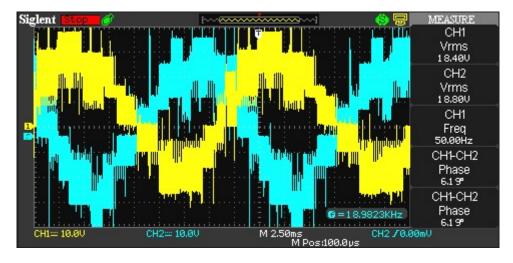

| 4.28 | Les signaux de commande de F11 et F31 sur trois périodes | 82 |

| 4.29 | Les signaux de commande de F21 et F41 sur trois périodes | 83 |

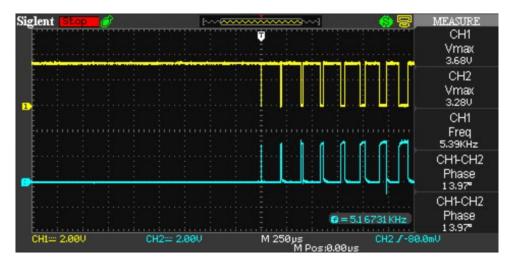

| 4.30 | Les signaux de commande de F11 et F31 sur 0,25ms         | 83 |

| 4.31 | Les signaux de commande de F21 et F41 sur 0,25ms         | 83 |

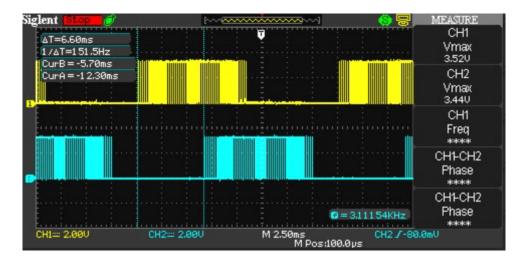

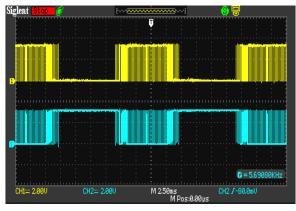

| 4.32 | Le déphasage de 120° entre F11 et F12 $\hdots$           | 84 |

| 4.33 | Le déphasage de 240° entre F11 et F13 $\hdots$           | 84 |

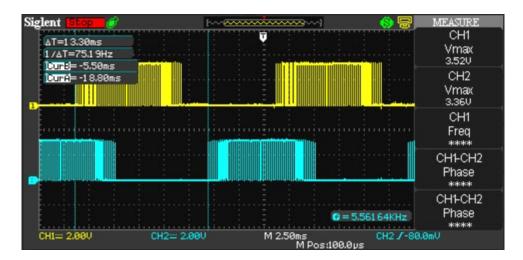

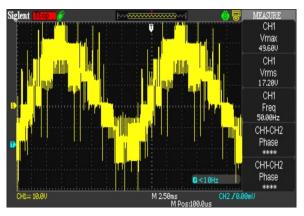

| 4.34 | La tension Van et la tension Vbn                         | 84 |

| 4.35 | Les signaux de commande de F11 et F31                    | 85 |

| 4.36 | La tension simple Van                                    | 85 |

| 4.37 | La tension de premier bras VAM                           | 85 |

| 4.38 | Le banc d'essai                                          | 86 |

## Introduction générale

Le développement rapide des algorithmes de commande performants pour les machines à courant alternatif nécessite des dispositifs de réglage tout aussi efficaces, tant en termes de tension que de fréquence d'alimentation. Parmi les solutions les plus couramment adoptées aujourd'hui, les onduleurs à trois niveaux occupent une place prépondérante [9].

Afin d'améliorer la qualité de la tension délivrée par ces convertisseurs statiques, de nombreuses topologies ont été étudiées puis développées. Dans le secteur industriel, trois structures principales sont largement commercialisées : la structure NPC (Neutral Point Clamped), les structures imbriquées, ainsi que les onduleurs en cascade (en H) [9].

La forme de la tension de sortie dépend également de la stratégie de commande utilisée. Plusieurs méthodes ont été mises au point, notamment la commande en pleine onde et les techniques de modulation de largeur d'impulsion (MLI), telles que la modulation triangulo-sinusoïdale, la commande par hystérésis, ou encore la modulation vectorielle [10].

Ce projet de fin d'études se concentre sur l'étude de l'onduleur à trois niveaux de type NPC. Il débute par la modélisation mathématique de l'onduleur à deux niveaux, suivie de l'analyse détaillée de deux stratégies de commande : la commande en pleine onde et la commande triangulo-sinusoïdale. Le deuxième chapitre aborde ensuite la modélisation mathématique de l'onduleur à trois niveaux, accompagnée de l'étude des mêmes stratégies de commande adaptées à cette topologie. La stratégie dite Space Vector Modulation PWM (SVM) pour l'onduleur à trois niveaux est ensuite programmée sous MATLAB/Simulink, et les résultats de simulation obtenus sont présentés et interprétés. Enfin, la SVM est programmée en langage VHDL et réalisée matériellement sur une carte FPGA afin de générer les signaux de commande nécessaires pour le contrôle en temps réel d'un onduleur à 12 IGBTs.

Ce mémoire est structuré en 4 chapitres de la manière suivante :

Chapitre 1 : Modélisation et commande de l'onduleur à deux niveaux

Chapitre 2 : Modélisation et commande de l'onduleur trois niveaux à structure NPC

Chapitre 3 : Stratégie de modulation vectorielle d'un onduleur à trois niveaux (SVM)

Chapitre 4 : Implémentation de la stratégie SVM sur un circuit FPGA

Enfin, nous terminerons ce mémoire par les principales conclusions et quelques perspectives.

## Chapitre 1

# Modélisation et commande de l'onduleur à deux niveaux

#### 1.1 Introduction

Dans le domaine industriel, les entraînements électriques requièrent de plus en plus des vitesses variables. À cet égard, les progrès réalisés en électronique de puissance ont permis le développement de nombreuses solutions permettant de piloter efficacement des moteurs en courant alternatif à vitesse variable. Parmi ces solutions, on distingue les onduleurs autonomes commandés par Modulation de Largeur d'Impulsion (MLI) [9].

Un onduleur est un convertisseur statique qui assure la conversion d'une source de tension continue en une tension alternative. Alimenté en tension continue, il modifie périodiquement les connexions entre l'entrée et la sortie afin de générer une tension alternative. Pour améliorer la qualité de la tension de sortie, plusieurs techniques de MLI ont été proposées dans la littérature [9].

Dans ce chapitre, nous nous intéressons à l'onduleur triphasé à deux niveaux commandé d'abord avec la stratégie pleine onde puis par la stratégie triangulo-sinusoïdale. Ce chapitre comprend d'abord la modélisation mathématique de l'onduleur, suivie de sa simulation sous le logiciel MATLAB. Enfin, les résultats de simulation sont présentés et analysés en détail .

#### 1.2 La structure de base de l'onduleur à deux niveaux

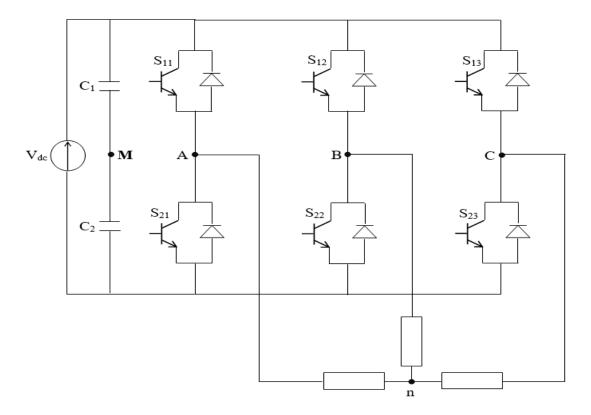

La Figure (1.1) présente la structure de base de l'onduleur à deux niveaux. Celui-ci est constitué de six interrupteurs bidirectionnels répartis en trois phases, ainsi que de deux condensateurs à l'entrée, alimentés par une même source de tension continue. Ces condensateurs permettent d'accéder au point milieu noté M.

Les interrupteurs appartenant au même bras ne doivent jamais conduire simultanément, afin de protéger la source de tension  $V_{dc}$ . Pour cela, la commande complémentaire du système doit être respectée.

La tension de sortie du convertisseur est obtenue par la **combinaison appropriée des états des interrupteurs**, ce qui permet de l'exprimer mathématiquement à l'aide de fonctions décrivant l'état de conduction des semi-conducteurs.

Figure 1.1 : Structure de base de l'onduleur à deux niveaux

#### 1.2.1 Fonctions de commutation

On note par  $S_{ij}$  les six interrupteurs de notre onduleur, tel qu'à chaque interrupteur  $S_{ij}$  est associée une fonction de commutation  $F_{ij}$  qui prend la valeur 0 ou 1 selon l'état de l'interrupteur (ouvert ou fermé), comme montré dans l'équation (1.1) [5].

$$F_{ij} = \begin{cases} 0 & \text{si } S_{ij} \text{ est ouvert} \\ 1 & \text{si } S_{ij} \text{ est ferm\'e} \end{cases}$$

(1.1)

Tel que:

- -i = 1 ou 2 représente l'interrupteur supérieur ou inférieur,

- j = 1, 2, 3 représente le bras.

- 1, 2, 3 représente le bras, Les deux interrupteurs supérieur et inférieur doivent être complémentaires, c'est-à-dire que lorsque l'un est fermé, l'autre doit impérativement être ouvert, conformément à la relation suivante :

$$F_{11} = \overline{F_{21}}$$

$F_{12} = \overline{F_{22}}$

$F_{13} = \overline{F_{23}}$

(1.2)

#### 1.2.2 Etats d'un bras de l'onduleur

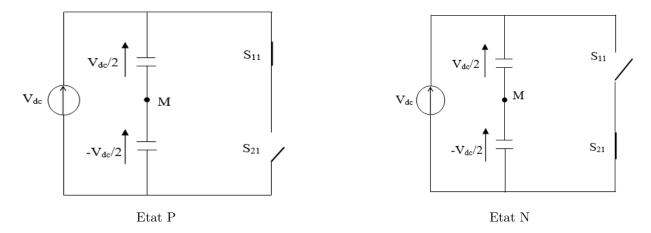

Le nom **deux niveaux** a été attribué à ce convertisseur en raison des deux niveaux de tension générés par chaque bras, correspondant à deux états physiquement réalisables du convertisseur.

L'un est symbolisé par la lettre  $\mathbf{P}$ , et l'autre par la lettre  $\mathbf{N}$ .

- État P: L'interrupteur supérieur  $S_{1j}$  (avec j=1,2,3) est fermé, tandis que l'interrupteur inférieur  $S_{2j}$  est ouvert. La tension de sortie par rapport au neutre de la source (n) est alors égale à  $+\frac{V_{dc}}{2}$ .

- État N : L'interrupteur inférieur  $S_{2j}$  (avec j=1,2,3) est fermé, tandis que l'interrupteur supérieur  $S_{1j}$  est ouvert. La tension de sortie par rapport au neutre de la source (n) est alors égale à  $-\frac{V_{dc}}{2}$ .

Ces deux états sont représentés dans la La Figure (1.2).

Figure 1.2 : Etats d'un bras de l'onduleur à deux niveaux.

On définit la tension de bras comme la tension entre les points A, B ou C et le point milieu M, situé entre les deux condensateurs  $C_1$  et  $C_2$ . Ces tensions sont notées  $V_{AM}$ ,  $V_{BM}$  et  $V_{CM}$ . Pour chaque état du bras, les états des interrupteurs et la tension de sortie sont résumée dans le tableau 1.1. On définit pour chaque bras (j) deux fonctions complémentaires, correspondantes aux deux états du bras :

| État du bras | $F_{1j}$ | $F_{2j}$ | $V_{KM}$            |

|--------------|----------|----------|---------------------|

| P            | 1        | 0        | $\frac{V_{dc}}{2}$  |

| N            | 0        | 1        | $-\frac{V_{dc}}{2}$ |

**Table 1.1:** Table d'excitation pour N=2

#### 1.2.3 Tensions de sortie

Les trois tensions du bras sont liées aux fonctions de commutation par les équations suivantes[1]:

$$V_{AM} = (F_{11} - F_{21}) \cdot \frac{V_{dc}}{2}$$

$$V_{BM} = (F_{12} - F_{22}) \cdot \frac{V_{dc}}{2}$$

$$V_{CM} = (F_{13} - F_{23}) \cdot \frac{V_{dc}}{2}$$

(1.3)

On définit par la **tension simple** la tension entre le point A, B ou C (les tensions générées par bras) et le neutre N, d'où les tensions simples sont notées :  $V_{AN}$ ,  $V_{BN}$ ,  $V_{CN}$ .

On définit par la **tension composée** la tension entre deux bras (line-to-line), notée  $U_{AB}$ ,  $U_{BC}$ ,  $U_{CA}$ . Ces trois tensions sont exprimées par les équations suivantes :

$$U_{AB} = V_{AM} - V_{BM} = V_{AN} - V_{BN}$$

$$U_{BC} = V_{BM} - V_{CM} = V_{BN} - V_{CN}$$

$$U_{CA} = V_{CM} - V_{AM} = V_{CN} - V_{AN}$$

(1.4)

Dans cette partie, on introduit les différentes équations mettant en relation les tensions de notre onduleur, ce qui permet de définir la relation entre la sortie et l'entrée.

Lorsque le système (la charge) est équilibré, c'est-à-dire  $Z_1 = Z_2 = Z_3 = R$ , on a :

$$V_{AM} + V_{BM} + V_{CM} = 0$$

$$V_{AN} + V_{BN} + V_{CN} = 0$$

$$U_{AB} + U_{BC} + U_{CA} = 0$$

(1.5)

Les tensions simples peuvent aussi être exprimées en fonction des tensions composées par les relations suivantes :

$$V_{AN} = \frac{U_{AB} - U_{CA}}{3}$$

$$V_{BN} = \frac{U_{BC} - U_{AB}}{3}$$

$$V_{CN} = \frac{U_{CA} - U_{BC}}{3}$$

(1.6)

D'où la forme matricielle des tensions simples :

$$\begin{bmatrix} V_{AN} \\ V_{BN} \\ V_{CN} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} U_{AB} - U_{CA} \\ U_{BC} - U_{AB} \\ U_{CA} - U_{BC} \end{bmatrix}$$

(1.7)

En introduisant les équations (1.4) dans (1.7), on obtient :

$$\begin{bmatrix} V_{AN} \\ V_{BN} \\ V_{CN} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} V_{AM} - V_{BM} - V_{CM} + V_{AM} \\ V_{BM} - V_{CM} - V_{AM} + V_{BM} \\ V_{CM} - V_{AM} - V_{BM} + V_{CM} \end{bmatrix}$$

(1.8)

$$\begin{bmatrix} V_{AN} \\ V_{BN} \\ V_{CN} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 2V_{AM} - V_{BM} - V_{CM} \\ -V_{AM} + 2V_{BM} - V_{CM} \\ -V_{AM} - V_{BM} + 2V_{CM} \end{bmatrix}$$

(1.9)

Les tensions simples sont donc exprimées en fonction des tensions des bras par :

$$\begin{bmatrix} V_{AN} \\ V_{BN} \\ V_{CN} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ -\frac{1}{2} & 1 & -\frac{1}{2} \\ -\frac{1}{2} & -\frac{1}{2} & 1 \end{bmatrix} \begin{bmatrix} V_{AM} \\ V_{BM} \\ V_{CM} \end{bmatrix}$$

(1.10)

Les courants d'entrée  $i_{d1}$  et  $i_{d2}$  de l'onduleur triphasé en fonction des courants  $i_a, i_b, i_c$  de la charge s'expriment en utilisant les fonctions de commutation des interrupteurs comme suit :

$$i_{d1} = F_{11}i_a + F_{12}i_b + F_{13}i_c$$

$$i_{d2} = F_{21}i_a + F_{22}i_b + F_{23}i_c$$

(1.11)

#### 1.3 Stratégies de commande

Les onduleurs de tension jouent un rôle central dans les systèmes de conversion d'énergie électrique, notamment dans les applications industrielles, les énergies renouvelables et l'alimentation des machines électriques. L'efficacité et les performances du convertisseur dépend en grande partie de la stratégie de commande mise en œuvre. Plusieurs techniques de commande ont été développées au fil des années pour répondre aux exigences croissantes en matière de rendement, de qualité spectrale et de contraintes de commutation. Parmi les plus répandues, on retrouve la commande triangulo-sinusoïdale (SPWM), la modulation vectorielle (SVM), ainsi que les stratégies à pleine onde. Chaque approche présente des avantages spécifiques en termes de complexité, de qualité du signal, de pertes de commutation et d'adaptabilité aux différentes topologies d'onduleur. Une analyse comparative de ces méthodes permet de mieux cerner leur pertinence selon les applications visées [10].

#### 1.3.1 La commande pleine onde

Dans les applications à vitesse variable, l'onduleur de tension fonctionne presque exclusivement selon la technique de Modulation de Largeur d'Impulsion (MLI) sur toute la plage opération-nelle. Ce convertisseur statique assure la modification simultanée de la fréquence et de l'amplitude des tensions électriques de sortie . Néanmoins, l'analyse technique du fonctionnement en mode pleine onde reste fondamentale, servant de référence et de point de comparaison pour l'étude approfondie des performances des stratégies MLI.

L'analyse de la méthode à pleine onde se concentre ici sur une charge électrique triphasée équilibrée, avec une configuration en étoile afin de simplifier l'approche. Cette stratégie offre plusieurs possibilités techniques de commande pleine onde, mais nos études portent principalement sur la commande dite de  $180^{\circ}$ .

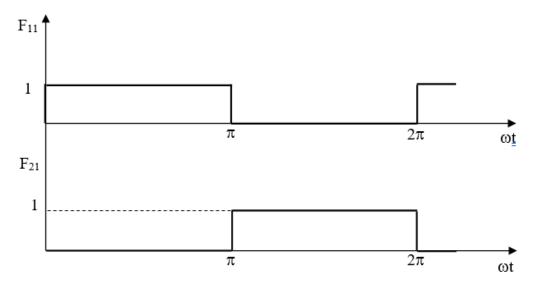

Dans son principe de fonctionnement, chaque interrupteur conduit pendant une durée correspondant exactement à une demi-période  $(\pi)$ , avec des séquences de commande décalées de 120° d'un bras par rapport aux autres.

Cette technique impose certaines conditions, comme le respect de la commande complémentaire pour éviter les courts-circuits. Elle génère ainsi six signaux de commande pour l'onduleur à deux niveaux, permettant la conversion du courant continu d'entrée en un système triphasé alternatif requis par la charge [10]

La figure (1.3) illustre la forme des signaux de commande des deux interrupteurs  $S_{11}$  et  $S_{21}$  avec la commande de 180°

Figure 1.3 : La forme des signaux de commande F11 et F21 pour l'onduleur à deux niveaux

#### 1.3.2 Résultats de simulation et interprétations

Quand la sortie d'un onduleur est coupée par alternance à chaque cycle complet, on dit que l'onduleur est en **mode de commande en pleine onde**. Dans ce type de fonctionnement, les interrupteurs alternent entre l'ouverture et la fermeture pendant la moitié de la période. Le convertisseur décrit dans les sections précédentes est simulé dans **MATLAB/Simulink** en utilisant une commande de **180 degrés**.

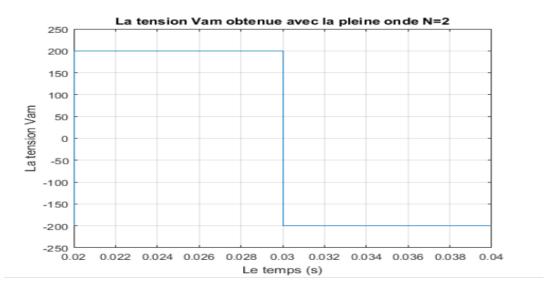

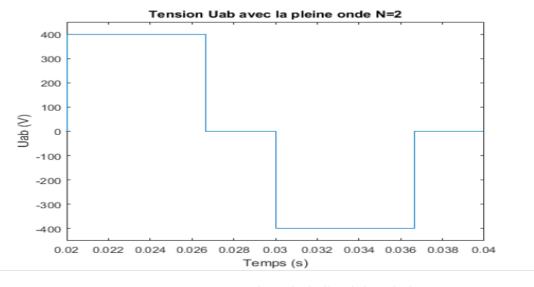

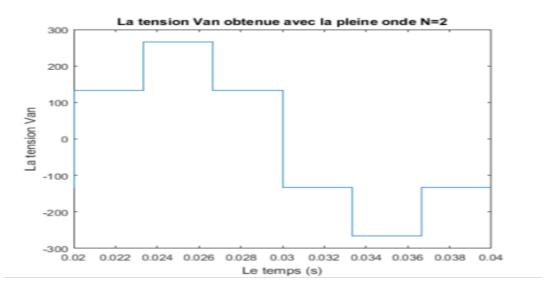

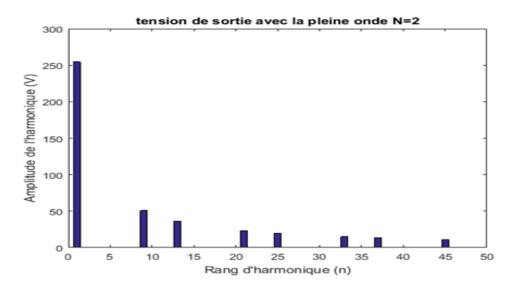

Les figures 1.4, 1.5, 1.6, 1.7, 1.8 présentent respectivement :

- les six signaux de commande de l'onduleur,

- la tension générée par bras  $V_{am}$ ,

- la tension composée  $U_{ab}$ ,

- la tension simple  $V_{an}$  avec son spectre d'harmonique.

On constate que les signaux de chaque bras sont complémentaires, et que chaque interrupteur est actif pendant 180°. La tension  $U_{ab}$  contient trois niveaux de tension  $(V_{dc}, 0 \text{ et } -V_{dc})$  de valeurs (400 V, 0 et -400 V). Sa tension efficace est de 282.8 V.

Lorsque l'onduleur est alimenté sous 400 V, les niveaux de tension  $\left(\frac{V_{dc}}{2}\right)$  et  $\left(-\frac{V_{dc}}{2}\right)$  sont clairement visibles sur les graphes de la tension du bras  $V_{am}$ .

Quant aux tensions simples qui alimentent la charge alternative équilibrée, elles sont affichées sur la figure 1.7. Ces signaux alternatifs se composent de quatre niveaux de tension :  $\frac{2V_{dc}}{3}$ ,  $\frac{V_{dc}}{3}$ ,  $-\frac{V_{dc}}{3}$  et  $-\frac{2V_{dc}}{3}$

correspondant respectivement à  $(400\,\mathrm{V},\,200\,\mathrm{V},\,-200\,\mathrm{V}$  et  $-400\,\mathrm{V})$  pour l'onduleur à deux niveaux.

La tension simple présente une tension efficace de 188.52 V, un **THD** de 28.81%, et une valeur efficace du fondamental de 180.02 V (figure 1.8).

Figure 1.4 : La forme des signaux de commande de F11 et F21 pour l'onduleur à deux niveaux

Figure 1.5 : La tension de sortie Vam de l'onduleur à deux niveaux

Figure 1.6 : La tension composée Uab de l'onduleur à deux niveaux

Figure 1.7: La tension simple Van

Figure 1.8 : Analyse harmonique de Van (V)

#### 1.3.3 La modulation de largeur d'impulsion (MLI)

La modulation de largeur d'impulsion (MLI) triangulo-sinusoïdale est considérée comme l'une des principales stratégies de commande parmi les différentes approches MLI existantes. Son principe repose sur la comparaison entre une référence de forme sinusoïdale et une porteuse de forme triangulaire à haute fréquence, permettant ainsi de déterminer avec précision les états de commutation de chaque semi-conducteur de l'onduleur [10].

Suite à cette comparaison, les états de chaque interrupteur sont déterminés selon un algorithme spécifique. Dans cette stratégie de commande, l'amplitude crête-à-crête de la porteuse triangulaire correspond à la tension du circuit intermédiaire  $V_{dc}$ . Pour maintenir un fonctionnement en régime de modulation linéaire, une condition essentielle doit être respectée : l'amplitude de la référence de tension  $V_{ref}$  doit impérativement rester inférieure au pic de la porteuse triangulaire  $V_p$ , ce qui s'exprime par la relation suivante :  $V_{ref} < V_p$ .

La commande MLI est caractérisée par deux paramètres fondamentaux :

• L'indice de modulation m, défini comme le rapport entre la fréquence de la porteuse  $f_p$  et la fréquence du signal de référence  $f_m$ :

$$m = \frac{f_p}{f_m} \tag{1.13}$$

• Le coefficient de réglage r, qui exprime le rapport entre l'amplitude de la référence  $A_m$  et celle de la porteuse  $A_p$ :

$$r = \frac{A_m}{A_p} \tag{1.14}$$

Pour assurer un fonctionnement linéaire de l'onduleur, la condition suivante doit être satisfaite :  $r \le 1$ .

#### 1.3.4 Résultats de simulation et interprétations

Le principe de la commande triangulo-sinusoïdale est appliqué à l'onduleur à deux niveaux.le convertisseur est alimenté sous 400V.

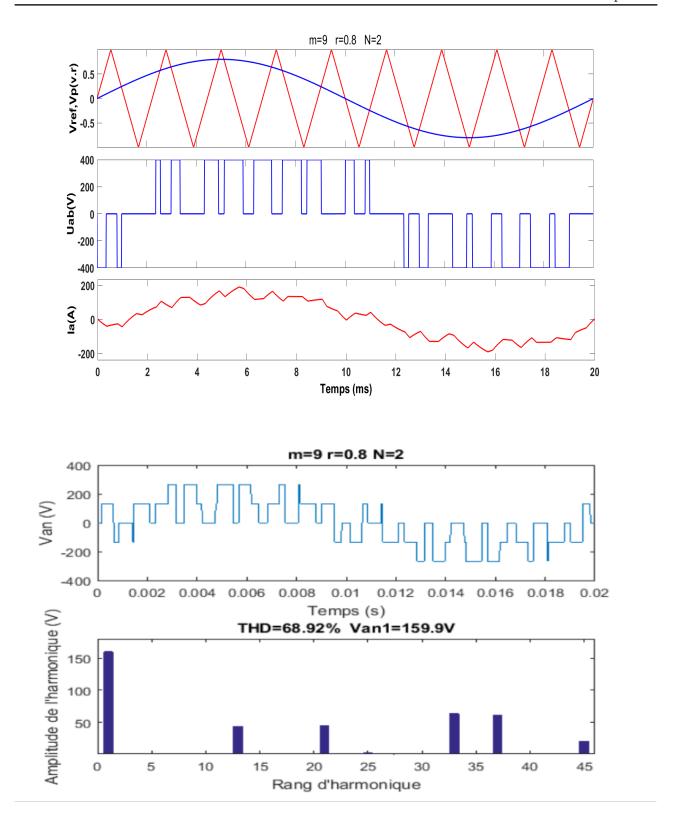

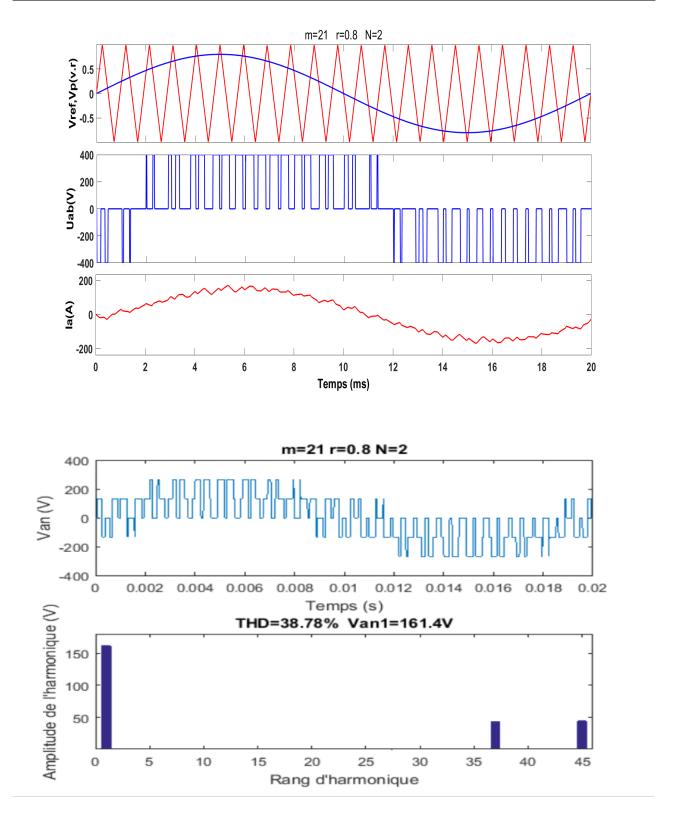

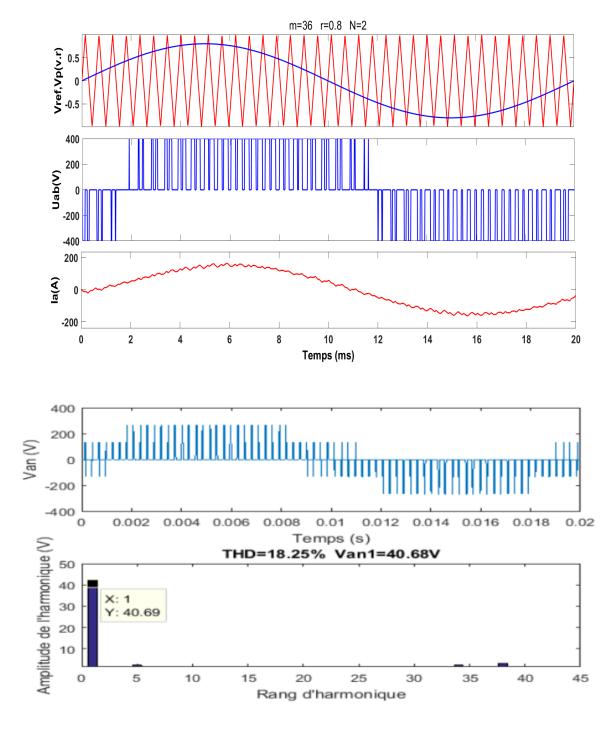

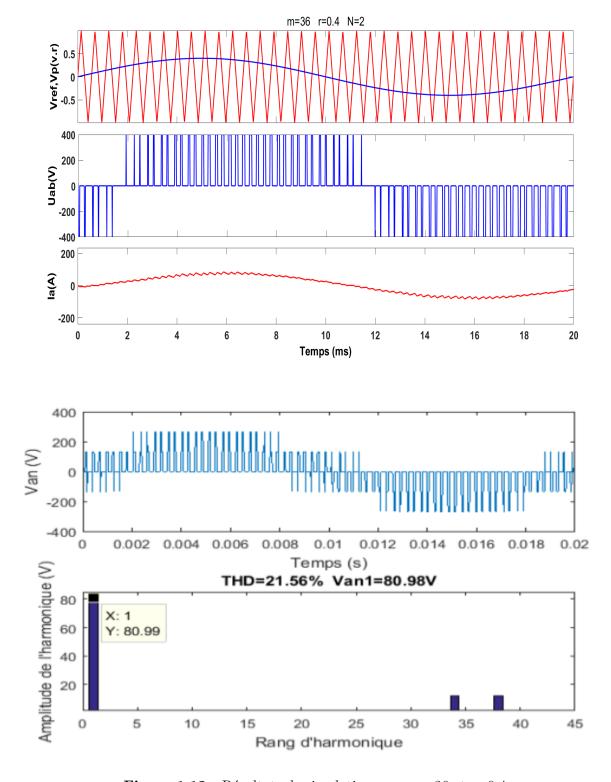

Les figures de 1.9 à 1.12 donnent la porteuse et la référence utilisée, la tension composée Uab, le courant  $\mathbf{Ia(t)}$  et la tension simple avec son spectre d'harmonique.

Les résultats de simulation sont obtenus pour des différentes valeurs de m et r pour l'effet de ces paramètres sur la qualité de la tension produite. L'analyse des résultats montre que :

- L'augmentation de l'indice de modulation pour l'onduleur à deux niveaux étudié permet de pousser les harmoniques vers les fréquences élevées ce qui facilite leur filtrage par la machine à courant alternatif.

- L'absence des harmoniques de rang trois et multiples de trois sont nuls.

- Le THD diminue quand l'indice de modulation m augmente.

- Pour un THD minimal on garde r légèrement en dessous de 1.

Figure 1.9 : Résultats de simulation pour m=9 et r=0.8

**Figure 1.10 :** Résultats de simulation pour m=21 et r=0.8

Figure 1.11 : Résultats de simulation pour m=36 et r=0.8

Figure 1.12 : Résultats de simulation pour m=36 et r=0.4

Figure 1.13 : Résultats de simulation pour m=36 et r=0.2

#### 1.4 Conclusion

Dans ce chapitre, nous avons étudié l'onduleur triphasé à deux niveaux. Nous avons commencé par détailler sa structure générale, puis son mode de fonctionnement, afin de déduire les équations nécessaires à sa modélisation. Les tensions du bras, les tensions simples, ainsi que les tensions composées ont été exprimées en fonction des fonctions de connexion, qui traduisent l'état de chaque interrupteur. Pour la commande du convertisseur, deux techniques distinctes ont été utilisée et analysées. La commande à pleine onde, puis la commande triangulo-sinusoïdale, dans laquelle une seule porteuse a été utilisée. Les équations développées ont été vérifiées par des simulations sous MATLAB, ce qui a permis de valider la cohérence de la modélisation théorique. Les résultats obtenus montrent un bon comportement dynamique et statique de l'onduleur, confirmant ainsi la pertinence des choix de modélisation et de commande.

Conclusion Page 26

## Chapitre 2

# Modélisation et commande de l'onduleur à trois niveaux

#### 2.1 Introduction

Dans le domaine industriel, les entraı̂nements électriques requièrent de plus en plus des vitesses variables. À cet égard, les progrès réalisés en électronique de puissance ont permis le développement de nombreuses solutions permettant de piloter efficacement des moteurs en courant alternatif à vitesse variable. Parmi ces solutions, on distingue les onduleurs autonomes commandés par Modulation de Largeur d'Impulsion (MLI) [9].

Un onduleur est un convertisseur statique qui assure la conversion d'une source de tension continue en une tension alternative. Alimenté en tension continue, il modifie périodiquement les connexions entre l'entrée et la sortie afin de générer une tension alternative. Pour améliorer la qualité de la tension de sortie, plusieurs techniques de MLI ont été proposées dans la littérature [9].

Dans ce chapitre, nous nous intéressons à l'onduleur triphasé à trois niveaux commandé d'abord avec la commande pleine onde puis par la commande triangulo-sinusoïdale. Ce chapitre comprend d'abord la modélisation mathématique de l'onduleur, suivie de sa simulation sous le logiciel MATLAB. Enfin, les résultats de simulation sont présentés et analysés en détail.

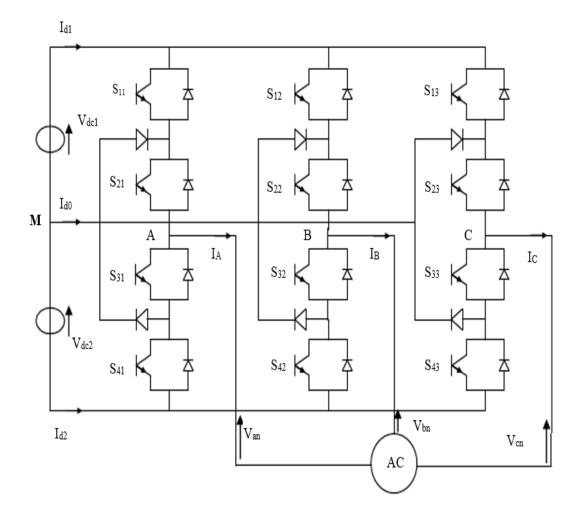

#### 2.2 La structure de base de l'onduleur à trois niveaux

L'onduleur à trois niveaux est composé de trois bras, comme illustré à la Figure 2.1. Chaque bras comprend quatre interrupteurs bidirectionnels, réalisés par l'association d'un transistor et d'une diode.

Afin d'éviter un court-circuit de la source continue à l'entrée de l'onduleur, ou l'ouverture de la charge alternative à la sortie, il est impératif d'empêcher la commutation simultanée (fermeture ou ouverture) des quatre interrupteurs d'un même bras.

Par ailleurs, on suppose que la tension d'entrée est répartie équitablement entre les deux capacités, soit :

$$V_{dc1} = V_{dc2} = \frac{V_{dc}}{2}$$

et en valeurs relatives :  $V_{dc1} = V_{dc2} = 1$

Figure 2.1 : Structure NPC de l'onduleur à trois niveaux [5].

#### 2.2.1 Fonctions de commutation

Pour chaque interrupteur  $S_{ij}$  (avec i=1,2,3,4 et j=1,2,3), on définit une fonction de commutation  $F_{ij}$  de la manière suivante :

$$F_{ij} = \begin{cases} 1 & \text{si } S_{ij} \text{ est ferm\'e} \\ 0 & \text{si } S_{ij} \text{ est ouvert} \end{cases}$$

(2.1)

Pour un onduleur donné, on définit également la fonction de connexion d'un demi-bras, notée  $F_{j1}^b$  pour le demi-bras supérieur et  $F_{j0}^b$  pour le demi-bras inférieur. La fonction  $F_{j1}^b$  vaut 1 seulement si tous les interrupteurs du demi-bras sont fermés et  $F_{j0}^b$  vaut 0 dans le cas où un des interrupteurs du demi-bras est ouvert [5].

#### 2.2.2 Etats d'un bras de l'onduleur

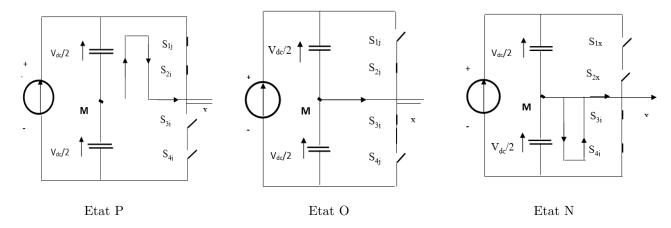

En mode commandable, chaque bras de l'onduleur possède trois états possibles (figure 2.2) :

- État P: Les deux interrupteurs du haut  $S_{1j}$  et  $S_{2j}$  (avec j=1,2 ou 3) sont fermés, tandis que les deux interrupteurs du bas  $S_{3j}$  et  $S_{4j}$  sont ouverts. La tension de sortie par rapport au neutre de la source (o) est  $\frac{V_{dc}}{2}$ .

- État O : Les deux interrupteurs du milieu  $S_{2j}$  et  $S_{3j}$  sont fermés, tandis que les interrupteurs des extrémités  $S_{1j}$  et  $S_{4j}$  sont ouverts. La tension de sortie par rapport au neutre est 0.

- État N : Les deux interrupteurs du bas  $S_{3j}$  et  $S_{4j}$  sont fermés, tandis que ceux du haut sont ouverts. La tension de sortie par rapport au neutre de la source (o) est  $-\frac{V_{dc}}{2}$ .

Pour chaque état du bras, les états des interrupteurs et la tension de sortie sont résumés dans le tableau 2.1.

On définit pour chaque bras j trois fonctions de connexion, correspondant aux trois états du bras.

Pour éviter, d'une part, la conduction simultanée des quatre interrupteurs d'un même bras, ce qui peut entraîner leur destruction par une croissance excessive du courant lors d'un court-circuit, et, d'autre part, l'ouverture simultanée de tous les interrupteurs d'un bras, pouvant produire une surtension, on définit alors la commande complémentaire optimale suivante [5]:

$$\begin{cases}

F_{1j} = \overline{F_{3j}} \\

F_{2j} = \overline{F_{4j}}

\end{cases}$$

(2.2)

où  $F_{1j}$  est la commande de base de l'interrupteur  $S_{1j}$  relative au bras j.

Ainsi, avec cette commande complémentaire, les fonctions de connexion des quatre interrupteurs du bras j sont liées par les relations suivantes :

$$F_{1j} = 1 - F_{3j}$$

et  $F_{2j} = 1 - F_{4j}$  (2.3)

Figure 2.2 : Etats d'un bras de l'onduleur à trois niveaux [1]

| État du bras | État d'interrupteurs du bras |          |          |          | Tension de sortie   |

|--------------|------------------------------|----------|----------|----------|---------------------|

|              | $F_{1j}$                     | $F_{2j}$ | $F_{3j}$ | $F_{4j}$ | $ m V_{KM}$         |

| Р            | 1                            | 1        | 0        | 0        | $\frac{V_{dc}}{2}$  |

| О            | 0                            | 1        | 1        | 0        | 0                   |

| N            | 0                            | 0        | 1        | 1        | $-\frac{V_{dc}}{2}$ |

Table 2.1 : Etats d'un bras de l'onduleur

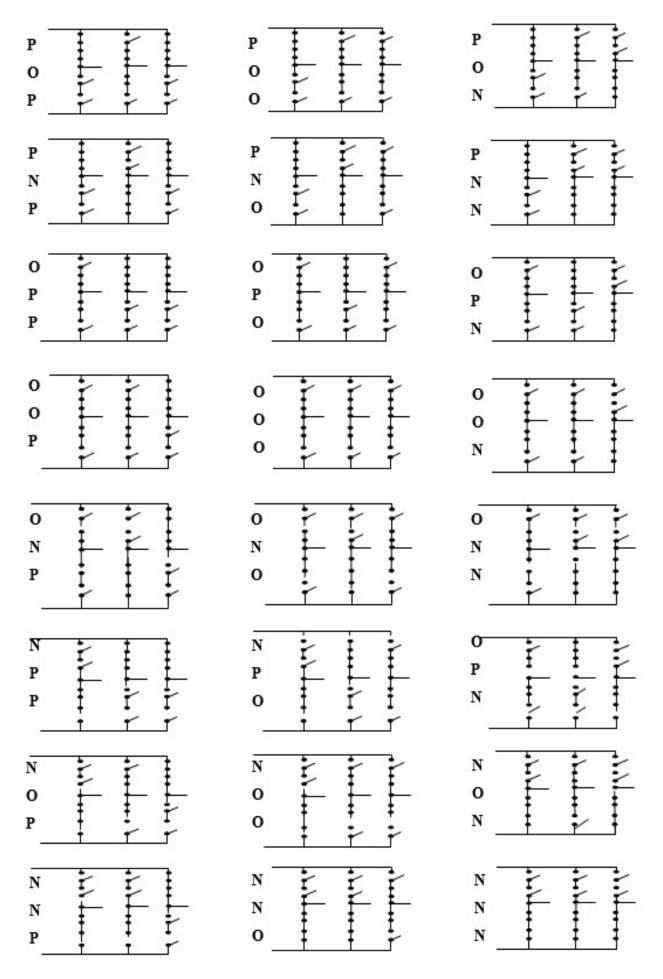

Chaque bras de l'onduleur peut prendre trois états. Ainsi, l'onduleur triphasé a  $3^3 = 27$  états possibles. Ces états sont identifiés en indiquant les états des trois bras. Par exemple, l'état **PON** indique que le premier bras est à l'état P, le deuxième à l'état Q, et le troisième à l'état Q. La figure 2.3 résume les états de l'onduleur triphasé à trois niveaux.

Figure 2.3 : Etats de l'onduleur [1].

#### 2.2.3 Tensions de sortie

Les fonctions de connexion des demi-bras pour N=3, s'expriment comme suit [5] :

$$\begin{cases} F_{j1}^b = F_{j1}F_{j2} \\ F_{j0}^b = F_{j3}F_{j4} \end{cases}$$

(2.4)

Le système d'équations (1.5) montre que la fonction de connexion du demi-bras  $F_{jm}^b$  vaut (1) dans le cas où les deux interrupteurs du demi-bras associés sont tous fermés, et nulle dans tous les autres cas. En utilisant les fonctions de connexion des interrupteurs, les potentiels des nœuds (A, B, C) de l'onduleur triphasé à trois niveaux par rapport au point milieu M de la source de tension d'entrée sont tels que :

$$\begin{cases} V_{AM} = F_{11}F_{21}V_{dc1} - F_{31}F_{41}V_{dc2} \\ V_{BM} = F_{12}F_{22}V_{dc1} - F_{32}F_{42}V_{dc2} \\ V_{CM} = F_{13}F_{23}V_{dc1} - F_{33}F_{43}V_{dc2} \end{cases}$$

(2.5)

En supposant que  $V_{dc} = V_{dc1} = V_{dc2}$ , Le système (2.5) devient :

$$\begin{cases} V_{AM} = (F_{11}F_{21} - F_{31}F_{41})V_{dc} \\ V_{BM} = (F_{12}F_{22} - F_{32}F_{42})V_{dc} \\ V_{CM} = (F_{13}F_{23} - F_{33}F_{43})V_{dc} \end{cases}$$

(2.6)

Le système (1.5) montre que l'onduleur à trois niveaux revient à une mise en série de deux onduleurs à deux niveaux, l'un est constitué pas les demi-bras du haut alimenté par  $(V_{dc1})$ , et l'autre est constitué par les demi-bras du bas et alimenté par  $(-V_{dc2})$  En introduisant les fonctions de connexion (2.4) dans me système (2.6), on obtient le système d'équation suivant[5]:

$$\begin{cases} V_{AM} = (F_{11}^b - F_{10}^b)V_{dc} \\ V_{BM} = (F_{21}^b - F_{20}^b)V_{dc} \\ V_{CM} = (F_{31}^b - F_{30}^b)V_{dc} \end{cases}$$

(2.7)

Les différentes tensions composées s'écrivent :

$$\begin{cases}

U_{AB} = V_{AM} - V_{BM} = (F_{11}F_{21} - F_{12}F_{22})V_{dc1} - (F_{31}F_{41} - F_{32}F_{42})V_{dc2} \\

U_{BC} = V_{BM} - V_{CM} = (F_{12}F_{22} - F_{13}F_{23})V_{dc1} - (F_{32}F_{42} - F_{33}F_{43})V_{dc2} \\

U_{CA} = V_{CM} - V_{AM} = (F_{13}F_{23} - F_{11}F_{21})V_{dc1} - (F_{33}F_{43} - F_{31}F_{41})V_{dc2}

\end{cases}$$

(2.8)

En introduisant les fonctions de connexion des demi-bras dans le système (2.8), on obtient l'équation matricielle suivante :

$$\begin{pmatrix} U_{AB} \\ U_{BC} \\ U_{CA} \end{pmatrix} = \begin{pmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \\ -1 & 0 & 1 \end{pmatrix} \begin{bmatrix} F_{11}^b \\ F_{21}^b \\ F_{31}^b \end{bmatrix} V_{dc1} - \begin{pmatrix} F_{10}^b \\ F_{20}^b \\ F_{30}^b \end{pmatrix} V_{dc2}$$

$$(2.9)$$

Pour  $V_{dc1} = V_{dc2} = V_{dc}$ , cette relation se réduit à :

$$\begin{pmatrix} U_{AB} \\ U_{BC} \\ U_{CA} \end{pmatrix} = \begin{pmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \\ -1 & 0 & 1 \end{pmatrix} \begin{pmatrix} F_{11}^b - F_{10}^b \\ F_{21}^b - F_{20}^b \\ F_{31}^b - F_{30}^b \end{pmatrix}$$

(2.10)

Les courants d'entrée  $i_{d1}$  et  $i_{d2}$  de l'onduleur triphasé en fonction des courants  $i_a$ ,  $i_b$  et  $i_c$  de la charge en utilisant les fonctions de connexion des interrupteurs s'expriment comme suit :

$$\begin{cases}

i_{d1} = F_{11}F_{21}i_a + F_{12}F_{22}i_b + F_{13}F_{23}i_c \\

i_{d2} = F_{31}F_{41}i_a + F_{32}F_{42}i_b + F_{33}F_{43}i_c

\end{cases}$$

(2.11)

En utilisant les fonctions de connexion des demi-bras, la relation (2.11) devient :

$$\begin{cases}

i_{d1} = F_{11}^b i_a + F_{21}^b i_b + F_{31}^b i_c \\

i_{d2} = F_{10}^b i_a + F_{20}^b i_b + F_{30}^b i_c

\end{cases}$$

(2.12)

Le courant  $i_{d0}$  est lié aux différents courants d'entrée et aux courants de charge par la relation suivante :

$$i_{d0} = i_a + i_b + i_c - i_{d1} - i_{d2} (2.14)$$

#### 2.3 Stratégies de commande

Afin de piloter les semi-conducteur de l'onduleur à trois niveaux, il est nécessaire de produire un signal carré dont les instants de commutation sont calculés selon une stratégie de commande donnée. Parmi les techniques existantes, nous nous intéressants à la génération de ces signaux par commande pleine onde puis la MLI triangulo-sinusoïdale.

#### 2.3.1 La commande pleine onde

Le principe de la commande pleine onde appliquée au convertisseur à trois niveaux est similaire à celui présenté dans le chapitre 1 sur l'onduleur à deux niveaux. En effet, tous les semi-conducteurs doivent fonctionner durant 180°, comme le montre la Figure 2.4. Certaines commandes sont déduites à partir du système (2.2), d'autres en assurant le déphasage de 120° nécessaire entre les phases, soit dans le cas des systèmes équilibrés, soit par le respect de la table de commande 2.1.

Le profil de la tension  $V_{am}$  adopté est présenté sur la Figure 2.4, accompagné des signaux de commande des interrupteurs supérieurs du bras 1.

Figure 2.4 : La forme des signaux de commande  $F_{11}$  et  $F_{21}$  pour l'onduleur à trois niveaux

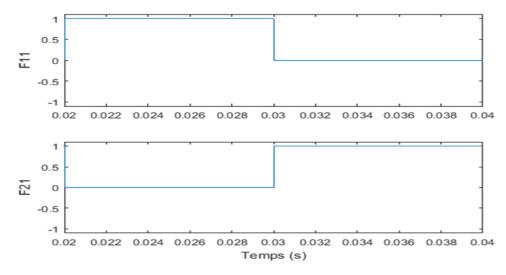

#### 2.3.2 Résultats de simulation et interprétations

La commande pleine onde appliquée à l'onduleur à trois niveaux nécessite la génération de six signaux de commande. Les Figures 2.5 et 2.6 présentent respectivement :

- la forme des signaux de commande  $F_{11}$  et  $F_{31}$  du premier bras de l'onduleur,

- la tension générée par le bras  $V_{AM}$ ,

- la tension composée  $U_{ab}$ ,

- la tension simple  $V_{an}$  accompagnée de son spectre d'harmoniques.

On constate que les signaux  $F_{11}$  et  $F_{31}$  sont complémentaires.

La tension  $U_{ab}$  présente trois niveaux :  $\frac{V_{dc}}{2}$ , 0, et  $-\frac{V_{dc}}{2}$ , correspondant à des valeurs de 200 V, 0 V, et -200 V. Sa valeur efficace est de 141,31 V.

Lorsque l'onduleur est alimenté sous une tension continue de 400 V, les niveaux de tension  $\frac{V_{dc}}{2}$  et  $-\frac{V_{dc}}{2}$  apparaissent clairement sur la tension du bras  $V_{AM}$ .

Quant à la tension simple appliquée à la charge alternative équilibrée, elle est représentée sur la Figure 2.6. Elle présente une tension efficace de 94,24 V, un taux de distorsion harmonique (THD) de 29,38%, et une valeur efficace de la composante fondamentale de 89,8 V.

Figure 2.5 : La forme des signaux de commande des interrepteurs de premier bras pour l'onduleur à trois niveaux

Figure 2.6 : Résultats de fonctionnement de l'onduleur à 3 niveaux avec la commande pleine onde.

## 2.3.3 La modulation de largeur d'impulsion (MLI)

Le principe de cette stratégie repose sur la comparaison d'un signal sinusoïdal de référence avec deux signaux porteurs triangulaires. Dans notre cas, les signaux triangulaires sont de forme unipolaire, comme illustré dans la figure 2.7. La comparaison entre les trois signaux de référence permet de générer les signaux de commande pour les trois bras de l'onduleur [10]. La commande MLI est caractérisée par deux paramètres fondamentaux :

• L'indice de modulation m, défini comme le rapport entre la fréquence de la porteuse  $f_p$  et la fréquence du signal de référence  $f_m$ :

$$m = \frac{f_p}{f_m} \tag{1.13}$$

• Le coefficient de réglage r, qui exprime le rapport entre l'amplitude de la référence  $A_m$  et celle de la porteuse  $A_p$ :

$$r = \frac{A_m}{A_p} \tag{1.14}$$

Pour assurer un fonctionnement linéaire de l'onduleur, la condition suivante doit être satisfaite :  $r \le 1$ .

Figure 2.7 : Signaux de référence et porteuses triangulaires

## 2.3.4 Résultats de simulation et interprétations

La simulation de la MLI triangulo-sinusoïdale a été réalisée par Simulink. Deux porteuses sont générées d'amplitude  $V_p$  et trois références sinusoïdales décalées entre elles de 120°. La fréquence des porteuses dépend du paramètre m tandis que l'amplitude maximale  $V_{\rm max}$  des trois références est contrôlée par le paramètre r. L'onduleur est alimenté par une tension continue  $V_{\rm dc}$  égale à  $400\,{\rm V}$ .

Les résultats sont obtenus pour différentes valeurs de l'indice de modulation m et de le coefficient de réglage r. Pour une meilleure analyse, nous avons fixé d'abord m à 36 et fait varier r (0.2, 0.4 et 0.8). Ensuite, nous avons maintenu r=0.8 et fait varier m (36, 21 et 9).

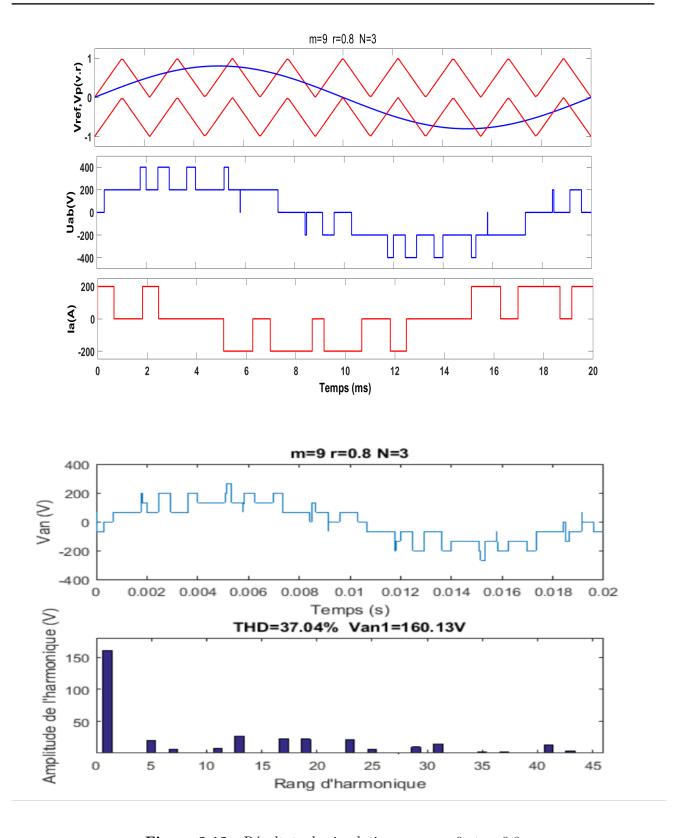

Les figures de 2.8 à 2.12 montrent les porteuses utilisées avec les trois tensions de référence et la tension simple  $V_{an}$  accompagnée de son spectre d'harmoniques.

D'après les résultats, nous avons observé que lorsque l'indice de modulation augmente, la tension efficace de la fondamentale croît également. Pour les trois valeurs de  $r:0.2,\,0.4$  et  $0.8,\,$  la valeur de la fondamentale est respectivement égale à  $40.32\,\mathrm{V},\,80.31\,\mathrm{V}$  et  $160.01\,\mathrm{V}$ . Cela confirme la relation directe entre l'indice de modulation et l'amplitude de la composante fondamentale dans le spectre de sortie, comme indiqué dans l'équation (2.15).

De plus, l'augmentation de m de 9 à 21 puis 36 a pour effet de repousser les harmoniques vers les hautes fréquences. Cela facilite grandement leur filtrage, car les filtres passe-bas deviennent plus efficaces lorsque les harmoniques indésirables sont éloignées de la fréquence fondamentale. Par ailleurs, la valeur du THD diminue considérablement avec l'augmentation de m et m, ce qui a été observé pour un indice de modulation de 36 et un taux de modulation égal à m0.8 le THD décroît jusqu'à m17.68 % (Fig. 2.10).

Figure 2.8 : Résultats de simulation pour m=36 et r=0.2

Figure 2.9 : Résultats de simulation pour m=36 et r=0.4

Figure 2.10 : Résultats de simulation pour m=36 et r=0.8

Figure 2.11 : Résultats de simulation pour m=21 et r=0.8

**Figure 2.12 :** Résultats de simulation pour m=9 et r=0.8

## 2.4 Conclusion

Dans ce chapitre, nous avons présenté en détail les équations mathématiques décrivant le fonctionnement d'un onduleur triphasé à trois niveaux de type NPC, après en avoir introduit la structure de base. Deux stratégies de commande ont été étudiées et simulées : la commande pleine onde et la modulation triangulo-sinusoïdale utilisant deux porteuses unipolaires. Les simulations effectuées sous MATLAB confirment que, dans les deux cas, les niveaux de tension sont correctement générés, aussi bien pour les tensions (Vam, Uab, Van), respectant ainsi le principe de fonctionnement attendu du convertisseur.

La modulation triangulaire, en particulier, présente un avantage notable en offrant un degré de liberté supplémentaire qui permet d'ajuster la valeur efficace de la tension de sortie, améliorant significativement son spectre. La variation de l'indice de modulation influe directement sur la valeur efficace de la tension , tandis que l'augmentation du taux de modulation entraîne une réduction marquée du THD (Total Harmonic Distortion), avec une diminution de plus de 52

En conclusion, la modulation de largeur d'impulsion permet un contrôle efficace de la tension de sortie tant sur le plan de sa valeur efficace que de sa qualité spectrale, notamment en ce qui concerne la réduction du THD.

Conclusion Page 42

## Chapitre 3

# Stratégie de modulation vectorielle d'un onduleur à trois niveaux (SVM)

## 3.1 Introduction

Les convertisseurs multiniveaux sont aujourd'hui largement répandus dans les systèmes de conversion d'énergie, en particulier dans les applications à moyenne et haute tension. Leur principal avantage réside dans leur capacité à générer des formes d'onde plus proches d'une sinusoïde idéale, ce qui permet de réduire significativement les pertes de commutation, les contraintes sur les composants électroniques et les interférences électromagnétiques. Cette amélioration de la qualité de l'énergie permet d'augmenter le rendement global du système tout en prolongeant la durée de vie des équipements[5].

En parallèle à l'essor de ces structures, plusieurs méthodes de commande ont vu le jour, notamment les techniques de modulation de largeur d'impulsion (PWM). Ces méthodes permettent de gérer précisément les états des interrupteurs de l'onduleur afin de synthétiser la tension de sortie désirée. Parmi les techniques les plus connues, on retrouve la modulation par signaux porteurs, le contrôle par hystérésis et l'élimination sélective des harmoniques.

Parmi ces approches, la modulation par vecteur spatial (Space Vector Modulation – SVM) s'impose comme l'une des plus efficaces et les plus utilisées. Contrairement aux méthodes classiques basées uniquement sur des signaux de référence, la SVM prend en compte l'état global du vecteur tension dans le plan  $(\alpha, \beta)$ , ce qui permet une commande plus fine de l'onduleur. Cette technique présente plusieurs avantages notables :

- Une réduction importante des harmoniques dans les tensions et les courants de sortie, améliorant ainsi la qualité de l'énergie;

- Une meilleure exploitation de la tension disponible sur le bus continu, ce qui augmente l'amplitude maximale de la tension de sortie;

- Une mise en œuvre numérique relativement simple, ce qui facilite son intégration dans des microcontrôleurs, DSP ou FPGA utilisés dans les systèmes embarqués [9].

# 3.2 Principe général de la modulation par vecteur spatial (SVM)

La modulation par vecteur spatial (SVM) est une technique discrète de commande dans laquelle un vecteur de référence échantillonné, noté  $v^*$ , est reproduit par la moyenne temporelle pondérée de plusieurs vecteurs de commutation choisis de manière appropriée. Cette méthode permet une synthèse efficace de la tension de sortie à partir des états de commutation disponibles.

La stratégie SVM repose généralement sur trois étapes fondamentales :

- 1. **Détermination de la position du vecteur de référence** : identification du secteur et de la région dans lesquels se situe le vecteur  $v^*$  dans le plan de Clarke  $(\alpha, \beta)$ .

- 2. Calcul des durées d'activation : évaluation des temps pendant lesquels les vecteurs de commutation sélectionnés doivent être appliqués pour approcher au mieux  $v^*$ .

- 3. **Génération des signaux de commande** : production des impulsions logiques destinées à piloter les interrupteurs de l'onduleur en fonction des temps calculés.

Les tensions de référence sont généralement des tensions triphasées équilibrées, données par le système suivant :

$$v_a^* = V_m \sin(\omega t)$$

$$v_b^* = V_m \sin\left(\omega t - \frac{2\pi}{3}\right)$$

$$v_c^* = V_m \sin\left(\omega t + \frac{2\pi}{3}\right)$$

(3.1)

où  $\omega = 2\pi f$  est la pulsation angulaire, et  $V_m$  représente l'amplitude des tensions de phase.

Les tensions triphasées  $v_a^*$ ,  $v_b^*$  et  $v_c^*$  peuvent être transformées en un vecteur bidimensionnel dans le plan  $(\alpha, \beta)$  à l'aide de la transformation de Clarke [1] :

$$\begin{bmatrix} v_{\alpha}^* \\ v_{\beta}^* \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} v_a^* \\ v_b^* \\ v_c^* \end{bmatrix}$$

(3.2)

Cette transformation permet de représenter les tensions dans un plan orthogonal simplifiant l'analyse et la synthèse dans la méthode SVM.

La projection des tensions triphasées de référence dans le plan  $\alpha\beta$  donne naissance à un vecteur appelé **vecteur de tension de référence**, défini comme :

$$\vec{v}_s^* = \begin{bmatrix} v_\alpha^* & v_\beta^* \end{bmatrix}^T \tag{3.3}$$

Ce vecteur tourne dans le plan  $\alpha\beta$ , dans le sens antihoraire, à une fréquence angulaire  $\omega$ .

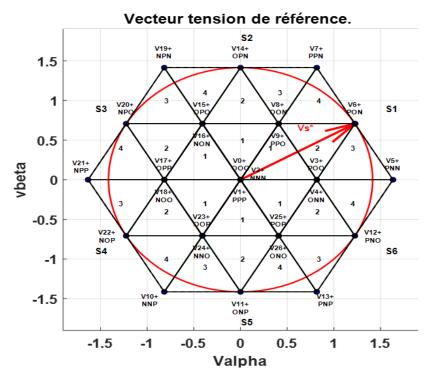

Figure 3.1 : Vecteur tension de référence.

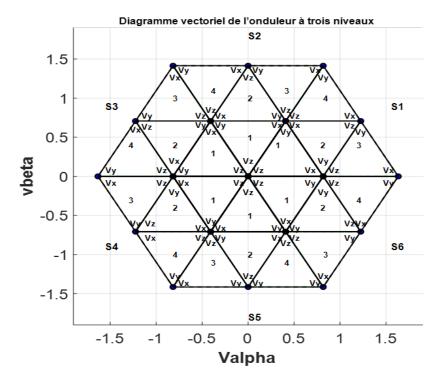

### 3.2.1 Vecteur tension de sortie et diagramme vectoriel

À partir des états de commutation triphasés  $S_a$ ,  $S_b$  et  $S_c$ , on peut définir le vecteur de tension de référence  $\vec{v}_s^*$  dans le plan complexe comme suit[1]:

$$\vec{v}_s^* = S_a + S_b \cdot e^{j\frac{2\pi}{3}} + S_c \cdot e^{j\frac{4\pi}{3}} \tag{3.4}$$

Ces positions sont représentées sur le diagramme vectoriel de l'onduleur (comme montre la figure 3.1) Elles sont organisées suivant deux hexagones concentriques :

- **Hexagone externe**: il comporte douze positions correspondant aux états suivants: PNN, PON, PPN, OPN, NPO, NPP, NOP, NNP, ONP, PNP et PNO.

- **Hexagone interne**: il contient six positions correspondant aux paires d'états redondants suivantes: (POO-ONN), (PPO-OON), (OPO-NON), (OPP-NOO), (OOP-NNO) et (POP-ONO).

- Enfin, **une position centrale** à l'origine du diagramme correspond aux états PPP, 000 et NNN.

Chaque position de l'hexagone interne est obtenue à partir de deux états distincts, appelés états redondants, et les vecteurs correspondants sont désignés comme vecteurs redondants. Le diagramme vectoriel est divisé en six secteurs triangulaires, chacun délimité par l'origine et deux sommets consécutifs de l'hexagone externe. Chaque secteur est ensuite subdivisé en quatre régions élémentaires, formant ainsi un total de 24 régions distinctes dans le diagramme vectoriel.

À partir des tensions de référence triphasées  $v_a^*$ ,  $v_b^*$  et  $v_c^*$ , le vecteur de tension de référence est défini par :

$$v_s^* = \frac{2}{3} \left( v_a^* e^{j0} + v_b^* e^{-j\frac{2\pi}{3}} + v_c^* e^{j\frac{2\pi}{3}} \right)$$

(3.5)

Ce vecteur peut également s'exprimer sous forme complexe dans le plan  $(\alpha, \beta)$ :

$$v_s^* = v_\alpha^* + j v_\beta^* \tag{3.6}$$

où  $(\alpha, \beta)$  représentent respectivement les composantes directe et quadrature du vecteur  $v_s^*$  dans le plan  $(\alpha, \beta)$ .

Par ailleurs, on peut également exprimer ce vecteur sous forme polaire :

$$v_s^* = mV_{\text{max}} \cdot e^{j\theta} \tag{3.7}$$

où  $V_{\max}$  est l'amplitude maximale .

- m: taux de modulation  $(0 \le m \le 1)$ ;

- $\theta$ : position angulaire du vecteur  $\vec{v_s}$ .

#### 3.2.2 Détermination du secteur

Où  $V_{\text{max}}$  représente l'amplitude maximale du vecteur de tension dans le plan  $(\alpha, \beta)$ , et  $\theta$  est la position angulaire du vecteur. à partir des coordonnées  $v_{\alpha}^*$ ,  $v_{\beta}^*$  et de la position angulaire  $\theta$ , on peut déterminer dans quel secteur s et dans quelle région r se situe le vecteur  $v_s^*$  dans le plan  $(\alpha, \beta)$ .

Le secteur est déterminé de la manière suivante[1] :

$$s = \begin{cases} 1 & \text{si } 0 \le \theta < \frac{\pi}{3} \\ 2 & \text{si } \frac{\pi}{3} \le \theta < \frac{2\pi}{3} \\ 3 & \text{si } \frac{2\pi}{3} \le \theta < \pi \\ 4 & \text{si } \pi \le \theta < \frac{4\pi}{3} \\ 5 & \text{si } \frac{4\pi}{3} \le \theta < \frac{5\pi}{3} \\ 6 & \text{si } \frac{5\pi}{3} \le \theta < 2\pi \end{cases}$$

En fonction de la position angulaire  $\theta$ , le vecteur se trouve dans l'un de ces secteurs du plan  $(\alpha, \beta)$ .

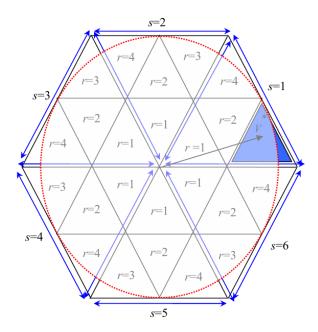

## 3.2.3 Détermination de la région

La région à l'intérieur de chaque secteur est déterminée à partir des équations des trois droites qui délimitent ses frontières. Comme illustré dans la figure 3.2, la région 1 est délimitée par les deux bords adjacents du secteur lui-même et par une droite supplémentaire propre à cette région.

Pour les régions 3 et 4, l'une des frontières est toujours définie par l'une des deux limites du secteur, tandis que l'autre frontière est constituée par le périmètre extérieur de l'hexagone vectoriel. La troisième frontière des régions 1, 2 et 4 est définie par des équations spécifiques aux géométries de ces régions.

Ainsi, après avoir identifié les régions 1, 2 et 4 à l'aide de leurs délimitations respectives, la portion restante de chaque secteur est automatiquement attribuée à la région 3[2].

Figure 3.2 : Secteurs et régions du diagramme vectoriel [1].

## 3.2.4 Définition de la période d'échantillonnage dans la MLI vectorielle

La période d'échantillonnage  $T_s$  représente un sous-multiple de la période T des tensions de référence  $v_a^*$ ,  $v_b^*$  et  $v_c^*$ . Sur le diagramme vectoriel, cette période correspond à un intervalle angulaire de largeur  $\frac{2\pi T_s}{T}$ , appelé intervalle d'échantillonnage.

La fréquence d'échantillonnage  $\frac{1}{T_s}$  est généralement beaucoup plus élevée que la fréquence de la tension et du courant de sortie  $\frac{1}{T}$ . Une fréquence de commutation élevée permet d'améliorer la qualité de la tension de sortie de l'onduleur en réduisant la distorsion harmonique. Toutefois, une augmentation excessive de cette fréquence entraîne des pertes supplémentaires dans les interrupteurs de l'onduleur. Ainsi, un compromis est nécessaire entre la qualité de la tension de sortie et les pertes de commutation dans les interrupteurs [11].

## 3.2.5 Séquence des états de l'onduleur

Au cours de chaque période d'échantillonnage  $T_s$ , le vecteur de tension de référence  $v_s^*$  doit être égal à la moyenne pondérée de trois vecteurs d'état  $v_x$ ,  $v_y$ , et  $v_z$ , correspondant aux sommets du triangle à l'intérieur duquel se trouve  $v_s^*$  dans le plan  $(\alpha, \beta)$

. Cette relation s'écrit[1] :

$$v_s^* = MV_{\text{max}}e^{j\alpha} = \frac{T_x v_x + T_y v_y + T_z v_z}{T_s} = d_x v_x + d_y v_y + d_z v_z$$

(3.8)

où  $T_x$ ,  $T_y$  et  $T_z$  représentent les durées d'application respectives de chaque vecteur d'état au cours de la période  $T_s$ , vérifiant la contrainte :

$$T_x + T_y + T_z = T_s$$

ou encore  $d_x + d_y + d_z = 1$  (3.9)

La position angulaire du vecteur  $v_s^*$  à l'intérieur d'un secteur est définie par :

$$\alpha = [0, 60^{\circ}]$$

Les vecteurs  $v_x$ ,  $v_y$  et  $v_z$  dépendent de la position du vecteur  $\vec{v}_s^*$  dans le diagramme vectoriel, c'est-à-dire du secteur et de la région considérés. Par exemple, lorsque  $v_s^*$  est situé dans la région r=3 du secteur s=1, on a :

- $v_x$ : vecteur correspondant à l'état PNN (état X),

- $v_y$ : vecteur correspondant à l'état PON (état Y),

- $v_z$  : vecteur correspondant à l'état POO (état  $Z_1$ ) ou ONN (état  $Z_2$ ).

Figure 3.3 : Etats X, Y et Z pour les différentes régions du diagramme vectoriel.

La correspondance entre les vecteurs X, Y, et Z avec les états de l'onduleur varie en fonction des secteurs et des régions, comme illustré dans la figure 3.3.

L'équation (3.9) et la décomposition de l'équation (3.8) suivant les deux axes  $(\alpha, \beta)$  permettent de déduire les rapports  $d_x$ ,  $d_y$ ,  $d_z$ , et par suite les durées  $T_x$ ,  $T_y$ ,  $T_z$ . Le tableau (3.1) donne la décomposition de l'équation (3.8) pour les quatre régions d'un secteur donné. Cette décomposition s'applique pour tous les secteurs du diagramme vectoriel : pour passer d'un secteur à l'autre, il suffit de positionner l'axe  $\alpha$  sur le début du secteur concerné.

| Région | Décomposition                                                                                                                                                                                         |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r = 1  | $\begin{cases} \frac{\sqrt{3}}{2}m\cos\theta = \frac{1}{2}d_x + \frac{1}{4}d_y \\ \frac{\sqrt{3}}{2}m\sin\theta = \frac{\sqrt{3}}{4}d_y \end{cases}$                                                  |

| r=2    | $\begin{cases} \frac{\sqrt{3}}{2}m\cos\theta = \frac{1}{4}d_x + \frac{1}{2}d_y + \frac{3}{4}d_z \\ \frac{\sqrt{3}}{2}m\sin\theta = \frac{\sqrt{3}}{4}(d_x + d_z) \end{cases}$                         |

| r=3    | $\begin{cases} \frac{\sqrt{3}}{2}m\cos\theta = d_x + \frac{3}{4}d_y + \frac{1}{2}d_z \\ \frac{\sqrt{3}}{2}m\sin\theta = \frac{\sqrt{3}}{4}d_y \end{cases}$                                            |

| r=4    | $\begin{cases} \frac{\sqrt{3}}{2}m\cos\theta = \frac{3}{4}d_x + \frac{1}{2}d_y + \frac{1}{4}d_z \\ \frac{\sqrt{3}}{2}m\sin\theta = \frac{\sqrt{3}}{4}(d_x + d_z) + \frac{\sqrt{3}}{2}d_y \end{cases}$ |

**Table 3.1**: Décomposition par région pour la SVM d'un onduleur à trois niveaux[1].

La résolution du système formé par l'équation  $T_x + T_y + T_z = T_s$  et par les deux équations issues de la décomposition du vecteur de référence permet d'obtenir les expressions des durées d'application  $T_x$ ,  $T_y$  et  $T_z$  selon la position du vecteur  $\vec{v}_s^*$  dans le plan  $(\alpha, \beta)$ . Ces expressions dépendent du secteur et de la région dans lesquels se situe le vecteur de référence.

| Région | $T_x$                                                    | $T_y$                        | $T_z$             |

|--------|----------------------------------------------------------|------------------------------|-------------------|

| 1      | $2T_s m \sin\left(\frac{\pi}{3} - \theta\right)$         | $2T_s m \sin(\theta)$        | $T_s - T_x - T_y$ |

| 2      | $T_s - 2 m T_s \sin\left(\frac{\pi}{3} - \theta\right)$  | $T_s - 2 m T_s \sin(\theta)$ | $T_s - T_x - T_y$ |

| 3      | $-T_s + 2 m T_s \sin\left(\frac{\pi}{3} - \theta\right)$ | $2T_s m \sin(\theta)$        | $T_s - T_x - T_y$ |

| 4      | $2 m T_s \sin\left(\frac{\pi}{3} - \theta\right)$        | $-T_s + 2T_s m \sin(\theta)$ | $T_s - T_x - T_y$ |

**Table 3.2 :** Temps de commutation  $T_x$ ,  $T_y$  et  $T_z$  pour chaque région du SVM d'un onduleur à trois niveaux[2].

Ainsi, pour obtenir des tensions de sortie triphasées sinusoïdales aussi proches que possible des valeurs de référence souhaitées, on applique successivement différents états de l'onduleur pendant des durées bien déterminées au cours de chaque période d'échantillonnage.

L'état X est appliqué pendant un certain temps, suivi de l'état Y, puis de l'état Z pour compléter la période. Ces états peuvent correspondre à plusieurs combinaisons appelées états redondants, qui produisent la même tension de sortie. Le choix entre ces redondances peut être effectué selon plusieurs critères :

Minimiser les pertes de puissance de l'onduleur en réduisant le nombre de commutations par période; • Équilibrer les tensions aux bornes des condensateurs sur le côté continu de l'onduleur, car ceux-ci se chargent et se déchargent en fonction des états appliqués.

Afin de limiter les pertes et de réduire les harmoniques de la tension de sortie, on adopte une séquence particulière d'application des états X, Y et Z:

- Appliquer les trois états dans un ordre déterminé pendant la première moitié de la période d'échantillonnage, puis dans l'ordre inverse pendant la seconde moitié;

- Répartir équitablement le temps d'application entre les redondances disponibles;

- Appliquer le même état au début et à la fin de chaque période d'échantillonnage.

- Inverser l'ordre de succession des états à chaque changement de secteur.

Le tableau 3.3 résume les séquences d'états appliquées pendant une demi-période pour les différentes régions du diagramme vectoriel. Lors de la seconde moitié de la période, cette séquence est répétée en ordre inverse.

| Secteur |   |   | Ré | gior | 1 1 |   |   |   | Ré | gior | 1 2 |   |   | Régi | ion 3 |   |   | Régi | ion 4 |   |

|---------|---|---|----|------|-----|---|---|---|----|------|-----|---|---|------|-------|---|---|------|-------|---|

| 1       | N | 0 | 0  | 0    | P   | P | P | 0 | 0  | P    | P   | P | O | P    | P     | P | 0 | P    | P     | P |

|         | N | N | 0  | 0    | O   | P | P | N | 0  | O    | O   | P | N | N    | O     | O | 0 | O    | P     | P |

|         | N | N | N  | 0    | O   | O | P | N | N  | N    | O   | O | N | N    | N     | O | N | N    | N     | O |

| 2       | P | P | O  | 0    | 0   | N | N | P | O  | O    | 0   | N | P | P    | O     | 0 | O | O    | N     | N |

|         | P | P | P  | 0    | 0   | O | N | P | P  | P    | 0   | O | P | P    | P     | 0 | P | P    | P     | O |

|         | P | O | O  | 0    | N   | N | N | O | O  | N    | N   | N | O | N    | N     | N | O | N    | N     | N |

| 3       | N | N | N  | 0    | O   | O | P | N | N  | N    | O   | O | N | N    | N     | O | N | N    | N     | O |

|         | N | O | 0  | 0    | P   | P | P | O | O  | P    | P   | P | O | P    | P     | P | 0 | P    | P     | P |

|         | N | N | 0  | 0    | O   | P | P | N | O  | O    | O   | P | N | N    | O     | O | 0 | O    | P     | P |

| 4       | P | O | O  | 0    | N   | N | N | O | O  | N    | N   | N | O | N    | N     | N | O | N    | N     | N |

|         | P | P | O  | 0    | O   | N | N | P | O  | O    | O   | N | P | P    | O     | 0 | O | O    | N     | N |

|         | P | P | P  | 0    | O   | O | N | P | P  | P    | O   | O | P | P    | P     | 0 | P | P    | P     | O |

| 5       | N | N | 0  | 0    | 0   | P | P | N | 0  | O    | O   | P | N | N    | O     | 0 | 0 | O    | P     | P |

|         | N | N | N  | 0    | 0   | O | P | N | N  | N    | O   | O | N | N    | N     | 0 | N | N    | N     | O |

|         | N | O | 0  | 0    | P   | P | P | O | 0  | P    | P   | P | O | P    | P     | P | 0 | P    | P     | P |

| 6       | P | P | P  | 0    | 0   | O | N | P | P  | P    | 0   | O | P | P    | P     | 0 | P | P    | P     | O |

|         | P | O | O  | 0    | N   | N | N | O | O  | N    | N   | N | O | N    | N     | N | O | N    | N     | N |

|         | P | P | O  | 0    | 0   | N | N | P | O  | O    | 0   | N | P | P    | O     | 0 | O | O    | N     | N |

Table 3.3 : Séquences des états dans les différentes régions du diagramme vectoriel [2].

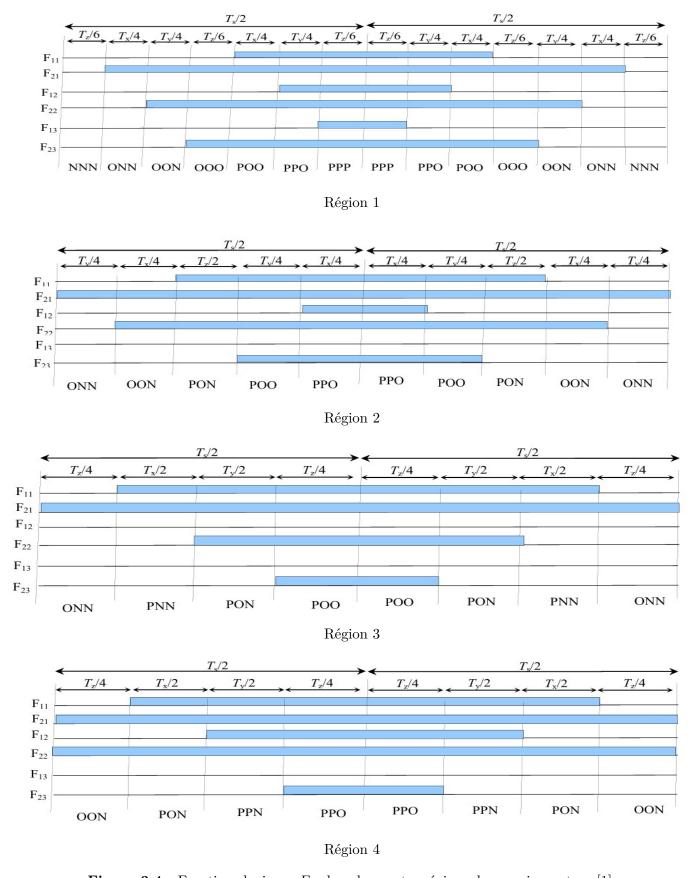

**Figure 3.4 :** Fonctions logiques  $F_{ij}$  dans les quatre régions du premier secteur [1].

À partir de cette séquence, on déduit les fonctions logiques de commande associées aux interrupteurs de l'onduleur. La figure 3.4 montre la forme de ces fonctions logiques pour les interrupteurs des demi-bras supérieurs pendant une période d'échantillonnage, dans les quatre régions du premier secteur du diagramme vectoriel. Les fonctions logiques des demi-bras in-

férieurs sont obtenues par complémentation. On remarque que chaque interrupteur ne change d'état que deux fois par période d'échantillonnage.

À partir des fonctions logiques déterminées pour les quatre régions du premier secteur, on déduit les durées de fermeture des interrupteurs durant la période d'échantillonnage  $T_s$  dans chaque région. Par exemple, pour les quatre régions du premier secteur, les durées de fermeture des interrupteurs des demi-bras supérieurs sont résumées dans le tableau 3.4 Les durées de fermeture des autres interrupteurs peuvent être obtenues par complémentation.

| Région | Demi bras 1                                        | Demis bras 2                     | Demis bras 3                       |

|--------|----------------------------------------------------|----------------------------------|------------------------------------|

| 1      | $S_{11}$ : $T_{\rm x}/2+T_{\rm y}/2+T_{\rm z}/3$   | $S_{12}$ : $T_{y}/2+T_{z}/3$     | $S_{13}$ : $T_{\rm z}/3$           |

|        | $S_{21}$ : $T_x + T_y + 2 T_z/3$                   | $S_{22}$ : $T_x/2+T_y+2$ $T_z/3$ | $S_{23}$ : $T_x/2+T_y/2+2$ $T_z/3$ |

| 2.     | $S_{11}$ : $T_{\rm x}/2 + T_{\rm y}/2 + T_{\rm z}$ | $S_{12}$ : $T_{\rm x}/2$         | $S_{13}$ : 0                       |

|        | $S_{21}$ : $T_x + T_y + T_z$                       | $S_{22}$ : $T_x + T_y/2 + T_z$   | $S_{23}$ : $T_x/2+T_y/2$           |

| 3      | $S_{11}: T_{\rm x} + T_{\rm y} + T_{\rm z}/2$      | S <sub>12</sub> : 0              | $S_{13}$ : 0                       |

|        | $S_{21}$ : $T_x + T_y + T_z$                       | $S_{22}$ : $T_y + T_z/2$         | $S_{23}$ : $T_z/2$                 |

| 4      | $S_{11}$ : $T_{\rm x} + T_{\rm y} + T_{\rm z}/2$   | $S_{12}$ : $T_{y}+T_{z}/2$       | $S_{13}$ : 0                       |

|        | $S_{21}$ : $T_x + T_y + T_z$                       | $S_{22}$ : $T_x + T_y + T_z$     | $S_{23}$ : $T_z/2$                 |

Table 3.4 : Durées de fermeture des interrupteurs dans le cas du premier secteur [1].

## 3.2.6 Résumé de l'algorithme SVM pour l'onduleur triphasé à trois niveaux

L'algorithme de modulation vectorielle spatiale (SVM) appliqué à un onduleur triphasé à trois niveaux repose sur les étapes suivantes :

- Transformation de Clarke : à partir des tensions de référence triphasées  $v_a^*, v_b^*, v_c^*$ , on calcule les composantes dans le plan  $(\alpha\beta)$  selon la transformation de Clarke, ce qui donne  $V_alpha$  et  $V_beta$ , représentant le vecteur de tension dans le plan complexe.

- Coordonnées polaires : à partir de V\_alpha et V\_beta, on calcule :

$$heta = an^{-1} \left( \frac{ extsf{V\_beta}}{ extsf{V\_alpha}} \right)$$

- Détermination du secteur et de la région : l'angle  $\theta$  permet d'identifier le secteur  $s \in \{1, ..., 6\}$ , tandis que la combinaison des signes et des valeurs de V\_alpha et V\_beta permet de déterminer la région  $r \in \{1, 2, 3, 4\}$  à l'intérieur de ce secteur.

- Sélection des vecteurs de commutation : en fonction du secteur s et de la région r, trois vecteurs de commutation  $V_X, V_Y, V_Z$  sont choisis pour approximer le vecteur de référence.

- Calcul des temps de commutation : les durées  $T_X, T_Y, T_Z$  d'activation des vecteurs  $V_X, V_Y, V_Z$  sont calculées pour synthétiser la tension désirée au cours de la période d'échantillonnage.

- **Génération des signaux MLI**: les états de conduction des interrupteurs sont déduits de la séquence des vecteurs appliqués et des temps calculés, ce qui permet de générer les impulsions de commande PWM.

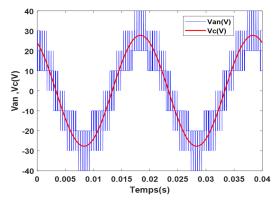

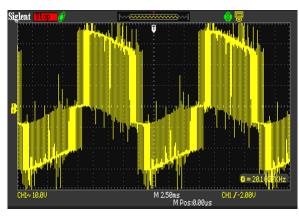

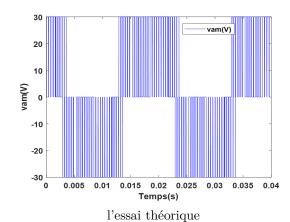

### 3.2.7 Résultats de simulation et interprétations