## الجمهرية الجزائرية الدمقراطية الشعبية الجمهرية الجمهرية الجرائرية الدمقراطية الشعبية REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET PRY ARE 30 \$

MINISTERE DE L'ENSEIGNEMENT SUPERIEUR

#### ECOLE NATIONALE POLYTECHNIQUE

#### DEPARTEMENT D'ELECTRONIQUE

En Vue de l'Obtention

du Grade de Magister en Electronique appliquée

OPTION: Acquisition de Données

par

Souad GHERNAOUTI

## Elaboration d'un Système Informatique pour la Commande et le Contrôle d'un Poste de Soudage MIG pulsé

# الجمهرية الجزائرية الدمقراطية الشعبية REPUBLIQUE <u>ALGERIENNE DEMOCRATIQUE ET</u> POPULAIRE وزارة التعليم العالي وزارة التعليم العالي MINISTERE <u>DE L'ENSEIGNEMENT</u> SUPERIEUR

#### ECOLE NATIONALE POLYTECHNIQUE

DEPARTEMENT D'ELECTRONIQUE

du Grade de Magister en Electronique appliquée

OPTION: Acquisition de Données

par

Souad GHERNAOUTI

## Elaboration d'un Système Informatique pour la Commande et le Contrôle d'un Poste de Soudage MIG pulsé

| Soutenue le | 15 Decembre 1994, devant | le jury compose de : |

|-------------|--------------------------|----------------------|

| Messieurs': | . B. DERRAS              | Président            |

|             | N. BELKHAMZA             | Examinateu           |

|             | C. LARBES                | Examinateur          |

|             | N. LOUAM                 | Examinateur          |

|             | O. NADJEMI               | Rapporteur           |

المدرث الوطنية المتعددة التقنيسات المكتبة — BIBLIOTHEQUE المكتبة Ecole Nationale Polytechnique

A ma mère et mon père en témoignage de mon affection pour eux

> A mes frères et soeurs A mes beaux frères et mes belles soeurs A toute ma famille et mes amis

The second secon

المدرسة الوطنية المتعددة التقنيبات المكتبة — BIBLIOTHEQUE المكتبة وEcole Nationale Polytechnique

Remerciements

Carlo Control of the control of the

Notre travail a été réalisé au niveau du laboratoire de Robotique du Centre de Développement des Technologies Avancées (CDTA), à El-Madania.

#### Je tiens à remercier :

- Monsieur B. Derras, maître de conférence à l'E.N.P. d'avoir accepté la présidence de notre jury de thèse.

#### Je remercie:

- Monsieur N. Belkhamza, maître de conférence de l'université de Blida,

- Madame L. Hemami, chargée de cours à l'E.N.P.

- Monsieur C. Larbes, gradé du PHD,

- Monsieur N. Louam, maître de conférence à l'E.N.P.,

pour l'intérêt qu'ils portent à ce travail en acceptant de le juger.

Monsieur O.Nadjemi, chargé de recherche, pour son suivi et ses conseils qui m'ont permis de mener à bien ce travail.

Je remercie également :

- Y. Boucetta, N. Daddi Moussa, K. Kara et M. Zemiri, du laboratoire de Robotique pour leur disponibilité et leurs conseils.

- Karima et Abdelkarim du laboratoire d'Architecture des Systèmes pour leur aide.

- N. Zenati, N.Lahcene, R. Belaidène et M. Hamitouche de l'équipe de vision pour leur soutien amical.

Je suis reconnaissante à Mahmoud, Amine, Zahia et Djamila pour m'avoir encouragé dans mes travaux de recherche.

Je n'oublierais pas de remercier vivement Houria pour son accueil amical, ses conseils et sa disponibilité permanente. Ainsi que Malika et Ouahiba pour leurs conseils constructifs, disponibilité et aide qu'elles ont porté durant l'élaboration de ce travail et lors de la rédaction du manuscrit. Je remercie aussi Ratiba pour sa disponibilité.

The second of th

المدرسة الوطنية المتعددة التقنيبات المكتب قص BIBLIOTHEQUE Ecole Nationale Polytechnique

Table des matières

#### Introduction

### CHAPITRE I: LA Structure Matérielle du Système Informatisé

| 1. NOTIONS DE SOUDAGE                                   | <u>5</u>    |

|---------------------------------------------------------|-------------|

| 1.1 Le soudage GTA                                      | 5           |

| 1.2 LE SOUDAGE MAG                                      | 6           |

| 1.3 LE SOUDAGE MIG PULSE                                | 6           |

| 2. LA CELLULE EXPERIMENTALE                             | <u>7</u>    |

| 2.1 LE POSTE DE SOUDAGE SYNERGIQUE MIG PULSE M450 PS    |             |

| 2.1.1 MODE PROGRAMMEUR                                  | 10          |

| 2.1.2 MODE SYNERGIQUE                                   | 10          |

| 2.1.3 SORTIE MONITEUR                                   |             |

| 2.1.4 ENTREE DE COMMANDE PAR POTENTIOMETRE NUMERIQUE    | 11          |

| 2.1.5 LES COMMUTATEURS DE MARCHE/ARRET                  |             |

| 2.2 LES CAPTEURS                                        |             |

| 2.2.1 CAPTEUR DE COURANT                                | 12          |

| 2.2.2 CAPTEUR DE VITESSE DE DEFILEMENT DU FIL-ELECTRODE | 14          |

| 2.2.3 CAPTEUR DE PRESSION                               | 14          |

| 2.2.4 CAPTEUR DE TENSION                                | 15          |

| CHAPITRE II : Structure Fonctionnelle du Système Inform | atisé       |

| 1. LA CARTE INTERFACE DE COMMUNICATION                  | <u>.</u> 19 |

| 2. INTREFACE DE COMMANDE ET D'ACQUISITION               | 21          |

| 2.1 FONCTIONS DE COMMUNICATION                          | 21          |

2.1 LES PROGRAMMES DE TRAITEMENT DES ROUTINES D'INTERRUPTION......57

| Table des matières                                                  | المدرسة الوطنية المتعددة التقنيبات المكتب BIBLIOTHEQUE | III         |

|---------------------------------------------------------------------|--------------------------------------------------------|-------------|

|                                                                     | Ecole Nationale Polytechnique                          |             |

| 2.2 LES PROGRAMMES DE TRAITEMENT ET CALCUI                          |                                                        |             |

| 2.2.1 CALCUL DE LA MOYENNE PROGRESSIVE                              |                                                        |             |

| 2.2.2 PROGRAMME D'ACQUISITION                                       |                                                        | 63          |

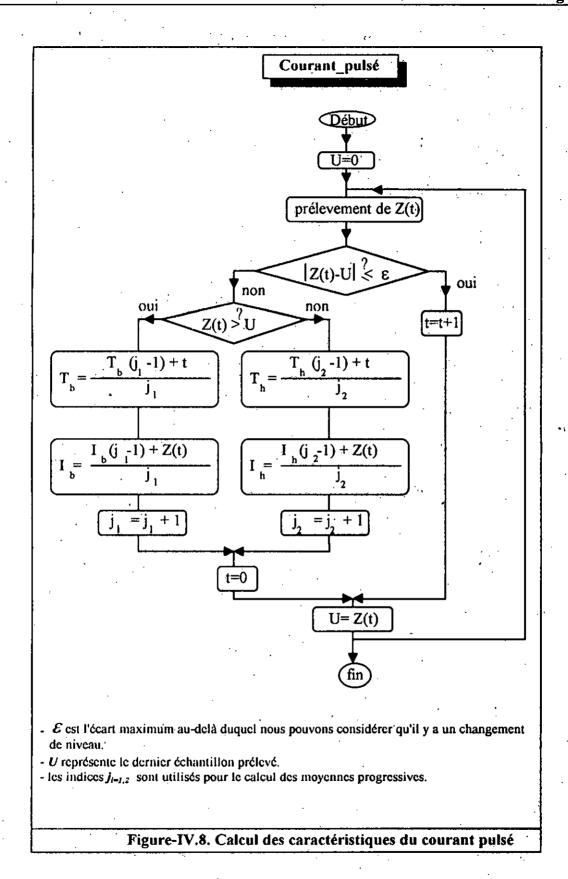

| 2.2.3 DETERMINATION DES CARACTERISTIQUES DU                         | COURANT PULSE                                          | 64          |

| 2.2.4 TRAITEMENT DES URGENCES                                       |                                                        | 66          |

| 2.3 LE PROGRAMME D'INITIALISATION                                   | •••••••                                                | 66          |

| SCHEMAS D'IMPLANTATIONS                                             |                                                        |             |

| CHAPITRE V : Inerface de Commande Et<br>Carte d'Acquisition et d'Is | solation Galvanique                                    | ·           |

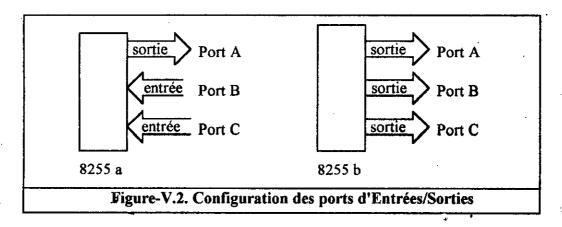

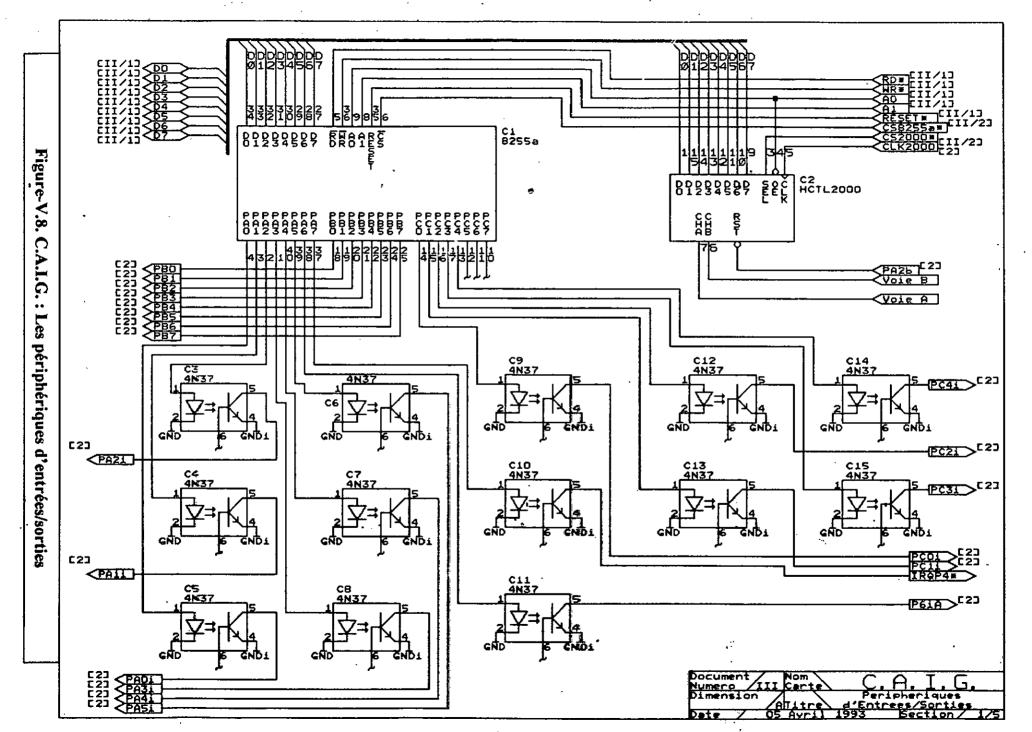

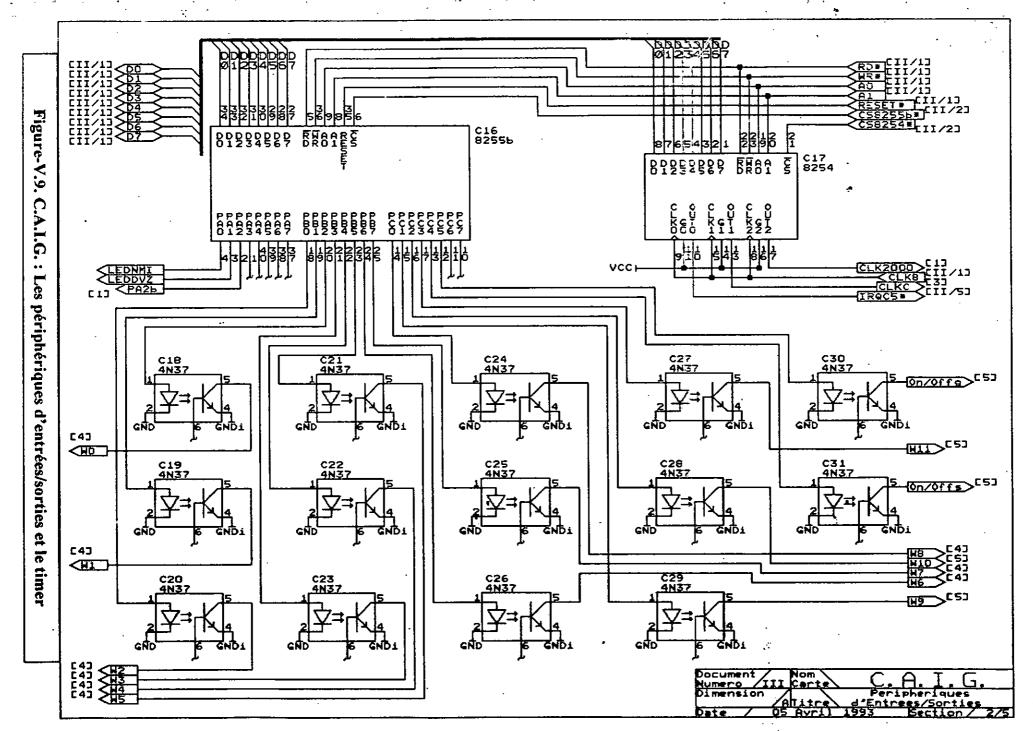

| I. LES INTERFACES PARALLELES PROGRAM                                | IMABLES                                                | <u> 81</u>  |

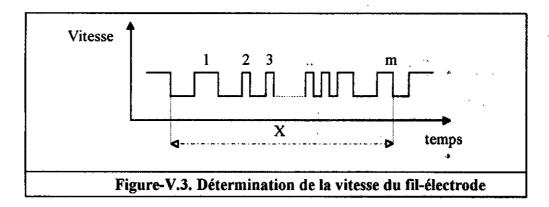

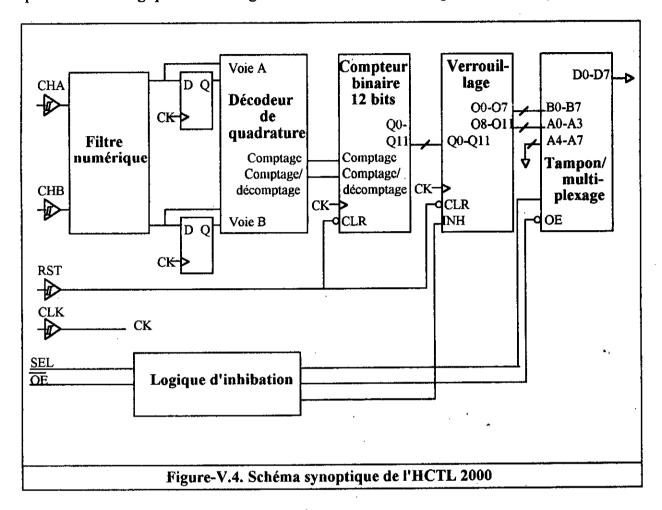

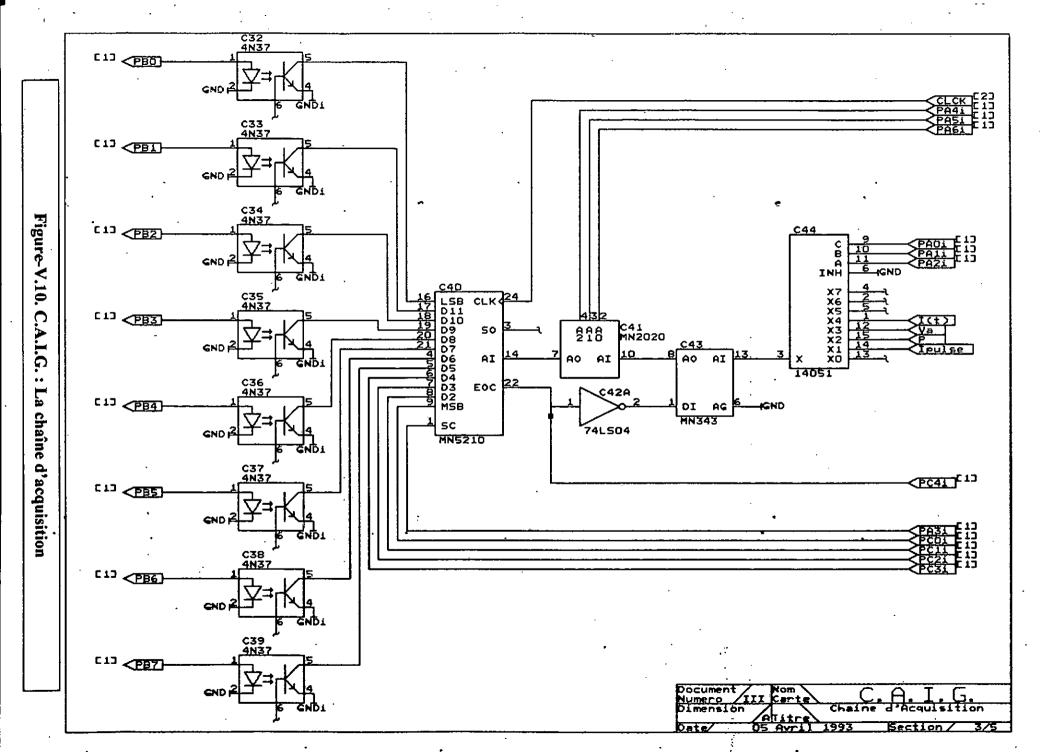

| 2. INTERFACE COMPTEUR/DECODEUR DE Q                                 | UADRATURE HCTL 2000                                    | 83          |

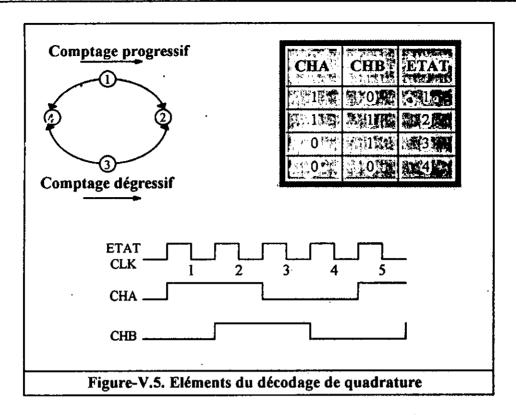

| 2.1 FILTRE NUMERIQUE                                                |                                                        | 83          |

| 2.2 DECODEUR EN QUADRATURE                                          |                                                        | •           |

| 2.3 COMPTEUR DE POSITION                                            |                                                        |             |

| 2.4 INTERFACE DU BUS                                                |                                                        | 85          |

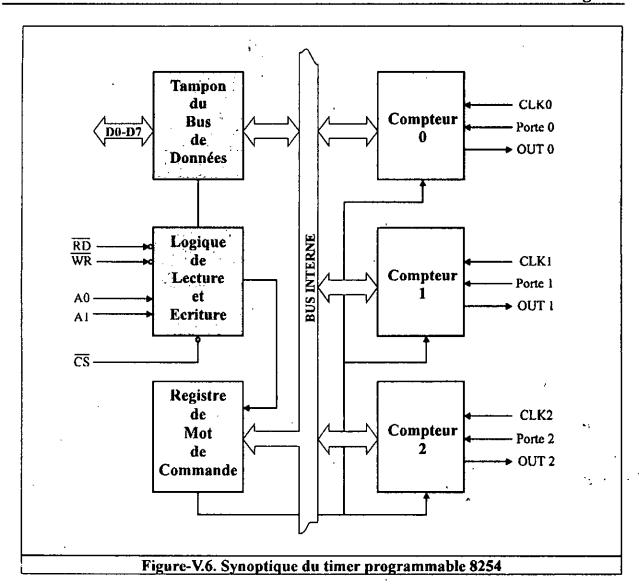

| 3. LE CIRCUIT TIMER 8254                                            |                                                        | 95          |

|                                                                     | •                                                      |             |

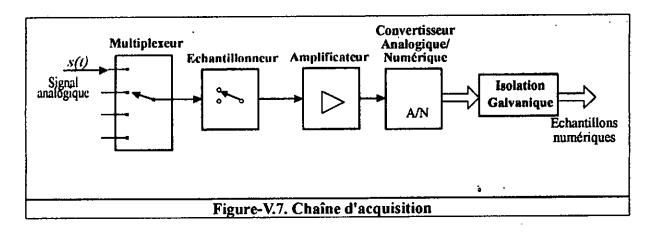

| 4. LA CHAINE D'ACQUISITION                                          |                                                        | 87          |

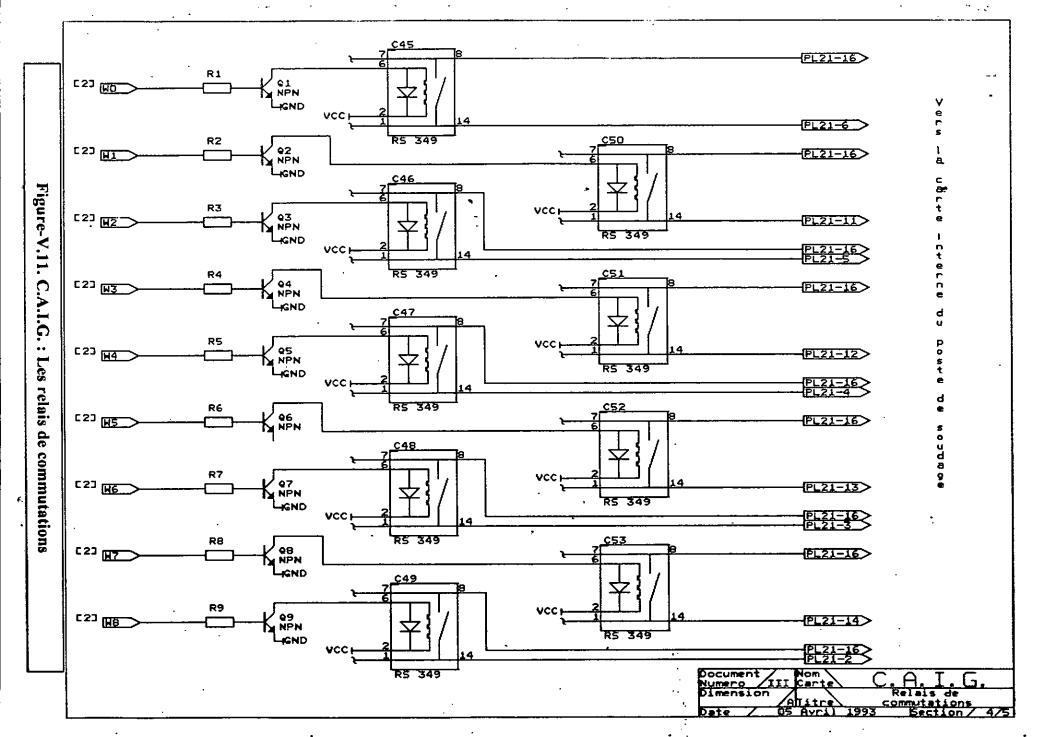

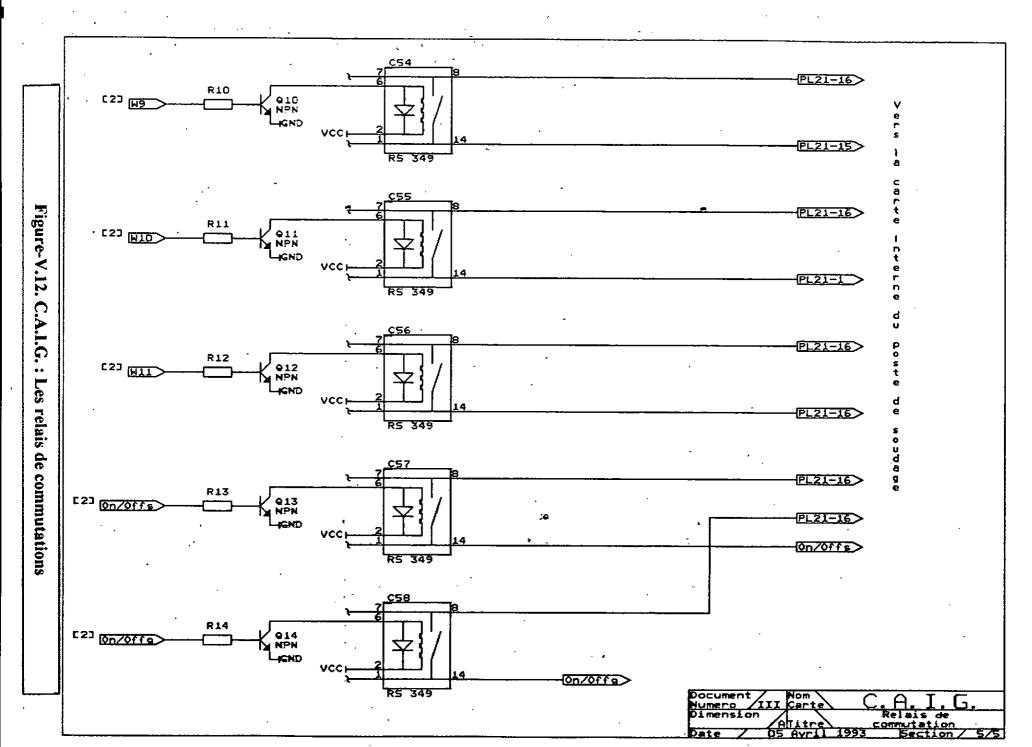

| 5. RELAIS DE COMMUTATION                                            |                                                        | <u>89</u>   |

| 6. CIRCUITS D'ISOLATION GALVANIQUE                                  | ***************************************                | 89          |

| SCHEMAS D'IMPLANTATIONS                                             |                                                        |             |

| CHAPITRE VI : Organisation Logicielle d                             | u Système Informatisé                                  |             |

| 1. LANGAGE DE PROGRAMMATION TEMPS I                                 | REEL                                                   | <u> 100</u> |

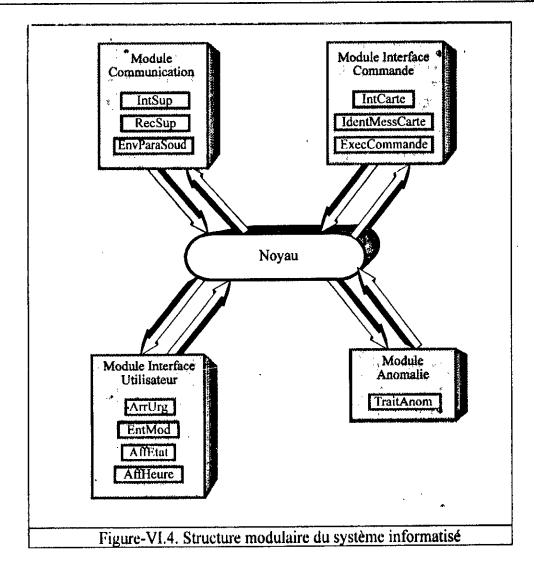

| 2. ORGANISATION LOGICIELLE DU SYSTEM                                | E INFORMATISE                                          | 100         |

| 2.1 PROCESSUS DU MODULE COMMUNICATION                               |                                                        | 105         |

| 2.2 PROCESSUS DE L'INTERFACE DE COMMANDE                            | ******************************                         | 105         |

| 2.3 PROCESSUS DU MODULE INTERFACE UTILISATI                         | EUR                                                    | 106         |

| 2.4 PROCESSUS DU MODULE ANOMALIE                                    | ***************************************                | 106         |

| 2.5 PROCESSUS DU NOYAU                      | SIBLIOTHEQUE      |  |  |  |

|---------------------------------------------|-------------------|--|--|--|

| 3. LE NOYAU                                 | Ecolo No          |  |  |  |

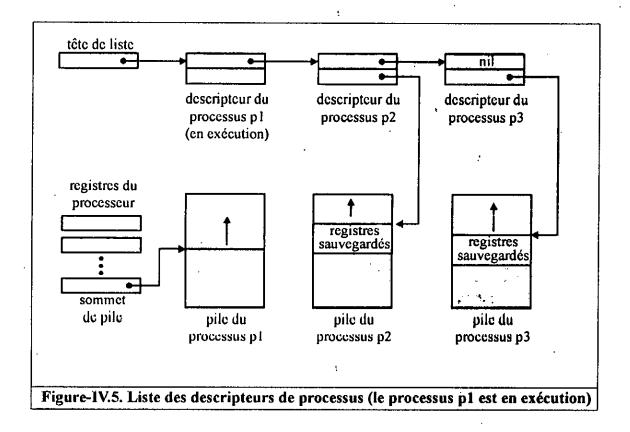

| 3.1 ALLOCATION DU PROCESSEUR.               | 106               |  |  |  |

| 3.1.1 PRIMITIVE DE CREATION DE I            | PROCESSUS         |  |  |  |

| 3.1.2 PRIMITIVE DE COMMUTATION DE PROCESSUS |                   |  |  |  |

| 3.1.3 PRIMITIVES DE GESTION DES             | INTERRUPTIONS 109 |  |  |  |

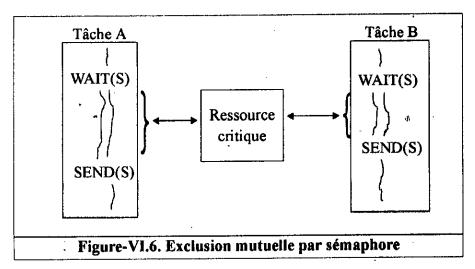

| 3.2 L'EXCLUSION MUTUELLE                    | 110               |  |  |  |

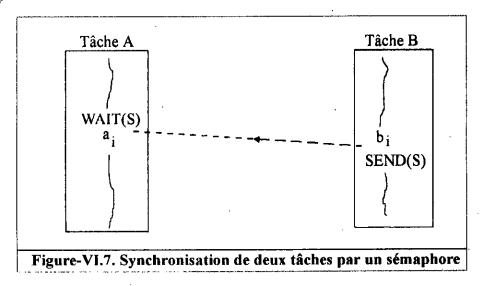

| 3.3 LA SYNCHRONISATION                      | 111               |  |  |  |

|                                             | <u>ON113</u>      |  |  |  |

|                                             | 113               |  |  |  |

| •                                           | 114               |  |  |  |

| 4.3.1 <b>G</b> ESTION DE LA LIAISON SERI    | E114              |  |  |  |

| 4.3.2 DETECTION DES ERREURS                 | 114,              |  |  |  |

| 4.3.3 IDENTIFICATION DU MESSAGE             |                   |  |  |  |

| 5. MODULE INTERFACE COMM                    | ANDE120           |  |  |  |

| 6. MODULE INTERFACE UTILIS                  | ATEUR123          |  |  |  |

| 7. MODULE ANOMALIE                          | 125               |  |  |  |

Conclusion

Annexe A

Annexe B

المدرسة الرطنية المتعددة التقنيسات المكتبة — BIBLIOTHEQUE المكتبة — Ecele Nationale Polytechnique

Introduction

The second of th

البدرسة الوطنية المتعددة التقنيبات المكسسية --- BIBLIOTHEQUE المكسسية المكسسية المحكسسية Ecolo Nationale Polytechnique

Les exigences de qualité dans les pays industrialisés ont favorisé l'évolution des techniques d'assemblage et de soudage à l'arc. Le développement des sources d'énergies de soudage (contrôle transistorisé), a facilité l'ajustage des paramètres de soudage et a contribué par la suite à l'apparition du soudage synergique. Ce procédé est très utilisé dans le soudage de qualité en raison des nombreux avantages qu'il procure comme la régulation automatique des paramètres de soudage et le maintien de la stabilité de l'arc avec le changement de la vitesse. Cependant, dans ce cas, les paramètres de soudage sont fixés par l'opérateur avant le lancement de l'opération de soudage. Ainsi, ce dernier n'intervient à aucun moment durant l'évolution du procédé, il y a donc peu d'interaction avec l'environnement externe. Les efforts élaborés alors pour éviter l'apparition de défauts dus à la source sont importants et coûteux.

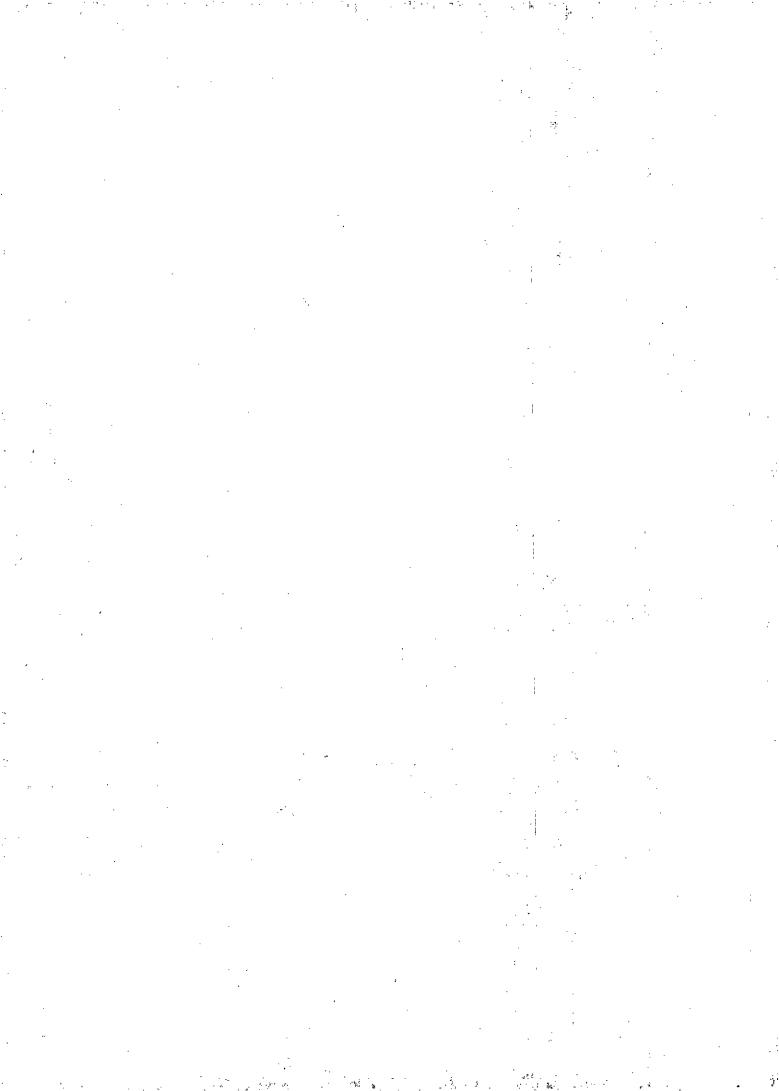

Afin d'introduire cette interactivité en temps réel, le laboratoire de robotique du C.D.T.A a lancé un projet intitulé Système de Soudage Assisté par Ordinateur (S.S.A.O.). Ce dernier utilise un bras manipulateur, un poste de soudage comme source d'énergie, une caméra CCD matricielle reliée à un système de traitement d'images et un système superviseur coordonnant ces éléments.

Le projet S.S.A.O. est un bon moyen d'acquisition des connaissances actuelles dans le domaine de soudage. En effet, il fournit plusieurs avantages, à savoir :

- l'accroissement des vitesses de soudage,

- l'augmentation des taux de dépôt de matière,

- l'élargissement du domaine d'emploi, notamment par l'augmentation des fourchettes des paramètres de soudage et des surfaces soudables.

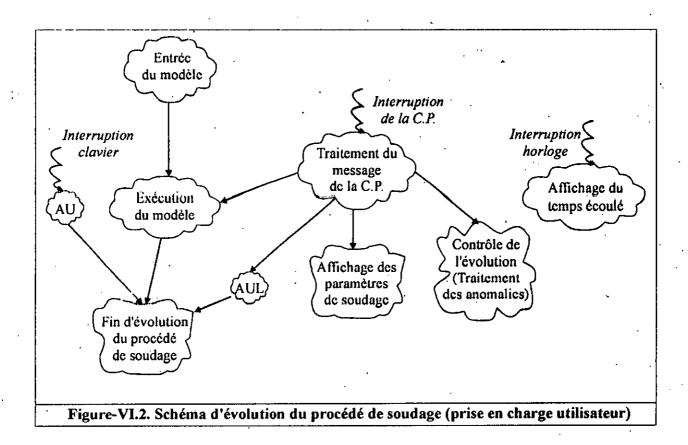

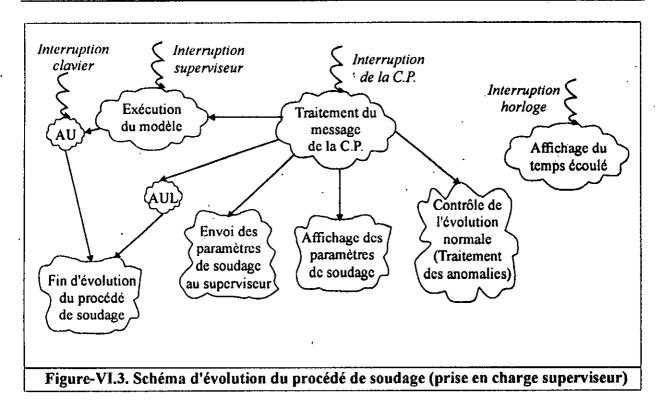

Notre travail consiste donc à réaliser la commande par micro-ordinateur du poste de soudage pour fournir au système superviseur et à l'opérateur les moyens

d'intervenir pendant l'évolution du procédé. En effet, le système informatisé réalisé doit exécuter instantanément une commande superviseur (ou utilisateur) et l'informer régulièrement pendant l'évolution du procédé des valeurs des paramètres de soudage. Le système favorise ainsi la correction de toute anomalie dès son apparition.

L'élaboration de ce travail nécessite une conception matérielle faisant l'objet des cinq premiers chapitres et une conception logicielle présentée au dernier chapitre de ce mémoire.

Nous commençons dans le chapitre I, par la présentation de la cellule expérimentale. Elle est constituée de la source d'énergie de soudage (le poste) et des différents capteurs permettant le prélèvement de l'état de l'environnement de soudage.

Au chapitre II, nous exposons la structure fonctionnelle du système informatisé. Les différentes fonctions des éléments du système informatisé à savoir l'interface de communication et l'interface de communication sont présentées.

Le chapitre III donne les détails de conception et de réalisation de la carte assurant la communication avec le superviseur. Tandis que la conception matérielle et logicielle de l'interface de commande et d'acquisition est présentée aux chapitres IV et V.

Enfin, l'organisation logicielle du système informatisé fait l'objet du chapitre VI. Ce chapitre expose l'approche modulaire adoptée et les différents mécanismes de programmation temps réel utilisés pour le développement de la partie logicielle du système informatisé. Dans ce chapitre, nous présentons les différents points de conception du programme de gestion du système informatisé et le langage utilisé à cet effet.

## CHAPITRE

Structure Matérielle du Système Informatisé

Le projet S.S.A.O. [Nad-93] utilise des moyens techniques évolués comme l'illumination laser, la camera CCD, le robot, afin d'obtenir un meilleur contrôle des différentes phases de soudage. Ces différentes phases sont, la phase d'inspection préliminaire, la phase d'exécution de la tâche et la phase de contrôle de qualité.

#### Phase d'inspection préliminaire (présoudage) :

Dans cette phase, une localisation et orientation des objets à souder ainsi qu'une détection du type de joint à souder et de ses dimensions sont effectuées.

#### ◆ Phase d'exécution de la tâche (soudage) :

En seconde étape, le guidage de la torche en temps réel et le contrôle des paramètres de soudage et des dimensions du cordon de soudure (pénétration et largeur du cordon) sont effectuées.

#### ♦ Phase de contrôle de qualité (post soudage) :

Enfin, un contrôle de la géométrie du cordon de soudure est établi ainsi qu'une détection des anomalies de soudage.

Pour réaliser ces fonctions, le projet S.S.A.O. (figure I.1) utilise les moyens suivants :

- un bras manipulateur pour le maintien et le guidage de la torche de soudage,

- un Système Informatisé (S.I.) prenant en charge le contrôle du poste de soudage,

- un système de traitement d'images regroupant une caméra CCD matricielle, pour l'acquisition d'images de l'arc lui-même ou du joint de soudure, et un laser de faible puissance pour l'illumination du joint de soudure et

- un système superviseur assurant le contrôle et la coordination de l'ensemble de ces éléments.

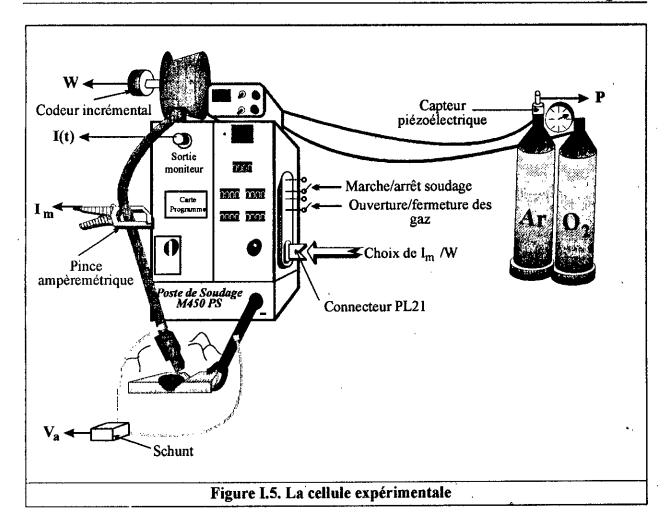

Dans le cadre de ce projet, notre travail consiste en la conception et réalisation du S.I. dont l'objectif est de contrôler les paramètres de soudage pendant l'évolution du procédé. La cellule expérimentale prévue à cet effet est composée d'un poste de soudage MIG pulsé M450 PS et de différents capteurs pour le prélèvement des paramètres de soudage.

Avant de voir plus en détail les différentes composantes de la cellule, nous avons jugé nécessaire d'introduire quelques notions sur le soudage.

#### 1. NOTIONS DE SOUDAGE

Les deux types de soudage à l'arc les plus communs sont le procédé Gaz Tungsten Arc (GTA) et le procédé Gaz Metal Arc (GMA). Ils utilisent la chaleur dégagée par l'arc existant entre l'électrode et la pièce à souder pour faire fondre le métal et joindre les pieces par fusion. Ce type de soudage à l'arc est assez répandu dans la fabrication industrielle de métaux [Sic-88].

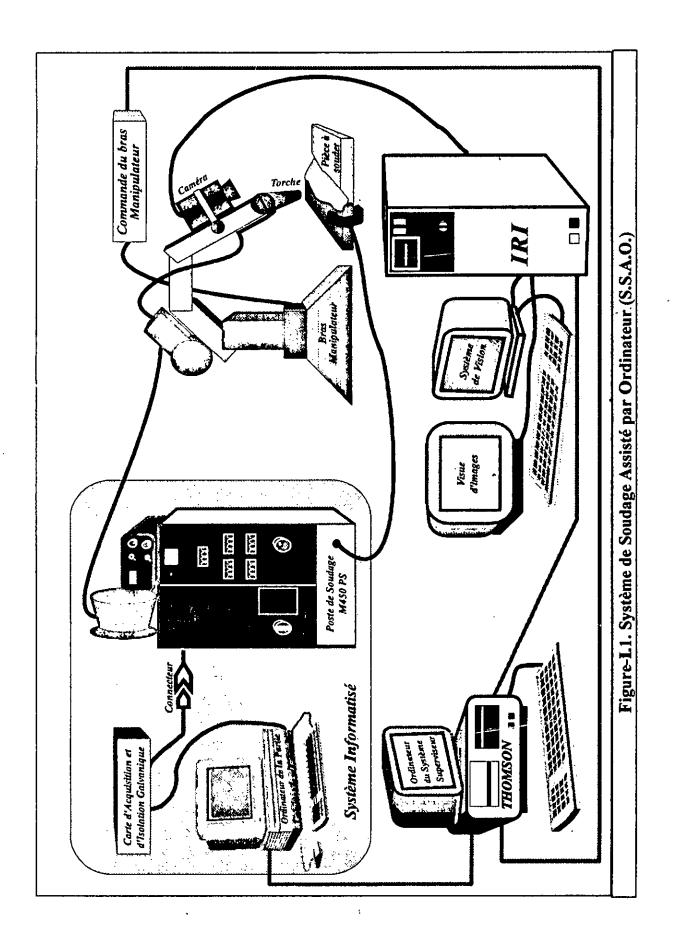

#### 1.1 Le soudage GTA

Dans le GTA, appelé aussi *Tungsten Inert Gaz (TIG)*, l'arc est crée entre une électrode non consommable en *Tungstène* et le métal à souder, comme le montre la figure I.2. Le courant traversant l'électrode étant important (de 50 à 700 A), une forte intensité de chaleur est alors dégagée par l'arc provoquant ainsi la fusion des pièces à souder.

Notons que le métal fondu formé sur les pièces à souder est appelé bain de soudure. La protection de la contamination par l'atmosphère de ce dernier ainsi que de l'arc et le métal d'apport est assurée par un gaz inerte tel que l'Argon ou un mélange de gaz [Sic-88].

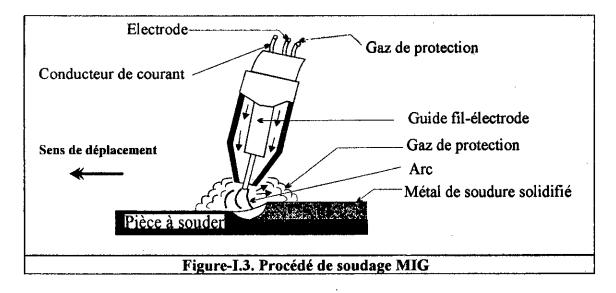

#### 1.2 Le soudage MAG

Le soudage *MAG*, appelé également *Metal Inert Gaz (MIG)*, utilise la chaleur dégagée par l'arc existant entre une électrode consommable et la pièce à souder (figure I.3). Le gaz de protection peut être un gaz inerte tel que l'*Argon* ou l'*Hélium*, ou un mélange de gaz inertes avec l'oxygène ou le dioxyde de carbone (CO2). L'électrode est alimentée par un courant dont la haute densité provoque sa fusion. La vitesse de défilement du fil-électrode est un paramètre très important pour le contrôle du procédé de soudage [Sic-88].

#### 1.3 Le Soudage MIG pulsé

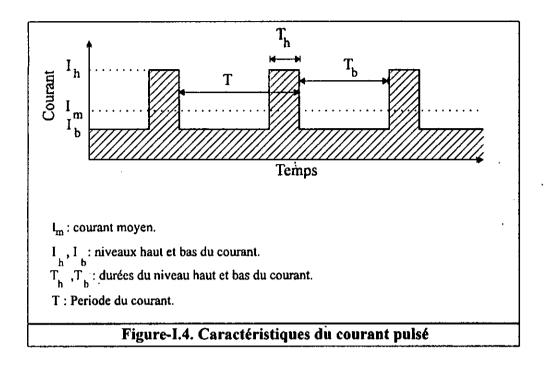

Dans le procédé de soudage MIG, les caractéristiques de transfert du métal sous une atmosphère inerte sont acceptables uniquement par l'utilisation de courants relativement importants. Le soudage de matériaux de faible épaisseur et dans toutes les positions est alors impossible avec ce procédé [Tri-81]. L'emploi de courants modulés introduits par Needham [Nee-62] et l'apparition de sources d'alimentation transistorisées ont contribué à

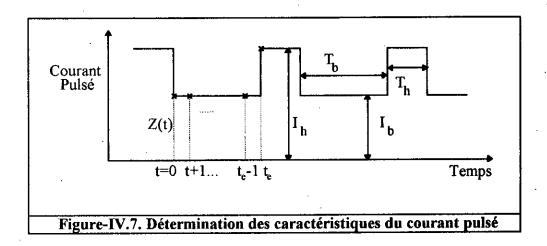

la naissance du soudage MIG utilisant un courant pulsé (figure I.4). Ce procédé a l'avantage de permettre un meilleur contrôle de dépôt du métal d'apport.

Dans ce cas l'obtention d'une bonne qualité de soudure dépend de l'expérience du soudeur, car il doit choisir selon l'application, le type de gaz de protection, le diamètre du fil-électrode et les paramètres de soudage à savoir :

- la vitesse de défilement du fil-électrode W,

- les niveaux et les durées  $I_b$ ,  $I_h$ ,  $T_b$ ,  $T_h$  du courant (figure I.4),

- et la tension de l'arc électrique  $V_a$ .

Après avoir présenté quelques notions sur le soudage à l'arc, nous allons maintenant reprendre plus en détail la partie concernant la cellule expérimentale.

#### 2. LA CELLULE EXPERIMENTALE

La cellule expérimentale constituée d'un poste de soudage et de capteurs (figure I.5), est réalisée afin de pouvoir prélever l'ensemble des paramètres de soudage reflétant l'état du procédé de soudage. De plus, il est possible à travers cette cellule de choisir les valeurs de certains de ces paramètres comme la vitesse de défilement du fil-électrode.

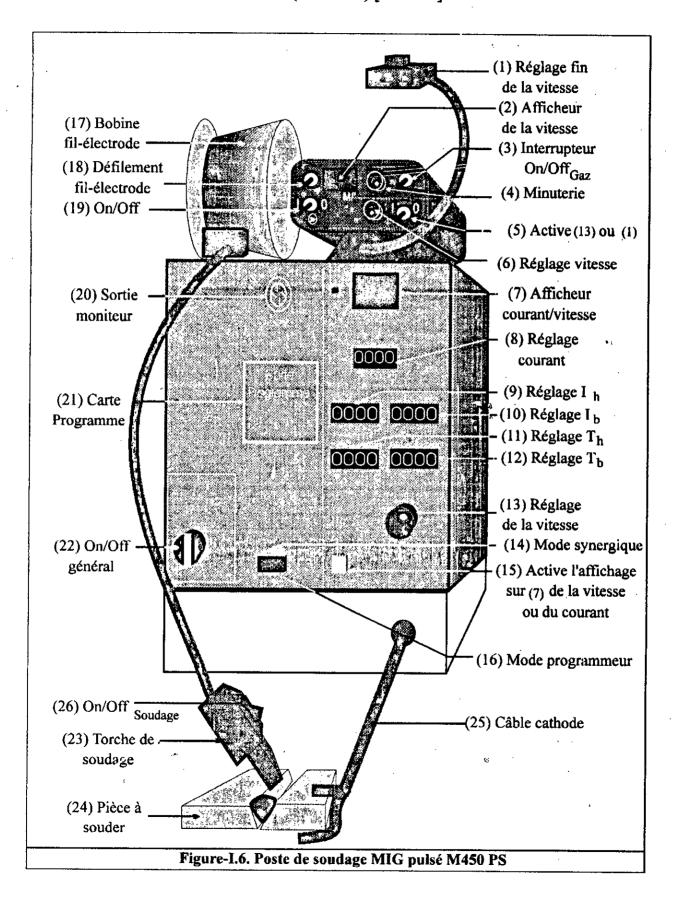

#### 2.1 Le poste de soudage synergique MIG pulsé M450 PS

Le poste de soudage disponible au niveau du laboratoire de robotique du *C.D.T.A* est de la série *M450 PS* (figure I.6). Il est la source d'énergie de soudage *MIG*, fournissant à sa sortie un courant pulsé (allant jusqu'à 350 A), une vitesse de défilement du fil-électrode et un débit déterminé du gaz. Il permet également de faire un réglage fin de la vitesse de défilement à distance [GEC-85].

Le soudage synergique MIG pulsé a été développé par Advanced Welding Products Division (AWP) en association avec Welding Institute. Les systèmes AWP fournissent un courant pulsé avec une grande précision. Durant chaque niveau haut du courant, une gouttelette unique de métal se détache du fil-électrode et traverse proprement l'arc. La stabilité de l'arc est assurée par le bouclage continu du courant. Le

signal synergique est élaboré par un programme qui lie la fréquence du courant pulsé à la vitesse de défilement du fil-électrode (cf.I.2.1.2.) [GEC-85].

Le M450 PS peut opérer selon deux modes de fonctionnement qui sont le mode programmeur et le mode synergique.

#### 2.1.1 Mode programmeur

Ce mode est un mode manuel car l'utilisateur peut choisir les valeurs des paramètres suivants :

- Le niveau bas  $I_b$  et le niveau haut  $I_h$  du courant pulsé appliqué à l'électrode consommable ainsi que leurs durées respectives  $T_b$  et  $T_h$  (figure I.4).

- La vitesse de défilement W de l'électrode consommable.

#### 2.1.2 Mode synergique

Ce mode de fonctionnement est très important car il permet de faire un contrôle enligne des paramètres de soudage. Son principe consiste à fournir une corrélation entre le courant moyen et la vitesse de défilement du fil-électrode. Cette corrélation est fixée par la carte programme ( $n^{\circ}21$  figure I.6). L'opérateur ne choisit que la valeur de la vitesse de défilement, la valeur du courant s'en déduit automatiquement. La relation existante entre le courant moyen  $I_m$  et la vitesse de défilement du fil-électrode W est donnée par [Ami-86]:

$$I_{m} = k.W (I.1)$$

où :

k est la pente des caractéristiques de consommation de l'arc de longueur moyenne.

et

$$I_{m} = \frac{I_{b} \cdot T_{b} + I_{h} \cdot T_{h}}{T} \tag{I.2}$$

La carte programme renferme quatre potentiomètres, chacun d'eux influe sur la corrélation (I.1) tout en gardant les équations suivantes constantes :

$$I_b - I_b = Cte (I.3)$$

$$T_b + T_b = Cte (I.4)$$

En plus de ces deux modes de fonctionnement, le poste de soudage fournit une sortie moniteur et une entrée de commande de la vitesse/courant en mode synergique. Ces entrées/sorties sont exploitées pour la réalisation du S.I.

#### 2.1.3 Sortie moniteur

La sortie moniteur directement accessible sur le poste (n°20 figure I.6) fournit le signal courant qui nous renseigne sur deux aspects importants qui sont :

- la valeur limite du courant, puisque le signal prend une forme particulière (présence de piques), ce qui permet de signaler un arrêt d'urgence et

- la forme du signal courant nous permet d'évaluer la corrélation (I.1) existante entre la vitesse et le courant qui est fixée par la carte programme.

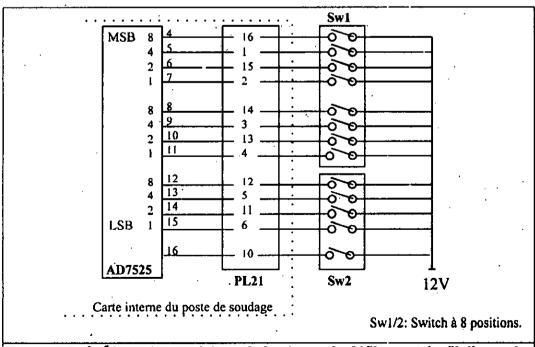

#### 2.1.4 Entrée de commande par potentiomètre numérique

Sur une carte interne du poste se trouve un potentiomètre à contrôle numérique l'AD7525 ayant la même fonction que le potentiomètre de commande de la vitesse de défilement du fil-électrode (n°13 figure I.6). Ce circuit nécessite 12 lignes numériques de commande pouvant avoir des valeurs comprises entre 0 et 12V. Pour éviter tout problème de masse, le poste fournit le 12V par l'intermédiaire de la pin 10 du connecteur PL21 (figure I.7).

Il suffit alors de reboucler cette ligne ou non sur les 12 lignes d'entrées de l'AD7525 pour fixer la valeur de la consigne.

Figure-I.7. Commande numérique de la vitesse de défilement du fil-électrode

La commande à travers ce potentiomètre n'est utilisée qu'en mode synergique. En effet, vue la nature du procédé, le courant ne peut être contrôlé indépendamment de la vitesse car une augmentation de courant entraîne une fusion plus rapide de l'embout de l'électrode et nécessite alors un accroissement de la vitesse du fil-électrode pour maintenir la longueur de l'arc constante.

Par ailleurs, les commandes de marche/arrêt sont assurées au niveau du poste par des commutateurs.

#### 2.1.5 Les commutateurs de marche/arrêt

Le poste possède deux commutateurs de marche/arrêt :

- le commutateur de mise en marche de l'opération de soudage placé au niveau de la torche (n°26 figure I.6), et

- le commutateur de l'arrivée des gaz de protection (n°3 figure I.6), fonctionnant automatiquement dès le lancement de l'opération de soudage. La fermeture des gaz est contrôlée par une minuterie (n°4 figure I.6), qui se déclenche après l'extinction immédiate de l'arc de soudage.

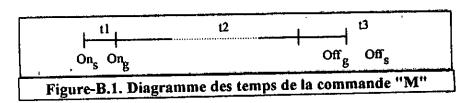

Afin de réaliser ces commandes de commutation par ordinateur nous avons mis en place deux relais. Le premier actionne/désactionne l'alimentation du fil-électrode par un courant fourni par la source d'énergie synergique pulsé (On/Off<sub>s</sub>). Le second est placé pour l'ouverture/ fermeture du robinet d'arrivée des gaz de protection (On/Off<sub>s</sub>).

La cellule expérimentale en plus du poste soudage, renferme des capteurs pour le prélèvement des paramètres de soudage.

#### 2.2 Les capteurs

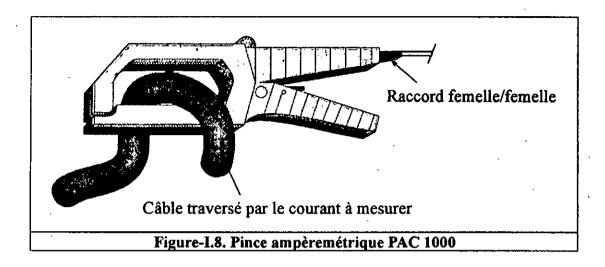

Afin de mesurer le courant, la vitesse de défilement, la pression du gaz de protection et la tension de l'arc, nous utilisons respectivement une pince ampèremétrique, un codeur optique incrémental, un capteur piézoélectrique et un shunt.

#### 2.2.1 Capteur de courant

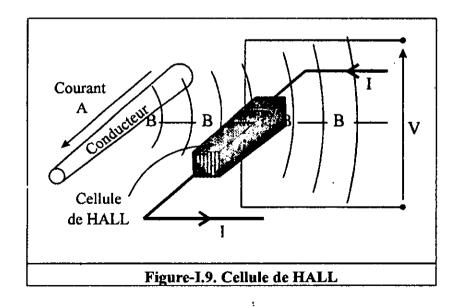

Le capteur de courant utilisé est une pince *ampèremétrique* dont le principe de fonctionnement est basé sur la cellule à *Effet HALL* (figure I.8).

Cette dernière est incorporée à l'intérieur du circuit magnétique d'une pince. Àinsi, lorsque elle est placée autour d'un conducteur parcouru par un courant A, un champ magnétique canalisé par son noyau lui est appliqué. La cellule délivre alors une tension proportionnelle à l'intensité du courant A circulant dans le conducteur (figure I.9) [CHA-91a].

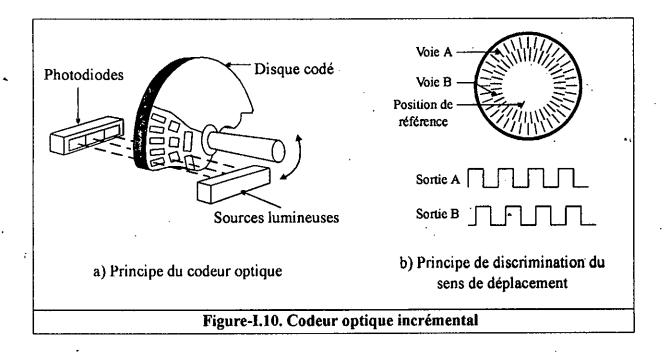

#### 2.2.2 Capteur de vitesse de défilement du fil-électrode

Nous utilisons un capteur numérique pour mesurer la vitesse. Ce capteur est un codeur incrémental solidaire aux galets d'entraînement du fil-électrode. Il est composé d'un dispositif optique associé à un disque transparent. La lecture se fait par transparence par l'intermédiaire d'une série de sources lumineuses situées sur un rayon d'un côté du disque et d'une série de photodétecteurs situés sur l'autre côté du disque (figure I.10.a). Le disque utilisé renferme deux voies permettant la détection du sens de déplacement (figure I.10.b) [Nus-87].

#### 2.2.3 Capteur de pression

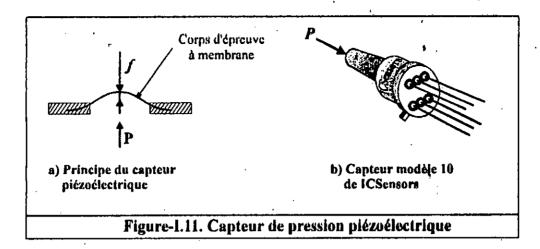

Nous effectuons le prélèvement de la pression afin de détecter la présence et la stabilité du gaz de protection influant sur le transfert de matière. Pour ce faire, nous employons le capteur *Modèle 10* d'*ICSensors* qui utilise la déformation d'un corps d'épreuve pour mesurer la pression appliquée (figure I.11). Il est équipé d'un élément piézoélectrique qui est robuste, compact et peu coûteux [ICS-85].

#### 2.2.4 Capteur de tension

La tension est directement prélevée entre le tube de contact et la pièce à souder.

Nous utilisons pour cela un *shunt* produit par *CHAUVIN & ARNOUX* qui peut être raccordé à un multimètre numérique [CHA-91b].

En plus de la cellule expérimentale, le S.I. renferme d'autres éléments. Une étude fonctionnelle détaillée de ce dernier est présentée dans le chapitre suivant.

## **BIBLIOGRAPHIE**

[Ami-86] M. Amin

Microcomputer control of synergic pulsed MIG welding Metal Construction, April 1986.

[CHA-91u] CHAUVIN & ARNOUX Pinces Ampèremétriques Avril 1991.

[CHA-91b] CHAUVIN & ARNOUX

Mesure et instrumentation

1991.

[GEC-85] GEC Industrial Controls Limited

Advanced Welding Products

The General Electric Company, 1985.

- [ICS-85] ICSensors Euro Sensor

Model 10, Application Note

TN-001 April 1988, TN-002 March 1985, TN-003 April 1988.

- [Nad-93] O. Nadjemi et al.

Réalisation d'un Système de Soudage Automatique Assisté par

Ordinateur.

Rapport Scientifique, Centre Développement des Technologies Avancées,

Laboratoire de Robotique, 1993.

- [Nee-62] J.C. Needham

Control of Transfer Aluminium Consomable Electrode Welding

Proc. Symposium Physics of the Welding Arc, I.W London, pp. 114-122,

1962.

- [Nus-87] Henri Nussbaumer

Informatique Industrielle III

Presses Polytechniques Romandes, pp. 316-372, 1987.

- [Sic-88] Pierre Sicard & Martin D. Levine

An Approch to an Expert Robot Welding System

IEEE Transactions on Systems, Man and Cybernetics vol 18, March/April,

1988.

- [Tri-81] D.E.M. Trindade

Synergic MIG welding of Aluminium

M.Sc Thesis, Cranfield Institut of Technology Academic year 1980-81.

- [Yaz-92] H. Yazid

Contribution à la définition d'un environnement informatique pour un système de soudage assisté par ordinateur

Thèse de Magister, Centre de Développement des Technologies Avancées, CDTA, Mars 1992.

# CHAPITRE

Structure Fonctionnelle du Système Informatisé

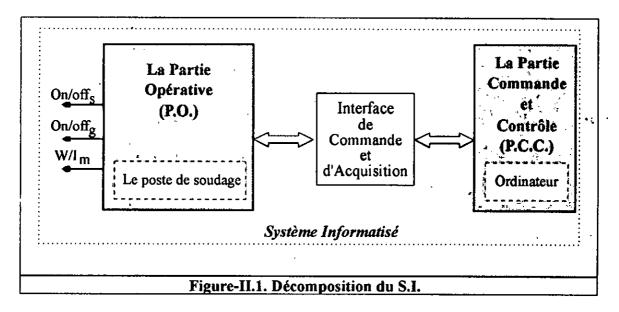

Afin de réaliser le système informatisé S.I. associé au poste de soudage, nous avons adopté l'approche fonctionnelle (figure II.1) qui est basée sur la division du système en deux parties [And-91]:

- une partie opérative définie comme un ensemble de tâches exécutives et,

- une partie commande et contrôle qui décrit la synchronisation des tâches exécutives en fonction des interactions avec l'environnement externe.

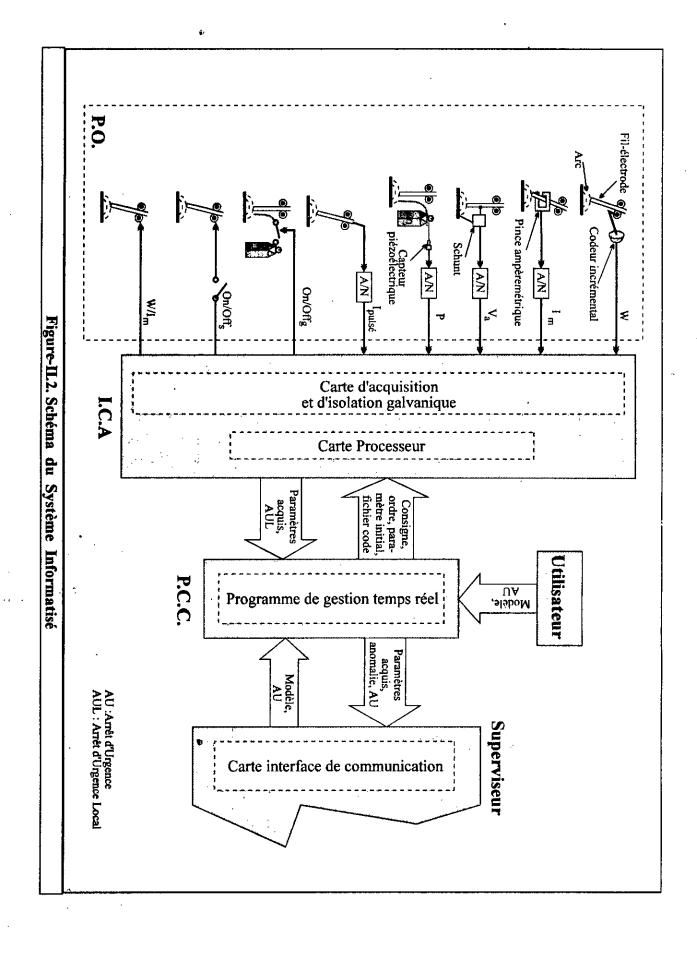

Le poste de soudage M450 PS constitue la Partie Opérative (P.O.) du système alors que la Partie Commande et Contrôle (P.C.C.) renfermant une programmation temps réel (cf. Chap. VI) est assurée par un micro-ordinateur compatible IBM (figure II.2). Ce dernier, communique avec le système superviseur à travers une Carte d'Interface de Communication (C.I.C.). Par ailleurs, il est lié au poste de soudage au moyen de l'Interface de commande et d'Acquisition (I.C.A.).

#### 1. LA CARTE INTERFACE DE COMMUNICATION

Nous avons dû réaliser en plus du travail demandé, une carte d'entrées/sorties associée au superviseur en vue d'accroître ses capacités de communication. En effet, le système superviseur ne dispose que d'une liaison série et d'une liaison parallèle souvent

exploitées par une souris et une imprimante. Par contre l'établissement de la liaison entre le système superviseur et l'ensemble des dispositifs (bras manipulateur, système de vision, système informatisé) nécessite l'utilisation d'un système de communication constitué d'au moins trois liaisons [Yaz-92].

Cette carte d'entrées/sorties (C.I.C.) est connectée sur le bus G64 de l'ordinateur superviseur THOMSON. Elle est liée à l'ordinateur de la P.C.C. par l'intermédiaire du port série basé sur un 8250 d'Intel.

#### 2. INTREFACE DE COMMANDE ET D'ACQUISITION

L'I.C.A. assure en même temps les fonctions de commande, d'acquisition et d'isolation galvanique entre le poste de soudage et l'ordinateur de la P.C.C. Par ses tâches de communication et de traitement, elle allège le travail de la P.C.C.

#### 2.1 Fonctions de communication

La P.C.C. transmet des ordres à la P.O. qui répond par une série de comptes rendus. Nous avons donc à considérer deux types de transferts : le transfert de la P.C.C. vers la P.O. et le transfert dans le sens inverse.

#### 2.1.1 Transfert de la P.C.C. vers La P.O.

La P.C.C. envoie au poste, à travers l'I.C.A., des ordres suivants :

- Marche/Arrêt de l'opération de soudage,

- Ouverture/Fermeture de l'arrivée des gaz de protection et

- Activer/Interrompre la phase d'acquisition : à la différence des deux précédents ordres, cette commande est une opération logicielle. Elle permet d'activer/ désactiver le prélèvement d'une série d'échantillons au niveau du poste de soudage.

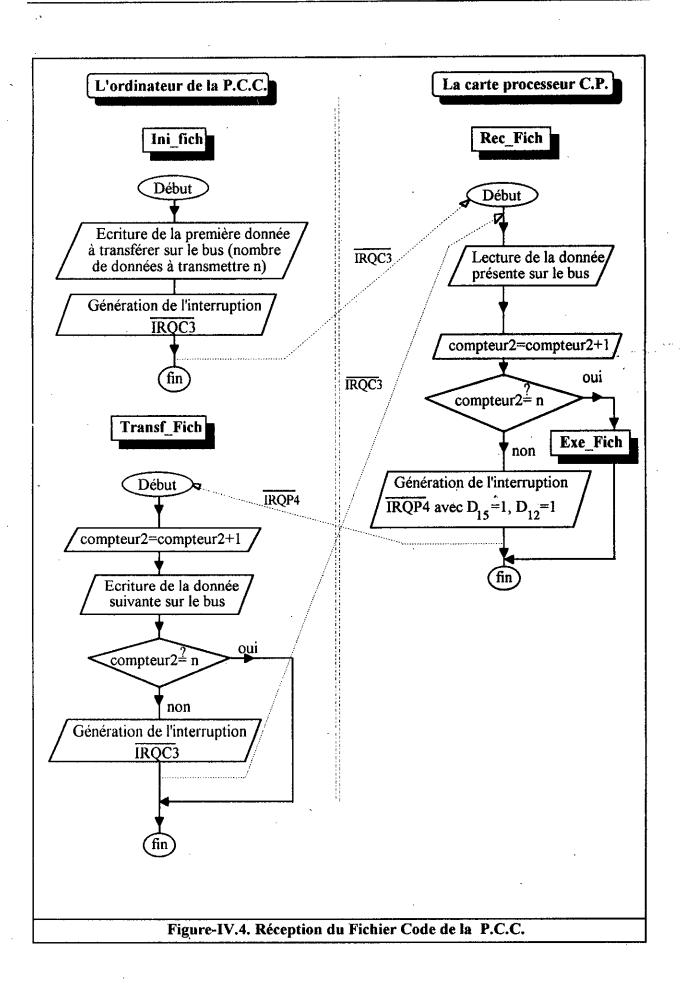

En plus, la *P.C.C.* transmet à l'*I.C.A.* la consigne fixant la valeur de la vitesse de défilement du fil-électrode, des paramètres permettant son initialisation et éventuellement un *fichier code.* Ce dernier, donne la possibilité à l'utilisateur de reprogrammer en assembleur l'*I.C.A.*

#### 2.1.2 Transfert de la P.O. vers la P.C.C.

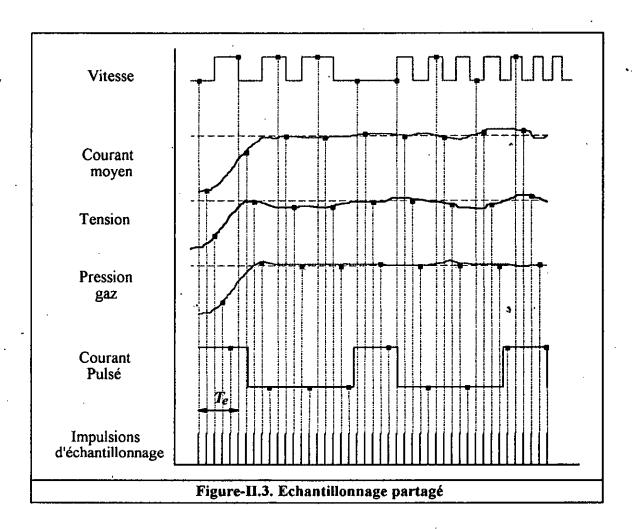

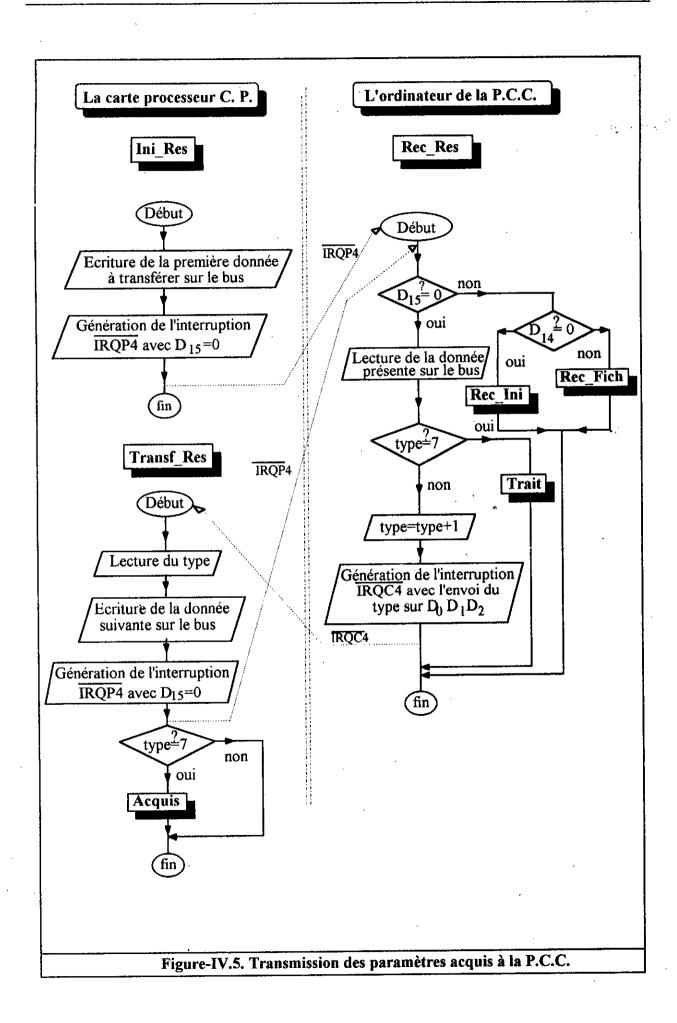

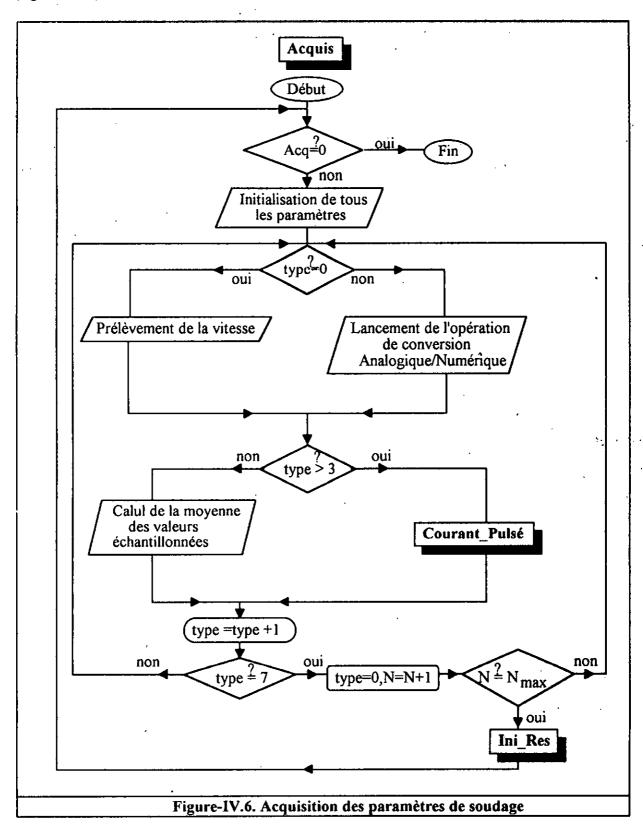

Après le traitement relatif à l'opération d'acquisition, l'I.C.A. transmet automatiquement à la P.C.C. les valeurs moyennes des paramètres de soudage acquis au niveau du M450 PS. Afin d'éviter une perte d'informations et pour économiser de l'espace mémoire, un échantillonnage partagé leur est appliqué. Il consiste a prélever durant la période de temps  $T_e$  un échantillon de l'ensemble des paramètres de soudage (figure II.3).

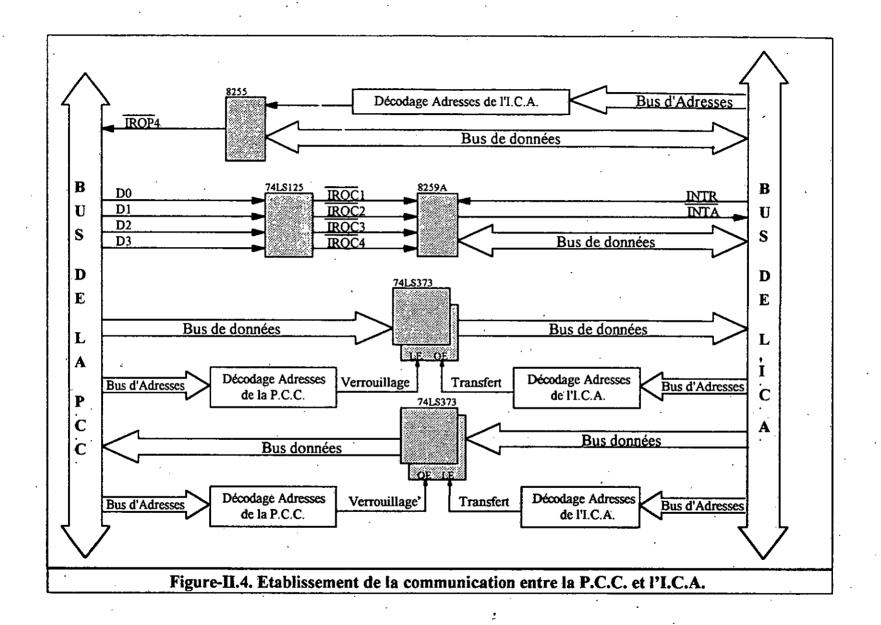

Afin d'établir la communication entre la P.C.C et la P.O. en évitant tout problème de conflit, nous utilisons des verrous associés à un système d'interruptions (figure II.4).

Le dialogue s'établit, dans le cas de cette communication, comme suit :

- 1. L'ordinateur de la *P.C.C.* (resp. *I.C.A.*) écrit la donnée à transmettre sur le verrou en le considérant comme un espace mémoire périphériques d'entrées/sorties.

- 2. L'ordinateur de la *P.C.C.* (resp. *I.C.A.*) envoie par la suite une interruption à l'*I.C.A.* (resp. ordinateur de la *P.C.C.*) signalant une présence de donnée sur le bus commun, la donnée étant verrouillée sur le latch.

- 3. L'I.C.A. (resp. ordinateur de la P.C.C.) se branche sur la routine de traitement d'interruption où elle trouve une commande de lecture du verrou contenant la donnée.

La donnée transmise de la P.C.C. vers l'I.C.A. peut être :

- un ordre,

- une consigne,

- un paramètre initial ou

- un élément du fichier code.

Par contre, la donnée transmise de l'I.C.A. vers la P.C.C. peut contenir des informations différentes. Les valeurs possibles de cette donnée sont :

- la valeur moyenne du paramètre de soudage acquis,

- une information utilisée pour le dialogue (comme un prêt à recevoir une donnée)

ou

- une information signalant une erreur grave,

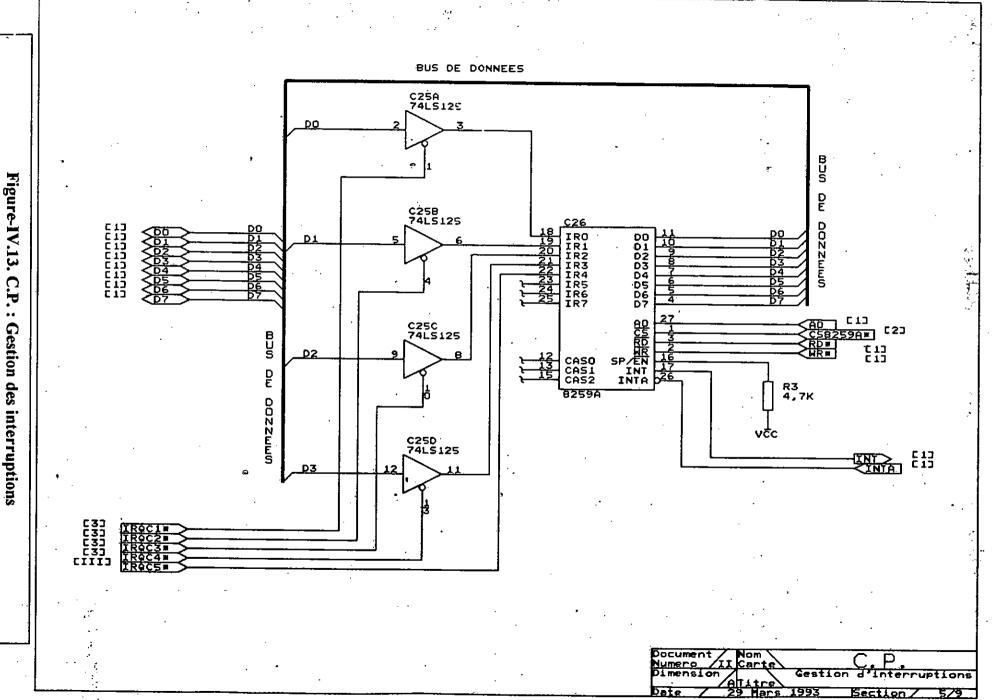

Le système d'interruption associé est constitué de quatre interruptions allant de la P.C.C. vers l' I.C.A.  $\overline{IRQC1}$ ,  $\overline{IRQC2}$ ,  $\overline{IRQC3}$  et  $\overline{IRQC4}$ . Par contre, nous ne disposons que d'une seule interruption  $\overline{IRQP4}$  dans l'autre sens.

Les autres interruptions sont disponibles sur le bus d'extension de l'ordinateur du bus de la P.C.C. que nous évitons d'utiliser afin d'adapter l'interface parallèle à un IBM XT ou AT.

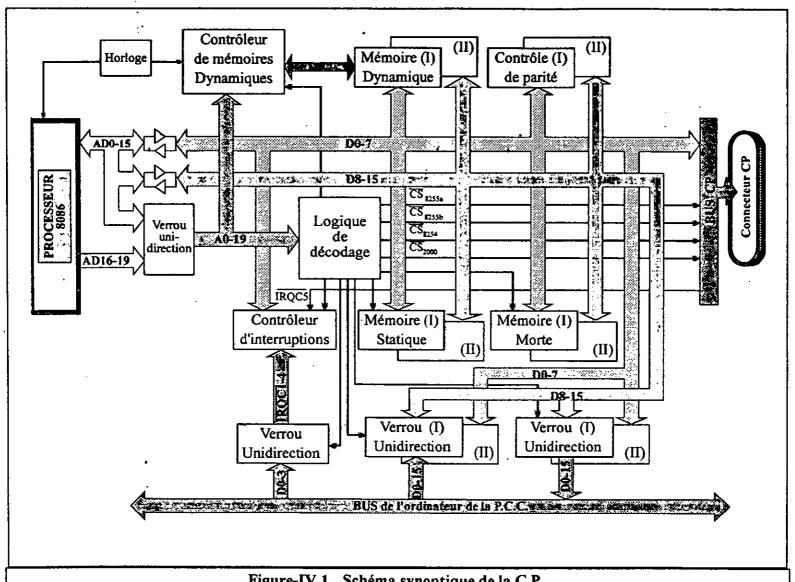

#### ♦ L'interruption IRQC1

Elle signale à l'I.C.A. que la donnée disponible au niveau du latch renferme, selon la valeur des bits de poids forts  $D_{15}D_{14}D_{13}$ , les consignes suivantes (tableau II.1):

- l'ordre de transmettre la valeur courant/vitesse à fixer au niveau du poste,

- l'ordre d'actionner/désactionner le commutateur de la torche de soudage pour faire démarrer le procédé ou l'arrêter totalement,

- l'ordre d'actionner ou non le commutateur d'ouverture des gaz et

- l'ordre de lancer ou d'interrompre l'opération d'acquisition des paramètres de soudage.

| D <sub>15</sub> | D <sub>14</sub> | D <sub>13</sub> | Fonction                                    |

|-----------------|-----------------|-----------------|---------------------------------------------|

| 0               | 0               | 0               | Arrêt de l'opération de soudage             |

| 0               | 0               | 1               | Lancement de l'opération de soudage         |

| 0               | 1               | 0               | Fermeture des Gaz                           |

| 0               | 1               | 1               | Ouverture des Gaz                           |

| 1               | 0               | 0               | Lancer l'opération d'acquisition            |

| 1               | 0               | 1               | Interrompre l'opération d'acquisition       |

| 1               | 1               | _               | $D_0$ - $D_{11}$ = consigne courant/vitesse |

Tableau-II.1. Fonctions de l'interruption IRQC1

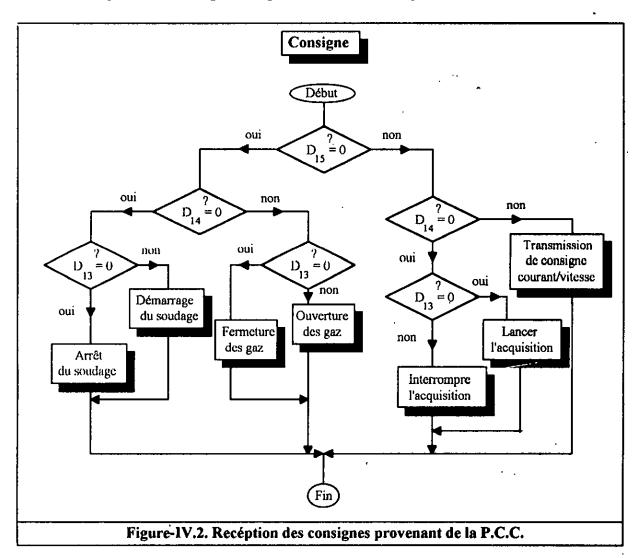

## ♦ L'interruption IRQC2

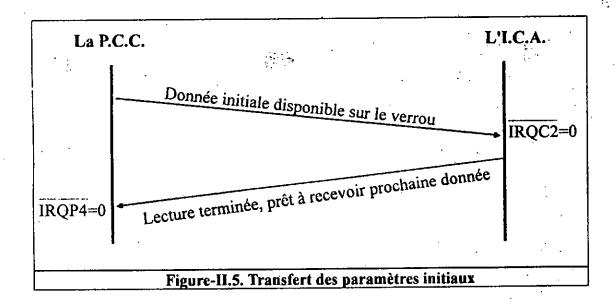

Cette interruption est utilisée en association avec l'interruption *IRQP4* allant vers la *P.C.C.* (figure II.5). Elle permet la transmission d'éléments utilisés pendant la phase d'initialisation appelés paramètres initiaux, telle que la valeur du nombre d'échantillons à prélever (cf. IV.2.2.1).

<sup>\*</sup> En mode synergique.

## ♦ L'interruption IRQC 3

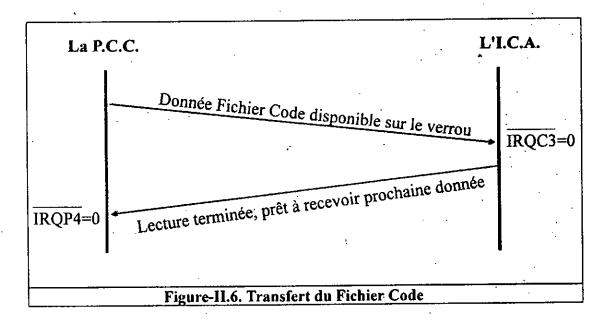

Comme pour  $\overline{IRQC2}$ , elle permet en association avec  $\overline{IRQP4}$  le transfert du *fichier* code par dialogue (figure II.6).

## ♦ L'interruption IRQC 4

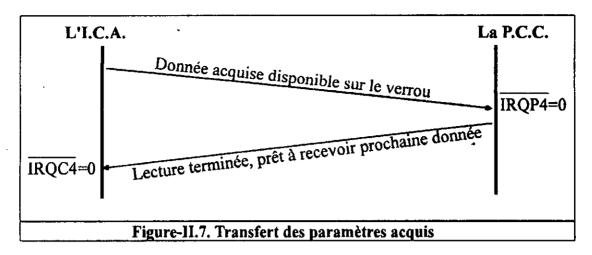

A la différence des deux précédentes interruptions,  $\overline{IRQC4}$  indique à l'I.C.A. que la P.C.C. est prête à recevoir un autre paramètre acquis par dialogue (figure II.7).

## ♦ Interruption de l'ordinateur de la P.C.C. (IRQP4)

Nous disposons d'une seule interruption allant vers la P.C.C. ( $\overline{IRQP4}$ ) que nous avons codifié pour bénéficier de toutes les fonctions de dialogue citées précédemment (tableau II.2). Les bits  $D_{14}$ - $D_{13}$ - $D_{12}$ , appelés encore type, différencient les paramètres de soudage acquis.

Tableau-II.2. Description des différentes fonctions de l'interruption IRQP4

| D <sub>15</sub> | D <sub>14</sub> | D <sub>13</sub> | D <sub>12</sub> | Fonction                                                                                                       |  |

|-----------------|-----------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------|--|

|                 | 0               | 0               | 0               | D <sub>0</sub> -D <sub>11</sub> = valeur moyenne de la vitesse                                                 |  |

|                 | 0               | 0               | 1               | D <sub>0</sub> -D <sub>11</sub> = valeur moyenne du courant                                                    |  |

|                 | 0               | 1               | 0               | $D_0$ - $D_{11}$ = valeur moyenne de la tension                                                                |  |

|                 | 0               | 1               | 1               | D <sub>0</sub> -D <sub>11</sub> = valeur moyenne de la pression du gaz                                         |  |

| 0               | 1               | 0               | 0               | D <sub>0</sub> -D <sub>11</sub> = valeur moyenne de la durée du niveau haut du courant pulsé (T <sub>h</sub> ) |  |

|                 | 1               | 0               | 1               | D <sub>0</sub> -D <sub>11</sub> = valeur moyenne de la durée du niveau bas du courant pulsé (T <sub>b</sub> )  |  |

|                 | 1               | 1               | 0               | D <sub>0</sub> -D <sub>11</sub> = valeur moyenne du niveau haut du courant pulsé (I <sub>h</sub> )             |  |

|                 | 1               | 1               | 1               | D <sub>0</sub> -D <sub>11</sub> = valeur moyenne du niveau bas du courant pulsé (I <sub>b</sub> )              |  |

| 1               | 0               | 0 -             | 0               | Prêt à recevoir le prochain paramètre initial (voir figure II.5)                                               |  |

|                 | 0               | 0               | 1               | Prêt à recevoir la prochaine donnée fichier (voir figure II.6)                                                 |  |

| 1               | 1               | 0               | 0               | Arrêt d'urgence local : erreur DRAM (NMI)                                                                      |  |

|                 | 1               | 0               | 1               | Arrêt d'urgence local : erreur division par zéro                                                               |  |

|                 | 1               | 1               | 0.              | Arrêt d'urgence local : erreur débordement                                                                     |  |

En plus, cette interruption est exploitée pour signaler un Arrêt d'Urgence Local (AUL). Ce dernier, peut survenir à la suite de l'apparition d'une erreur de parité ou d'erreurs graves (tels qu'un dépacement ou une division par zéro).

#### 2.2 Traitement et calcul

L'I.C.A. est exploitée pour effectuer les différents traitements et calculs suivants :

- Exécution d'un programme utilisateur écrit et compilé en code machine, au niveau de la P.C.C. permettant la reprogrammation de l'I.C.A. Nous l'avons nomé fichier code.

- Contrôle des différents circuits de conversion et d'échantillonnage.

- Calcul de la valeur moyenne de chaque donnée acquise.

- Détermination des caractéristiques (Ib, Ih, Tb, Th) du courant pulsé.

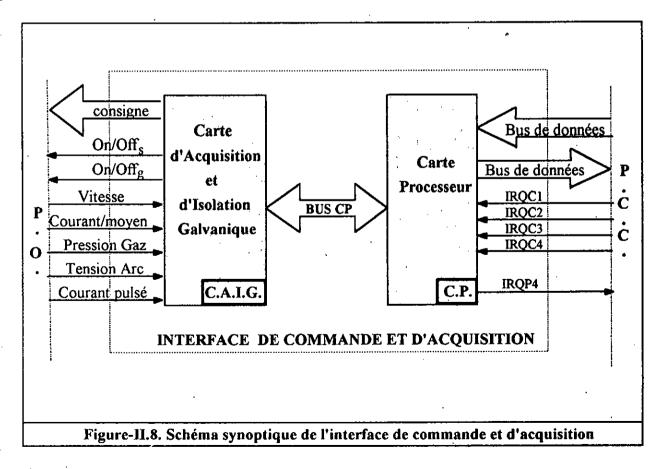

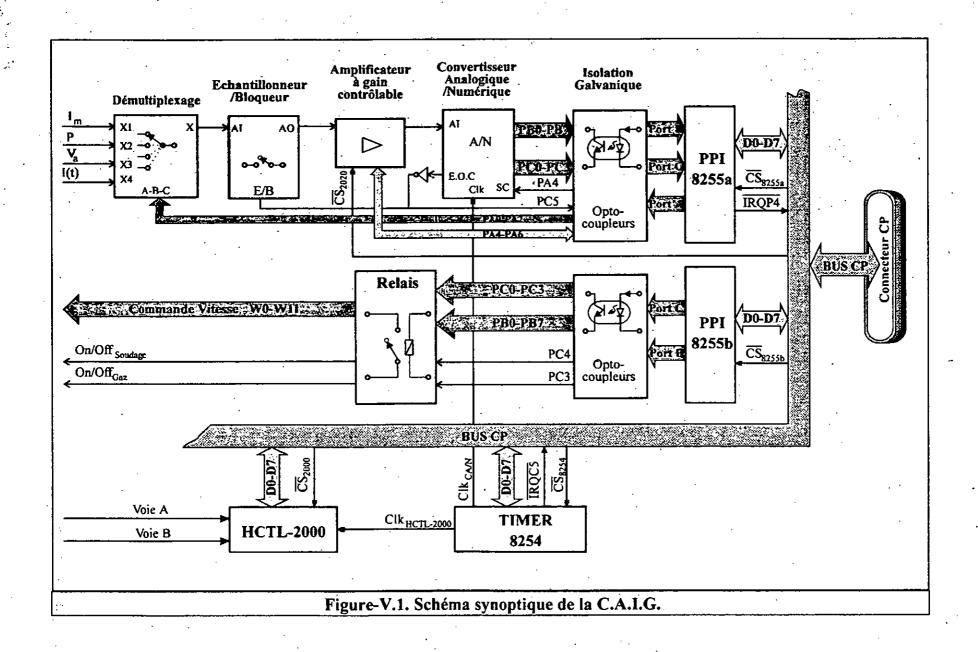

Afin de réaliser ces fonctions, l'I.C.A. est organisée selon le schéma synoptique de la figure II.8.

Elle est constituée de deux cartes, la C.P. et la C.A.I.G. :

- la C.P. (Carte Processeur), est une carte connectée sur le bus de l'ordinateur de la P.C.C. contenant un processeur et,

- la C.A.I.G. (Carte d'Acquisition et d'Isolation Galvanique), est une carte comprenant des circuits de conversion, des circuits d'isolation galvanique et des relais de commutation.

Dans les prochains chapitres nous présentons l'organisation matérielle et logicielle de la C.I.C. et de la C.P. ainsi que la structure de la C.A.I.G.

#### **BIBLIOGRAPHIE**

- [And-91] C. André, L. Fancelli

Etude d'une réalisation mixte (Asynchrone/Synchrone) d'un système

temps réel

APII, Automatique-Productique-Informatique Industrielle, revue RAIRO,

vol 25, n°2, 1991.

- [Yaz-92] H. Yazid

Contribution à la définition d'un environnement informatique pour un système de soudage assisté par ordinateur

Thèse de Magister, Centre de Développement des Technologies Avancées, CDTA, Mars 1992.

CHAPITRE

BOOK

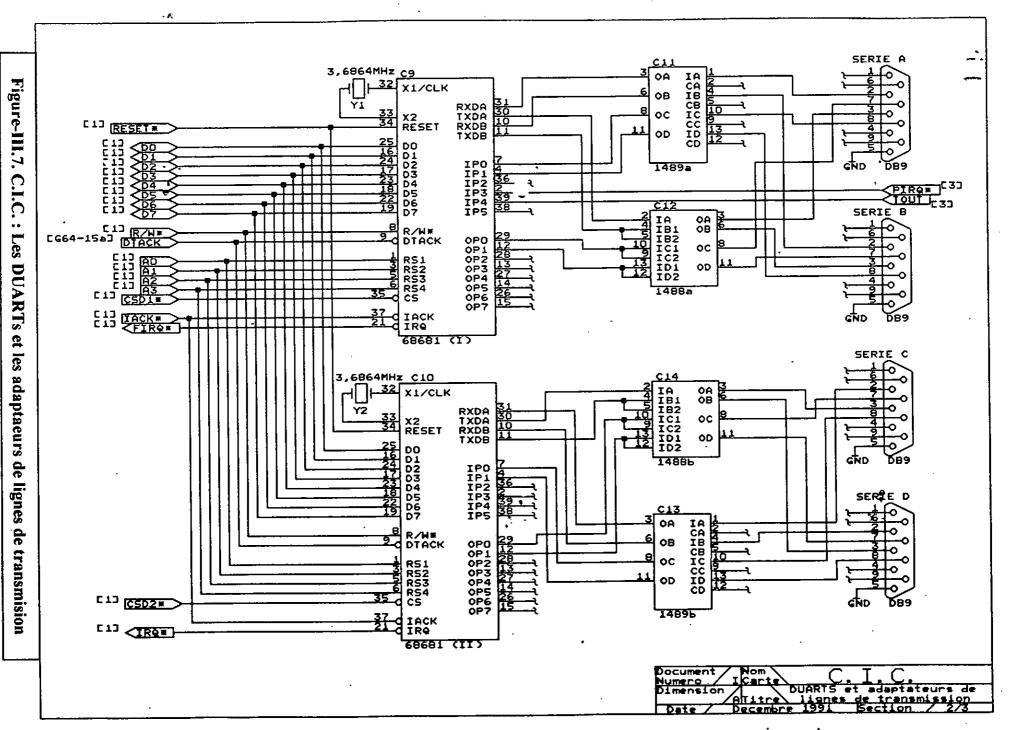

Carte Interface de Communication

La C.I.C. est installée sur le bus de l'ordinateur superviseur THOMSON. Elle est constituée essentiellement de deux double contrôleurs asynchrones de communication et d'une interface programmable parallèle. La C.I.C. bénéficie donc d'un port d'entrées/sorties parallèle et de quatre ports d'entrées/sorties sériels au standard RS 232C (annexe A) dont le canal A est exploité pour établir la communication avec la P.C.C.

#### 1. ARCHITECTURE MATERIELLE DE LA C.I.C.

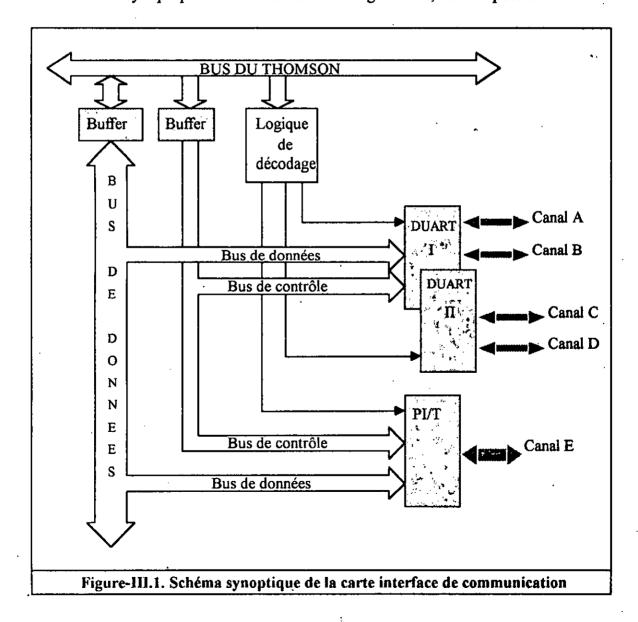

Le schéma synoptique de la C.I.C. donné en figure III.1, est composé de :

- deux doubles contrôleurs programmables de communication asynchrone

DUART.

- une interface parallèle PI/T,

- un buffer pour l'amplification et mémorisation du bus de données,

- un buffer pour l'amplification et mémorisation du bus de contrôle et

- une logique de décodage et des adaptateurs de lignes de transmission.

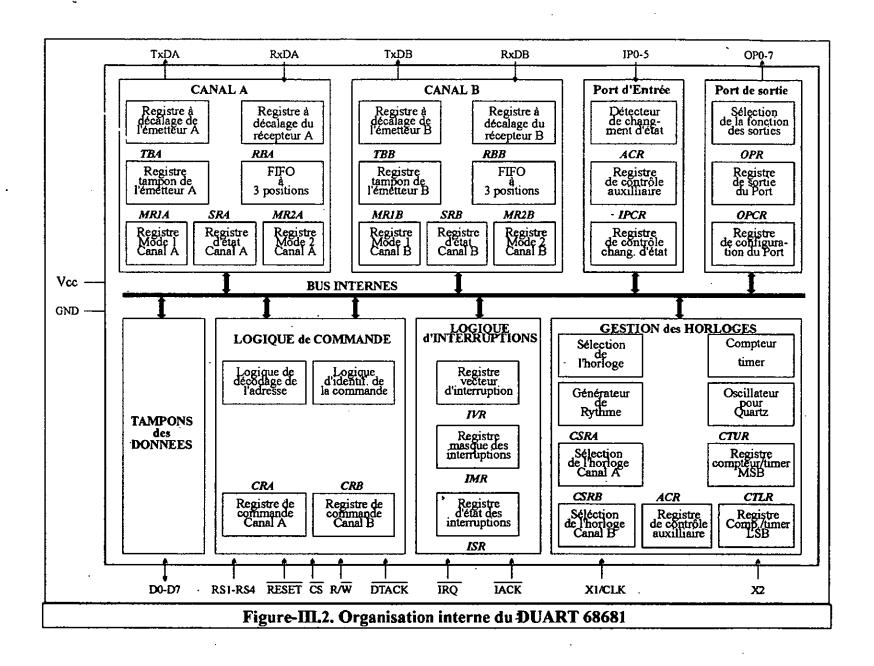

#### 1.1 Le DUART 68681 [Jau-85]

Le *DUART* regroupe deux canaux de communication asynchrone, chacun d'eux peut être exploité individuellement (figure III.2). Ce circuit convertit les données sérielles en données parallèles à la réception et il opère d'une manière inverse à l'émission. Il offre aussi une variété de fonctions à savoir, des fonctions de communication asynchrone, des fonctions ports et des fonctions de temporisation pour simplifier le programme de gestion de la communication.

#### ♦ Les fonctions de communication asynchrone

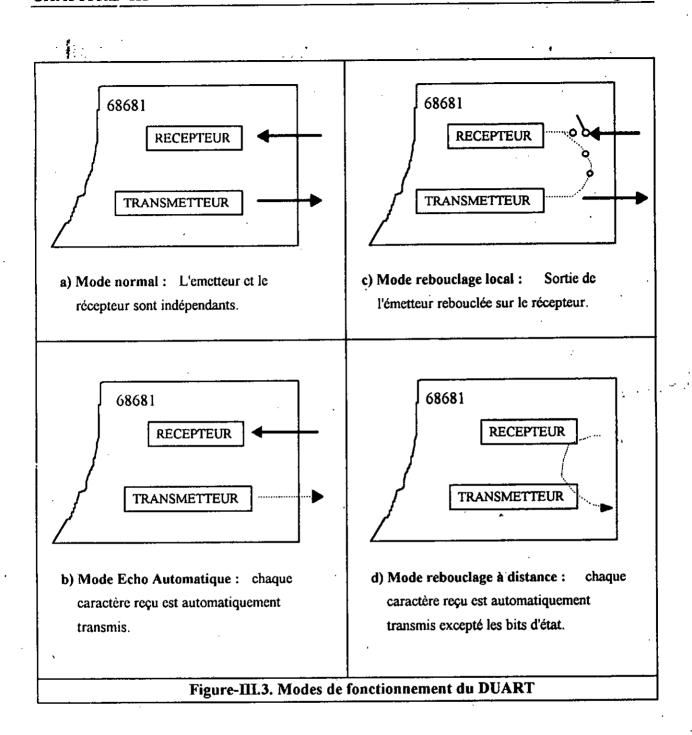

Chaque canal peut opérer selon quatre modes de fonctionnement (figure III.3) avec une vitesse de transfert choisie parmi dix-huit valeurs distinctes et une détection d'erreurs de communication par le contrôle de parité et de survitesse pour des applications réseaux.

Le *DUART* possède une gestion d'interruptions constituée de deux sources, l'une regroupant huit conditions masquables et l'autre renfermant cinq conditions séparées. Ce circuit permet aussi de faire une communication par contrôle de modem.

#### **♦** Les fonctions ports

Le **DUART** dispose :

- d'un port de sortie multifonction à huit lignes utilisées comme des lignes de sortie

à usage général ou pour la génération d'interruptions et

- d'un port d'entrée multifonction de six lignes utilisées comme des lignes de sortie

à usage général, comme horloge ou comme détecteurs de changement d'état.

## ♦ Les fonctions de temporisation

Ces fonctions donnent la possibilité d'effectuer un décomptage de nombres d'impulsions ou de générer des signaux carrés à une fréquence programmée.

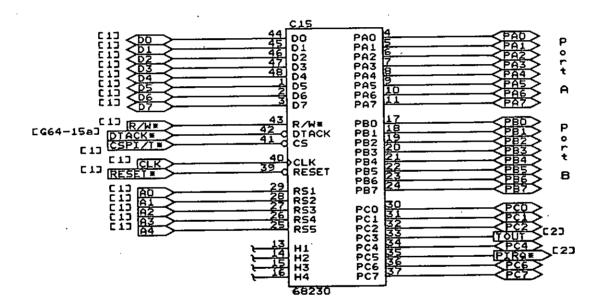

## 1.2 Le PI/T 68230 [Jau-85]

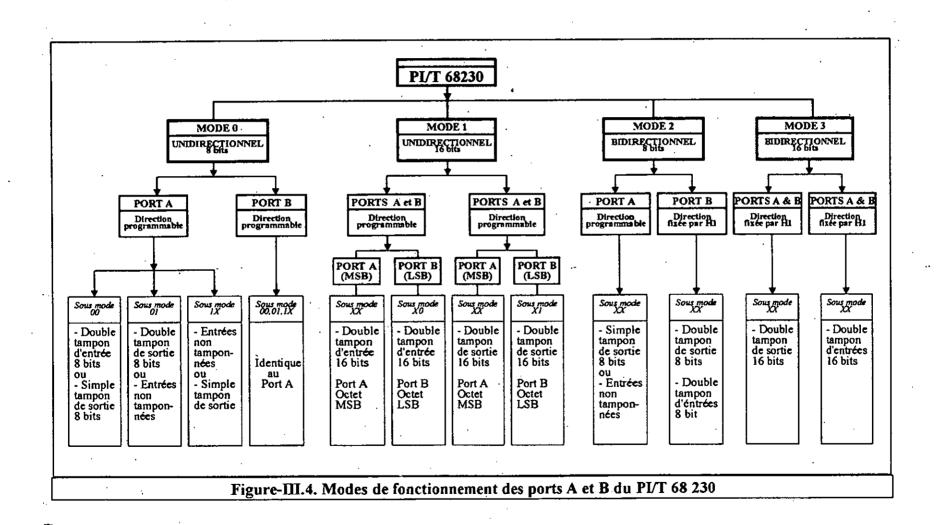

Le PI/T permet à la fois l'interfaçage parallèle et la temporisation.

#### ♦ L'interfaçage parallèle

Le 68230 renferme deux ports A et B pouvant être utilisés selon quatre modes (figure III.4), un port C multifonctions, quatre lignes de dialogue et deux lignes d'interruptions.

#### ♦ La temporisation

Le *PI/T* fournit à travers un temporisateur 24 bits un certain nombre d'outils de temporisation tels que :

- la génération d'interruptions périodiquement ou après un délai,

- l'élaboration de signaux carrés et

- la mesure d'un temps écoulé.

Le 68230 permet une gestion matérielle et logicielle d'interruptions vectorisées ou autovectorisées. Il possède une horloge interne prédivisée par 32 et une horloge externe avec ou sans prédivision par 32.

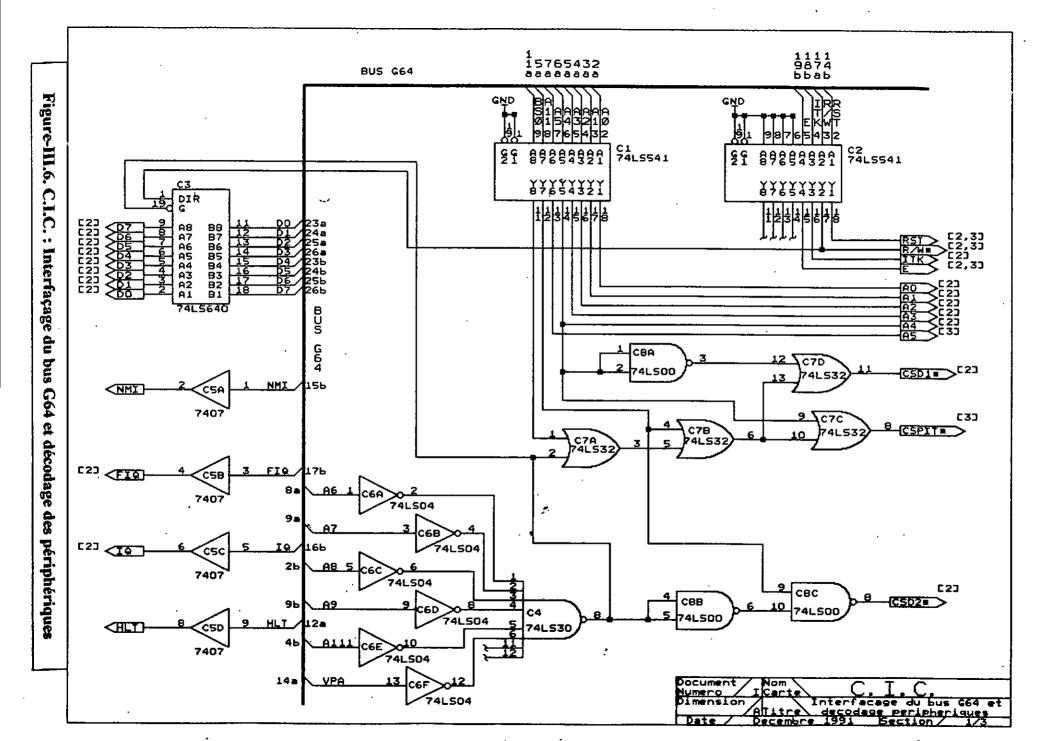

### 1.3 Logique de décodage

Selon l'organisation de l'espace mémoire du superviseur THOMSON, la zone d'adressage réservée aux périphériques asynchrones s'étend de l'adresse FF 000H à l'adresse FF 7FFH et pour les périphériques synchrones de l'adresse FF 800H à l'adresse FF FFFH [THO]. Afin de respecter cette organisation tout en sachant que le DUART possède 16 registres internes et le PI/T en possède 32, nous avons fixé l'adressage des périphériques suivant le tableau III.1, le PI/T étant utilisé en mode synchrone. La logique câblée correspondante est illustrée dans la figure III.6.

Tableau-III.1. Adressage des périphériques de la C.I.C.

| Peripheriques d'entrees/sorties | Adresse en hexadecimal |

|---------------------------------|------------------------|

| DUART (I)                       | FF 000 - FF 00F        |

| DUART (II)                      | FF 010 - FF 01F        |

| . PI/T                          | FF 800 - FF 81F        |

#### 1.4 Gestion des interruptions de la C.I.C.

Le système superviseur permet deux interruptions utilisateurs  $\overline{IRQ}$  et  $\overline{FIRQ}$ . L'interruption  $\overline{IRQ}$  est une ligne reliée à l'entrée du microprocesseur, son passage à l'état bas provoque le traitement de la séquence d'interruption dont le vecteur est FFF8H-FFF9H. Par contre le passage à un niveau bas sur la ligne  $\overline{FIRQ}$  entraîne le traitement de la séquence d'interruption rapide (i.e. Il y a une sauvegarde dans la pile du compteur programme et du registre code condition) au vecteur FFF6H-FFF7H [THO-85].

Nous utilisons  $\overline{FIRQ}$  comme une entrée de demande d'interruption du DUART (I) et  $\overline{IRQ}$  comme une entrée de demande d'interruption du DUART (II) (section 2/3-I). Par contre, le PI/T qui peut fonctionner en mode auto-vectorisé, envoie une demande d'interruption port à travers la ligne IP2 et une interruption timer à travers IP3 du DUART (I). En effet, les ligne IP0-IP3 du DUART peuvent être utilisées comme détecteur de changement d'état [Jau-85].

#### 2. ORGANISATION LOGICIELLE

Les *DUARTs* et le *PI/T* sont initialisés et configurés au moyen de routines assembleur 68000 écrites au niveau du superviseur. Ces routines gèrent les sources d'interruptions et elles permettent un choix de la vitesse de transmission, du format du caractère de transmission et du mode de transmission.

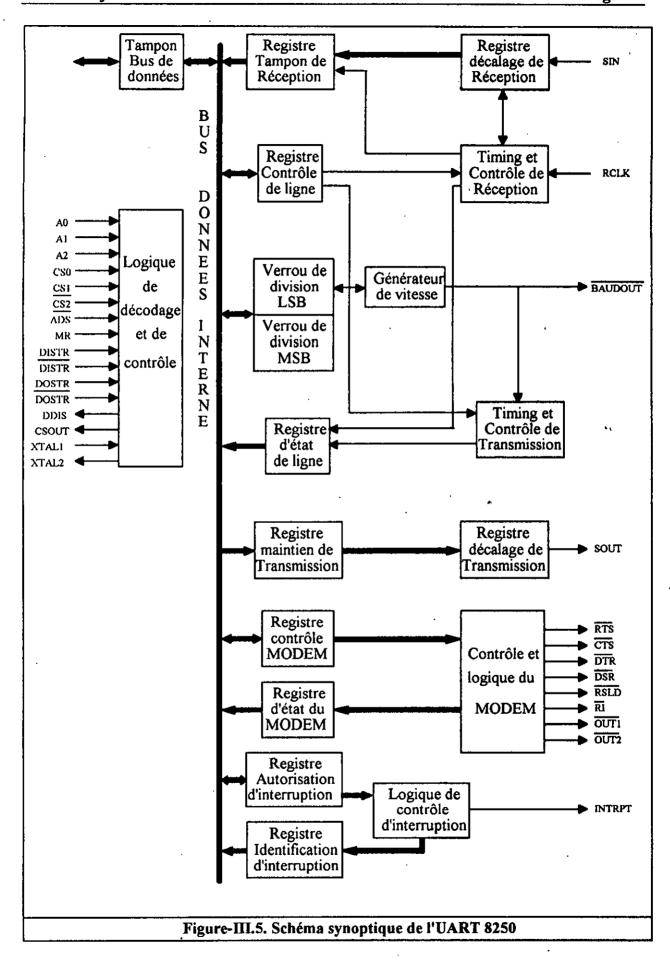

## 3. LE PORT SERIE DE LA PARTIE COMMANDE ET CONTROLE (8250)

La gestion de la sortie série de la *P.C.C.* se fait au moyen du 8250 d'Intel [WEST-80]. C'est un emetteur récepteur asynchrone universel (UART). Son schéma synoptique est présenté dans la figure III.5. Il convertit des données parallèles en données sérielles à l'émission, et à la réception l'opération est inversée. L'information sérielle transmise est constituée d'un bit stop suivi de cinq à huit bits de données avec ou sans parité et de un, un et demi ou deux bits stop.

Les registres internes de l'*UART* permettent de programmer les différents types d'interruption, le contrôle modem et le format du caractère. L'état du 8250 peut être consulté à tout moment. L'*UART* permet de programmer la vitesse de transmission en divisant de 1 à 2<sup>16</sup> le signal de l'horloge interne. Il peut fonctionner en mode interruptible on par scrutation.

Après avoir présenté la communication entre la P.C.C. et le système superviseur, nous passons à l'interfaçage de cette dernière à la P.O. par l'intermédiaire de l'I.C.A. dont les fonctions et la structure sont données dans les prochains chapitres.

## BIBLIOGRAPHIE

[Jau-85] Patrick Jaulent

Circuits périphériques de la famille 68 000

Edition EYROLLES, 1985.

[THO-85] THOMSON SEMICONDUCTEURS

Manuel d'utilisation

EFS-ISY 3/4 machine 16 bits G64+ avec OS9/68000, Ref. F008.

Julliet, 1985.

[WEST-80] WESTERN DIGITAL CORPORATION

WD8250 Asynchronous Communications Element

1980.

Schémas d'implantation de La Carte Interface de Communication

Parallele/Timer PI/T Section/ 3/3

Figure-III.8. C.I.C.: Interface Parallèle/Timer(PI/T)

· .

•

## CHLAPITRE

MW

Interface de Commande et d'Acquisition: Carte Processeur

Pour réaliser toutes les fonctions introduites au chapitre III, la conception de la carte processeur (C.P.) se décompose en deux étapes, l'étape de conception matérielle et celle du développement logicielle correspondant.

#### 1. ORGANISATION MATERIELLE DE LA C.P.

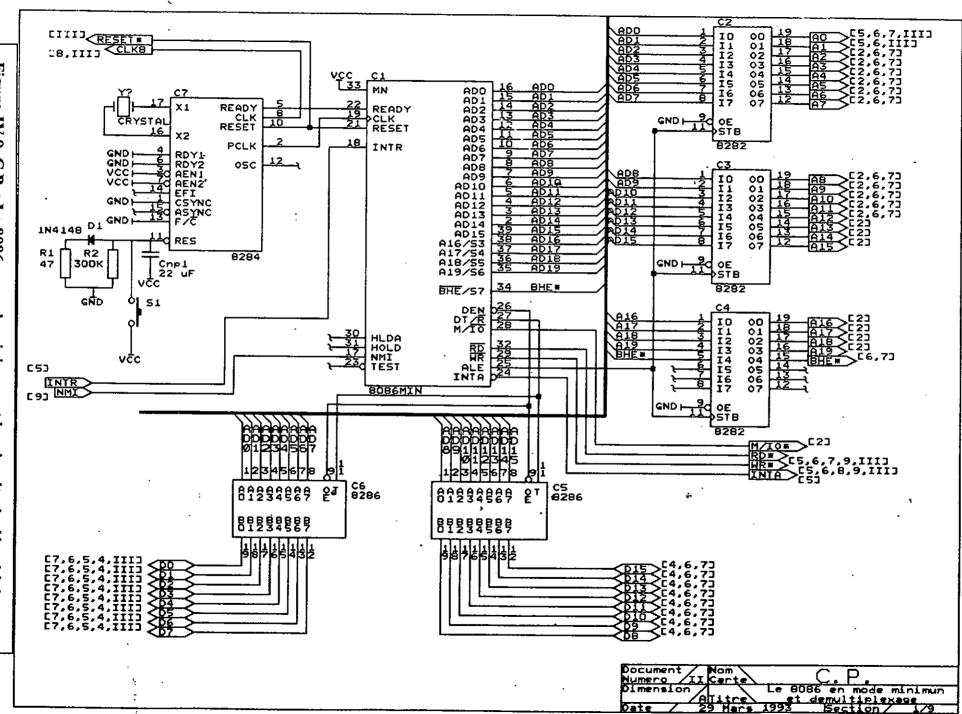

La C.P. est une carte basée sur un processeur 16 bits travaillant en mode minimum. Elle peut être connectée à un bus compatible PC IBM/XT ou PC IBM/AT.

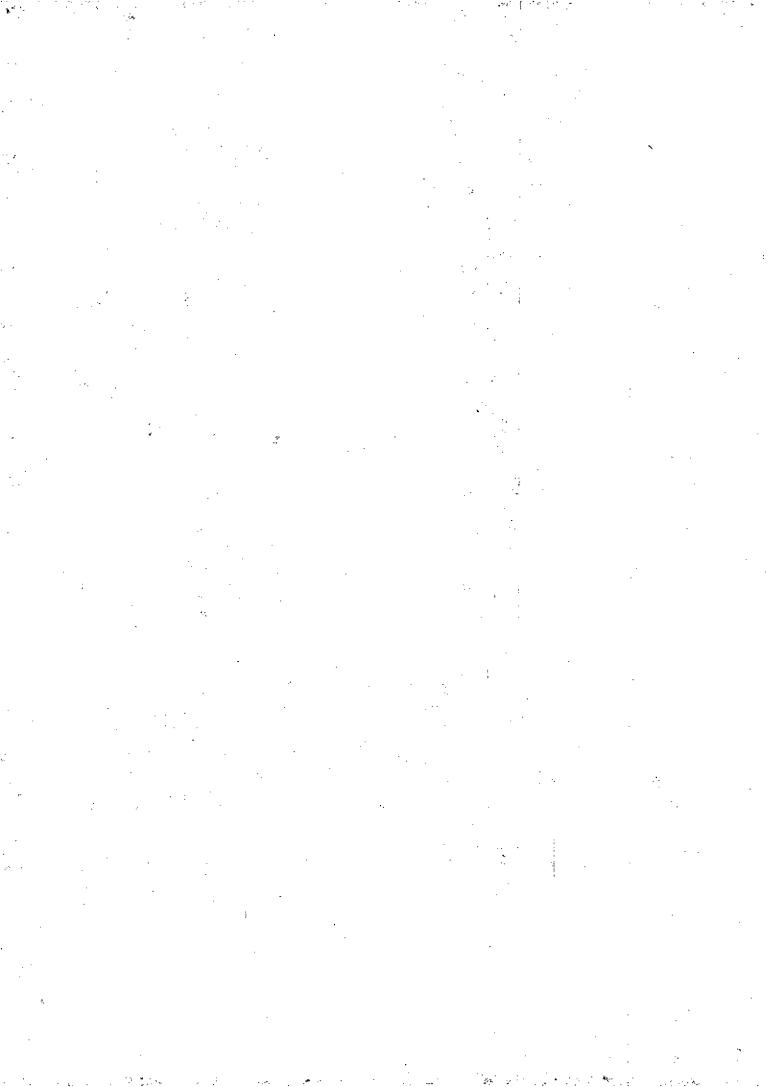

Le tableau IV.1 présente ses caractéristiques et la figure IV.1 illustre son schéma synoptique.

#### Tableau-IV.1. Caractéristiques de la carte processeur

- 1. Processeur principal Intel 8086 à quatre MHz.

- 2. Capacité mémoire morte de huit Koctets.

- 3. Capacité mémoire vive statique de quatre Koctets.

- 4. Capacité mémoire vive dynamique de cent vingt-huit Koctets avec parité avec possibilité d'extension à deux cents cinquante-six Koctets

- 5. Huit niveaux d'interruptions vectorisées.

Dans ce qui suit, nous présentons les détails de conception des différentes parties de la C.P. à savoir le démultiplexage des bus, les circuits générateur d'horloge, l'organisation mémoire statique et dynamique et la gestion des interruptions.

Figure-IV.1. Schéma synoptique de la C.P.

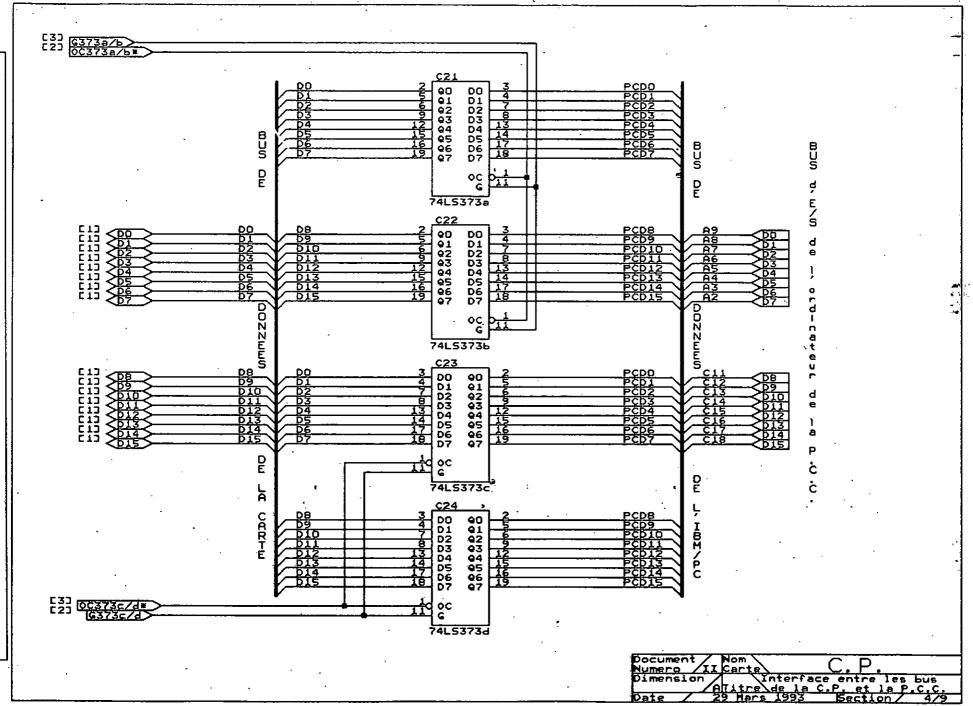

#### 1.1 Démultiplexage du bus

Le processeur 8086 (C1 de la figure IV.9) possède 16 lignes contenant en même temps le bus de données et une partie du bus d'adresses. Pour distinguer entre les deux trus, nous établissons un démultiplexage. Nous utilisons des verrous pour le bus d'adresses et le signal ALE commande leurs échantillonnage et verrouillage. Pour le bus de données, nous utilisons des transmetteurs commandés par les signaux DEN et DT/R (figure IV.9) [Lil-86].

# 1.2 Circuits RAZ et générateur d'horloge

Le générateur d'horloge *Intel 8284* (C7 de la figure IV.9) fournit, par l'utilisation d'un quartz de 24 MHz, un signal de remise à zéro et plusieurs signaux d'horloge [Lil-86], à savoir :

- une impulsion de RAZ permettant l'initialisation de la carte C.P.,

- un signal horloge à une cadence de 4 MHz exploité par le processeur qui est disponible sur la broche PCLK, et

- un signal horloge de 8 MHz utilisé par les circuits périphériques et employé pour le rafraîchissement de l'espace mémoire dynamique. Il est disponible sur la sortie CLK.

# 1.3 Logique d'interruption non masquable

L'interruption non masquable *NMI* du 8086 est utilisée pour traiter les erreurs de parité de la mémoire dynamique de la *C.P.* La source d'interruption est le signal produit par le circuit qui calcule la parité mémoire et détecte les erreurs (C38 et C39 de la figure IV.17). En cas d'erreurs l'interruption  $\overline{IRQP4}$  est générée pour signaler un *AUL*.

#### 1.4 Mémoire de la C.P.

La mémoire de la C.P. est constituée de :

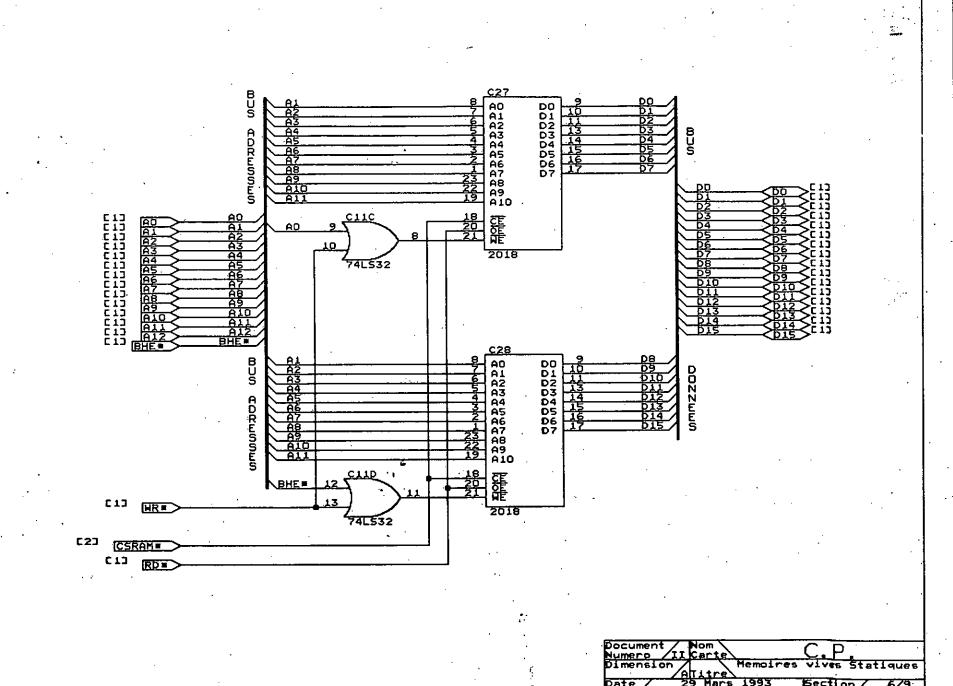

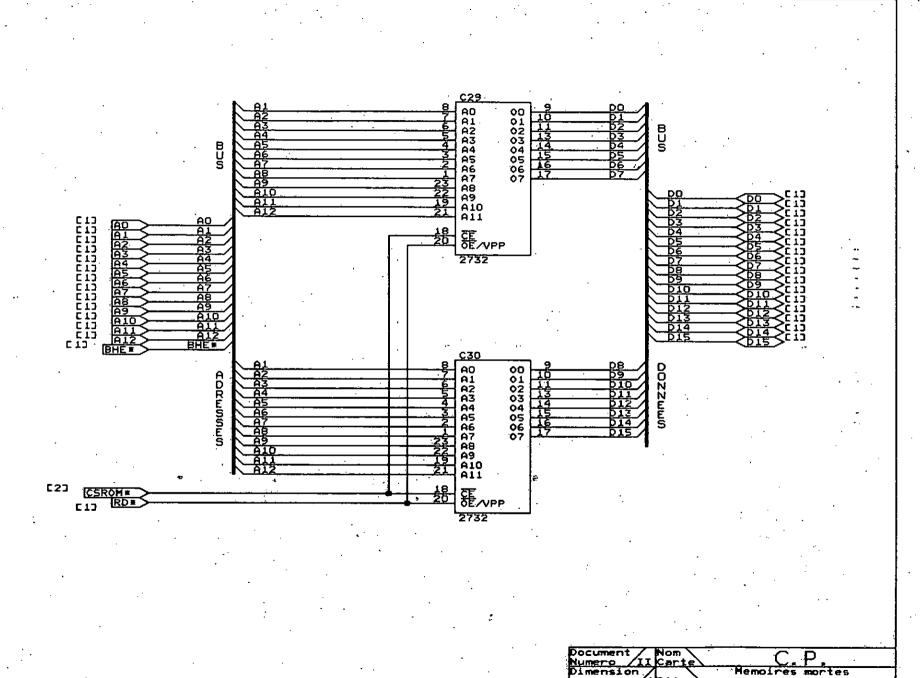

- huit Koctets d'*EPROM* fournis par deux circuits 2732 (4 Ko), l'un pour les octets de poids faibles et l'autre pour les octets de poids forts,

- quatre Koctets de RAM fournis par deux circuits 2128 (2 Ko) et

- cent vingt-huit Koctets de données disponibles sur deux TMS 4164EC8 avec possibilité d'extension à deux cents cinquante-six Koctets.

La mémoire morte doit être située en haut de l'espace adresses et la mémoire vive en bas de cet espace, car après une RAZ, le processeur cherche sa première instruction à l'adresse FFFF0H où il trouve une instruction de branchement. La structure de l'espace mémoire de la carte est présentée dans le tableau IV.2.

| Mémaire | A 19 | A <sub>18</sub> | A <sub>17</sub> | $\mathbf{A}_{16}$ | A <sub>15</sub> | A <sub>14</sub> | A <sub>13</sub> | A <sub>12</sub> | A <sub>11</sub> -A <sub>0</sub> | Zone d'adressage |

|---------|------|-----------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|---------------------------------|------------------|

| EPROM   | 1    | 1               | 1               | 1                 | 1               | 1               | 1               | -               | -                               | FE000H-FFFFFH    |

| RAM     | 0    | 0               | 0               | 0                 | 0               | 0               | 0               | 0               | =                               | 00000H-00FFFH    |

| DRAM    | 0    | 1               | _               | _                 | -               | _               | -               |                 | -                               | 40000H-7FFFFH    |

Tableau-IV.2. Adressage mémoire de la carte

La mémoire morte contient les programmes de gestion de la C.P. tandis que la mémoire vive statique renferme les données nécessaires au déroulement de ces programmes.

# 1.4.1 Organisation de la mémoire morte

La mémoire morte contient les programmes résidents, comportant les routines d'interruption de l'unité centrale\*, les routines d'interruption du contrôleur, le programme de traitement et le programme d'initialisation de la *C.P.* (tableau IV.3).

Il faut noter que quelque routines d'interruption de l'unité centrale permettent de générer une interruption vers la P.C.C. afin de signaler un AUL.

# 1.4.2 Organisation de la mémoire vive

La mémoire vive statique est exploitée comme espace de données pour les programmes résidents (tableau IV.4). Par contre, la mémoire vive dynamique est laissée à la disposition de l'utilisateur.

<sup>\*</sup> Ces interruptions sont appelées directement par l'unité centrale [Hau-88].

Tableau-IV.3. Organisation de la mémoire morte

| Programme                     | Nom      | Fonction                                                                  |  |  |  |  |  |  |  |  |

|-------------------------------|----------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Programme<br>d'initialisation | Init     | Initialisation de la C.P.                                                 |  |  |  |  |  |  |  |  |

| Programme de traitement       | Acquis   | Acquisition et calcul de la moyenne progressive des paramètres de soudage |  |  |  |  |  |  |  |  |

|                               | Div_Z    | Division par zéro                                                         |  |  |  |  |  |  |  |  |

| Routines                      | Pas      | Exécution pas à pas                                                       |  |  |  |  |  |  |  |  |

| d'interruption                | EDRAM    | Erreur dans la DRAM                                                       |  |  |  |  |  |  |  |  |

| de l'Unité                    | Break_P  | Point d'arrêt (test programme)  Erreur de débordement                     |  |  |  |  |  |  |  |  |

| Centrale                      | Deb      |                                                                           |  |  |  |  |  |  |  |  |

|                               | Cop_Ecr  | Copie d'écran                                                             |  |  |  |  |  |  |  |  |

| Routines                      | Consigne | Réception des consignes provenant de la<br>P.C.C. (IRQCI)                 |  |  |  |  |  |  |  |  |

| d'interruption                | Rec_Ini  | Réception des paramètres initiaux (IRQC2)                                 |  |  |  |  |  |  |  |  |

| du contrôleur                 | Rec_Fich | Réception du fichier écrit en code machine (IRQC3)                        |  |  |  |  |  |  |  |  |

| (8259A)                       | Tran_Res | Transfert des résultats de l'acquisition (TRQC4)                          |  |  |  |  |  |  |  |  |

|                               | Timer    | Lecture du timer (cf. V.3) ( <i>IRQC5</i> )                               |  |  |  |  |  |  |  |  |

0070-007F

0080-009F

| Contenu                                                | Adresse (en hexa) |

|--------------------------------------------------------|-------------------|

| Vecteurs d'interruptions de l'unité centrale           | 0000-001F         |

| Vecteurs d'interruptions du contrôleur                 | 0020-003F         |

| Résultats de l'acquisition à transférer vers la P.C.C. | 0040-004F         |

| Données employées par les programmes résidents         | 0050-005F         |

| Valeurs des paramètres initiaux                        | 0060-006F         |

Tableau-IV.4. Organisation de l'espace mémoire statique

### 1.4.3 Rafraîchissement de la mémoire dynamique et contrôle de parité

Données utilisées par le programme d'acquisition

Espace utilisé par la pile

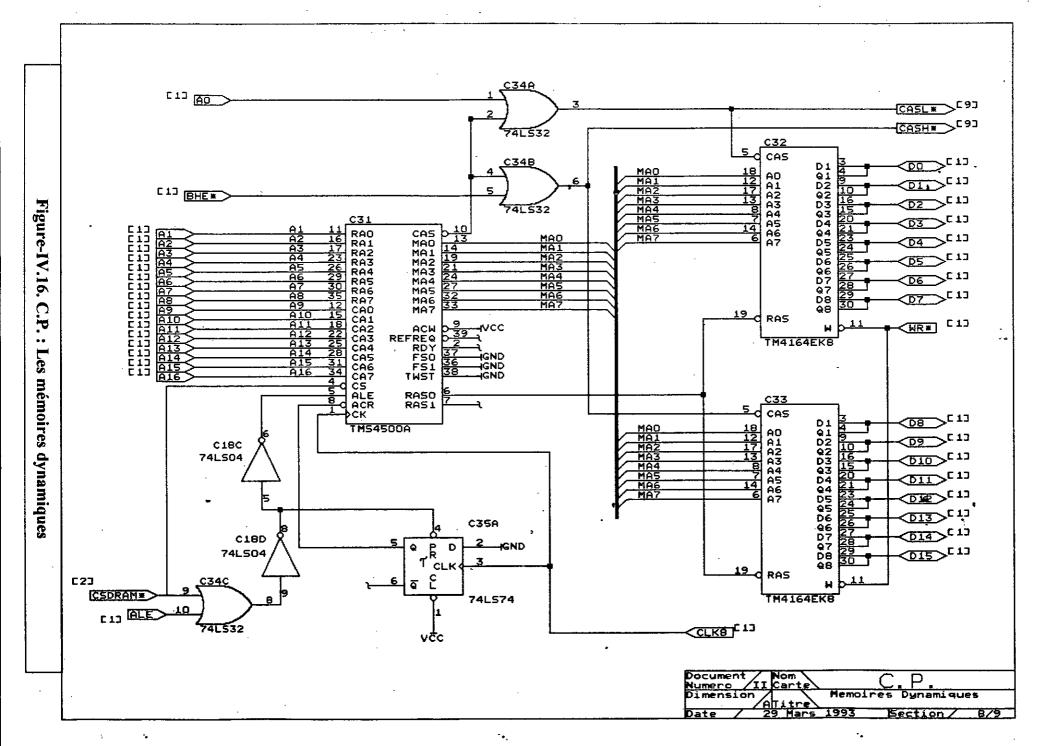

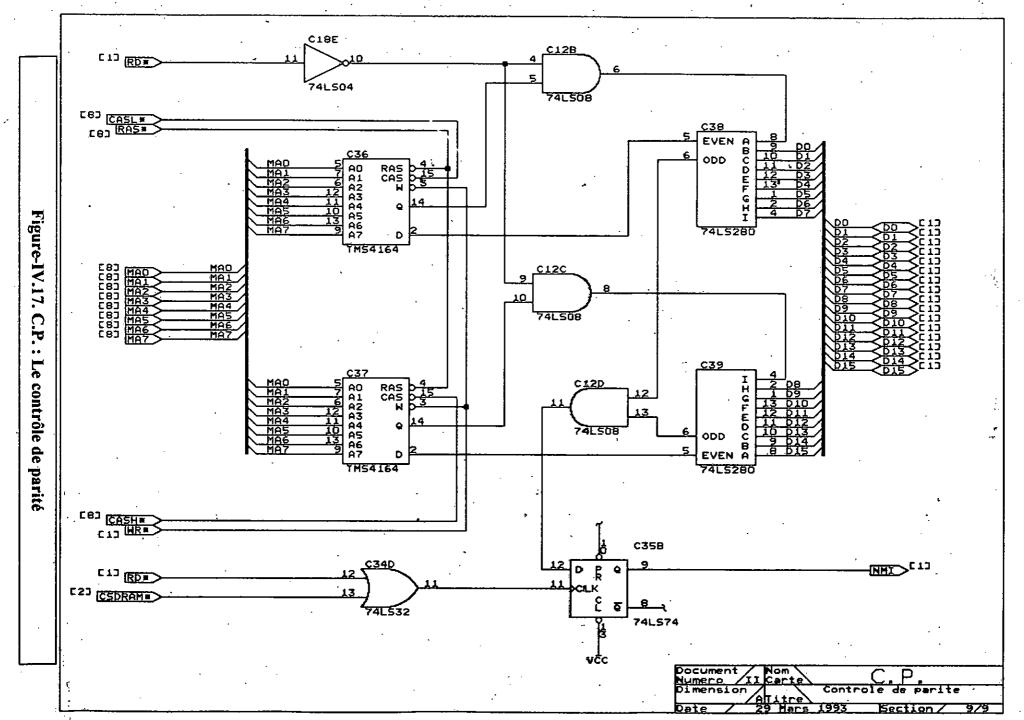

La C.P. dispose d'un espace de 128K octets de RAM Dynamiques TMS 4164EC8. Ce type de mémoire est volatile, ce qui nécessite un rafraîchissement périodique toutes les 4 millisecondes. Pour des raisons d'encombrement, il est impossible de mettre des boîtiers de DRAM dans de grands circuits. En effet, il faut dans ce cas, 16 lignes d'adresses, 2 lignes de lecture/écriture, 1 ligne de sélection de boîtier, 2 lignes d'alimentation et 1 ligne de donnée, ce qui correspond à un boîtier de 22 broches de surface  $\cong$  de 0,72 in<sup>2</sup>. Par conséquent la mémoire dynamique TMS 4164EC8 est organisée sous forme de tableau (256 × 256). Cette disposition réduit les besoins du bus d'adresses à 8 lignes, mais elle nécessite deux autres lignes pour verrouiller l'adresse [Cle-86]. Le contrôle des deux lignes en question ainsi que le multiplexage sont assurés par un autre circuit spécialisé, le TMS 4500A [TEX-82] (figure IV.16).

La difficulté associée aux *DRAMs* au cours de leur fabrication, est le problème de rayonnement émis par le matériau d'encapsulement. En effet, la valeur de chaque bit peut être troublée par cette radiation [Cle-86]. La solution à ce problème, est d'utiliser en supplément des mémoires dynamiques *TMS 4164* organisées en Kbit pour détecter ces erreurs par un contrôle de parité dont le principe de fonctionnement est le suivant :

Le circuit 74LS280 (C38 et C39 de la figure IV.17) fournit une sortie de parité paire et une autre de parité impaire calculées sur les neuf bits de données présentes à ses broches A-H. La génération de la parité se fait sur les huit bits de la donnée et sur le bit de parité calculé pendant l'opération d'écriture. En d'autres termes, pendant un cycle d'écriture la porte AND (C12B pour le poids faible et C12C pour le poids fort de la figure IV.17) est non valide et le bit de parité calculé sur les huit bits de données est enregistré dans le boîtier mémoire (C36 pour le poids faible et C37 pour le poids fort de la figure IV.17).

Lors du cycle de lecture, la porte AND est validée et le bit de parité précédemment calculé sur l'octet est comparé avec la parité présente. Cette valeur est enregistrée au front montant de l'horloge de la bascule D (C35B de la figure V.17), quand le boîtier de la mémoire dynamique est sélectionné en lecture [Cia-85].

Dans le cas d'une erreur, une impulsion niveau bas est envoyée à la logique d'interruption non masquable *NMI* qui prévient l'utilisateur à travers l'allumage d'une *LED* (figure V.9) et génère un *AUL*.

L'accès aux mémoires ainsi qu'aux périphériques est réalisé par l'emploi de la logique de décodage qui suit.

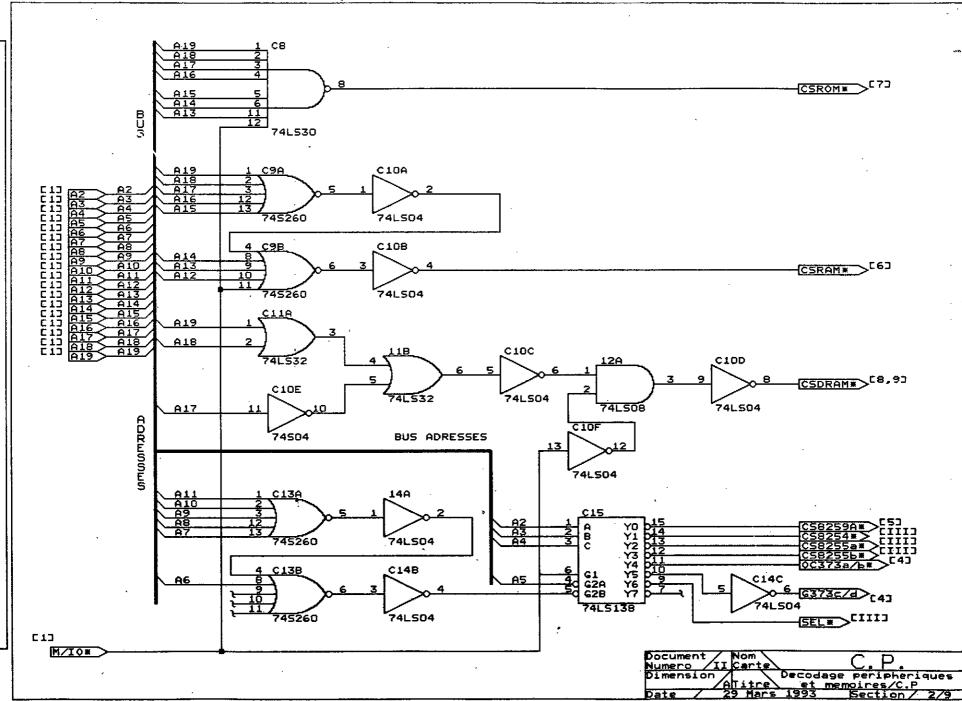

# 1.5 Décodage d'adresses mémoires et périphériques

La carte C.P. regroupe la logique de décodage des circuits périphériques de la carte C.P. et celle de l'ordinateur de la P.C.C. Pour les périphériques de la carte C.P., nous adoptons la logique de décodage présentée à la figure IV.10. L'adressage se fait par adressage distinct [Lil-86] dans la zone 0000H à FFFFH selon le tableau IV.5.

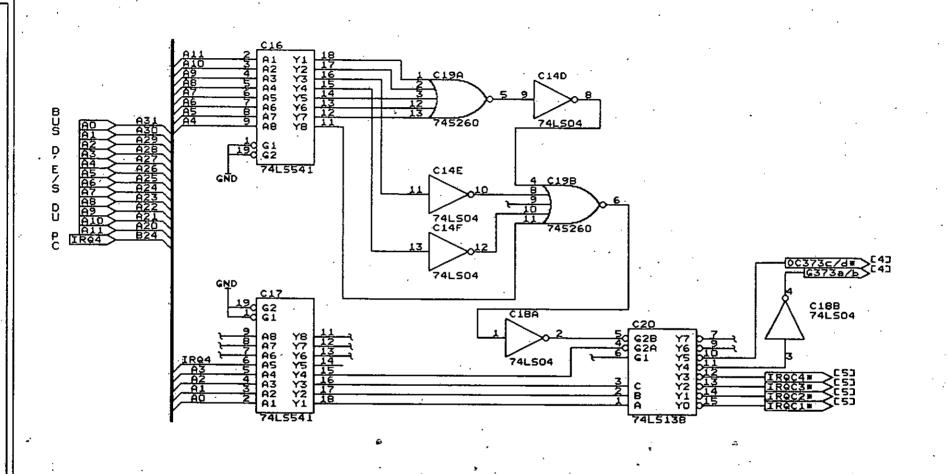

Sur la C.P., nous avons également une partie relative au décodage adresses des périphériques de l'ordinateur de la P.C.C. Celle-ci est utilisée pour identifier les interruptions ainsi que les circuits d'aiguillage entre le bus de la P.C.C. et celui de la C.P. (figure IV.11).

018H-019H

HCTL 2000

|               |                   |                   | . – |    |    |                  |    |    |                |    |                  |                |          |

|---------------|-------------------|-------------------|-----|----|----|------------------|----|----|----------------|----|------------------|----------------|----------|

| Peripheriques | $\mathbf{A}_{11}$ | $\mathbf{A}_{10}$ | A,  | AR | A, | $\mathbf{A}_{6}$ | A, | A. | $\mathbf{A_3}$ | Α, | $\mathbf{A}_{i}$ | $\mathbf{A}_0$ | Adresse  |

| 8259A         | 0                 | 0                 | 0   | 0  | 0  | 0                | 0  | 0  | 0              | 0  | 0                | •              | 000-001H |

| 8254*         | 0                 | 0                 | 0   | 0  | 0  | 0                | 0  | 0  | 0              | 1  | •                | •              | 004-007H |

| 8255a*        | 0                 | 0                 | 0   | 0  | 0  | 0                | 0  | 0  | 1              | 0  | •                | •              | 008-00BH |

| 8255b*        | 0                 | 0                 | 0   | 0  | 0  | 0                | 0  | 0  | 1              | 1  | -                | -              | 00C-00FH |

| 373a-b        | 0                 | 0                 | 0   | 0  | 0  | 0                | 0  | 1  | 0              | 0  | 0                | 0              | 010H     |

| 373c-d        | 0                 | 0                 | 0   | 0  | 0  | 0                | 0  | 1  | 0              | 1  | 0                | 0              | 014H     |

Tableau-IV.5. Adressage mémoire d'Entrées/Sorties de la C.P.

L'organisation de la mémoire d'Entrées/Sorties de la P.C.C. est présentée au tableau IV.6.

|               |    |     |    |    |                  | bison or         | AAROULION      |    | pourous de la constante de la | 400000000      | n<br>Sensitivinos | SANGARANAN MARKATAN |         |

|---------------|----|-----|----|----|------------------|------------------|----------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|---------------------|---------|

| Peripheriques | An | A,0 | Α, | A. | $\mathbf{A}_{7}$ | $\mathbf{A}_{6}$ | A <sub>5</sub> | A, | <b>A</b> <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\mathbf{A_2}$ | $\mathbf{A}_{1}$  | $\mathbf{A}_0$      | Adresse |

| IRQCI         | 0  | 0   | 1  | 1  | 0                | 0                | 0              | 0  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0              | 0                 | 0                   | 300H    |

| IRQC2         | 0  | 0   | 1  | 1  | 0                | 0                | 0              | 0  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0              | 0                 | 1                   | 301H    |

| ĪRQC3         | 0  | 0   | 1  | 1  | 0                | 0                | 0              | 0  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0              | 1                 | 0                   | 302H    |

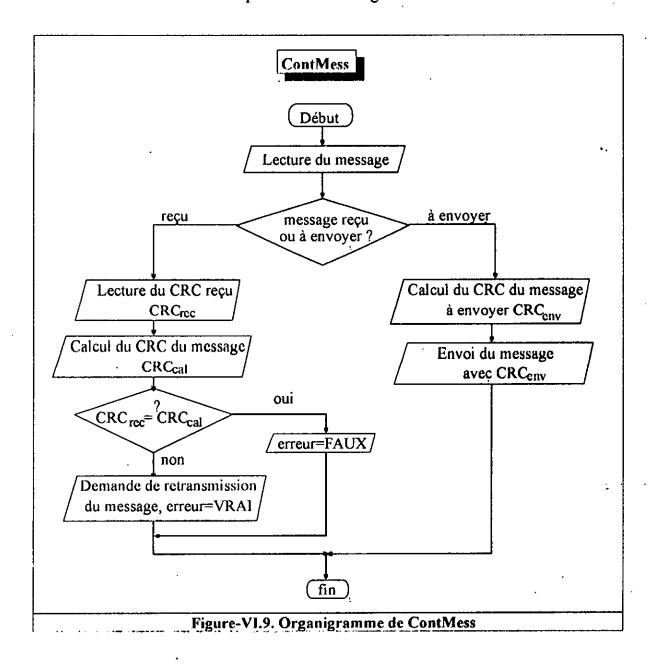

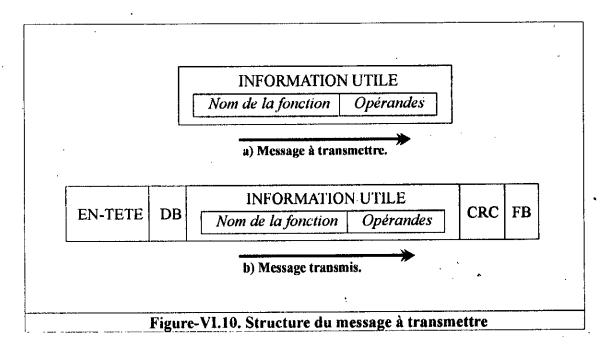

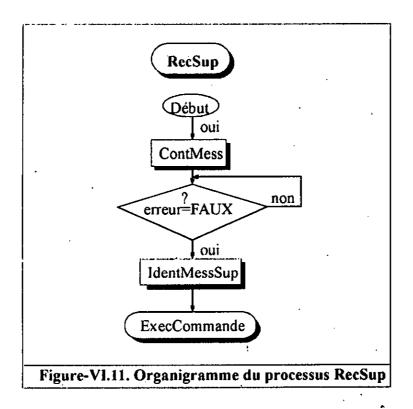

| ĪRQC4         | 0  | 0   | 1  | 1  | 0                | 0                | 0              | 0  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0              | 1                 | 1                   | 303H    |