الجمهورية الجزائرية الديمقراطية الشعبة REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

4/84

وزارة التعـــليم والبحــث العــلمــي وزارة التعــليم والبحــث العــلمــي MINISTERE DE L'ENSEIGNEMENT ET DE LA RECHERCHE SCIENTIFIQUE

291

## ECOLE NATIONALE POLYTECHNIQUE

DEPARTEMENT : ELECTRONIQUE

# PROJET DE FIN D'ETUDES

SUJET

ETUDE ET REALISATION D'UN

GENERATEUR DE SEQUENCES

PSEUDO ALEATOIRES A PLUSIEURS

SORTIES COMMANDES

Proposé par : M\_ROMANKEVITCH Etudié par : AMMOUR - KAMEL ET ARBAOUI - AMAR Dirigé par : M\_ROMANKEVITCH M\_MAHDI

PROMOTION: JUIN\_84

#### DIDICACES

Je dedie ce medeste travail /

\_A ma mère et mon père qui ont beaucoup consenti pour moi .

$-\Lambda$  mes anis .

-A mos frèros et seeurs .

#### A. AHAR .

Jo dedio ce travail:

- A ma mèro at.mon père et à leurs sacrifices

- A mes frères et seurs

- A mes amis .

A. KAMEL .

#### REMERCIEMENT

Nous tenens cette occasion pour remércier vivement nos promoteurs M. ROMANKEVITCH et M. MAHDI ,

qui par leurs aide precieuce et leurs conseils nous

ont guidé tout au long du semestre .

Nos remérciement s'adressent également à :

- M. CHIKHI

- M. BESSALLAH

- M. MENACER

Pour leurs nide dans la réalisation de notre projet .

## TABLE DES MATIELES

### INTRODUCTION

| Chapitre I S.B.P.A.                                                |      |

|--------------------------------------------------------------------|------|

| I.I.Définition d'une S.B.P.A.:                                     | 2    |

| I.2.génération d'une S.B.P.A.,                                     | - 2  |

| I.3. Séquence de longueur maximale :                               | -2   |

| I.4.Propriétés:                                                    | _4   |

| I.5. Representation des séquences par des polynômes:               | _ %  |

| I.6. Fonction d'autocorrelation:                                   | 16   |

|                                                                    | 13   |

| Chapitre II GENERATURS D. S.B.P.A.                                 |      |

| 2. Générateurs P.A. simple :                                       |      |

| 2II.G Introduction.                                                | -    |

| 2.I2 Générateurs P.A. simple:<br>2.I.3. Générateurs multirégistre: | 20   |

| 2.I.4.Générateurs d'étages variable :                              | 20   |

| 2.I.5.Application:                                                 | 22   |

| 2.2.Générateurs commandés:                                         | 26   |

| 2.2.I. Introduction .                                              | _27  |

| 2.22. Principe de base :                                           | -27  |

|                                                                    | _27  |

| P.A.                                                               |      |

| A PLUSIFURS SORTIES                                                |      |

| INTRODUCTION                                                       | 31   |

|                                                                    |      |

| 3.I.Posution du probléme :                                         | _ 32 |

| 3.2. Etude et réalisation :                                        | _33  |

| 3.2.I.G.S.P.A. COM ANDÉ                                            | 33   |

| 3.2.2. Synchronisation:                                            | _43  |

| 5.2.4.Copmande:                                                    | 45   |

|                                                                    | - 50 |

| J.J. Hoddie de comptage:                                           | 5.7  |

| J.J. Inti odde iin:                                                | 57   |

| J.J.23thona de principe et fonctionnement:                         | 57   |

| 3.4.MESURES:                                                       | 67   |

| 3.5.Conclution:                                                    | 67   |

Chapitre VI APPLICATION - 70

Chapitre V Simulation par un programme en Basic: - 71

CONCLUTION - 70

#### INTRODUCTION

Lorsque l'on produit des systèmes en grande quantité, il n'est plus possible de mettre ce produit au point ou de le reparer manuellement . Aussi utilise t-on des appareils qui puissent faire le test automatiquement , qui injéctant des signaux aux entrées des circuits sous test , vérifient l'état des sorties .

En de divergence avec l'état prévu, l'appareil aide l'opérateur à localiser l'élement défaillant.

De cette façon le dépannage prend quelque minutes .

L'objet de notre travail consiste en la réalisation d'un génerateur de séquenses pseudo-aléatoire àplusieurs mots sorties commandées pérmettant ainsi la génération des d'une façon pseudo-aléatoire, qui par la suite, seront utilisés pour faire le diagnostic des pannes dans les circuits numériques.

projet Notro s'articule autour de cinq chapitres:

-Le premier est consacré à l'étude des S.B.P.A.

-Le deuxième est consacré à l'étude des différents générateurs P.A. simples commandés et nen commandés

-Le troixième chapitre concernant l'étude et la réalisation du génerateur .

-Le quatrième est consacré à l'application de notre génerateur.

-Enfin le cinquième donne un programme de simulation en langage Basic .

Chapitre I Séquences Binaires Pseudo-Aléatoires 1-1- Définition d'une S. B. P. A . :

Une séquence étant une sults dévenements, si elle est pseudo-aléatoire, la suite des événement peut se déterminer parfaitement à priori, autrement dit elle est crée de façon déterministe, mais alle apparait comme aléatoire à un observateur qui Ignore la façon dont elle est fabriquée

1-2- Génération d'une S . B . P . A .

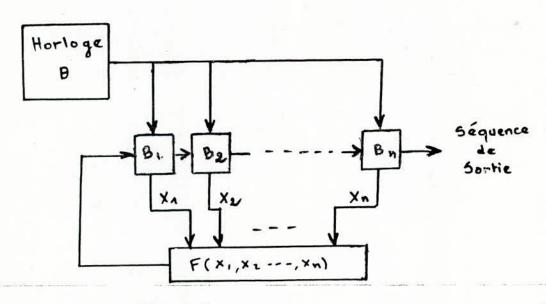

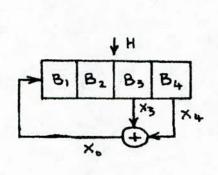

On peut facilement engendrer une 5. B. P. A. de niveau "0" ou "1". Il suffit de retroalimenter un régistre à décalage de M Digits à travers une Fonction booléenne, qu'on choisit trés généralement, comme addition modulo 2.

Soit un régistre d'ordre N constitué de N bascules et possèdent une contre réaction définie par la fonction bool senne F (x1x2---xn).

- Fig 1.1 -

La fonction booléenne correspond à une disjonction de certains Bits Xi .

La séquence ainsi obtenue est périodique, la longueur maximale qui peut être obtenue à pour valeur (2 -1) Bits.

En effet le régistre pourra prendre au maximum toutes les cambinaisons possibles des N éléments sauf la cambinaison correspondante à X i = 0 pour i= 1,2,---H qui donne une sortie constamment nulle.

Cette séquence ainsi génerée de longueur 2º1 est nommée S . B . P . A . de longueur maximale.

Pour que la séquence soit de longueur maximale, la fonction

F(Xi) ne peut être quelconque donc l'addition modulo 2 doit porter suf

certain Bits seulement. Parmi tous les cas possibles les plus intéréssants

sont ceux pour lesquels deux Bits seulement sont égaux à "1", l'addition

modulo -2 se reduit alors à un ou éxclusif.

Donnons deux éxemples, pour montrer l'éffet du choix de la fonction F(Xi) sut la longueur de la séquence génerée.

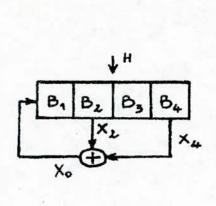

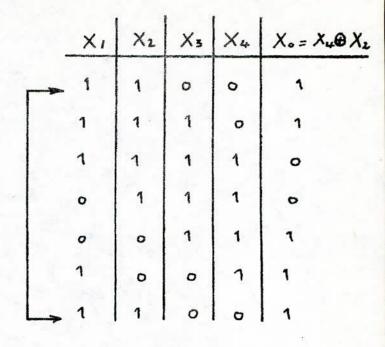

Exemple 1 : Soit un régistre à décalage constitué par 4 bascules représenté fig 1-2.

on peut remarquer que la périodicité est de 6 périodes d'horloge seulement, alors. que 4 bascules présentent 15 états différents.

Fig. 1.2

Fig. 1.3

|            | X, | X <sub>2</sub> | X3  | X4 | X. = X40 X3 |

|------------|----|----------------|-----|----|-------------|

| <b>├</b> → | 1  | 0              | 1   | 1  | 0           |

|            | 0  | 1              | 0   | 1  | 1           |

|            | 1  | 0              | 1   | 0  | 1           |

| 120        | 1  | 1              | 0   | 1  | 1           |

|            | 1  | 1              | 1   | 0  | 1           |

|            | 1  | 1              | 1   | 1  | 0           |

|            | 0  | 1              | 1   | 1  | 0           |

|            | 0  | 0              | 1.  | 1  | 0           |

|            | 0  | 0              | 0   | 1  | . 1         |

|            | 1  | 0              | 0   | 0  | 0           |

|            | 0  | 1              | 0   | 0  | 0           |

|            | 0  | . 0            | . 1 | 0  | 1           |

|            | 1  | 0              | 0   | 1  | 1           |

|            | 1  | 1              | 0   | 0  | o           |

|            | 0  | 1              | 1   | 0  | A           |

|            | 1  | 0              | 1   | 1  | 0           |

Exemple 2 : Soit le cas de la Fig 1.3.

On constate, pour ce cas, que la périodicité est de 15 périodes d'horloge qui est celle de la longueur maximale ( çàd  $2^n$  - 1) .

On voie donc, d'aprés ces 2 exemples simples, que le choix des Bits de la contre réaction est important.

Par conséquent, il faut trouver une methode qui puisse nous permettre de choisir une combinaison qui répond aux éxigence-voulues.

#### 1.3 Séquence de longueur maximale :

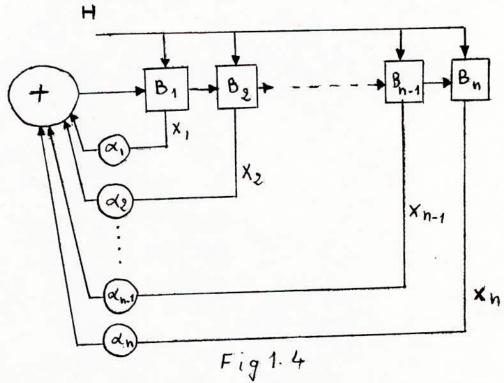

Considérons le montage de la Fig 1.4.

L'entrée serie du régistre reçoit un signal obtenu à partir du contenu des N cases.

Nous avons

$$e_{o}(k) = \sum_{j=1}^{\infty} \bigoplus_{k \neq j} (k)$$

ej (k) : étant le contenu de la case de rang j à l'instant k.

Le symbole € indiquant qu'il s'agit d'une sommation modulo 2.

Les ∠j sont des coefficients pouvant prendre seulement 2 valeurs

O où 1 .

Après la (K + 1) ième coup d'horloge on peut écrire.

où sous forme matricielle :

$$\begin{pmatrix}

e_{1}(K+1) \\

e_{2}(K+1) \\

---- \\

e_{n}(K+1)

\end{pmatrix} = \begin{pmatrix}

\alpha_{1} & \alpha_{2} & ---- & \alpha_{k} \\

1 & 0 & 0 \\

---- & 0

\end{pmatrix} \begin{pmatrix}

e_{1}(K) \\

e_{2}(K) \\

---- \\

e_{n}(K)

\end{pmatrix}$$

$$\begin{pmatrix}

e_{1}(K) \\

e_{2}(K) \\

---- \\

e_{n}(K)

\end{pmatrix}$$

c àd E (k+1) = A E(k). (1)

On montre que le système donné par (1) est linéaire.

A partir d'un état initial décrit par un vecteur E (o) l'évolution du système (1) Let déterminé par les équations.

$$E(1) = A \cdot E(0)$$

$$E (2) = A. E(1) = A. E(0).$$

$$E(K) = A^{k} E(O).$$

Après un certain nombre d'impulsions d'hologe le même état peut se reproduire.

La périodicité des états est telle que :

$$E (m + U) = E (m) = A.E (m).$$

qui s'écrit  $A E (m) = I.E (m).$

d'où  $(A^U - I).E (m) = 0.$

La périodicité de la matrice est telle que :

$$A^{L} = I$$

On montre alors que la fonction d'autocorrelation se réduit à un seul triangle à l'origine de largeur <u>+</u> une période d'horloge si les deux périodicités ainsi décrites sont égales à leur valeur maximale 2<sup>u</sup>-1. ( voir paragraphe 1.6 de ce même chapitre écemple 3 ).

Ceci est réalisé si certaines conditions sont remplies par les coefficients

Le polynôme caractéristique de la matrice A est défini par :

$$h(x) = |A - xI| = |A \oplus xI| = \begin{vmatrix} x_1 - x & x_2 & x_3 \\ 1 & -x_0 & 0 \\ 0 & 1 - x_0 \\ -x & -x \end{vmatrix}$$

En **a**rithmétique modulo - 2, l'addition et la soustration sont identiques.  $\{(\chi_i)\}$  se developpe alors comme :

Pour avoir une séquence de longueur maximale 2 - 1, il faut que h (x) soit erréductible et primitif.

Un polynôme est irréductible s'il ne posséde pas de polynôme diviseur de degré inférieur càd si  $h(x)=n(x)\cdot q(x)+r(x)$ . Et r(x) =0 alors h(x) est irréductible .

Un polynôme de degré **n** est primitif si la séquence générée correspendante a pour période 2<sup>n</sup>-1.

Enfin si la longueur 2 -I est un nombre premier l'irreductibilité du polynôme est la seul condition nécessaire

et suffisante.

Le lecteur trouvera dans le tableau I-I ci-dessous les polynôme caractéristique associés aux principales séquences de longueur maximale pour  $n \le 40$ .

h(x) étant le polynôme réciproque de h(x) défini comme  $h(x)=x^{n}h(x)$

$\mathbf{\hat{h}}(\mathbf{x})$  indique les bits de retroaction à choisir .

I-4-Propriétés des S.B.P.A. :

soit h(x) un polynôme primitif de degré n et soit l'ensemble des séquences pseudo-aléatoires obtenues par h(x).

Les S.B.P.A. ont

$$2^n$$

-I ségments différents  $a_{i}a_{i+1}$ ---- $a_{i+2}$ -2  $i=0,1,---2^n$ -2

Nous donnons ci-dessous les propriétés de ces séquences I.4.I Décalage :

si  $b=b_0b_1--b_2n_{-2}$  est n'importe quelle séquences appartenant à  $b_n$  , alors tout décalage cyclique de B :

$^{b_{j}b_{j}}_{j} \mp I^{--b} 2^{n} - 2^{b_{0}} - \cdots - b_{j} + I$ est aussi dans  $\S$

I.4.2.Recourence : nposons  $h(x) = \sum_{i=0}^{n} h_i x^i$  avec  $h_0 = h_n = I$ et  $h_i = 0$  ou I

toute séquence pseudo-aléatoire B& & satisfait la recurrence :

| -  | h (x)                 | h(x)              | n    | h(x)                        | ) ñ(x)                       |

|----|-----------------------|-------------------|------|-----------------------------|------------------------------|

| 2  | x2+x+1                | 1+ × + ×2         | 22   | X + X + 1                   | 1+ X+ X 22                   |

| 3  | x+ x + 1              | 1 + X + X         | 23   | 1 23 -                      | 17 23                        |

| 4  |                       | 1 + X + X         | 24   | 24 4 3                      | 20 21 23 24<br>4+ X+ X+ X+ X |

| 5  | 12.12.1               | 4+ X+ X 5         | 25   | ¥ 3<br>×+×+1                | 1 + x + x 25                 |

| 6  | X + X + 1             | 1 + X + X         | 26   | 26 8 7<br>X+X+X+X+1         | 17 19 05 2C                  |

| 7  | 1                     | 1 + X + X +       | 27   | 27 8 7<br>X + X + X + X + 1 | 19 2- 11                     |

| 8  | X+X+X+X+1             | 1+X+X+X+ X        | 28   | 21 3<br>X+X+1               | 1+X+X                        |

| 9  | X+ X+ 1               | 1 + X + X 9       | 29   | 29 Z<br>X + X + )           | x + x + x                    |

| 10 | /                     | 1+×+×"            | 30   | 30 16 15<br>X+X+X+X+1       | 1 + X + X + X + X            |

| 11 | X+X+1                 | 1+×+×"            | 31   | X+ X+1                      | 1 + X + X 3/                 |

| 12 | 12 7 4 3<br>X+X+X+X+1 | t + X+X+X+X       | 32   | 32 28 27<br>X+X+X+X+1       | 4 5 31 32<br>1+ X+X+X+X      |

| 13 | X+X+X+ X+1            | 1. + X+ X+ X+X    | 33   | X + X + 1                   | 1+ x+x 23                    |

| 14 | X+ X+ X+ X+ 1         | 1+ X+X+X+X        |      | X + X + X + X + 1           | 1+X+X+X+X                    |

| 15 | x+ x+1                | 1+x+x15           | 35   | 15 2<br>X + X + 1           | 1 + X + X 35                 |

| 16 | X+X+X+X+1             | 1 + X + X + X + X | 36   | X+ X+1                      | 1 + x + x 3 6                |

| 17 | x+ x+1                | 1+×+×17           | 37   | 37 12 10 2<br>X+X+X+X+X+1   | 1+ X+X+X+X                   |

| 18 | X+X+1                 | 1+x"+x18          | 38   | 38 4 J                      | 1+X+X+X+X<br>1+X+X+X+X       |

| 19 | X+X+X+X+1             | 1+ X+ X+ X+ X 19  | 39   | x+x+1                       | 1+X+X 29                     |

| 20 | 20 3<br>X+X+1         | 1+x+x             | 40 x | 40 21 19 2<br>+ X+ X+X+1    | 1+ X+ X + X + X + X          |

| 21 | X+X+1                 | 19 21<br>1+×+×    |      |                             |                              |

(I)

$$B_{i+n} = h_{n-1} B_{i+n-1} + h_{n-2} B_{i+n-2} + \dots + h_{i} b_{i+1} + b_{i}$$

$i = o , 1 --- \\ \text{Réciptoquement toute solution de } (\text{$\mathbb{I}$}) \text{ est dans } \delta_{\textbf{m}}$

Il ya donc  $\mathfrak N$  solution linéairement indépendant de (I), de même séquence linéairement indépendant dans  $\mathfrak S_n$ .

En effet, toutes les combinaisons sont obtenues puisque la longueur est maximale, sauf la combinaison oo---o qui est évitée.

Autrement dit la probabilité des "I" et des "o" est égale environ à I/2 pour massez grand.

$$P(0) = P(I) = I/2.$$

I.4.4. Addition :

La somme de deux séquences dans mest une autre séquence dans .

( la somme s'effectue en modulo-2 sans retenue.)

I.4.5. Addition et décalage.

Si on réalise la disjonction d'une séquence avec la même séquence retardée, le résultat est à son tour une nouvelle version retardée de la même séquence : on obtient ainsi en temps réel n'importe quelle réalisation retardée de ma séquence choisie.

I.4.6. Propriété de la fenêtre.

Si une fenêtre de largeur m (cad comprenant m bits) parcourt une suite \$m de "o" et de "I", chacun des 2 — I m-tuples binaires non nuls est recontré une seule fois.

Exemple pour m = 4: On a la suite.

... ooo 1001 10101111... fenêtre

Chaque 4tuples non nuls est vuune seul fois.

I.5. Représentation des S.B.P.A. par des polynômes :

La S.B.P.A. dans à une description consise par des polynômes. On peut représenter toute S.B.  $a = a_0 a - a_{k-}$  de longueur, par le polynôme:  $a(x) = a_0 + a_1 x + a_2 x^2 + \cdots + a_{k-1} x^{k-1}$  par exèmple:

000100110101111

est représentée par :

a (x) =

$$x^{9} + x^{6} + x^{7} + x^{9} + x^{11} + x^{12} + x^{13} + x^{14}$$

Un décalage cyclique d'un rang à droite de  $a_1, a_{k-1}, a_0 a_1, \dots, a_{k-2}, est$  représentée par  $a_{n-1} + a_0 x + \dots + a_{k-2} x^{k-1}$  si  $\mathcal{H}^k = 1 = x^n$  alors  $x \cdot a_1 x^n = a_0 x + a_1 x^n + a_2 x^n + \dots + a_{k-2} x^{k-1} + a_{k-1} x^k$   $\mathcal{H}_{*,a}(x) = a_{k-1} + a_0 x + \dots + a_{k-2} x^{k-1}$

D'où la multiplication par X correspond à un décalage cyclique à droite d'un rang  $\mathcal{K}^{k+1}$  est toujours divisible par le polynôme primitive de degré  $\mathcal{N}$  lorsque  $K=2^n-1$ , et la division est éffectuée en algèbre modulo 2.

Soit

$$h'(x) = \sum_{n=0}^{\infty} h_n x^{n-1} = h(\frac{1}{x}).$$

C'est le polynôme réciproque de h (x), obtenu par une inversion des coefficients.

Définissons

$$g(x) = \frac{x^{k+1}}{h(x)}$$

$$c-a-d \sin h(x) = \chi^4 + \chi^4 + 1$$

,  $h(x) = \chi^4 + \chi^3 + 1$

alors

$$g(x) = \frac{x^{15} + 1}{x^4 + x^3 + x^4} = 1 + x^3 + x^4 + x^6 + x^8 + x^9 + x^0 + x^{11}$$

notée que  $x^3$  g (x) = a(x).

Propriété :

La S. B. P. A. dans  $\leq n$  composée d'un polynôme  $x^i$  b (x) avec  $i = 0, ---, 2^n - 2^n$  et b  $(x) \in \leq n$ . (voir propriété 1.4.1.).

Par ailleurs il éxiste des polynômes : t(x).g(x) où t(x) est un polynôme de degré inférieur à n .

(Si  $b(x) = t(x) \cdot g(x)$  alors  $b(x) \cdot h(x) = t(x) \cdot (x + 1)$ En égalisant les coefficients de  $x^{n+1}$  dans cette identité on obtient :

$$\sum_{m=0}^{b_{i+m}h_{m}=0}$$

i=0, I, ---, k-n-I

vu que g(x),xg(x),---,x = I g(x) represente k séquence dans est être representer par t(x),g(x) où deg(t(x))(n) par conséquent g(x) est appelé polynôme génerateur de son

#### 1.1. Fonction d'autocorrelation d'une 5 . B. :

Avant de définir la fonction d'autocorrelation de n'importe qu'elle sequence V binaire, il est préférable de donner les caractéristiques d'un bruit blanc.

un bruit blanc étant un signal aléatoire dont la connaissance à un instant donné ne fournit aucun renseignement sur sa valeur à l'instant sui-vant. Cette propriété se traduit mathématiquement par une fonction d'auto-correlation qui est une impulsion de Dirac à l'origine des temps, fig. 1.5.

On obtient d'après la définition de la densité spéctrale.

Fig. 1.5.

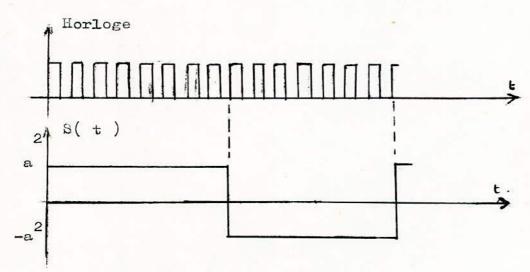

#### 1.6.1. Fonction d'autocorrélation.

On appelle fonction d'autocorrélation d'un signal quelconque X (+), la fonction :

$$\phi_{xx(7)} = \frac{1}{T} \int_{0}^{t} x(t).x(t+7) dt. (1)$$

Daus Le cas d'une suite binaire synchrone d'une horloge, associons + a au "1" Logique et - a au "0" Logique. L'intégrale (1) prend alors la forme suivante

$$\phi_{XX(k)} = \frac{1}{5} \sum_{j=1}^{L} x(j) \cdot x(j+k).$$

Quand K est une valeur entière K = 0, 1, ---, L

L est la longueur de la séquence.

Donnons quelques éxemples, pour éxpliquer comment on trace une fonction d'autocorrelation connaissant la séquence binaire engendrée.

#### Exemple 1:

Choisissons T = 15 , étant la période de l'horloge de T la durée de la séquence qui est recurrente.

Considérons la suite 1 1 1 1 1 1 1 1 0 0 0 0 0 0  $\bar{\bf a}$  laquelle est associé le signal X ( + ) fig. 1.6.

Codons + a par "1" et -a par "0", ainsi on obtient "

1'opération a b où reprente la coincidance,

| s ( t | ) į s ( | t - 7) | S (x) . | s ( t ~7)      |

|-------|---------|--------|---------|----------------|

| - a   | -       | a      |         | a <sup>2</sup> |

| - a   | +       | 2.     | -       | a <sup>2</sup> |

| + a   | -       | a      | -       | a <sup>2</sup> |

| + a   | +       | a      | *       | a <sup>2</sup> |

|       | - 2     |        |         |                |

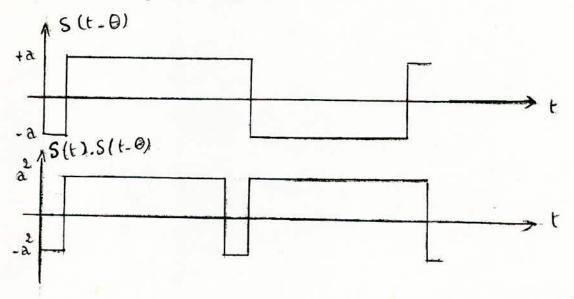

Il suffit donc, pour calculer les valeurs de la fonction d'auto-correlation pour chaque retard, de juxtaposer la suite d'origine et la

même suite décalée de 0, 20, ---, 55et d'éffectuer la coincidence bit

par bit.

Ensuite un simple calcul du nombre de " 1 " auquel on retranche le nombre de " 0 " le résultat multiplié par  $a^2/15$  donne  $\Phi \times \times (\tau)$  correspondant à  $\tau = \kappa \Theta$  choisi.

Nous avons donc :

$$\Phi \times \times (K\Theta) = \frac{a^2}{15} (n - P)$$

avec n le nombre de " 1 "

et P le nombre de " 0 "

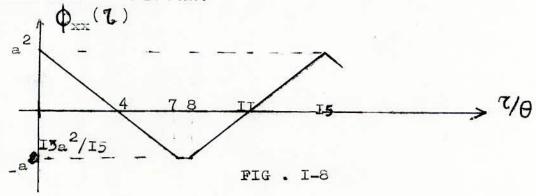

fig 1. 7.

1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 suite à l'origine

0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 suite décalée de

0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 coincidence.

Nous aurons donc

$$\phi_{XX}(\tau) = \frac{a^2}{45}(13-2) = \frac{11}{15}a^2$$

En continuant de même, on obtient la courbe de la fig 1.8. C'est pour un décalage de 7 à 8 que la suite décalée a la plus grande dissemblance avec elle-même.

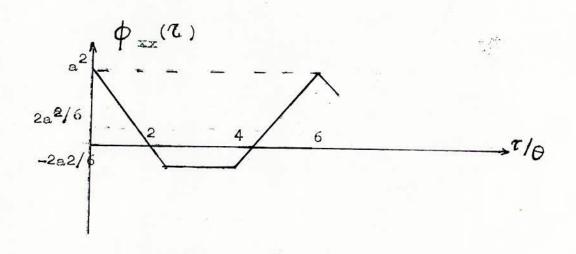

Exemple 2:

Concidérons maintement la suite 111001 de longueur 6 (c'est la séquence de l'éxemple ! fig.1.2).

Cette suite est une séquence pseudo-aléatoire de longueur non maximale.

Voyons sa fonction d'autocorrélation.

Un raisonnement analogue à celui de l'éxemple 1 donne la courbe de la fig. 1.9.

fig 1.9.

Cette courbe montre que la fonction d'autocorrelation se réduit à un seul triangle à l'origine mais de largeur + 2 périodes d'horloge.

#### Exemple 3:

Nous allons, enfin, voir le cas d'une séquence binaire pseudoaléatoire de longueur maximale 1 5 : 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 ( c'est

la suite de la séquence de l'éxemple 2 fig 1.3.).

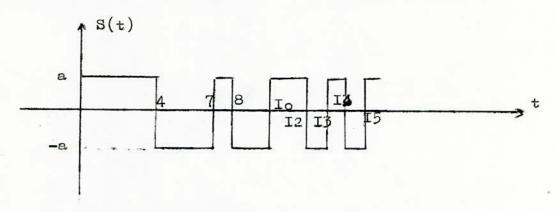

Le signal associé S (4) est représenté fig.1.10.

fig 1.10.

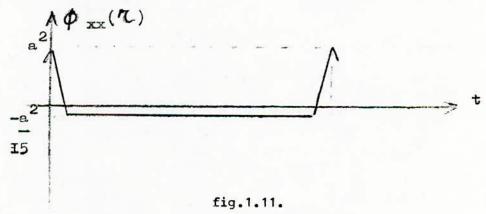

Correlé avec lui-même, la méthode suivre précédement permet d'obtenir la courbe fig. 1.11.

La séquence pseudo-aléatoire étudiée présente, comme toute les G.S.P.A. de longueur maximale, la particularité de posséder une fonction d'autocorrélation se rapprochant de l'impulsion de Dirac à l'origine, toute fois XX X (7) est périodique de période T.

#### Propriétés :

a - La valeur moyenne d'une S.B.P.A. de longueur maximale se calcule sur une période comme :  $E (x) = \frac{1}{L} \sum_{i=1}^{L} x(i) = a/L.$

Pratiquement, si L est assez grand, on néglice cette valeur et on considére que la séquence est centrée (c-a-d à Valeur moyenne nulle ).

$\underline{\text{B-}}$  On calcule l'autocorrelation sur une p'miode d'une S . B . P .A de longueur maximale comme :

$$\oint X X (\mathcal{T}) = \frac{1}{L} \sum_{k=1}^{L} X(j) \cdot X (j+k) = \begin{cases} a^2 & \text{si } k = n \text{ L } \text{ In } \text{EN} \end{cases}$$

$$\begin{cases} \frac{a^2}{L} & \text{si } k \neq n \text{ L} \end{cases}$$

Si maintement nous cherchons la valeur de la fonction de corrélation pour K  $\Theta(\chi)$  (k+1)  $\Theta$  deux cas sont à envisager :

si

$$K = 0$$

alors

$$\oint X X (7) = a^2 \left(1 - |2| \frac{L+1}{L}\right)$$

si

$$K \neq 0$$

alors  $\phi \times \times (\mathcal{T}) = -\frac{a^2}{r}$

Les éxemples 2 et 3 montrent qu'une  $\varsigma$ ,  $\varsigma$ ,  $\varsigma$ ,  $\varsigma$ ,  $\varsigma$ ,  $\varsigma$ ,  $\varsigma$ , de longueur maximale présente plus d'avantage que colle de longueur non maximale à savoir :

- la valeur moyenne diminue.

- la largeur du triangle à l'origine diminue aussi.

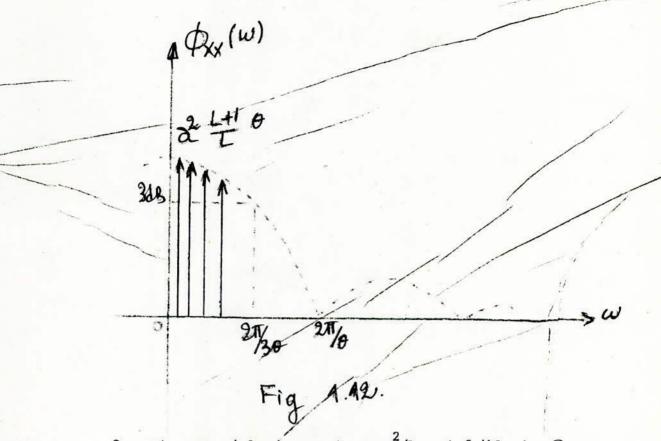

1.6.2. Densité spéctrale d'une S. B. P. A.

La densité spéctrale  $\phi_{X}$   $_{X}$  (  $_{W}$  ) de la fonction  $_{S}$  ( $_{E}$ ) étant la transformée de fourier de la fonction de corrélation, on peut écrire :

$$\phi_{XX(W)} = 2 \int_{0}^{T} \phi_{XX}(x) \cdot \alpha x \cdot dx$$

La figure 1.12 donne la densité spéchale d'une S.B.P.A. de

On montre que si la composante - a Lest faible (LO suffisamment grand), la première fréquence peut-être aussi voisine de zéro qu'on le désire; on peut noter aussi que l'amplitude du spectre décroit de 3 d B pour W = 2 T/ 3 P/ ainsi la séquence peut -être asimilée à un élément "bruit blanc " pour des fréquences allant jusqu' 1 / 3 P.

Chapitre II

Générateurs

Ps cudo. Aléatoires.

2 . I . G . S . P . A . Simple.

### 2 . I.I. INTRODUCTION.

On a vu dans le chapître qui précéde qu'un régistre à décalage avec une rétroalimentation convenable peut générer une source riche d'information. Nous verrons maintenant l'aspect pratique d'un tel généra-teur ; Puis nous donnerons comment réaliser un générateur multirégistre. Finalement nous traiteront le cas d'un G.S.P.A. dans lequel le nombre de bascules est raviable.

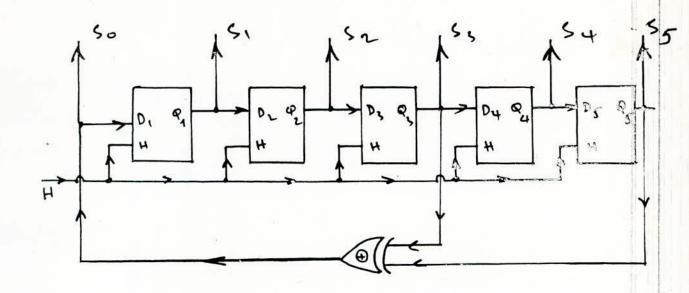

2.I.2G.S.P.A.Simple.

Le régistre à décalage est construit à l'aide de bascules simples il suffit de relier les horloges entre elles et la sortie de l'une est connectée à l'entrée de la suivante.

l'élément de rétroaction linéaire, peut-être réaliser à partir d'un XOR où plusieurs suivant le nombre de bascules utilisées.

Par éxemple : pour h (x) =  $x^5 + x^2 + 1$

on a le schéma électrique suivant , de la fig. 2 . I . I

$S_0$ ,  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$ , sont des S.B.P.A. de longueur  $2^5$ - I = 3I.

Remarque :

Une methode trés éfficace consiste à utiliser un compteur linaire à l'envers c-a-d à permuter le rôle du D,A et les digits intermédiaire B,C pour 4 bits les états succéssifs sont les suivants.

0 0 0 0 - I 0 0 0 - 0 I 0 0 - I 0 0 0 etc... soit en décimal 0,8,4,2,I0,6,I6,I,9,5,I3,3,II,7,I5,0.

on remarque que l'état 0 0 0 0 figure.

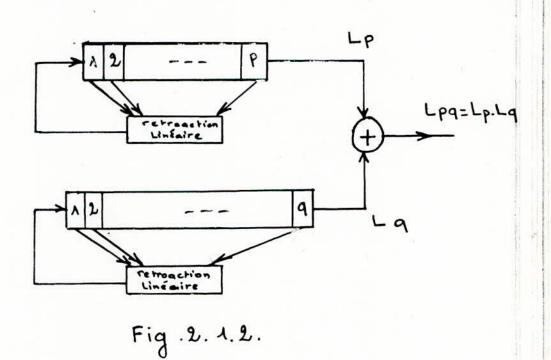

2 . I . 3 . Générateur multirégistre. Soit le cas de figure. 212.

Ce circuit est réalisé à partir de 2 G . S . P . A simple, l'un de longueur Lp l'autre de largeur Lp.

Si on réalise la d'inction d'une séquence Lp et d'une autre Lp, le résultat est une autre séquence mais de longueur Lpq

Fig. 2.1.1

égale au produit des 2 longueurs.

soit Lpq = Lp Lq.

remarque :

si La et Lp étaient de longueur maximale

c-a-d Lp =  $2^{p}-I$  et Lq =  $2^{q}-I$

alors Lpq =

$$(2^{p} - I)(2^{q} I) = 2^{p+q} + I - 2^{q} - 2^{p}$$

par contre si on utilise un seul régistre de p+q étage la longueur maximale sera :

$$L p'q = 2^{p+q} - I$$

on constate que L'pq > Lpq

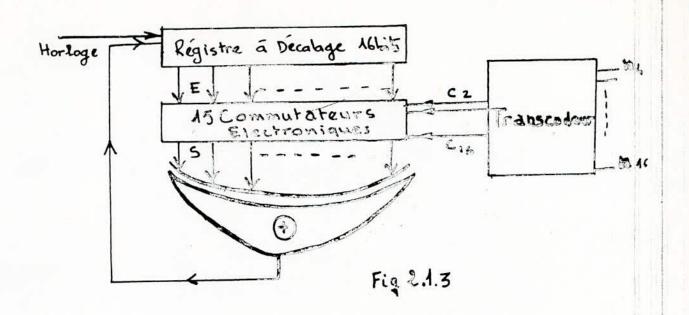

2 . I . 4 . G . S . P . A . d étages variable.

Ce générateur pulse des séquences de longueur maximale. Ces dernières penvent-être varier selon le nombre d'étage utilisé.

On a conçue un générateur allant de 4 à 16 étages.

A chaque nombre d'étages on affecte le polynôme primitif correspondant dont le but d'obtenir des séquences de longueur maximale.

Le sch sma est donné fig. 2.I.3.

Les commutateurs sont du type CD 4016 c CD 4066 c-à-d. chaque interrup--teur posséde une entrée, une sortie et une commande qui le met soit à l'état passant, soit à l'état bloqué.

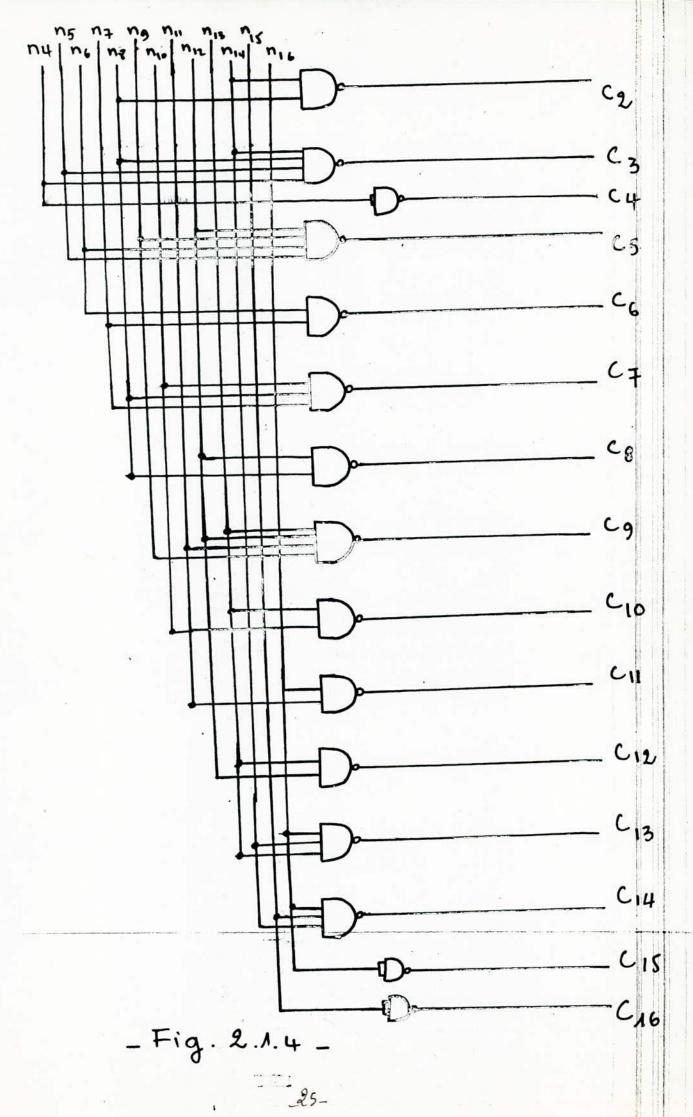

Voyons mainterant la constitution du transcodeur.

soient C<sub>2</sub> ---- C<sub>I6</sub>les sorties , N<sub>4</sub> , ----N<sub>I6</sub> les entrées.

Il faut donc exprimer la sortie en fonction de l'ontrée d'aprés le tableau II donné au chapître I on tire le tableau 2.I.I. qui correspond à :

| surtie         | Cو | C3 | C4 | C5 | C <sub>6</sub> | Cŧ | C s    | Cg     | C10 | Cal | Cae    | C13 | Cos | Cos  | Cas    |

|----------------|----|----|----|----|----------------|----|--------|--------|-----|-----|--------|-----|-----|------|--------|

| n <sub>4</sub> | 0  | 1  | 4  | 0  | 0              | 0  | 0      | 0      | 0   | O   | 0      | 0   | 0   | Ó    | 0      |

| n,             | 0  | 1  | 0  | 1  | 0              | 0  | 0      | 0      | 0   | 0   | 0      | 0   | 0   | 0    | 0      |

| n              | 0  | 0  | 0  | 1  | 1              | 0  | 0      | 0      | 0   | 0   | 0      | 0   | 0   | 0    | 0      |

| nz             | 0  | 0  | 0  | 0  | 1              | 1  | 0      | 0      | 0   | 0   | 0      | 0   | 0   | 0    | 0      |

| n.             | 4  | 1  | 0  | 0  | 0              | 1  | 1      | 0      | 0   | 0   | 0      | 0   | 0   | 0    | 0      |

| n,             | 0  | 0  | 0  | 1  | 0              | 0  | 0      | 1      | 0   | 0   | 0      | 0   | 0   | 0    | 0      |

| n 10           | 0  | 0  | 0  | 0  | 0              | 1  | 0      | 0      | 1   | 0   | 0      | 0   | 0   | 0    | 0      |

| nu             | 0  | 0  | 0  | 0  | 0              | 0  | 0      | 1      | 0   | 1   | 0      | 0   | 0   | 0    | 0      |

| N12            | 0  | 0  | 0  | 1  | 0              | 0  | . 1    | 1      | Ð   | 0   | 1      | 0   | C   | 0    | 0      |

| N13            | 0  | 0  | 0  | 0  | ,0             | 0  | 0      | 1      | 1   | 0   | 1      | 1   | 0   | 0    | 0      |

| 744            | 1  | 1  | 0  | 0  | 0              | C  | 0      | 0      | 0   | 0   | _ 0    | 1   | 1   | 0    | 0      |

| 715            | 0  | 0  | 0  | 0  | 0              | (  | 0      | 0      | 0   | 0   | ر<br>م | 0   | 1   | . 1  | 0      |

| 7146           |    | 0  | 0  | 0  | 0              | (  | ) (    | •      | 0   | 1   | 0      | 1   | 1   |      | 1      |

|                | ļ  |    |    |    | \$             | 4) | العصيب | أميمسر |     |     |        |     |     | C5 = | 0.2471 |

tableau 2. 1.1

Le schéme électrique du transcodeur est donmé fig.214

Pour choisir un générateur de n<sub>i</sub> étages ,il suffit de

mettre l'entrée du transcodeur correspondante à l'état bas .

Remarque: On peut avoir d'autre configurations donnant

un G.S.P.A. d'étage variables .

## 245.Application :

Les S.B.P.A., connues depuislongtemps, ont été utilisées dans plusieurs domaines.

En géneral, ellœ sont utilisées comme signaux de de tosts, vu qu'illes présentent plusieurs propriétés importantes

Ce type de signaux numériques . d'abord été utilisé dans les systèmes de communications digitaux puis plus recement lors de l'identification des sommes industriels ainsi que dans le domaine de détection des erreurs dans les circuits logique.

# 215. I. Génération de bruit :

"Fabriquer" du bruit n'est toujiurs facile, il est plus pratique d'avoir à créer une entrées détérministe.

une telle entrées éxiste, c'est les S.B.P.A..

On peut à l'aide de ces dérnières, génerés un bruit analogique dont le spectre est constant en basse fréquence et limité du côté des haute fréquences .

Le schéma de principe est donné fig .2.3.I

LA convertion peut être réaliser à partir d'un filtre passe bas , pourvu que la bande passante du filtre soit beaucoup plus petite que la fréquence d'horloge .

### 2.2 G.S. PAC:

#### 2.2. I. INTRODUCTION:

Un générateur P.A. simple nous génère de séquences dont la probabilité des "I" et des "O" est égale à 0,5 comme on l'a vu précédement.

Dans cette partie, nous allons essayer de réaliser un généra-teur pseudo-aléatoire dans lequel la séquênce générée est commandée

c-àd que la probabilité des " I " à la sortie est variable selon notre

choix.

#### 2.2.2. Principe de Base :

Le principe de la commandabilité est basé sur un comparateur qui compare le mot venant du G . P . A . simple et un autre mot venant d'un régistre, et ce dernier peut être varier à volonté, et nous rensiegne sur le nombre de " I " dans la séquence générée.

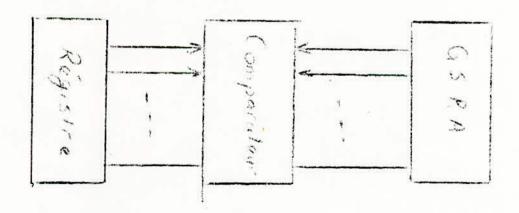

Le schéma de principe est donné par la fig. 2.2.1.

fig; 2.2.I.

### dispositif :

|         | Sortie A L B |       |        |      |      |  |  |  |  |  |

|---------|--------------|-------|--------|------|------|--|--|--|--|--|

| CAPAC   | 0000         | 0100  | 1000   | 1100 | 1111 |  |  |  |  |  |

| 1000    | O            | 9     | A      | 1    | 1    |  |  |  |  |  |

| U 150   | U            | 1     | 1      | 1    | Λ    |  |  |  |  |  |

| 0040    | O            | A     | 1      | 1    | A    |  |  |  |  |  |

| NO N    | 0            | 0     | υ.     | 1    | 1    |  |  |  |  |  |

| 1100    | 0            | · o   | O -    | А    | ٨    |  |  |  |  |  |

| 0110    | O.           | - 0   | A      | 4    | Λ    |  |  |  |  |  |

| AOAA    | 0            | O     | O      | 1    | 1    |  |  |  |  |  |

| 0404    |              | 0     | 1      | 1 1  | 1    |  |  |  |  |  |

| - 1     |              | 0     | U      | 1    | 4    |  |  |  |  |  |

| 4040    | 0            | Ü     | U      | 0    | 1    |  |  |  |  |  |

| 1101    | 0            | U     | Ú      |      | ,    |  |  |  |  |  |

| A AAAO  | 0            |       | - · ·  | 0    | 1    |  |  |  |  |  |

| 1111    |              | U     | ſ      | A    | 1    |  |  |  |  |  |

| DAAA    | 0            | 0     | A      | 1    | Λ    |  |  |  |  |  |

| 0014    | 0            | Λ     | 1      |      | 1    |  |  |  |  |  |

| 10001   | 0            | Λ     | ,A     | 1    | 1    |  |  |  |  |  |

| Nhre"1" | 0            | 4     | *      | 12   | 15   |  |  |  |  |  |

| P(1)    | 0            | 02667 | ō,\$33 | 0,8  | 1    |  |  |  |  |  |

Pour que le nombre de " I " soit bien le mot d'entrée B dans la séquence générée, il suffit de réaliser ces conditions :

Si A L B alors "I" apparait à la sortie du comparateur

Si A 7 B alors " 0 " apparait à la sortie du comparateur.

10

Montrons ceci par un éxemple :

soit un seléma de la fig. 2.2.2.

Fig. 222

On remarque dans l'éxemple précédent que les probabilités des "I" sont légérement supérieurs à celles indiquées par le mot B, cela vient du fait que la combinaison 0000 n'apparait pas dans les mots générés par 10 G.S.P.A.

Par contre, si on prend un G . S . P . A . de m bits, dans lequel on éxploite seulement p bits ( avec p m ) pour la comparaison, et en prenant uniquement la sortie A B du comparateur, on remarquera que ces probabilités sont légérement inférieur mais qu'ils tendront de plus en plus vers la probabilité voulue lorsque m - p devient faible. ( voir réalisation ).

# Chapitre II

Etude et Réalisation d'un Générateur de séquences Pseudo-Aléatoires à plusieurs Sorties Commandés.

#### INTRODUCTION :

La civilisation change et se développe dans les années, et elle utilisera de plus en plus des équipements plus sofficient et plus perfectionés suivant l'éxigence de la vie courante et avec elle les appareils de jadis deviennent moins éfficaces, donc il faut toujours chercher et concevoir des appareils de test plus éfficaces et qui répondent aux éxigences et contreintes demandées.

Maintenant où est apparu l'ordinateur et les éléments logiques, il est fastidieux et s'avère impossible pour un Ingenieur chargé de la mainte-nance d'utiliser les procédés conventionnels de dépannage tels que vol-tumétres et oxilloscopes : disposant de relativement peu de points de tests, du fait de la trés grande densité d'intégration des circuits, il se trouve confronté avec des configurations de données numériques longues et complexes.

Donc il faut concevoir des appareils qui puissent faire le contrôle automatiquement et pendant un temps trés bref.

Notre générateur à plusieurs sorties commande blequ'on a réaliser, consiste à générer des mots pseudo-aléatoirement qui par la suite seront utilisés pour le diagnostic des pannes dans les circuits numériques.

.../...

#### 3.1. Position du Problème :

Notre générateur peut être facilement réaliser à partir de plusieurs  $G\ .\ S\ .\ P\ .\ A\ .\ commandables\ à une seule sortie\ {\tt p}$

( comme celui étudié dans le Chapître 2 ), cens le but d'avoir plusieurs sorties indépendantes de probabilité variable utilisant par conséquent un nombre de matériels importants ce qui présente un encombrement non négligeable et un prix élevé.

Or, il éxiste un moyen plus rentable, qui permet à l'aide "un seul G . S . P . A . commandable de répondre aux éxigences demandées.

Notre appareils, délivre à ses sorties des séquences numériques de probabilité variable selon l'utilisateur et ceci d'une façon indépen-dante c-à-d. qu'on peut changer le nombre de " 1 " de chaque sortie d'une manière indépendante des autres.

# 3.2. Etude et réalisation :

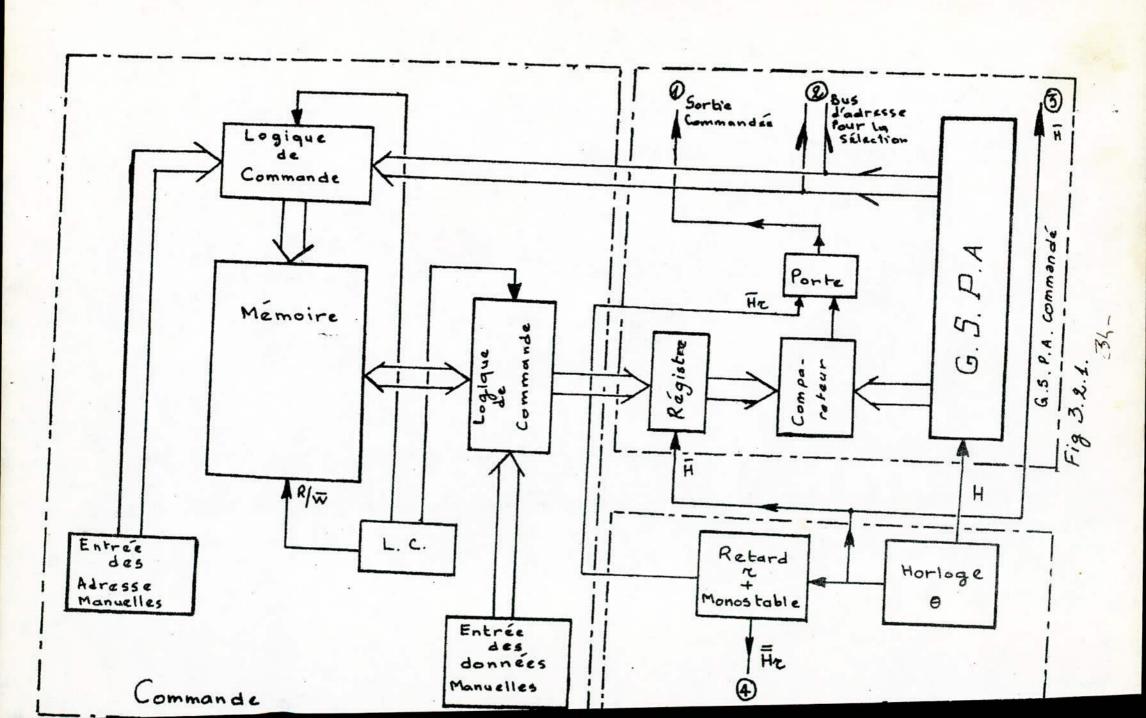

Le schéma synoptique est donné figure 3.2.1. et figure 3.2.2.

Comme on peut le remarquer, notre générateur peut être subdiviser en 4 parties :

- G .S .P .A . Commandé à une seule sortie.

- Synchronisation.

- Séléction.

- Commande.

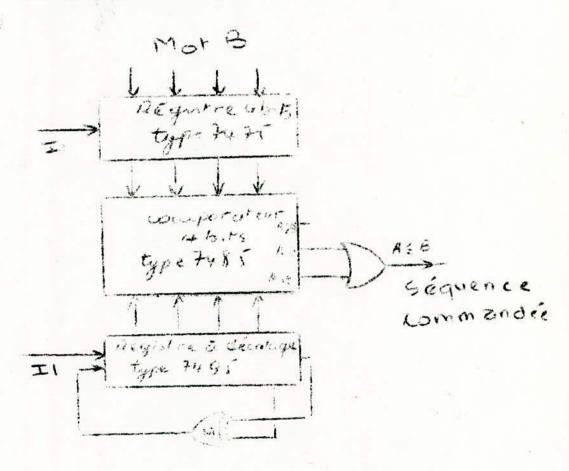

3.2.1. G . S . P . A . Commandé :

Ce générateur est basé sur le même principe que celui vu dans le chapître précédent.

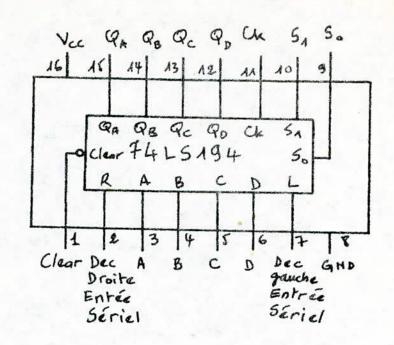

Le régistre à décalage a été réalisé par le circuit intégré S N 7 4 L S 194 ( fig 3.2.3 ).

Si  $S_0$  = "1" (broche 9) et  $S_1$  = "0" (broche 10). On réalise un décalage à droite du mot présent sur la sortie dés le premier front montant de l'horloge.

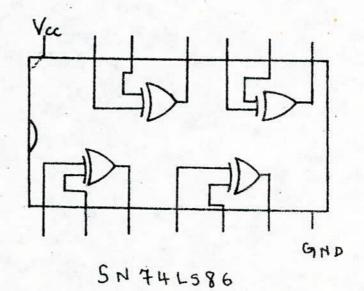

Le circuit intégré SN 74LS86 (fig 3.2.4.) définit l'élément de contre réaction ( c-a-d l'addition modulo 2).

Le G ..S . P . A seul, délivre des séquences qui vérifient les propriétés citées dans le chapître 1 à savoir.

$$P(0) = P(1) = 1/2.$$

Pour un régistre à décalage de 15 bits, la longueur des séquences est de  $L=2^{15}-1=32767$ .

On a choisi 15 bits pour 2 raisons.

- La rétroaction ne demande qu'une seule porte où éxclusif.

- La longueur des séquences obtenues est considérable.

Cette dernière est primordiable comme on va le voir tout de suite.

| Entreés |    |     |       |    |       |          |      |   |   |                | Sor           | ties           |                |

|---------|----|-----|-------|----|-------|----------|------|---|---|----------------|---------------|----------------|----------------|

| Clear   | M  | ode | Clock | 5  | ériel | Parallel |      |   |   | 10             | G             | 0              | _              |

|         | 50 | 51  |       | D. | D. G. |          | ABCD |   |   | Q <sub>A</sub> | $\varphi_{g}$ | Q <sub>C</sub> | Ψ <sub>D</sub> |

| 0       | X  | χ   | X     | X  | X     | X        | ×    | × | X | 0              | 0             | 0              | 6              |

| 1       | X  | X   | 0     | X  | X     | X        | X    | X | X | QA.            | 98            | . Q.           | 9              |

| 1       | 1  | 1   | 1     | ×  | X     | a        | 6    | c | d | a              | <b>b</b>      | c              | 9              |

| 1       | 0  | 1   | 1     | X  | 1     | X        | X    | × | X | 1              | Ø,            | Q              | , G            |

| 1       | 6  | 1   | 1     | X  | 0     | X        | X    | X | X | 0              | QAn           | Q              |                |

| 1       | J  | 0   | 4     | 1  | X     | X        | X    | X | X | QB,            |               |                | ο ¬            |

| 1       | 1  | 0   | 4     | 0  | X     | X        | X    | × | × | Q              |               |                |                |

| 1       | D  | 0   | X     | X  | ×     | X        | ×    | × | X | . QA           |               |                | Dn @           |

Brochage et table de fonction du CIrcuit intégré SN74L5194

Fig 32.3

Fig 3.2.4

Si on prend par éxemple un G . S . P . A . à 4 bits on aura les combinaisons suivantes :

0001

1000

0100

0010

1001

1100

0110

1011

0101

1010

1 1 0 1

1 1 1 0

1 1 1 1

0 1 1 1

0011

Dressons un tableau donnant le nombre du mot zéro et des mot différent de zéro en fonction du nombre des bits pris.

( voir tableau 3.2.1. ).

Avec un raisonnement analoque on peut généralisé à un G.S.P.A. à N bits (voir tableau 3.2.2.).

Comme le nombre de séquence i à prendre en considération est prissuivant le besoin, il faut donc prendre N assez grand pour que le mot zéro apparait autant de fois que les autres mots, autrement dit le rapport du nombre d'apparition du mot zéro sur celui de n'importe quel autre mot différent de zéro tend vers l'unité.

On constate bien que :

suivant le nombre d'étages.

| Nore de sequences<br>prises | Apparition du nore o | Apparition des mots |  |  |  |

|-----------------------------|----------------------|---------------------|--|--|--|

| 4                           | 0                    | 1                   |  |  |  |

| 3                           | 1                    | 2_                  |  |  |  |

| 2                           | 3                    | 4                   |  |  |  |

| 1                           | 7                    | 8                   |  |  |  |

tableau 3.2.1.

| Note de bits pris | Apparition du nore<br>Zéro | Apparition des mots |

|-------------------|----------------------------|---------------------|

| n                 | 0 =2-1                     | 1 = 2               |

| n-1               | 1 = 2'-1                   | 2 = 2               |

| n-2               | 3 = 2-1                    | 4 = 22              |

|                   | 1                          | •                   |

|                   |                            | 1                   |

| n-11              | 2047=21-1                  | 2048=211            |

| \                 | 1                          |                     |

| •                 | ,                          | Y .                 |

| n - p             | 2 -1                       | 2 P                 |

| avec nyp.         |                            |                     |

Tableau 3.2.2.

Pour notre cas, on a utilisé 4 bits du G . S . P . A . pour la combinaison et 4 autres bits pour l'adressage de la mémoire et la séléction.

Le schéma électrique du G . S . P . A . commandé est donné fig. 3.2.5.

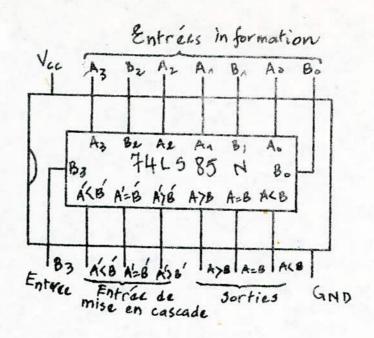

Le comporateur 4 bits est réalisé à partir du circuit intégré SN 74LS 85 (fig 3.2.4.).

Le régistre 4 bits à partir du circuit intégré SN 74LS (fig; 3.2.4.).

Le générateur fonctionne avec une fréquence d'horloge de 1 M H Z, c-à-d qu'a chaque impulsion d'horloge (front montant) on aura une nouvelle combinaison à la sortie, ce qui veut dire le G . S . P . A . garde chaque combinaison en mémoire pendant une période.

Les 4 bits choisis pour l'adressage de la mémoire et la sélection s'éffectue d'une manière pseudo-aléatoire.

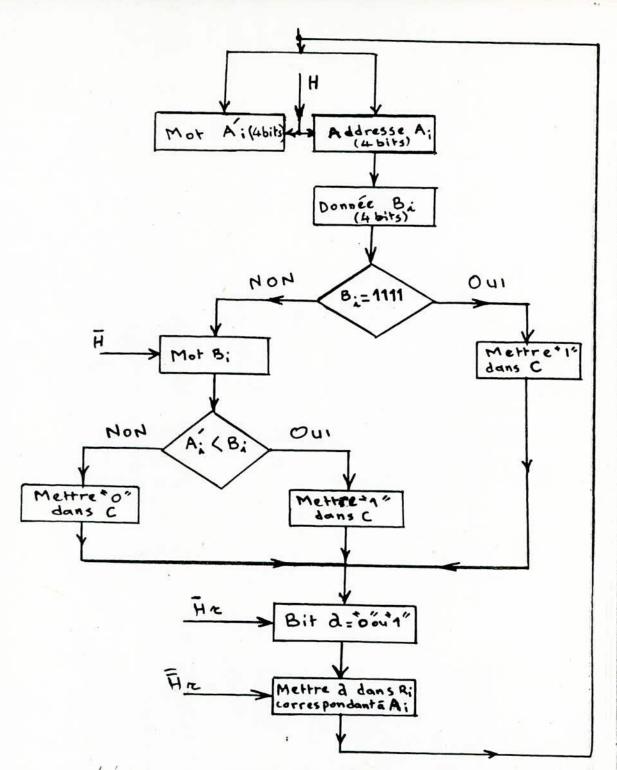

Selon l'adressage de la mémoire, cette dernière va liberer une donnée, qui n'est rien d'autre que la probabilité des " 1 ", qui va être présenter à la sortie du régistre 4 bits à chaque impulsion d'horloge H.

On remarque qu'il se produit un certain retard entre le mot du G. S. P. A. et le mot venant de la mémoire.

Il faut donc synchroniser les 2 informations pour que la comparai-son s'éffectue d'une manière corrécte c-à-d le 1er mot avec la 1er

donné etc----

Pour cela nous avons choisi la 2ème altérnance du signal d'horloge H appliqué au G . S . P . A . comme temps de comparaison.

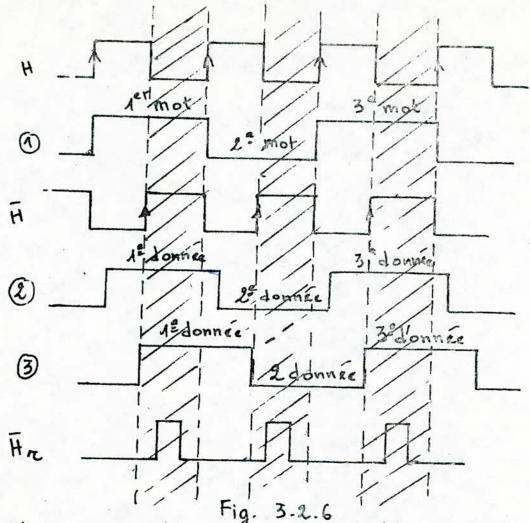

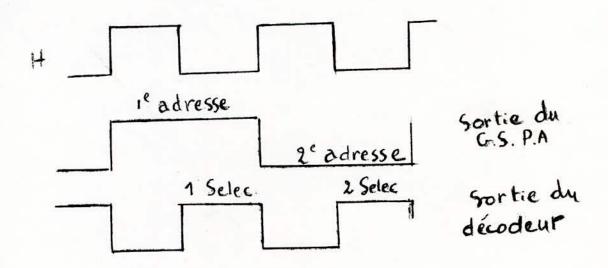

Pour plus de clarté voir chronogramme de la fig 3.2.6.

On voit que, sans le signal H<sub>r</sub>, la comparaison s'éffectue d'une façon anormale du fait que le 2ème mot sera comparé avec le 1er donnée venant de la R A M, d'où pour palier cet inconvénient on a été amené à créé un autre signal H<sub>r</sub> à partir de H, appliqué à une entrée d'une porte A N D dans laquelle l'autre entrée sera la sortie A K B du comparateur.

La zone hachurée est l'intervalle où s'effectue la comparation

D Représente la durée de chaque mot à la

Sortie du G.S.P.A. à la Ladence de H

D'Représente la durée de chaque donnée Sortant de la mémoire

3 Représente la durée de chaque donnée à l'entrée du comparateur

Rque:

Les niveaux hant et bas de 0, 0 et 3 n'ont aucune signification, c'st juste pour distinguer 2 mots successifs.

## 3.2.2. Synchronisation :

Ce bloc nous génére des signaux qui mettent notre appareil en régime de fonctionnement optimal c-à-d aucune information utile ne se perde.

Les signaux H et H sont généres par l'hologe intégré 6 8 7 I A FIG. 3.2.7.

CETTe horloge dispose de plusieur signaux en l'occurence : Broche 2 qui donne une sortie T T L de fréquence I M H Z . ( signal H ).

Ce signal est appliqué au G.S.P.A.

Broche I2 qui délivre le même signal H, de même gréquence mais en téchnologie N M O S.

Ce signal est appliqué au décodeur démultiplexeur I parmi 16.

Broche 23 qui génére un signal H en version N M O S de même fréquence que H.

Ce signal sera appliqué au régistre 4 bits et au double monos--tables.

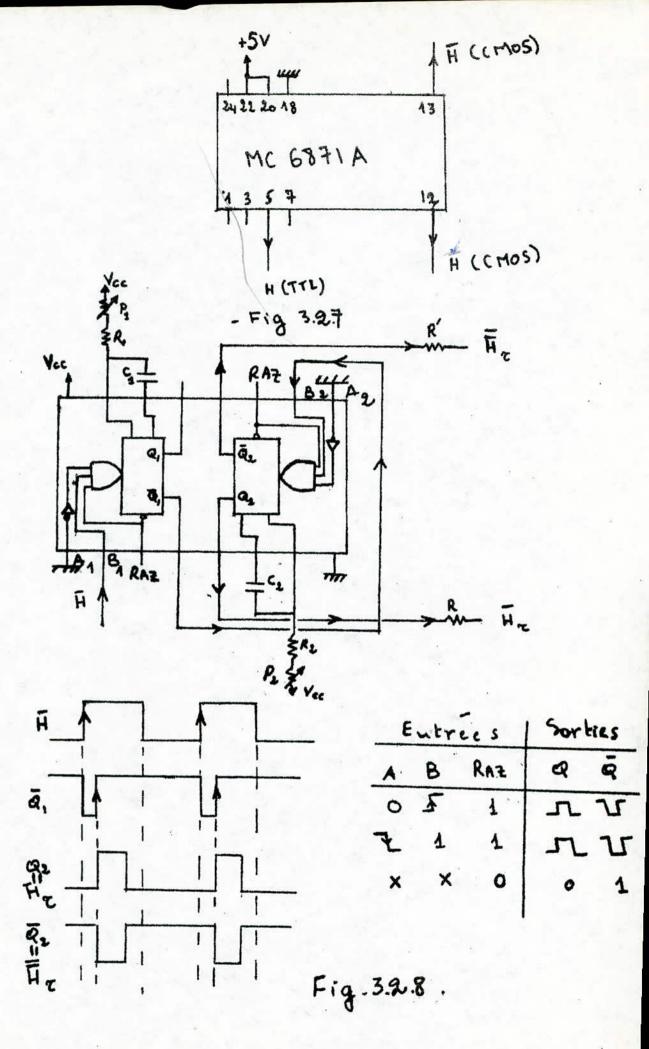

Nous allons voir maintenant, comment générer le signal  $\overset{\sim}{H}_{\mathbf{r}}$  et  $\overset{\sim}{H}_{\mathbf{r}}$  à partir du signal  $\overset{\sim}{H}_{\mathbf{r}}$ .

C'est avec un double monostable qu'on puisse réaliser  $\hat{H}_r$  car on a besoin à la fois de deux opérations, l'une éffectuant le retard du signal, l'autre la réduction du palier.

On a choisi pour cela le circuit intégré SN 74LSI23 (fig. 3.2.8.).

Ce circuit comprend en fait, 2 monostables identiques chaque élément ne comprend qu'une entrée A et une entrée B.

La durée de l'impulsion est définie par un circuit exterieur R.C aprés avoir été déclenché par un front.

Le déclenchement a lieu pour un front négatif appliqué à l'entrée A où par un front positif appliqué à l'entrée B conformement à la table de vérité fig 3.2.8.

Le schéma adopté est donné fig 3.2.8.

Le signal H est appliquée à l'entrée B ( déclenchement par un front montant ).

R, P, et C, ont été choisi de telle sorte que la durée de l'impulsion se reduit à IOOns pour rattraper le retard dû à la comparaison.

R<sub>2</sub> P<sub>2</sub> et C<sub>2</sub> ont été choisi pour une durée de 300 n s. environ pourvu qu'elle ne dépasse pas les 400 n s. Si non on aura un chevau-chement de 2 informations qui ne concorde pas.

Etant donné que la capacité utilisées sont inférieurs à In f, il faut donc se référer aux caractéristiques donnant la durée en fonct- : -ion de la capacité et la résistances.

On a prie :

Les ajustables  $P_{1}$  et  $P_{2}$  servent uniquement pour un ajistage corrécte des durées.

Le chronogramme de la fig. 3.2.8. éxplique en détail le fonctionnement global de ce montage.

Enfin, les résistances R et R' de 4 7 dhacune servent pour protèger les sorties H et H contre les courts ircuits.

l'intérêt du signal H sera vu par la suite (section 3.2.3.).

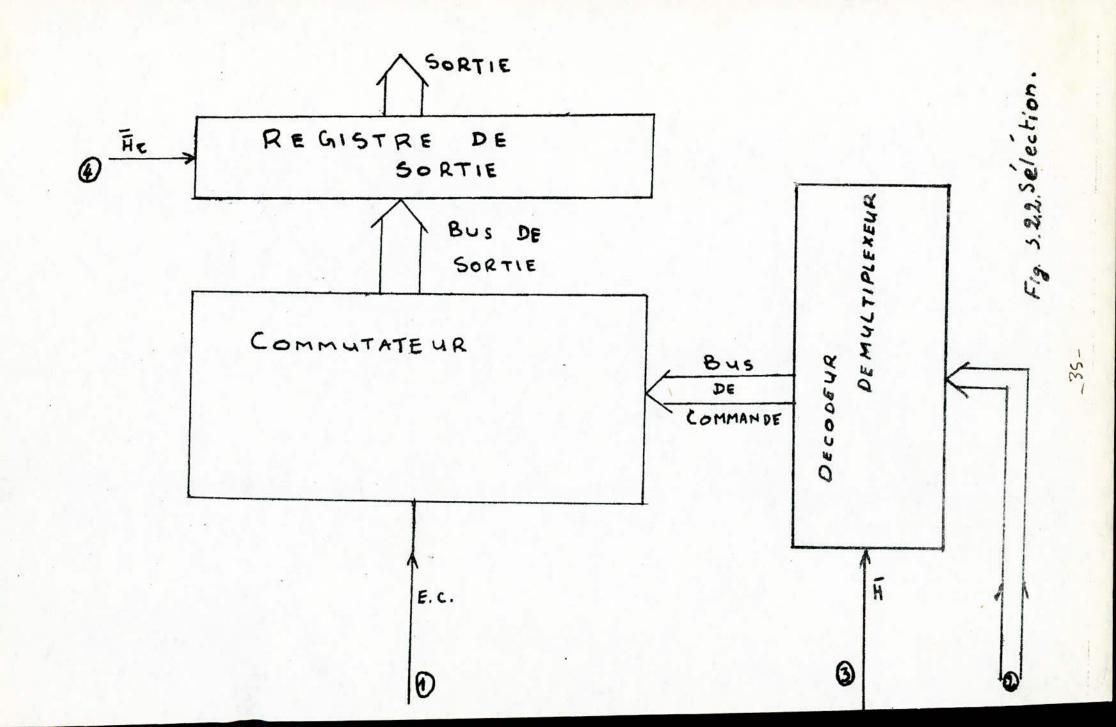

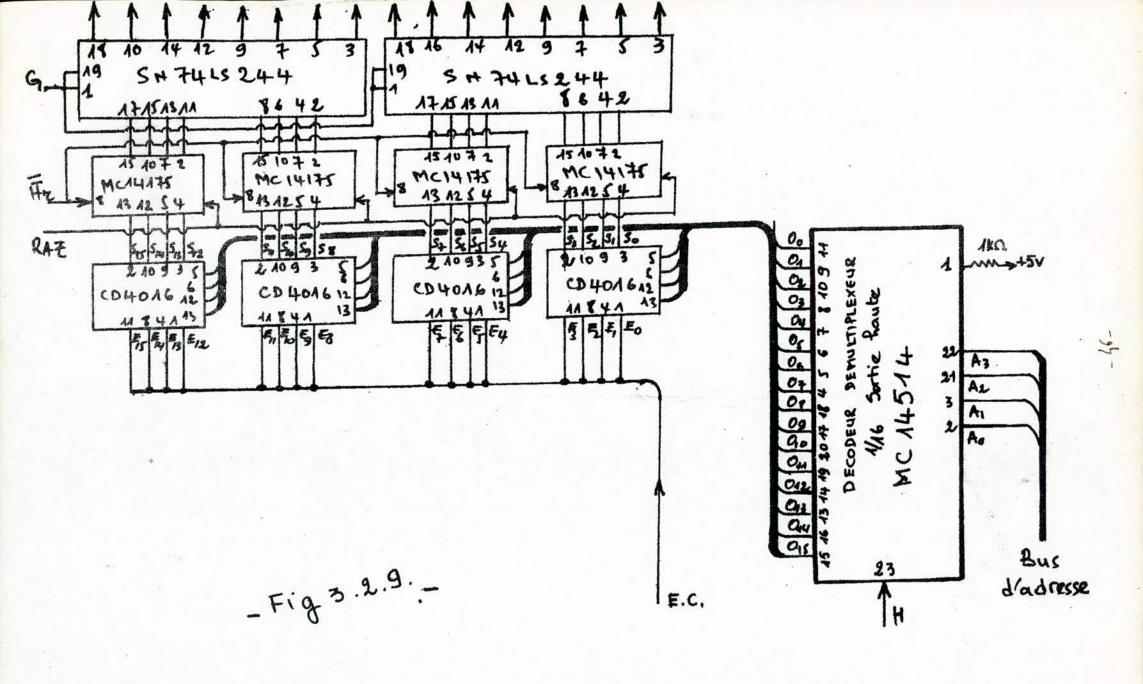

3.2.3. Bloc de séléction :

Il comprend 3 parties (fig. 3.2.9.).

- Décodeur démultiplexeur I/I6.

- Commutateur.

- Régistre de sortie.

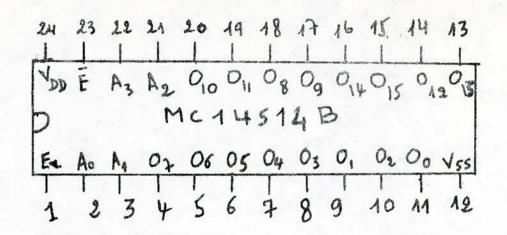

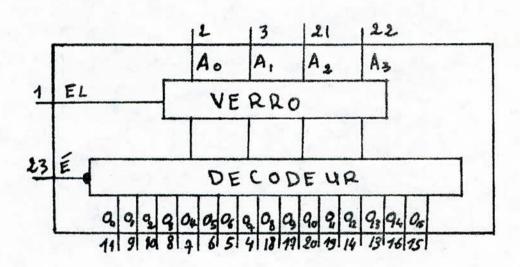

3.2.3.2. Décodeur démultiplexeur I/I6.

Il est réalisé à partir du circuit intégré CMOS le MC 14514 (fig. 3.2.1.0.).

Ce circuit présente l'avantage de disposer de 2 entrées.

Une pour le verrouillage de l'adresse ( E L ) et l'autre pour valider le décodage (  $\widetilde{E}$  ).

.../...

| E | ntrees  |    |    |    |    |      |      | Se               | rt | ie  | ς   |     |     |     |     |     | •   |

|---|---------|----|----|----|----|------|------|------------------|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Ē | AoAIA2A | 0. | 0, | 0, | 03 | O4 ( | )5 C | ) <sub>6</sub> ( | 3  | 8 0 | 9 ( | 010 | 0,, | 012 | 0,3 | 0,4 | 015 |

| 1 | XXXX    | 0  | 0  | 0  | 0  | 0    | 0    | 0                | D  | 0   | 0.  | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0000    | 1  | 0  | 0  | 0  | a    | 0    | 0                | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 1000    | ò  | 4  | 0  | 0  | 0    | 0    | 0                | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0100    | 0  | 0  | 4  | 0  | 0    | 0    | 0                | 0  | 0   | 0   | 0   | 0   | 0   | ø   | 0   | 0   |

| 0 | 1100    | 0  | 0  | 0  | 1  | 0    | 0    | 0                | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0040    | 0  | 0  | 0  | 0  | 4    | 0    | 0                | 0  | 0   | 0   | 0   | Đ   | 0   | 0   | 0   | 0   |

| 0 | 1010    | 0  | 0  | 0  | 0  | 0    | A    | 0                | 0  | 0   | 0   | 0   | D   | 0   | 0   | 00  | ō   |

| 0 | 0110    | 0  | 0  | 0  | 0  | 0    | 0    | 1                | 0  | 0   | 0   | 0   | 0   | .0  | 0   | 0   | 0   |

| Ó | 1110    | 0  | 0  | 0  | 0  | 0    | 0    | 0                | 4  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 0001    | 0  | 0  | 0  | 0  | 0    | 0    | 0                | Ó  | 4   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 1004    | 0  | 0  | 0  | 0  | 0    | 0    | 0                | 0  | 0   | 4   | 0   | 0   | 0   | 0   | 0   | 0   |

| 0 | 04 04   | 0  | 0  | 0  | 0  | 0    | 0    | 0                | 0  | 0   | Ö   | 1   | 0   | 0   | 0   | 0   | 0   |

| 0 | 1 1 01  | 0  | 0  | 0  | 0  | 0    | 0    | 0                | 0  | 0   | 0   | 0   | 4   | 0   | 0   | 0   | 0   |

| 0 | 0014    | 0  | 0  | 0  | 0  | 0    | 0    | 0                | 0  | 0   | 0   | 0   | 0   | 4   | 0   | 0   | 0   |

| 0 | 1011    | 0  | 0  | 0  | 0  | 0    | 0    | 0                | 0  | 0   | 0   | 0   | 0   | 0   | A   | 0   | ٥   |

| - | 0111    | 0  | 0  | 0  | 0  | 0    | 0    | 0                | 0  | 0   | 0   | 0   | ٥   | 0   | . 0 | 4   | 0   |

| 0 | 1111    | 0  | 6  | 0  | 0  | 0    | 0    | 0                | ٥  | 0   | .0  | 0   | 0   | 0   | 0   | 0   | 1   |

Fig 3.2.10.

Ce circuit présente également l'intêret d'avoir la sortie selec--tionnée à l'état haut et les autres à l'état bas conformement à la table de vérité donnée fig 3.2.10.

Au niveau du commutateur, on aura deux informations qui arrivent il faut donc les synchroniser.

Pour cela on a appliqué à l'entrée de validation du décodeur (broche 23 ) le signal d'horloge H.

Ce signal permet de faire fonctionner le décodeur uniquement lorsqu'il est à l'état bas, d'où le chronogramme suivant :

On voie que cette information sera présentér à l'entrée commande du commutateur pendant 500 ns lorsque H passe de " I " à " 0 ".

Parallélement on a vu que l'autre information (sortie comman--dée venant du comparateur) est présente elle aussi pendant cet inter--valle de temps d'où on a bien synchronisation.

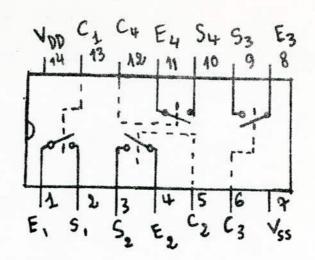

3.2.3.2. Commutateur :

Il est réalisé à partir du circuit intégré CMOS le CD 4016 (fig 3.2.II.).

Ce boitier contient en fait 4 commutateurs bidirectionnels dont chacun possède une entrée de commande d'ouverture où de ferméture de cet interrupteur électronique.

Etant donné qu'on a 16 sorties, il nous faut donc 4 boitiers C D 4 O I 6.

Les commandes sont reliées au décodeur.

Les entrées sont toutes reliées à la sortie commandée (fig 3;2;9.).

Brochage du CI CD4016

Brochage du CI MC 14175.

Fig 3.2.11

Donc selon l'adresse présente à l'entrée du décodeur, on aura un seul commutateur qui va être fermer, les autres restent ouverts, et par la suite l'information à l'entrée sera récurérée à la sortie correspondante.

Et par de procédé on aura, à chaque coup d'horloge, un seul état qui va être affecter à la sortie finale.

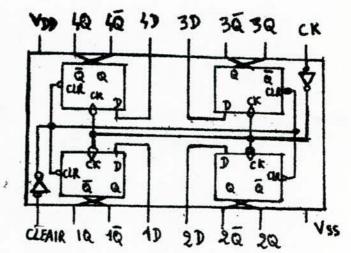

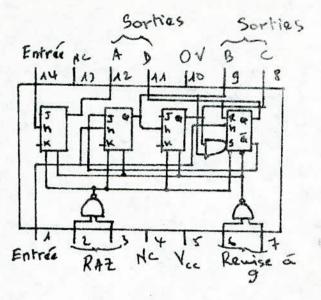

3.2.3.3. Régistre de sortie :

Ce régistre sert à garder en mémoire chaque mot pendant une période d'horloge.

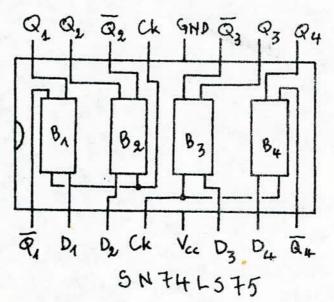

Il est réalisé par le circuit intégré MC I4 \$75 (fig 3.2.22 ).

Ce circuit contient 4 bascules D synchronisées par une seule horloge et une entrée R A Z commune.

L'entrée horloge est attaquée par le signal H. pour qu'elle puisse recopier le mot présent à l'entrée.

Vu que le régistre de sortie, est à téchnologie CMOS, chaque sortie est buférées dans le but de pouvoir attaquer plusieurs entrances.

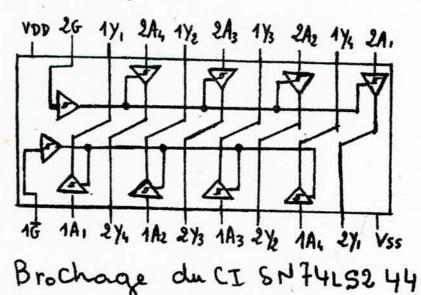

Le buffer utilisé étant le circuit S N 74LS 224. (voir fig; 3.2.II.).

## 3 . 2 . 4 . COMMANDE :

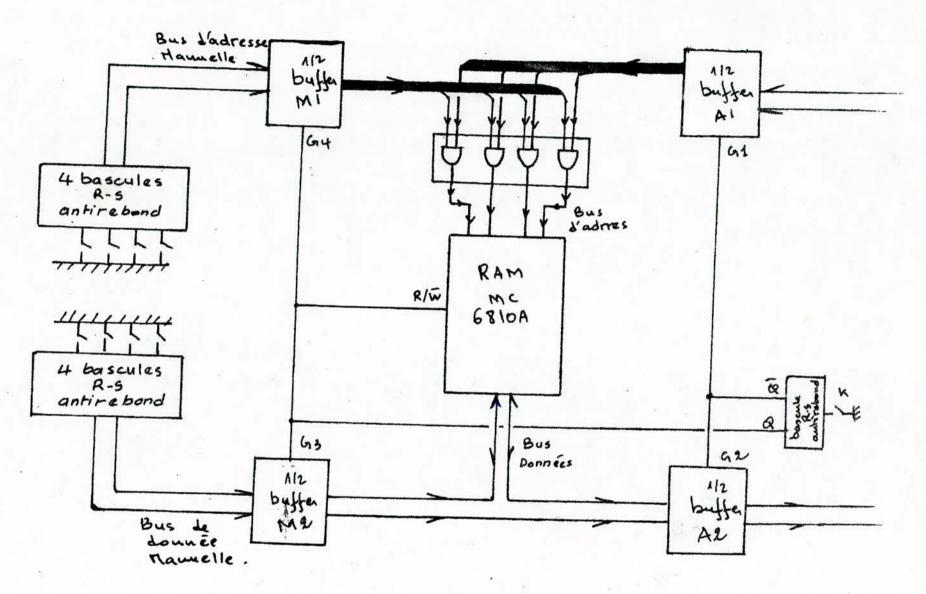

Le schéma synoptique est donné fig. 3:2.I.2.

On distingue donc 2 types de commandes: mannelle et auto-matique.

3.2.4.2. Commande manuelle:

Elle permet de choisir la probabilité qu'on désire avoir à la sortie.

Atant donné qu'on a 16 sorties, il nous faut donc une mémoire de 75 mots pour stocker les différentes probabilités.

La longueur du mot à été fixé à 4 bits, vu qu'on a besoin seulement de quelque probabilités remarquables.

Des mots de 4 bits peuvent former seulement I6 probabilités différentes qui sont données par le tableau suivant :

.../...

Fig 3.2.12.

Size

| 0 | (i | 4. | 0 | 0,125  |

|---|----|----|---|--------|

| 0 | 0  | 7. | I | 0,1875 |

| 0 | I  | G  | 0 | 0,25   |

| 0 | I  | O  | I | 0,3225 |

| 0 | I  | Ι  | 0 | 0,385  |

| 0 | I  | Ι  | I | 0,4375 |

| I | 0  | 0  | 0 | 0,5000 |

| I | 0  | 0  | I | 0,5625 |

| I | 0  | 1  | 0 | 0,625  |

| I | 0  | Ι  | I | 0,6875 |

| I | I  | 0  | 0 | 0,7500 |

| I | I  | 0  | I | 0,8125 |

| I | I  | Ι  | 0 | 0,875  |

| I | I  | Ι  | I | 0,9375 |

TABLEAU 3 . 2 . EI.

L'écart entre 2 probabilité successives est de 0,0625, pour le réduire il suffit d'augmenter la longueur du mot.

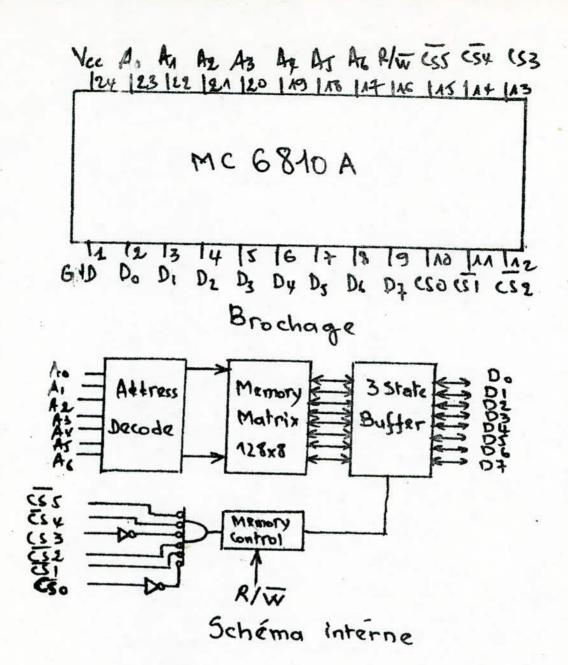

La R A M MC 68I0 A est utilisée pour réaliser le but recher--chér

Cette mémoire (fig. 3.2.13) posséde un bus de donnée bidirec--tionnel, da taille est de 128 x 8 bits.

Pour réduire cette taille à I6 x 4 bits il suffit de mettre à la masse A\_4 , A\_5 , A\_6 , D\_4 , D\_5 , D\_6 et D\_7 .

Si l'entrée R/W = "0", on obtient le mode écriture qui correspond à la commande manuelle d'où il fant que les buffers M, et  $M_2$  conduise par contre les buffers A et  $A_2$  soient à l'état haute impédance.

Pour réaliser ceci, il suffit donc d'avoir :

$$R/W = G_3 = G_4 = "O"$$

et  $G_1 = G_2 = "I"$ .

.../...

| CSO | CSI | czs | C53 | C54 | <b>CS</b> 5 |

|-----|-----|-----|-----|-----|-------------|

| 1   | 0   | 0   | 1   | 0   | 0           |

table de fonction normale.

- fig 3.2.13\_

Les entrées  $G_i$  permettent de mettre le buffer soit à l'état . passant soit à l'état haute imdédance.

si G = " 0 " le buffer est passant

si G = " I " le buffer est en haute impédance.

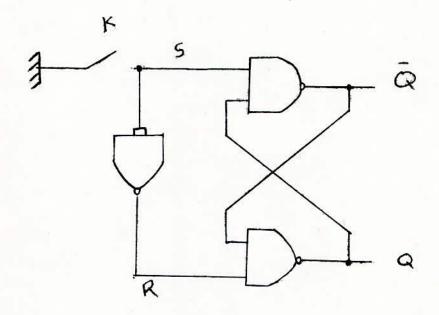

Cette commande peut-être faite à l'aide d'une bascule R - S anti-rebond qui a pour éffet d'éliminer les phénoménes transitoires dû à l'intérrupteur, son schéma éléctrique est le suivant :

Fig. 3.2.14.

Si K est ouvert R = "0" S = 3 I" alors Q= "I"

Si K est fermé R = "I" S = "0" alors  $\overset{\cdot \cdot \cdot}{Q}$  = "I" et Q = "0".

Si par exemple  $Q = G_I = G_2$  et  $\overline{Q} = G_3 = G_4 = R/W$ .

Alors K ouvert correspond au mode manuelle et K fermé au mode automatique.

L'entrée des données et l'adressage de la R A M se fait égale--ment à partir des bascules anti-rebond. (fig. 3.2.14.).

A chaque bit on fait correspondre une bascule R . S . 3.2.4.2. Commande automatique :

Elle correspond au régime de fonctionnement de notre générateur.

Dans ce mode, l'entrée R/W de la R.A.M se met à l'état lecture

par conséquent les buffers A<sub>I</sub> et A<sub>2</sub> conduisent, par M<sub>I</sub> et M<sub>2</sub> SONT

à l'état haute impédance, ce qui a pour éffet d'interpmpre complétement

le mode manuelle.

Le balayage de l'adressage de la mémoire s'opére d'une manière pseudo-aléatoire.

Les 4 portes A N D présentent à l'nntrée des bits d'adressages ont pour rêles d'éviter de relier 2 sorties T T L ( provenant des buffers  $\rm M_I$  et  $\rm A_I$  ) entre elles.

On remarque dans le tableau 3.2.I. que la probabilité I ne figure pas, alos que dans la pratique, il est intéressant d'avoir cette probabilité.

Il suffit d'affecter à IIII la probabilité I étant donné que 0,9375 n'a pas beaucoup d'intérêt dans la pratique.

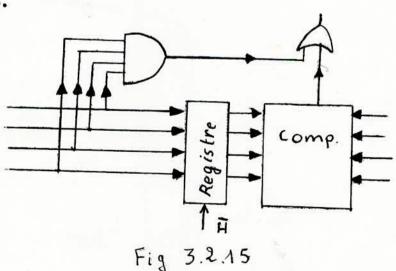

Pour réaliser ceci, on procède comme indique la figure 3.2.15.

La porte AND à quatre entrées détécte la donnée IIII, et quelque soit la sortie du comparateur on aura un "I" à la sortie de la porte OR.

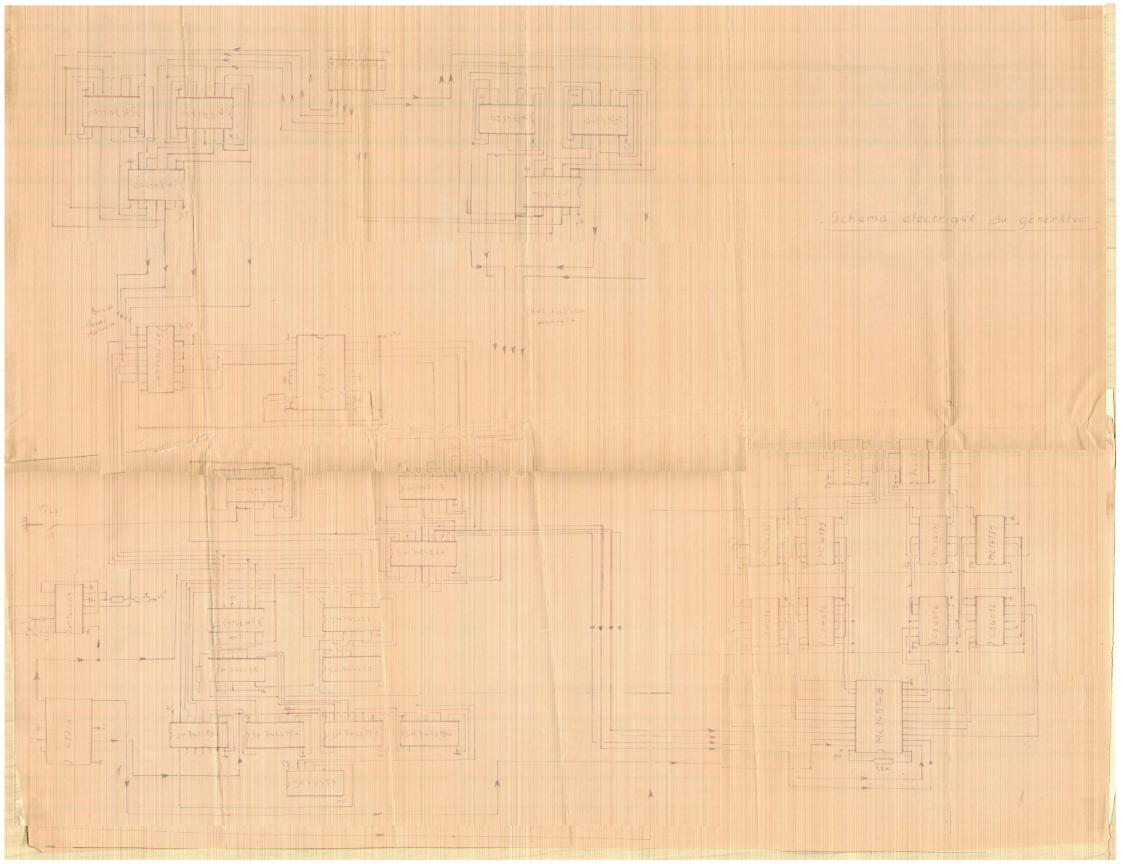

Fig. 3.2.16. : \_ Schéma fonctionnel du générateur\_

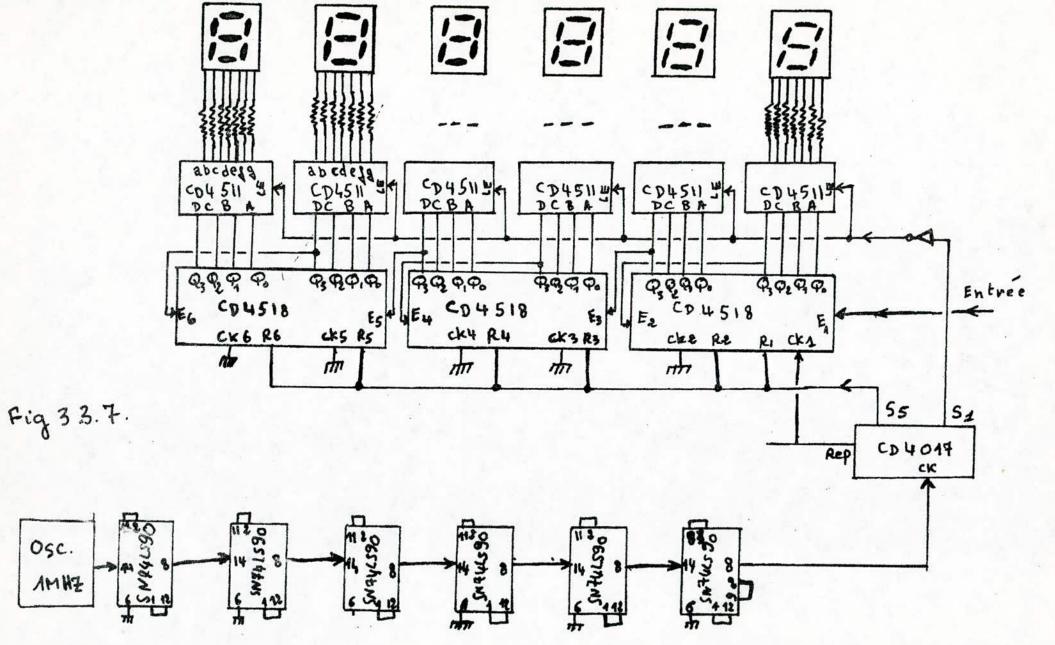

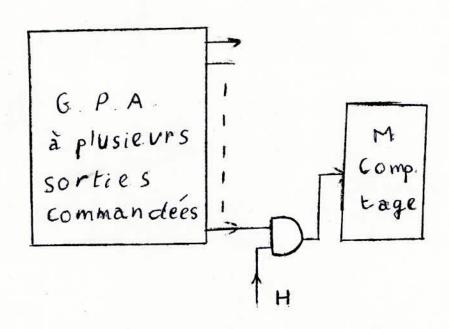

3 . 3 . Module de comptage :

3 . 3 . 1 . INTRODUCTION :

Etant donné que l'oxilloscope ne permet pas de mesurer la probabili--té à la sortie, on a été amené à réaliser un module de comptage qui résoud ce problème.

Ce module nous sert éssentiellement pour la mesure ( c-a-d la vérifi--cation ) des probabilités des différentes positions du régistre de sortie.

Il permet également de vérifier si le générateur pseudo-aléatoire pulse des séquences de longueur maximale ou non.

3 .33 . 2 . Schéma de principe et fonctionnement :

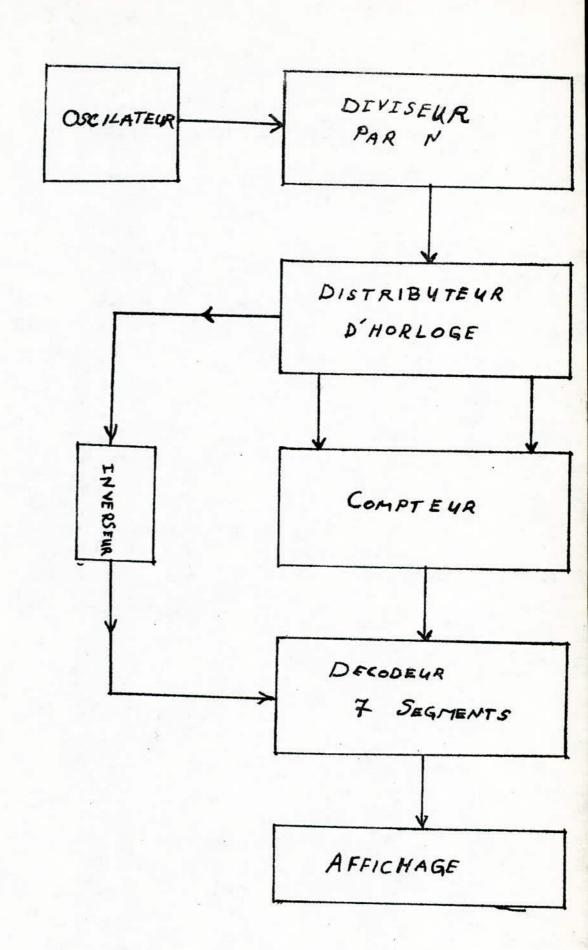

Le schéma synoptique est donne fig. 3.3.1.

Le module est basé sur le même principe d'un fréquencemètre c-a-d le comptage se fait pendant un temps T bien déterminé, choisi au préalable et qui est un multiple de la longueur maximale de la séquence générée par le G . S . P . A .

c-a-d.

$$t = KL$$

avec K entier.

$$L = 2^{15} - 1$$

$$= 1 s.$$

Donc la probabilité affichée n'est rien d'autre que le nombre de " 1 " d'une séquence de sortie sur le nombre d'impusion d'horloge pendant le temps t.

Le Schéma comprend :

3 . 3 . 2 . 1 . Oscillateur :

Pour obtenir des mesures précises, il faut que l'oxillateur soit stable en fréquence, d'où la nécéssité d'un quarti

Puisqu'on dispose d'un oscillateur de 1 M H Z, il suffit donc de réaliser un diviseur.

Etant donné que t = KL avec  $K \equiv N$ , prenons par éxemple K = 6.

d'où t<sub>o</sub> = 0, 1966s.

qui donne  $F_0 = 1/t = S_0 0 8 6 H Z_0$

Si on utilise le circuit intégré S N 7 4 L S 9 0 (fig. 3.3.2. ). il nous faut 6 boitiers réaliser le but recherché

- 5 boitiers pour la division par 8.

- 1 boitiers pour la division par 6.

Et de cette façon la fréquence  $f_o = 5$ , 0 8 6 H Z sera obtenue à partir de la fréquence 1 M H Z.

3 . 3 . 2 . 2 . Distributeur d'horloge.

Ce bloc nous délivre les différents signaux qui permettent le comptage, la remise à zéro ainsi que l'affichage.

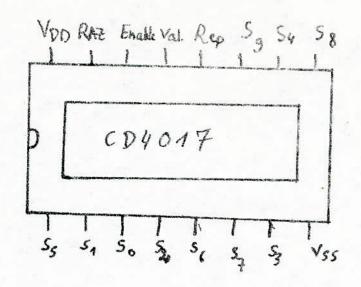

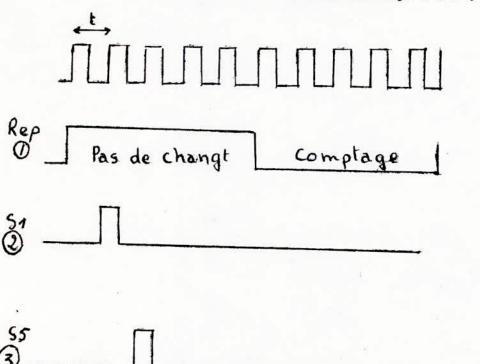

Il est réalisé à partir du circuit intégré C M O S CD 4 O 1 7 (fig; 3 . 3 . 3 .) qui est un compteur de décader, c-a-d qu'il avance pas à pas au rythme des impulsions d'horloge à front raide positif présentées sur l'entrée E. Par déplacement du niveau logique " 1 " sur les différentes sorties  $S_0$ ,  $S_1$  ---  $S_9$  les autres sorties restant au niveau logique " 0 ". Cette avance du compteur se produit uniquement si l'entrée V de validation se trouve au niveau logique " o ".

Toute impulsion positive sur l'entrée R A Z provoque la remise à zéro du compteur.

La fréquence  $f_o$  obtenue par division, servira comme signal d'hor-loge du circuit C D 4 O 1 7.

A partir de ce dernier, on a besoin seulement de 3 signaux, le premier permettant le comptage pendant 5 t, le deuxième assurant l'afficha-ge.

Brochage SN74LS90

| Division | Entraé | Sortie | Liaisons a effectuer     |

|----------|--------|--------|--------------------------|

| 2        | 14     | 12     | 2 st 6 à la masser       |

| 3        | 1      | 9      | 8 à 3, 9 à 2, 6 masse    |

| 4        | 1      | 8      | 11 = 2 at 3, 6 masse     |

| 5        | i      | ٨٨     | late à la masse.         |

| 6        | 14     | 8      | 12 a 1 9 a 2 8 a 3 6 ms  |

| 7        | 1      | 14     | 11214, 1222, 8=3,6 mase  |

| 8        | 14     | 8      | 12 a1 , 11 a 2 , 6 masse |

| 9        | 14     | 10     | 112 12 3, 1221, 6 mass   |

| 10       | 14     | 11     | 12a1, 2 et 6a la masse   |

Fig 3.3.2.

brochage du CD4017

| E | 50 | s, | 52 | 53 | 54 | 55 | Sr | 57 | 51 | 543 | R |

|---|----|----|----|----|----|----|----|----|----|-----|---|

| 1 | 4  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1 |

| 4 | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1 |

| 1 | 0  | 0  | 4  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1 |

| 个 | 0  | 0  | 0  | 4  | 0  | 0  | 0  | 0  | 0  | 0   | A |

| 1 | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0   | 1 |

| Ť | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0   | 0 |

| † | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0   | 0 |

| 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4  | 0  | 0   | 0 |

| 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4  | 0   | 0 |

| 4 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1   | 0 |

Table de Vérité du CD 4017

et enfin le dernier e e compteur à zéro. chaque fois qu'il recommence à compter de nouveau.

Pour plus de détail voir chronogramme fig. 3 . 3 . 4.

fig. 3 . 3 . 4 .

### 3 . 3 . 4 . Compteur :

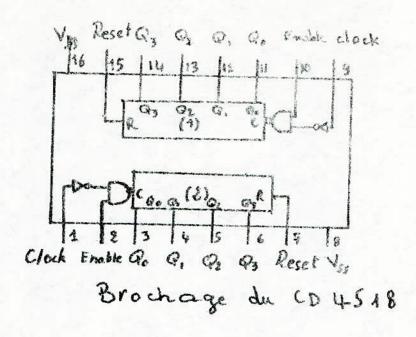

Il est réalisé à partir du circuit intégré C M O S C D . 5 . 8 (fig. 3 . 3 . 5 . ).

Ce circuit contient en fait 2 compteurs identiques intégrés dans un seul boitier.

Il éxiste 2 modes de comptage conformement à la table de vérité fig. 3 . 3 . 5 .

On a choisi la configuration suivante :

L'entrée clock sera attaquée par le signal (1) qui permet le comptage pendant S t et l'arrêt pendant S t?

Le signal ( 2 ) sera appliqué à l'entrée R A Z du compteur. Le comptage des impulsions se fait à travers l'entrée Enable.

| Clock | Enable | RAZ | Résultat       |

|-------|--------|-----|----------------|

| 5     | 4      | 0   | Incrementation |

| 0     | -F     | 0   | Incrementation |

| T     | ×      | 0   | Pas de changt  |

| ×     | 5      | Ð   | Pas de changt  |

| 不     | 0      | 0   | I as de changt |

| A     | F      | 0   | Pas de change  |

| ×     | ×      | 4   | Q==== Q3 = 0   |

Table de Vérité du CD4518.

Fig 3.3.5

La mise en cascade de plusieurs compteurs s'éffectue en reliant la sortie Q3 à l'entrée Enable de l'autre compteur.

## 3 . 3 . 5 . Décodeur + Afficheur :

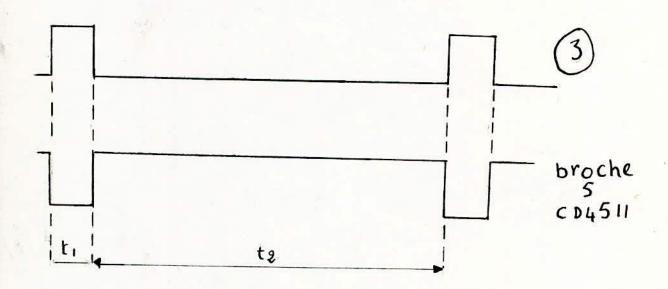

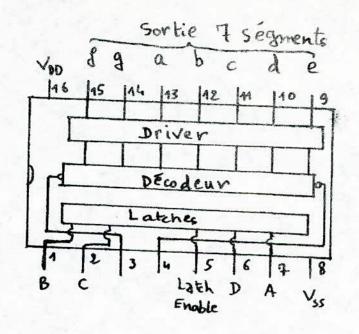

Le décodeur à été réalisé par le circuit intégré CMOS CD45II (fig. 3.3.6.).

Ce circuit recopie ce qu'il ya aux entrées DC BA dés que la broche 5 passe à l'état " o ".

Le décodage s'éffectue lorsque les broches 3 et 4 sont au niveau logique " I ".

Le signal (3) sera inversé avant d'être appliqué à la broche 5 du décodeur.

Pendant le temps  $t_{I}$ , le décodeur recopie ce qu'il a son entrée.

Pendant le temps  $t_2$  , il garde l'information recopiée en mé-moire.

Enfin des afficheurs du type cathode commune assurent l'afficha--ge en décimal.

Le schéma éléctrique global est donné fig. 3 . 3 . 7 .

brochage du CD4511

| Entices           |    |      | Sorties                       |

|-------------------|----|------|-------------------------------|

| broches<br>3 et 4 | LE | DCBA | Fga bc de                     |

| 0                 | ×  | ×    | 111111                        |

| 1                 | 1  | X    |                               |

| 1                 | 0  |      | Pas de changement<br>décodage |

table de vérité du 4511

fig 33.6.

Pour la mesure des probabilités à la sortic il suffit de procédor comme indiqué fig. 3.4. I:

Les résultats obtenus sont donnés par les

tableaux I et II

Conclusion:

Les résultats experimentaix obtems à la soite de notre générateur sont conformes avoi le probabilités inscrites dans la R.A.M.

le variations sont acceptable.

On voit donc, vier que votre générateur et commandable, ce qui et le but retherché.

Poite fois, on pour amélioner as resultats en augmentant la longueur du régistre à décalage. ( constation vu en matique

la consumation de generatem et de l'ordre 1 SoomA.

| DA      | 0000   | 0001   | oalo   | 0011   | 0100   | 0101    | 0110   | 0111   |

|---------|--------|--------|--------|--------|--------|---------|--------|--------|

| 0000    | 0      | 0      | O      | 0      | 0      | 0       | O      | 0      |

| 0001    | 0,0596 | 0,0513 | 0,0564 | 0,0385 | 0,0519 | 0,0562  | 0,0715 | 0,0915 |

| 0010    | 0,1306 | 0,1003 | 0,1    | 0,00   |        | 0,1216  |        | 100    |

| 0011    | 0,1916 | 0,1503 | 9,1509 | 0,1506 | 0,1612 | 1 25576 |        | 0,2105 |

| 0100    |        |        |        | 0,2175 |        | 0       |        | 17     |

| 0101    |        |        |        |        |        |         |        | 03306  |

| 0110    | 0,4    | 0,3415 | 0,378  | 93761  | 0,3908 | 0,4186  | 0,3646 | 41850  |

| 0111    |        |        |        |        |        |         |        | 0,4304 |

| V 0 0 D |        |        |        |        |        |         |        | 0,5310 |

| 1001    |        |        |        |        |        | 0,5412  |        |        |

| 1010    |        |        |        |        |        |         |        | 0,6415 |

| 1011    | 0,72   | 0,7178 | 0,6314 | 0,66   | 0,699  | 96866   |        | 0,6896 |

| 1100    | 0,7978 | 0,786  | 0,720  | 0,7514 | 97602  | 0,7391  | 9,780  | 9,7366 |

| 1101    | 0,8085 | 9,8691 | 9779   | 0,5178 | 09519  | 0,8009  | 9,8069 | 0,8219 |

| 1110    | 0,0311 | 0,9217 | 0,8401 | 9,8178 | 0,9366 | 0,8619  | 9,869  | 0,8911 |

| 1111    | 1      | 1      | ٨      | ٨      | 1      | 1       | 1      | 1      |

Tableon I

| DA          | 4000   | 4001    | 4010   | 4011   | 4100   | 4101          | 4110   | 4111    |

|-------------|--------|---------|--------|--------|--------|---------------|--------|---------|

| 0000        | 0      | 0       |        | 0      | 0      |               | 6      | 0       |

| Ø001        | 0,000  | 0,040   | 0,088  | 0,0627 | 0,6765 | 0,09          | 0,08   | 0,0687  |

| 0010        | 0,08   | 0,1330  | 0,154  | 0,127  | 0,157  | 0,14          | 0,14   | 0,136   |

| 0011        | 0,137  | 0,1850  | 0,22   |        | 0,2319 | 0,2384        |        | 0 1912  |

| 0100        | 0,2174 | 0,2115  | 00-    |        |        | 0,2901        | '      | 0, 1861 |

| 0101        | 0,2797 | 0,280   |        |        |        |               |        | 0,3200  |

| 0110        | 0,3428 | 0,3037  |        |        |        | 0,3889        |        |         |

| NAKO        | 0,3811 | 0,4 335 | 0,5246 |        |        | 0,43.4        | - 1    |         |

| 1000        | 0,4371 |         |        |        |        |               | 8 1    | 0,5205  |

| 1001        | 0,4783 |         |        |        |        |               |        | 0,6019  |

| 1010        | 0,5338 | 0,6007  | 0,70%  | 0,62   | 0,6599 | 0,6017        | 6117   | 0,6717  |

| NON         | 0,5978 | 0,16    |        |        |        | The second of | 377    | 0,7302  |

| 1100        | 0,6584 | 0,97    | 0,82   | 0,7104 | 0,7608 | 0,706         | 97306  | e, 78   |

| 1011        | 0,7164 | 0,8132  | -,8961 | 0, ४थ  | 0,8478 | 7569          | 0,7867 | 59567   |

| 1110        | 0,8115 | 0,8667  | 0,927  | 0,8338 | 0,874  | 0,8077        | 0,8415 | 99171   |

| 1 1 1 1 1 A | 1      | 1       | 1      | 1      | 1      | 1             | 1      | 1       |

\_ Tableau II \_

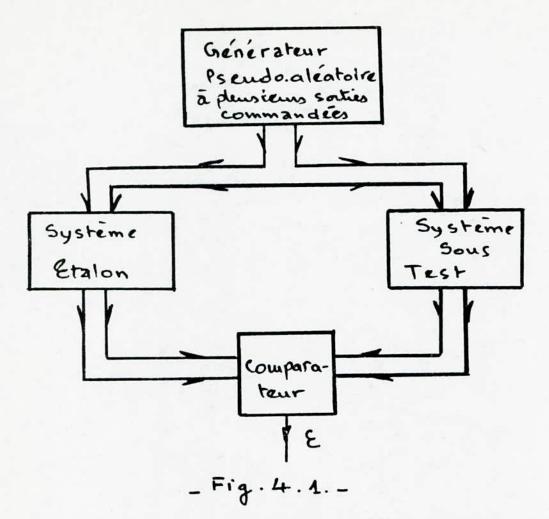

# CHAPITRE T : APPLICATION

Notre générateur a été conçu pour faire le diagnostic des pannes dans les circuits numérique.

Comme il peut être util pour "fabriquer" un bruit analogique.

yus allons voir comment il peut être introduit pour détécter les erreurs dans les circuits logiques.

### 4.I. Test par comparaison :

Cette méthode, désormais ancienne, consiste à comparer les sorties du système sous test avec celles . du système étalon .

Le schéma de principe est donné fig. 4.I.

Ce type de test par comparais on nécéssite l'emploi d'un systés étalon.

La comparaison peut être faite mot à mot , et de cette façon on détecte si notre circuit est en pannes ou non , sans localiser l'erreur .

Mais si la comparaison s'effectue bit par bit càd chaque sortie avec celle qui lui correspond, on aboutit à localiser la ou les sorties d'où vient l'erreur, dans ce cas, le comparateur se réduit donc pour chaque couple de sorties à un soul XOR.

Dans la pratique, il est intéressant de connaître le mot , à la sortie du générateur , qui à détécter la panne .

Les inconvenients de cette méthode réside

dans le fait qu'on à pas de possibilités de locali r

la pas et en plus on a besoin d'un étalen physique.

On peut remplacer l'étalon physique parun autre mathématique qui puisse réaliser les mêmes fonctions (c'est par programmation) caid que ce programme modélise le fonctionnement de l'élaton physique.

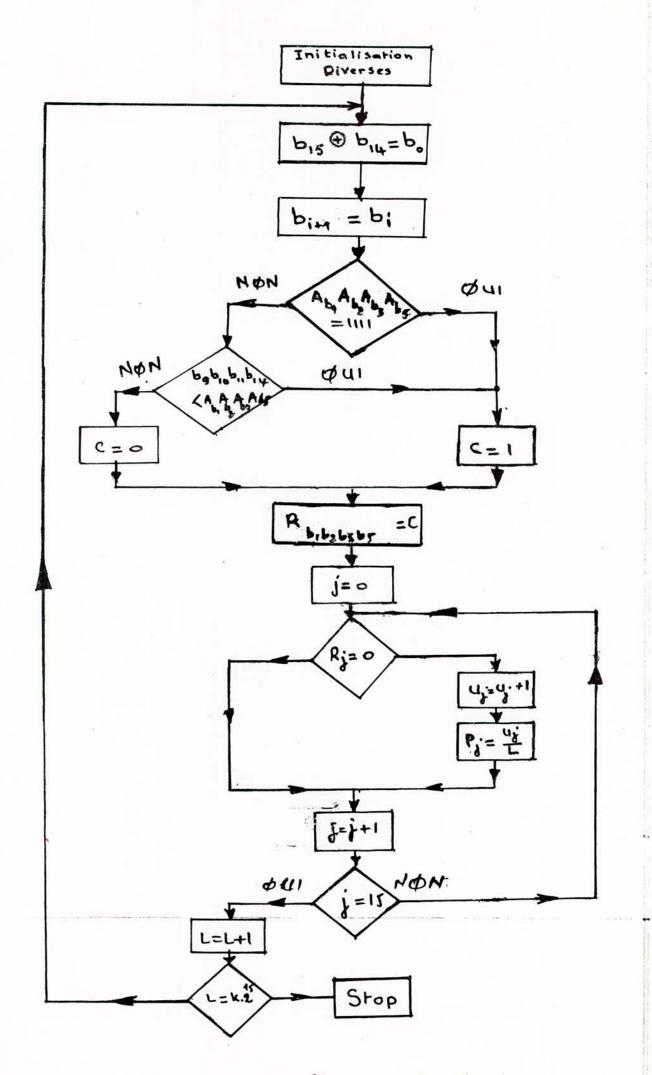

Chapitre I SIMULATION DE NOTRE GENERATEUR PAR UN PROGRAMME EN LANGAGE BASIC.

Il est préférable, avant d'entamer une réalisation (Logique rablée), de simuler cette dernière par un programme, dons le but d'optimiser et d'améliorer la rouseption du produit.

Stucture du programme.

Les lignes 10 à 35 initialisent le 16 états du régistre de sortie.

la lignes 40 à 710 permettent de faire entrer le 16 données (Probabilités) de la RAM.

De 114 à 238 simulent le G.S.P.A à 15 étages De 240 à 270 adressent la RAM.

le lignes 276 à 422 correspondent à la donnée qui sorte de la RAM.

la lique 4 26 détecte le mot 1111 (cimulation d'une porte AND à 4 entrées)

De 428 à 455: sinulation du comparateur le liques 468 à 498 correspondent à la selection du communateur.

De 500 à 560 détecte la Sortie va être affecter.

De 570 à 632 représentent le module du comptage pour sortie du requistre la lign 634 affiche sur l'écran le sequences de sorties les lignes 640 à 670 Scrutent le clavier pour faire appelle à les sous-programme 675: lit le clavier (commande manuelle qui a pour but de faire changer les probabilités inscritent dans la RAM)

677: 6.M. affichage son l'écran les 16 probabilité.

682 et 686 : condition Dés que 5=9 Vécran séfface.

le ligne 690 à 845 : c'et le sous programmes qui sont appelés par le touches du clavier (donc on a la possibilité de faire entreé une seule donnée.

850 à 880 : culculent les Probabilités. 885 : affichage de 16 probabilités. 890 : 895 -, 905 et 910 : possibilité de continuer le programme.

900 arrêt du programme.

30 Data 0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0

35 Data 0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0

40 Input D., D., D2, D3

45 Input E., E,, Ez, Ez

50 Input F., F., Fz, Fz

55 Input Go, Gi, Gz, Gz

60 Input Ho, H, Hz, H3

65 Input I., 1, 12, 13

to Input J., J., Jz, J3

75 Input k., K., Kz, Kz

80 Input Mo, M., Mz, M3

85 Input H., N., Hz, N3

90 Input 00, 01, 02,03

95 Input To, T1, T2, T3

100 Input X., X., Xz, X3

105 Input Y, 7, 72, 73

107 Input Z., Z., Zz, Z3

MOIMPUT Wo, W, WZ, WZ

112 Let L=1

114 Let by = 0

116 Let b2 = 0

119 Let b3 = 0

120 Let 64=0

122 Let b = 0

124 Let 6 = 0

126 Let b = 0

128 Let 6=0

130 Let b g=0

132 Let 6,0=0

134 Let b11=0

136 Let b12 =0

121 Let 613 =0

140 Let big = 0

142 Let b15=1

145 Let 3=0

150 if bit=0 and bis=0 or bit=1 and bis=1 Then let bo=0

200 if biv= and bis= 1 or biv= and bis= o Then Let bo=1

210 Let bis= biy

212 Let bi4= bi3

214 Let bis = biz

216 let biz = b11

218 Let b11 = b10

llo let bio=bg

222 Let bg = b8

224 Let bz = bz

226 Let by = 66

228 Let be = b5

230 Let b5= 64

232 Let by= b3

234 Let by= bz

236 Let b2 = b1

239 Let b = bo

240 if B, = 0 and bz = 0 and bz = 0 and bs = 0 Then Goto 276

242 if b, = 0 and bz= and bz= and bz= 1 Then Gotte 286

244 if b, =0 and bz=0 and bz= 1 and bz=0 Then Goto 296

246 if b,=0 and b2=0 and b3=1 and b5=1 Then G+T+ 306

248 if b, = 0 and b = 1 and b = 0 and b = 0 Then GoT \$ 316

250 if b,=0 and b2=1 and b3=0 and b5=1 Then GATH 326

252 if b1=0 and b2=1 and b3=1 and b5=0 Then Go To 336

254 if b, = and bz=1 and bz=1 and bz=1 Then GAT# 346

256 if b,=1 and b=0 and b=0 and b=0 Then 4x716356

258 if bi= 1 and bi= 0 and bi= 0 and bi= 1 Thru 4474366

The if bi= 1 and bz= 0 and bz= 1 and bz= o Then GKTK 3to

262 if b\_= 1 and b\_= 0 and b\_= 1 and b\_= 1 Then GaT 386

264 if b= 1 and b= 1 and b3 = 0 and b5=0 Then Gotte 396

Ellif b,= 1 and bz=1 and bz=0 and bz=1 Then GoTo 406

268 if b = 1 and b = 1 and b = 1 and b = 0 Then GoTo416

270 if b= 1 and b= 1 and b= 1 and b= 1 Then Gots 426

27 Let A .= D.

278 Let A = D,

280 Let A = D2

282 Let A3 = D3

284 GOTO 424

286 Let Ao= Fo

288 Let A = E,

230 Let Az=Ez

292 Let A3=E3

294 641 \$ 424

296 Let A = F.

298 Let A = F,

300 Let Azzfz

3.02 Let A3 = F3

304 G6 T& 424

306 Let A .= 4.

309 Let A = 61

3.10 Let Az= 62

312 Let Az= Gz

314 60 76 424

316 Let A .= H.

318 Let A = H.

320 Let Az= Hz

322 Let A3= 43

324 GATA 424

326 Let Ao = Io.

328 Let A = I1

330 let Az=Iz

332 Let A3 = I3

334 GOT 424

336 Let 4 = Jo

338 Let A = J,

340 Let Az=Jz 342 Let A3 = J3 344 GOTO 424 346 LRF 40 = K. 348 Let AI = KI 350 Let Az= Kz 352 Let A3 = k3 354 GOTA 424 356 Let Ao= Mo 358 Let 4,= 17 A 360 Let Az = Mz 362 Let A3 = M3 364 CAPTO 424 366 Let AozNo 368 Let A = H1 370 Let Az=Nz 372 Let Az= N3 374 COTO 424 376 Let Ao= 0. 378 Let A= 0, 380 Let A2 = 02 382 Let A3 = 03 384 GOTO 424 386 Let Ao=To 388 LEH AZ=TI 390 Let Az=Tz 392 Let Az= Tz

424 GATO 394 396 Let Au= Xo 398 Let A1= X1 400 Let Az = XL Let A 3 = x3 402 6 4 T 4 4 24 404 Let Ao = Yo 406 Let A = Y1 409 910 Let Az= Yu 412 Let A3= Y3 414 GOTO 424 Let Ao= to 416 418 Let A = Z, 420 Let Az=Zz Let As= 23 422 424 GATOS 424 426 Let Ao=wo Let An=w, 428 430 Let Az = We 432 Let A3 = W3 424 Fast 426 if A= 1 and A= 1 and A=1 and Az = 1 Then GATA 445 428 if bg (A3 Then GOTO 445 430 if bg > As Then hote 445 432 if 610 < Azthen Got 445 434 if  $b_{10} > A_2$  then goto 455 436 if  $b_{11} < A_1$  then goto 445 438 if  $b_{11} > A_1$  then goto 455 440 if  $b_{11} < A_0$  then goto 455 442 if  $b_{14} > A_0$  then goto 455 442 if  $b_{14} > A_0$  then goto 455 445 Let c = 1450 goto 468 455 Let c = 0

468 if b1 = 0 and b2 = 0 and b3 = 0 and b5=0 then goto 500 470 ig b, = 0 and be = 0 and b3 = 0 and b5 = 1 then goto 504 472 g by = 0 and be = 0 and by = 1 and by = 0 then goto 508 and  $b_3 = 1$  and  $b_5 = 1$  then goto 512 474 if by = 0 and bz = 0 476 yb, = 0 and be = 1 and by = 0 and by = 0 then goto 516 478 if by = 0 and be = 1 and  $b_3 = 0$  and  $b_5 = 1$  then goto 520 480 if by = 0 and be = 1 and b3 = 1 and b5 = 0 then goto 524 482 y b = 0 and bz = 1 and by = 1 and by = 1 things to 528 484 if b. = 1 and be = 0 and by = 0 and by = 0 then goto 532 48/ y b1 = 1 and b2 = 0 and b; = 0 and bs = 1 thengot = 536 and  $b_3 = 1$  and  $b_5 = 0$  then goto 54.0 488 y b = 1 and bz = 0 and b3 = 1 and b5 = 1 then goto 545 490 y b, = 1 and b2 = 0 and by = 0 and by = 0 then goto 548 492 if b = 1 and bz = 1 and by = 0 and bs = 1 then goto 552 494 igb1 = 1 and b2 = 1 and by = 1 and bs = 0 then goto 556 496 if by = 1 and be = 1 and bs = 1 and bs = 1 then goto 560 498 if b1=1 and b2=1 500 let R . = c

502 Gato 570

504 let R1=C

506 Goto 570

508 Let Re=c

510 GoTo 570

512 let R3 = C

514 GOTO 590

516 Let Rz = C

518 GOTO 570

520 Let Rs=C

522 GOTO 570

524 Let R6 = C

526 GOTO 570

528 Let R7 = C

530 Goto 570

532 Let R8 = C

534 GOTO 540

536 Let Rg = C

538 GOTO 570

540 Let R10=C

542 GOTO 570

544 Let R1=C

546 GOTO 570

548 Let R12=C

550 GOTO 570

552 Let Raz=c

554 GOTO 570

556 Let R4=C

558 GOTO 570

560 Let R15=C

570 if Ro<>1 then goto 574

572 Let Uo = Vo+1

574 if R1<>1 then goto 548

576 Let U1 = U1+1

578 y Rz <>1 than goto 582

580 Let U2 = U2+1

582 y R3 < >1 then goto 586

584 Let U3 = U3+1

586 if Ric>1 then goto 590

588 Let U3 = U2+1

590 y Rs <>1 then goto 594

592 Let Us = Us +1

594 if R6<>1 thm goto 598

596 Let Us = Vs+1

538 if R7<71 then goto 602

600 Let U7 = V4+1

602 if R8 <>1 than goto 606

604 Let U8 = U8+1

606 if Rg < >1 then goto 610

608 Let Ug = Ug+1

610 y R10 < >1 then goto 614

612 Let U20 = U40 +1

614 if Rm < >1 thougato 618

616 Let U1 = U1 +1

618 if R12 <>1 then goto 622

620 Let U12 = V12 +1

622 if R13 <>1 than goto 626

624 Let U13 = U13+1

626 if R14 < > 1 then goto 630

628 Let U14 = U14+1

630 if R15 <> 1 than goto 634

632 let V 15 = U15+1

634 Print L;" ", Ao; Ao; Ao; Ao; Ao; "" "; Ro; Ro; Ro; Ro; Ro; Ro; Ro; Ro;

R7; R8; R9; R10; R11; R12; R13; R14; R15; " "; V0; " "; V1; " "; V2; " ";

U3; ""; U4; ""; U5; ""; U6; ""; U7; ""; U8; ""; U5; ""; U40; ""; V41; ""; U42; ""; U43; ""; U44; ""; U45

636 if S=9 then Poure 100

638 Let L = L+1

640 if Inkeys = "0" then Goods 690

642 if Inkeys = "1" then Gorah 700

644 if Inkeys = "2" then Gomb 410

646 ig Inkeys = "3" then Gorah 720

648 if Inkeys ="4" then Gowl 430

650 if Inkeys = "5" then Gomb 740

652 if Inkeys = "6" then Goul 450

654 if Inkeys = "7" then Coul 460

651 if Inkeys = "8" then Gosul 770

658 if Inkeys = "9" then Couch 480