الجمهورية الجزائرية الديمقراطية الشعبية REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التعـــليم والبحـــث العـــلمــي MINISTERE DE L'ENSEIGNEMENT ET DE LA RECHERCHE SCIENTIFIQUE

200

# ECOLE NATIONALE POLYTECHNIQUE

DEPARTEMENT: ELECTRONIQUE

# PROJET DE FIN D'ETUDES

SUJET

Etude et réalisation d'un dispositif de protection microprogrammé pour un réacteur nucléaire expérimental

Proposé par :

A. BOUZIDA

F. HAFID

Etudié par :

EL GOURI Abdelatif

YFOUDIL-BEY Kamal

Dirigé par

A. BOUZIDA

F. HAFID

PROMOTION: JUIN 1984

# الجمهدورية الجنزائرية الديمقداطية الشعبية REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التعصليم والبحصة العصلمسي MINISTERE DE L'ENSEIGNEMENT ET DE LA RECHERCHE SCIENTIFIQUE

# ECOLE NATIONALE POLYTECHNIQUE

DEPARTEMENT:

ELECTRONIQUE

# PROJET DE FIN D'ETUDES

SUJET

ETUDE ET REALISATION

D'UN DISPOSITIF DE PROTECTION

MICROPROGRAMME POUR UN

REACTEUR NUCLEAIRE EXPERIMENTAL

Proposé par:

A.BOUZIDA F.HAFID Etudié par :

EL-GOURI Abdelatif FOUDIL-BEY Kamal Dirigé par

A. BOUZIDA

PROMOTION:

JUIN 84

### REMERCIEMENTS

Ce travail a été réalisé au Commissariat aux Energies Nouvelles d'Alger (C.E.N).

Nous tenons a exprimer toute notre gratitude à Melles A.BOUZIDA et F.HAFID qui n'ont ménagé ni leurs efforts, ni leur temps, et qui ont permis que ce travail soit réalisé dans de très bonnes conditions.

Nous adressons nos plus vifs remerciements Monsieur A.SAIDJ et nous esperons qu'il trouvera ici l'expression de notre très respectueuse reconnaissance pour son aimable collaboration lors de la mise au point de la maquette.

Nous remercions Monsieur M.SFLLAL pour l'attention qu'il nous a portée durant ce travail.

Nous avons bénéficié des conseils de Mr.M.REZIG à qui nous exprimons toute notre gratitude.

Que toutes les personnes du C.D.C.E et en particuliers Mr BETTAYEB et Mr TATAH pour nous avoir accueillis au CEN sachent combien nous avons apprécie leur aide désintéressée et amicale.

Que toutes les personnes du services reprographie soient remerciées pour le soin et l'attention qu'elles ont apportés à la réalisation du document.

# SOMMAIRE

### I. GENERALITES .

- 1. Description succincte d'un réacteur nucléaire

- 2. Les accidents probables pendant le fonctionnement des piles atomiques.

- 3. Philosophie de la sécurité de fonctionnement des piles atomiques.

- 4. Système de protection.

### II. LE SYSTEME DE PROTECTION :

- A Choix d'un système de protection

- B Application au réacteur de recherche SILOE.

### III. CARACTERISTIQUES DES PRINCIPAUX CIRCUITS UTILSES.

- A Bescription du microprocesseur MC 6800

- B Memoire Reprom MCM 2716.

- C Circuit d'horloge programmable MCM 6840

- D Description du P.I.A. MC 6820

### IV. REALISATION:

- 4.1 Adressage des circuits ou décodage

- 4.2 Commande des buffers de données

- 4.3 Lignes de controles utilisées

- 4.4 Utilisation des circuits

### V. PROGRAMMATION DU SYSTEME :

- 5.1 Boucle d'autorisation de montée des barres

- 5.2 Boucle de chute d'urgence

- 5.3 Programme auto-testant

- 5.4 Remarques concernant les différents sous-programmes.

### INTRODUCTION

Afin de prévoir une énergie de remplacement à l'énergie d'origine fossile et pour des raisons économiques (voire politiques et stratégiques), les grands pavs industrialisés ont été amenés à développer la production d'énergie électrique à partir des produits fissiles.

Cette forme d'énergie est plus communément appelée énergie nucléaire.

Les premières piles atomiques ont été construites pour produire du plutonium à des fins militaires. Ces installations ont été complétées par des ensembles destinés à récupérer la chaleur extraite des piles pour leur refroidissement et à utiliser cette énergie calorifique pour produire de l'électricité.

Le travail qui nous a été confié consiste en la réalisation d'un dispositif pour la protection d'un réacteur nucléaire expérimental basé sur l'utilisation d'un système de développement "EXORCISER" réalisé autour du microprocesseur MC 6800. Le document qui va suivre traite dans ses deux premiers chapitres, des différents aspects sur la sécurité et la protection des réacteurs nucléaires, la description du réacteur SILOE, du C.E.N.G de Grenoble et son système de protection. Quant au troisième chapitre, il donne un bref aperçu sur les principaux circuits utilisés suivi d'une description détaillée de la partie Hardware du travail contenu dans le chapitre quatre.

Dans le chapitre cinq sont développés les différents organigrammes et programmes permettant de contrôler le fonctionnement du réacteur.

La consultation des rapports de sûreté du C.E.A. (62 - 63) nous a permis de dégager les principaux critères sur lesquelles repose la conception du dispositif.

### CHAPITRE I - GENERALITES

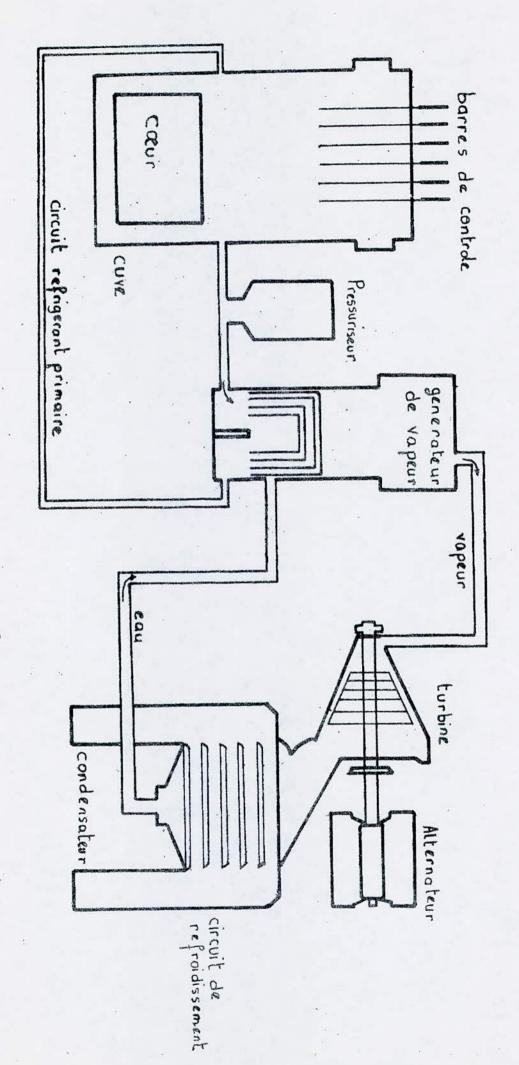

### I - DESCRIPTION SUCCINCTE D'UN REACTEUR NUCLEAIRE

Un réacteur nucléaire comporte trois parties ; le coeur, comparable à une chaudière où est produite l'énergie ; un dispositif de réclage et de sécurité : une enveloppe étanche pouvant supporter des pressions importantes.

Trois éléments importants caractérisent le coeur :

- Le combustible qui, en subissant le phénomène de fission sous l'action de neutrons incidents, est la source du dégagement de l'énergie sous forme de chaleur.

- Le modérateur, destiné à ralentir par choc les neutrons pour les rendre plus aptes à produire la fission, en général c'est un contra solide ou liquide constitué d'atomes de noyaux très légers sur lesquels les neutrons viennent rebondir, à chaque choc ils perdent une partie de leur énergie cinétique et ainsi ils atteignent le seuil d'énergie requis pour être capturés par le noyau du combustible.

- Le fluide caloporteur, chargé d'évacuer hors du réacteur la chaleur libéréepar la fission.

Le dispositif de réglage et de sécurité qui contrôle la réactivité est essentiellement composé de barres fabriquées à l'aide de matériaux ayant des sections efficaces de captures très importantes pour les neutrons. Les barres sont de deux sortes, les barres de contrôle dont l'enfoncement plus ou moins important dans le coeur permet de contrôler la réaction en chaîne; les barres de sécurité qui stoppent la réaction nucléaire en cas d'incident majeur. Ces dernières peuvent pénétrer à l'intérieur du coeur en un temps très court sous l'action de la force de gravitation. Leur nombre est suffisamment important pour palier à tout risque de non fonctionnement. (voir Fig I.1).

II LES ACCIDENTS PROBABLES PENDANT LE FONCTIONNEMENT DES PILES ATOMIOUES

Les accidents nucléaires sont multiples : nous pouvons citer entre autres :

- Accidents dus à des ensembles critiques.

fig 1.1

- Accidents dus à des fausses manoeuvres.

- Accidents dus à des pannes d'appareillages électriques, électroniques ou mécaniques.

- Accidents dus à la conception initiale de la pile ou de son contrôle.

- Accidents d'origine nucléaire.

- Accidents qui entraînent la surchauffe du modérateur ou du combustible.

- Accidents entraînés par le feu.

### II.1 - Accident de démarrage :

C'est souvent pendant cette période de marche de la pile que les accidents les plus graves sont susceptibles de se produire. L'accident est souvent fonction à la fois des caractéristiques nucléaires et thermodynamiques de la pile; et du taux d'insertion de réactivité; aussi le démarrage d'une pile demeure certainement une des opérations les plus délicates dans sa conduite. Il est fondamental de pouvoir suivre à tout instant dans cette opération l'évolution de la puissance neutronique et de veiller à ce que cette évolution soit limitée par le taux des neutrons retardés. La phase de démarrage étant l'une des deux phases traitées dans cette étude, nous reviendrons plus loin, plus en détail sur cette partie.

### II.2 - Accident de réfrigération :

Il est lié en dénéral aux pannes intervenant sur le système d'évacuation des calories (rupture du circuit primaire). En effet, il est impossible d'annuler complétement la puissance neutronique d'une pile une fois qu'elle a fonctionné. Ceci est dû (par exemple, pour une pile à l'uranium naturel sans source, modérée au graphite) aux fissions spontanées qui engendrent une puissance de quelques milliwatts. En plus de cette puissance neutronique résiduelle que l'on ne peut jamais annuler, il existe une énergie calorifique non négligeable qui est fournie par la désintégration des produits de fission accumulés dans les barreaux combustibles. L'arrêt du système de réfrigération est donc désastreux puisque l'élévation de température peut entraîner la fusion du coeur. Pour palier à ce type d'accident on prévoit souvent plusieurs circuits d'évacuation de la puissance résiduelle.

### III PHILOSOPHIE DE LA SECURITE DE FONCTIONNEMENT DES PILES ATOMIQUES

La philosophie de la sécurité de fonctionnement des piles atomiques s'oriente vers les critères suivants :

- 1. Arrêter le moins souvent la pile :

- d'abord pour amortir le cout de sa construction et de son installation,

- diminuer le nombre des opérations de démarrage fois

- 2. Arrêter la pile chaque qu'il y a un doute sur la sécurité de fonctionnement (vitesse de l'arrêt = fonction de l'accident à éviter).

- 3. Eviter les interventions manuelles, ceci implique l'automatisation de toutes les manoeuvres et la mise en place de dispositifs complexes et couteux.

### IV SYSTEME DE PROTECTION

Plusieurs systèmes concourent à contrôler les installations nucléaires ; nous distinguons principalement : - le système de contrôle - le système de protection.

Le système de contrôle tend à maintenir le réacteur dans un domaine de fonctionnement sûr défini avec certaines marges de sécurité.

Le système de protection est l'ensemble des équipements électriques et mécaniques nécessaires pour maintenir le réacteur dans un état sûr en cas de transitoires anormaux où d'accidents. En effet, dans ces cas là, il est nécessaire d'arrêter le réacteur (arrêt d'urgence) pour éviter de sortir des limites du domaine de fonctionnement. L'arrêt d'urgence est provoqué par coupure de l'alimentation des mécanismes de groupes de barres qui chutent par gravité dans le coeur.

Sur les installations actuelles, les fonctions de protections sont assurées par des automatismes cablés; toutefois, pour avoir une fiabilité et une sûreté de fonctionnement accrues, une plus grande souplesse d'utilisation (modularité; adaptabilité) et une amélioration des critères de déclenchement par un traitement de l'information la tendance est à l'utilisation des systèmes numériques et programmés. Les calculateurs sont déjà présents dans les systèmes de contrôle, cependant on note une certaine réticence des autorités de sûreté nucléaire vis-à-vis de leur introduction dans les systèmes de protection.

Divers projets sont en étude ou en cours de réalisation ; nous pouvons citer entre autres :

- Le système (TRTC), chargé de la surveillance des températures du coeur dans les réacteurs de type PHENIX et SUPER PHENIX. Il est composé de 2 systèmes séparés à base de minicalculateurs industriels.

- Le système de protection intégré numérique ; il possède une structure multiprocesseur à redondance quatre.

### CHAPITRE II - LE SYSTEME DE PROTECTION

### A - CHOIX D'UN SYSTEME DE PROTECTION

Un système de protection, depuis l'acquisition des paramètres jusqu'aux éléments élaborants les ordres de sécurité, comporte de nombreux éléments.

## 1.1 - Principales composantes d'un système de protection :

Il comprend essentiel ment les équipements suivants :

- Les équipements de détection des paramètres à surveiller.

- Les équipements destinés à élaborer les ordres de démarrage (ou d'arrêt) des actionneurs du système de protection. Ces équipements réalisent un certain nombre de fonctions appelées "fonctions de protection" tels que :

- . Fonctions d'arrêt d'urgence.

- . Fonctions de sauvegarde qui peuvent être

- injection de sécurité,

- isolement et aspersion d'enceinte,

- démarrage d'alimentation de secours.

### A. II - Système numérique de protection

Pour être admis à faire fonctionnellement partie du système de protection d'un réacteur, un calculateur doit satisfaire à toutes les exiquences constitutives qui s'appliquent au système de protection. Ceci entraîne l'utilisation de plusieurs calculateurs redondants dont l'ensemble constitue le système numérique chargé de provoquer à l'issu d'un vote une ou plusieurs actions de sécurité.

### A. III - Redondance

Il existe plusieurs types de redondance dans un système de protection. La redondance des capteurs fait qu'à chaque grandeur physique sont associées plusieurs mesures. Le logiciel de traitement effectue un vote entre les états de mesure ; et le programme peut déterminer le ou les calculateurs défaillants.

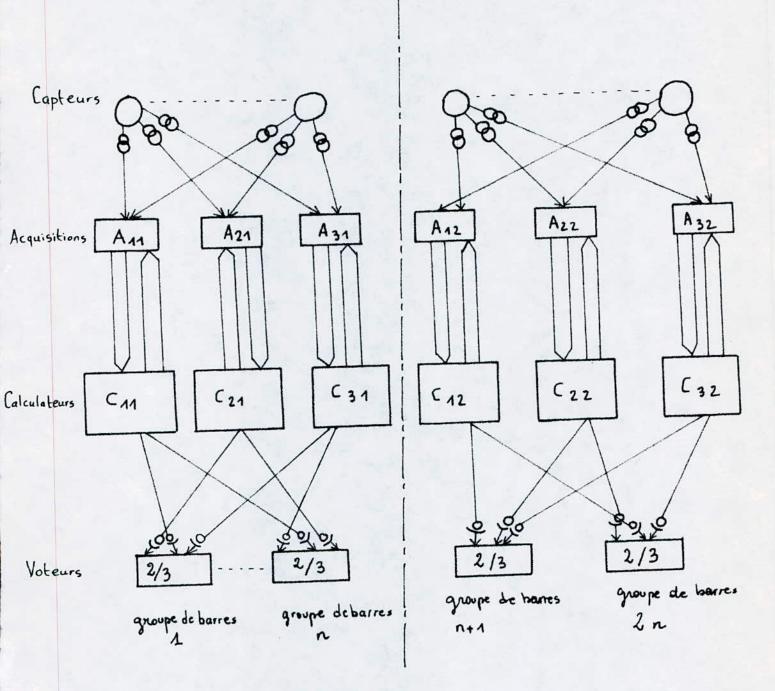

La redondance des voies de traitement fait qu'une grandeur peut être prise en compte plusieurs fois, ce qui améliore encore la probabilité de détection d'un incident. Enfin, il y a redondance sur les voteurs ; à chacun est associé un actionneur agissant sur un groupe de barres. La figure 2.1 représente un système de redondance 2/3 dont chaque voie de mesure est gérée par 3 calculateurs.

### A.IV - Système de détection de défaillances

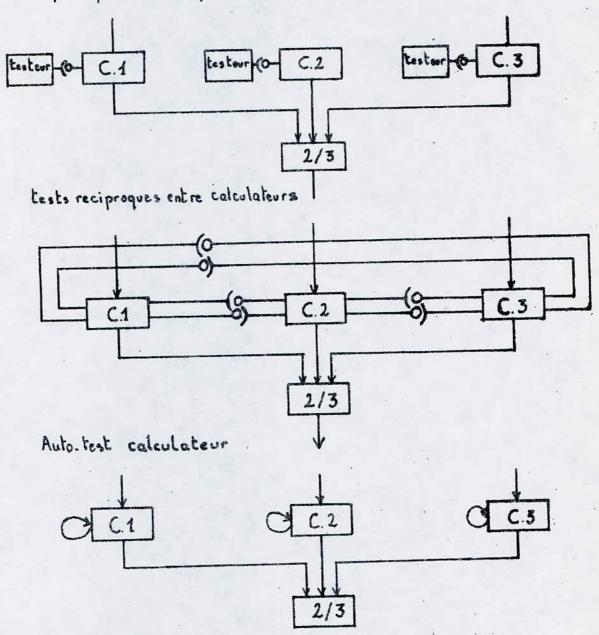

pour détecter une anomalie dans un des calculateurs, il faut vérifier le bon fonctionnement pour un grand nombre de combinaisons de données entrant normalement dans ce dispositif. C'est une tâche assez complexe pour laquelle il existe plusieurs solutions. La figure 2.2 représente quelques possibilités de tests pour un essemble de calculateurs.

- a) Dispositif de test pour chaque calculateur.

- b) Tests réciproques entre calculateurs.

- c) Auto-test calculateurs.

### A.V - Choix d'une structure (Auto-test)

Le test de bon fonctionnement du système sera fait par autotest des 3 calculateurs qui travailleront en autonomie sans aucune synchronisation. Il en résulte une grande netteté du système en cas de défaillance : ce qui facilite leurs détections et leurs réparations. L'organe de décision sera réduit à un minimum de matériel ce qui est favorable à la fiabilité du système.

Jusqu'à présent, une centralisation d'acquisition de données était normale pour les centrales nucléaires qui sont déjà partiellement protégées par calculateurs. Cepéndant il v a une forte tendance à la décentralisation de l'acquisition des données afin de réduire le volume des câbles nécessaires pour envoyer le grand nombre de données du coeur du réacteur jusqu'au centre de traitement.

fig: 2.1

Dispositif de test pour chaque calculateur

fig: 2.2

### B - APPLICATION AU REACTEUR DE RECHERCHE SILOE

Les paragraphes précédents nous ont permis de voir un système microprogrammé à redondance triple ; chaque calculateur étant autotestant. Comme application nous nous baserons sur un réacteur expérimental de type piscine, le réacteur SILOE du C.E.N.G. (Grenoble).

Dans ce chapitre nous définirons le système des barres de commandes, les chaînes de mesures nucléaires et le système de sécurité.

### B.I - Système de barres de commande

Les critères à prendre en compte pour définir l'efficacité des barres de commande sont de deux types :

Sur le plan de la sécurité, il est nécessaire d'avoir en toutes circonstances, et notamment en début de cycle deux barres de sécurité en position haute : on assure ainsi l'arrêt du réacteur, même en cas de coincement d'une des barres.

Sur le plan de la compensation et du pilotage, il faut compenser les effets de température, d'empoisonnement Xenon et Samarium et conserver une antiréactivité suffisante pour que le cycle en pile ait la durée souhaitée (sur le plan expérimental et économique); et que la marge de pilotage assure un fonctionnement normal jusqu'en fin de cycle.

Compte tenu de l'expérience acquise sur SILOE, cinq éléments de commande suffisent pour contrôler un coeur de 30 à 35 éléments.

### B.II - Chaînes de mesures nucléaires

La puissance nominale (P.N) du réacteur est de 10 MW, avec possibilité de fonctionner à des puissances supérieures. La gamme de mesure s'étend donc de 0,3 M à 2,5 P.N. Cette gamme est divisée en trois sous gammes :

Les mesures dans chaque sous gamme sont assurées par :

- Une chaîne de fission ou chaîne de démarrage de 3.10 à 3.10 P.N

- Deux chaînes logarithmiques ou chaîne en puissance de 3.10 à 2,5 P.M

- Trois chaînes linémires dont une de pilotage et deux de sécurité de 3.10 à 2,5 P.N

### B.II.1 - Chaînes de démarrage :

- a) Détecteur : chambre à fission (CFU1 ; CFU2), enfermée dans une perche étanche en AG3.

- b) Chaîne de mesure : Préamplificateur, amplificateur, discriminateur, mise en forme, intégrateur logarithmique et périodémètre.

- c) Gamme de mesure :

Taux de comptage 1 à 10 C/S

Temps de doublement -30 S à + 3 S

- d) Seuils :

Seuils puissance : 1 seuil mini I1 = 2 C/S

1 seuil maxi I2 = 50 000 C/S

Seuils période : 2 seuils positifs I1 = 5 sec

I2 = 3 sec

### B.II.2 - Chaînes logarithmiques

- a) Détecteur : chambre C.C.C enfermée dans une perche étanche en AG3.

- b) Chaînes de mesure : Préamplificateur, amplificateur, périodemètre.

- c) Games de mesure :

Amplificateur : 10 à 10 A

Périodémètre :-30 S à + 3 S

- d) Seuils

Seuils puissance : 2 seuils. 1 seuil mini I1 = 10 A

1 seuil maxi I2 = 6.10

Seuils période : 2 seuils positifs T1 = 5 sec T2 = 3 sec

### B.II.3 - Chaînes de sécurité :

- a) Détecteur : chambre C.C.C enfermée dans une perche étanche en AG3

- b) Chaîne de mesure : Amplificateur

- c) Gamme de mesure : 5.10 à 5.10 A

- d) Seuils :

Un seuil chute normale à 1,5 P.N

Un seuil chute urgente à 2 P.N

Un seuil minimum à 5.10 P.N

### B.II.4 - Chaînes linéaires de pilotage

- a) Détecteur : chambre C.C.C 2 enfermée dans une perche étanche en AG5.

- b) Chaîne de mesure : Amplificateur, calculateur d'écart entre la puissance lue par l'électronique 'P' et la puissance 'Po'.

- c) Gammes de fonctionnement

Gamme A: 0 - 250 KW

B: 0 - 1 MW

C: 0 - 2,5 MW

D: 0 - 5 MM

E: 0 - 25 MW

Commutateur de gamme à cinq positions correspondantes aux gammes A,B,C,D,E placé au pupitre.

Si le commutateur de gamme n'est pas sur la gamme A ou B, il n'est pas possible de démarrer le réacteur. Ceci est destiné à éviter que l'opérateur ne démarre le réacteur sur l'une des autres gammes.

### B.III - Système de sécurité

Les systèmes de sécurité sont de deux types :

- Les alertes qui ne comportent qu'une signalisation optique et acoustique.

- Les alarmes qui comportent une action de sécurité doublée d'une signalisation optique et acoustique.

Dans notre étude nous nous intéressons particulièrement aux boucles de démarrage et de chute d'urgence.

### B.III.1 - Les alarmes :

Les alarmes sont destinées à prévenir l'opérateur d'une situation anormale en trainant une action automatique urgente. L'attention de l'opérateur doit être attirée sur la manoeuvre automatique en cours, pour lui permet-

tre soit de l'interrompre (cas de réduction de puissance), soit au contraire de l'exécuter correctement en cas de mauvaise exécution automatique.

### B.III.2 - Poucle Autorisation de démarrage :

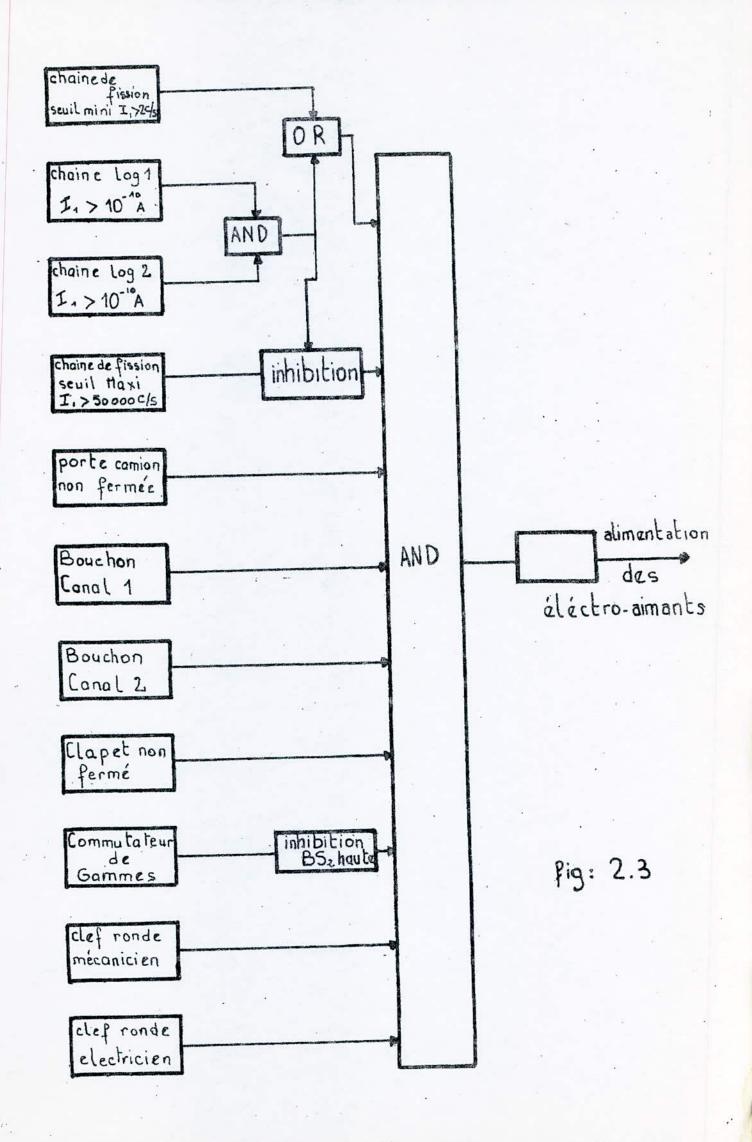

Il s'agit d'une boucle à émission de courant, interdiseant l'alimentation des électroaimants des barres au démarrage de la pile, et le passage du pilotage manuel au pilotage automatique, si certaines conditions ne sont pas remplies. (voir Fig 2.3).

Les conditions à remolir sont les suivantes :

- Indication suffisante sur la chaîne à fission (seuil mini de puissance)

- Indication au dessous du seuil maximum sur la chaîne à fission (seuil maxi puissance). Cette interdiction est inhibée automatiquement dès qu'il y a une indication de puissance suffisante sur la chaîne logarithmique 1 et de la chaîne logarithmique 2 (seuils mini puissance).

- Commutateur de gamme sur gamme A ou B. Cette interdiction est inhibée automatiquement dès que BS2 est en butée haute.

- Clapet de convexion naturel fermé.

- Bouchon canal 1 en place

- Bouchon canal 2 en place

- Porte à cemion fermée

- Clé de ronde mécanicien en place

- Clé de ronde électricien en place

- Fermeture du circuit d'alimentation des électroaimants par la clé d'autorisation de démarrage.

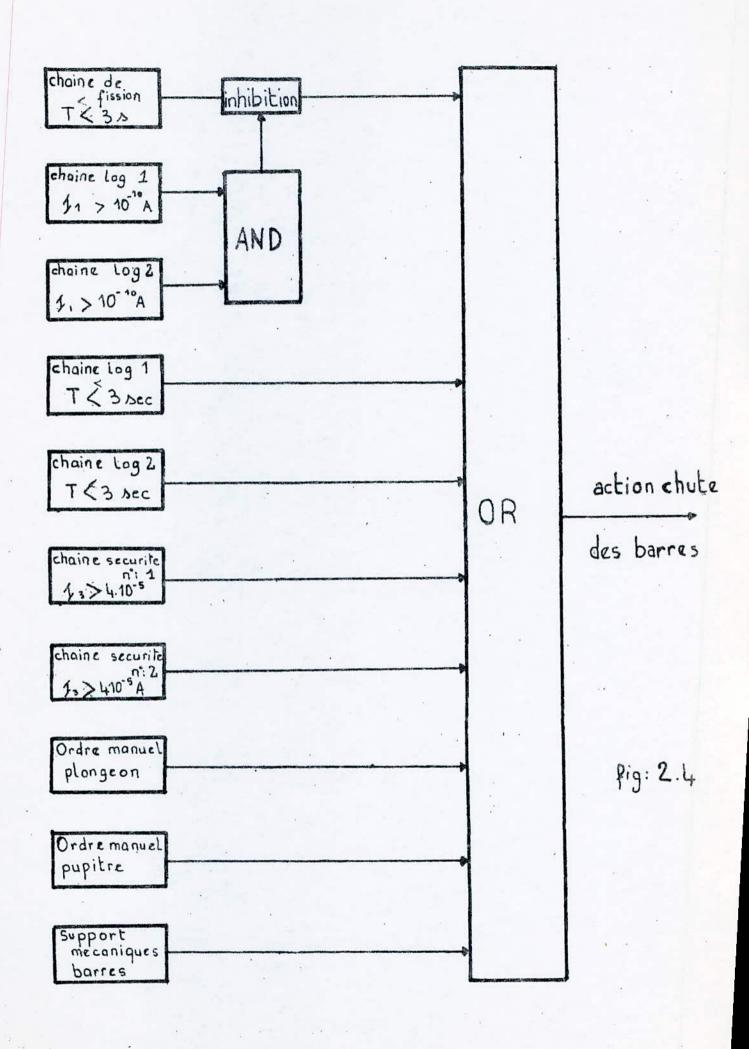

### B.III.3 - Boucle chute d'urgence

C'est une houcle à manque de courant provoquant :

- La chute de toutes les barres par coupure de l'alimentation des électroaimants. (voir Fig 2.4).

- Le passage de pilotage automatique au pilotage manuel.

- La descente des électroaimants des barres.

Les ordres entraînant la chute urgente proviennent :

- de la chaîne à fission de démarrage : période inférieure à T2 (2ème seuil période). Cette sécurité est inhibée automatiquement lorsque les deux chaînes logarithmiques donnent une indication de puissance (seuil minimum puissance).

- Des chaînes logarithmiques 1 et 2 : période inférieure à T2 (2ème seuil période).

- Des chaînes de sécurité : dépassement de puissance supérieure à une valeur donnée (2ème seuil maxi).

### CHAPITRE III - CARACTERISTIOUES DES PRINCIPAUX CIRCUITS UTILISES

### A - DESCRIPTION DU MICROPROCESSEUR MC 6800

### A.1 - Généralités

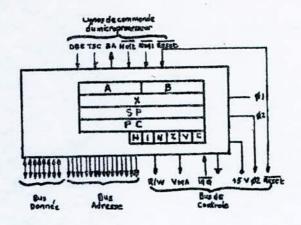

C'est un microprocesseur 8 bits possédant 72 instructions, un bus de données bidirectionnel de 8 bits et un bus d'adresse de 16 bits, ce qui lui donne un espace d'adressage de 64 K.octets.

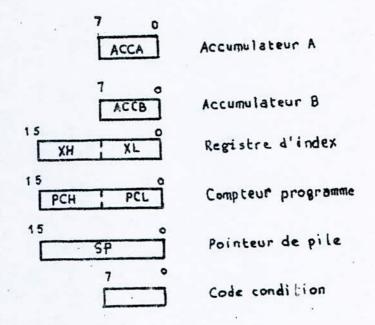

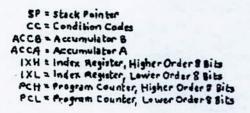

Le MC 6800 comprend les registres suivants :

- . 2 accumulateurs A et B de 8 bits

- . 1 registre d'index de 16 bits

- . 1 compteur programme de 16 bits

- . 1 pointeur de pile de 16 bits

- . 1 registre d'état ou code condition de 3 bits dont cinq d'entre eux indiquent les résultats d'une opération sur l'UAL :

- . N : négatif

- . Z : zéro

- . C : retenue

- . H : demie retenu

- . I : masque d'interruption

- . V : dépassement en complément à deux.

Les 2 bits de poids fort restants sont toujours à 1.

### A.2 - Modes d'adressage :

Le MC 6800 possède 7 modes d'adressage.

- Adressage immédiat :

Dans ce mode d'adressage l'opérande dispose de un à deux octets (suivant le type d'instruction) placés après le code opération. Seuls les instructions concernant le registre d'index et la pile utilisent des opérandes immédiats à 2 octets.

- Adressage direct :

L'instruction a une longueur de 2 octets. Ce mode d'adressage ne permet l'adressage que d'une seule page (adresse OO à FF).

- Adressage étendu :

L'instruction a une longueur de 3 octets. Les 2 derniers contiennent l'adresse absolum (16 bits) de l'opérande. - Adressage indexé :

L'instruction a une longueur de 2 octets. pour obtenir l'adresse de l'opérande, l'unité centrale ajoute au contenu de l'index, la valeur du deuxième octet de l'instruction. Ceci permet d'accéder une zone mémoire de 256 octets à partir de l'adresse définie par le registre d'index.

- Adressage implicite :

L'instruction a une longueur de 1 octet. Il y a 25 instructions de ce type portant sur 1 ou 2 registres.

- Adressage relatif :

L'instruction a une longueur de 2 octets. Le second octet sert de déplacement relatif par rapport à la valeur courante du compteur programme + 2. Ce déplacement est codé en complément à 2.

AE = PC + 2 + offset

AE = adresse effective

PC = compteur programme.

Avec ce mode d'adressage on peut accéder à un octet placé dans l'espace PC - 126 ; PC + 129.

- Adressage d'accumulateurs :

Dans ce mode on spécifie l'un des 2 accumulateurs A ou B, les instructions ont une longueur de 1 octet.

Types d'instructions :

Le MC 6800 comprend 72 instructions qui peuvent être classées en

- . instructions de transfert de données

- . instructions de modification de données

- . instructions arithmétiques

- . instructions logiques

- . instructions de branchements

- . instructions de test et de manipulation du registre d'état

- . instructions sur le registre d'index et le pointeur de pile

- . instructions liées aux interruptions.

### A.3 - Description externe du MC 6800

### Signaux de contrôle :

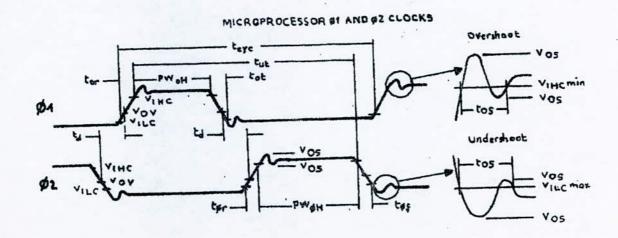

- $-\phi_4$  et  $\phi_2$ : ce sont 2 entrées donnant les 2 phases d'horloge dont la machine a besoin. Ces signaux doivent satisfaire à certaines conditions de niveau et de non recouvrement ; voir figure 3.2.

- HALT : cette entrée commande le fonctionnement de l'unité centrale. Si elle est au niveau haut, la machine travaille, si elle passe au niveau bas, celle-ci s'arrête à la fin de l'exécution de l'instruction en cours. Elle met en 3ième état ses sorties bus de données, bus adresses, VMA passe au niveau bas et BA au niveau haut.

- TSC (Three state control) : cette entrée contrôle l'état du bus d'adresse et de la ligne R/W. Elle demande à la machine de les mettre en mode troisième état, cet état apparaît 500 ns après que TSC = 2,25 volts. Les lignes VMA et BA sont au niveau bas.

- $R/\tilde{W}$ : cette sortie compatible TTL indique au milieu extérieur, mémoires et périphériques, le type d'accès que fait l'unité centrale. Il y a accès en lecture si  $R/\tilde{W}$  est à l'état haut et accès en écriture si  $R/\tilde{W}$  est à l'état bas.

Si une requête TSC ou HALT est faite, la ligne  $\mathbb{R}/\bar{\mathbb{W}}$  est mise en troisième état.

- VMA (valid memory address) : cette sortie est utilisée pour mentionner aux organes extérieurs qu'une adresse est validée sur le bus d'adresse. En général on utilise cette sortie pour sélectionner les décodeuss d'adresses.

- DBE (Data bus enable) : cette entrée contrôle l'état du bus de données de la machine. C'est une entrée compatible TTL et qui met le bus en troisième état, si elle est au niveau bas. Dans un mode normal d'utilisation du 6800 cette entrée est pilotée par la phase  $\emptyset_2$  de l'horloge.

- BA (bus available) : en fonctionnement normal cette sortie est au niveau bas. Si le MC 6800 met cette ligne au niveau haut, ceci implique que la machine est arrêtée et que le bus d'adresses est en troisième état donc disponible pour un autre partenaire. Cette situation apparaît après que la ligne HALT ait été mise à 0 ou que la machine ait exécuté l'instruction "Wait". Dans ce cas toutes les sorties qui peuvent être mises en troisième état le sont ; les autres sont mises à un niveau inactif.

fig:

fig:

Pig3.2

La machine reste dans cet état tant que l'entrée HALT n'est pas remise à l'état haut ou si une interruption NMI ou IRO n'est pas détectée.

- Bus d'adresse : A - A - A

16 sorties sont utilisées par le MC 6800 pour indiquer l'adresse de l'octer mémoire référencé. Ces sorties sont munies d'amplificateurs trois états. Ainsi la machine peut mettre ses 16 sorties en troisième état. En général le bus d'adresses est utilisé en association avec la ligne VMA qui est une ligne de contrôle pour ce bus. Si VMA est portée au niveau haut une adresse est véhiculée par le bus et est validée, sinon, elle n'est pas significative.

- Bus de données : D : D,

Ces 8 lignes bidirectionnelles sont utilisées par l'unité centrale pour échanger des informations (octets). Elles ont la possibilité d'être mises en troisième état. Le bus de données est utilisé avec la ligne R/W qui indique au milieur extérieur le sens dans lequel l'échange a lieu.

Si R/W est à l'état haut : le MC 6800 accède l'octet en lecture ; l'échange a lieu dans le sens : milieu extérieur —— unité centrale.

Si R/W est à l'état bas : le 'MC 6800 accède l'octet en écriture ; l'échange a lieu dans le sens : unité centrale — milieur extérieur.

### A.4 - Sélection des éléments extérieurs :

Le MC 6800 possède un espace d'adressage de 64 K. Les mémoires ainsi que les appareils périphériques sont connectés sur le même bus. La sélection d'une mémoire ou d'un périphérique se fait par décodage des adresses. En général la manière la plus simple de sélectionner un élément est d'utiliser les bits de poids fort des adresses combinés à des dispositifs logiques.

### A.5 - Mécanismes d'interruptions :

Le MC 6800 possède : 2mécanismes d'interruptions Hardware

1 mécanisme d'interruption Software

1 mécanime d'initialisation.

Dans tous les cas l'unité centrale effectue un branchement indirect à une adresse dépendant du type de l'interruption mise en jeu et du nombre de lignes d'adresses utilisées. Les octets mémoires d'adresses FFF8 à FFFF contiennent les adresses de ces différentes routines. La table suivante donne l'affectation de ces octets :

| Vec          | mécanisme |         |

|--------------|-----------|---------|

| MSB          | LSB       |         |

| FFFE         | न्यस्य    | RESTART |

| Р <b>РРС</b> | FFFD      | NMI     |

| FFFA         | FFFB      | SWI     |

| FFF8         | FFF9      | IRO     |

Détaillons à présent les deux mécanismes d'interruption hardware ; cependant, il faut noter le rôle joué par l'entrée RESET. Elle est

à front montant sensitive, c'est à dire qu'elle est active après que le

MC 6800 ait constaté le passage de celle-ci de l'état bas à l'état haut.

Le MC 6800 accède alors aux deux octets d'adresses FFFF et FFFE et stocke

leur contenu dans le compteur programme. Il positionne le bit I des interruptions IRQ. Le programme d'initialisation prévu par l'utilisateur est

alors activé. Cette entrée doit être maintenue au niveau haut pour lue la

machine fonctionne.

### IRO (interrupt Request)

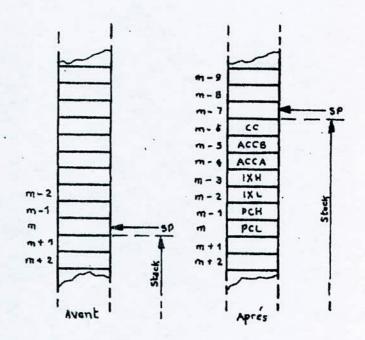

Cette entrée est active quand elle est au niveau bas. Elle signifie alors qu'il y a une demande d'interruption venant de l'extérieur. Si le bit I de masquage des interruptions est à zéro, l'interruption peut avoir lieu; sinon le MC 6800 continue le programme en cours tant que le bit I est à un. Si l'interruption est possible, le MC 6800 termine l'instruction en cours, puis il y a une sauvegarde de l'état processeur dans la pile comme il est indiqué sur la figure 3.3.

Le bit de masque des interruptions est positionné à un et le MC 6800 accède aux octets d'adresses FFF8 et FFF9 pour prendre l'adresse de la routine des interruptions de type IRO.

### NMI (non masquable interrupt)

Cette entrée est à front descendant, c'est à dire sensible au passage du niveau haut au niveau bas. Les mécanismes que pour l'IRO sont mêmes mis en jeu avec les différences suivantes :

- l'interruption a toujours lieu, le bit I n'est pas significatif.

- Le MC 6800 accède aux adresses FFFC et FFFD pour connaître l'adresse d'implantation de la routine.

# fig: 3.3 Sauvegarde lors d'une interruption

Il est à noter l'existence d'un mécanisme d'interruption programmable, celui-ci est activé par l'instruction SWI. Le microprocesseur procède alors à une sauvegarde de l'état des différents registres et accède aux octets d'adresses FFFA et FFFB pour connaître l'adresse de l'implantation de la routine du type SWI.

### B - MEMOIRE REPROM MCM 2716.

Le MCM 2716 est une mémoire morte reprogrammable. Pour des applications pour lesquelles un automatisme est exigé, ce type de mémoire permet de stocker les programmes. A la mise en marche du système, les programmes implantés peuvent être immédiatement exécutés.

Elle possède une capacité de 16 384 bits organisés en 2 048 mots de 8 bits. Le brochage est donné en annexe.

### C. CIRCUIT D'HORLOGE PROGRAMMABLE : MC 6840

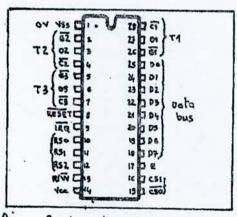

Le MC 6840 est un PTM (Programmable Timer Module) constitué de 3 compteurs binaires indépendants, commandés et contrôlés par l'unité centrale grâce à leurs registres de commande, d'état et de données. (Fig 3.4).

### C.1 - Description interne

Chacun des 3 timers se compose d'un compteur 16 bits et d'un registre de chargement "Latch" où est stockée la valeur d'initialisation du compteur. L'arrivée d'un ordre d'initialisation provoque le positionnement du compteur à la valeur préchargée dans le registre.

Lorsque le compteur est validé, celui-ci se met ensuite à décompter jusqu'à zéro. La fin du décomptage est indiquée par le positionnement d'un bit (drapeau) dans le registre d'état.

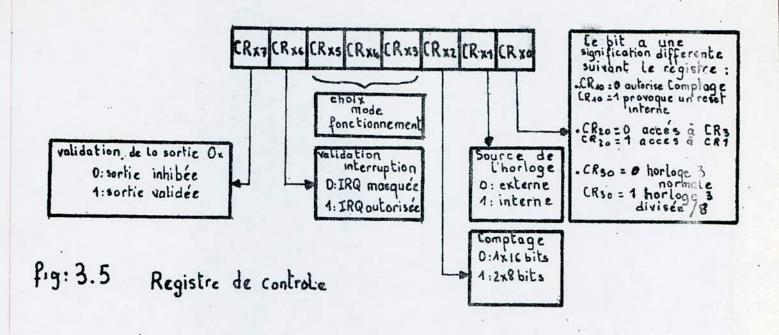

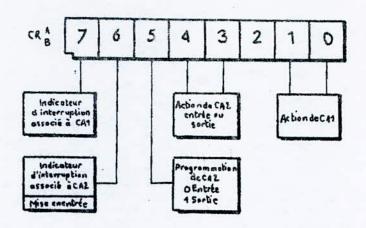

### C.1.1 - Registre de contrôle : CR.X (X = 1,2 ou 3)

Ils sont au nombre de 3. Ces registres sont accessibles par le microprocesseur en écriture seulement et leurs contenus imposent le mode de fonctionnement (Fig 3.5). Il est à noter que les bits CRX3, CRX4 et CRX5 permettent le choix du mode de fonctionnement des différents Timers (Fig 3.6) Nous reviendrons plus loin sur les différents modes de fonctionnement.

N.B : La notation CRX2 s'interprète de la façon suivante : Le bit 2 du registre de contrôle X(X = 1, 2 ou 3).

### C.1.2 - Registre d'état :

C'est un registre de 8 bits qui collecte des informations sur les 3 compteurs. Ce registre est accessible uniquement en lecture par l'unité centrale (Fig 3.7).

I, I, I, sont les drapeaux de "time out" (fin de décomptage du registre i = 1,2 ou 3). Ils sont positionnés à 1 lors de l'arrivée à 0 du compteur. Le bit de poids fort correspond aux demandes d'interruptions du type IRQ.

si INT = 1 IRO est à l'état bas (donc active).

La formule booleenne de INT est : INT = I3.CR<sub>3.6</sub> + I2CR<sub>4.6</sub> + I1CR<sub>4.6</sub>

Les drapeaux I<sub>4</sub>,I<sub>2</sub>,I<sub>3</sub> sont remis à zéro, soit par un reset (externe ou interne), soit par une initialisation du compteur ou encore par sa lecture quand elle suit immédiatement la lecture du registre d'état.

# Structure et brochage du 6840 Tampen List Secrit Compt 2 George Compt 3 Tampen List Tampen T

fig: 34 Synaptique du 6840 : un module . Timer . programmable contenant 3 compteurs commandés par l'unite centrale

R/W RSL RSI RSO

fig : Brochagedu 6840

| F1.7 | ^ | A | - |   | 17  | -  | -  |

|------|---|---|---|---|-----|----|----|

| TUI  | 0 | 0 | 0 | 0 | 1 1 | 12 | 14 |

fig :3.7 Registre d'etat

| , |

|---|

| 6 |

|   |

| CRX5 CRX4 CRX |   |    | Mode           |      |

|---------------|---|----|----------------|------|

| 0             | 0 | 0  | Multivibrateur | (a)  |

| 0             | 0 | 4  | fréquencemetre | (>)  |

| 0             | 1 | 0  | Multivibrateur | (p)  |

| 0             | 1 | A  | Intervalemetre | (4)  |

| 1             | 0 | 0  | Monostable     | (a)  |

| 1             | 0 | 1  | frequencemetre | (2)  |

| 1             | 1 | 0, | Monostable     | (6)  |

| 1             | 1 | 1  | Intervalemetre | ( >) |

- Legende: (a) reinitialisation du compteur sur Reset ou G

- (b) reinitialisation du compteur sur Reset, 6 ou ecriture registre

- (>) interruption si période compteur > periode G

- (4) interruption si periode compteur < periode &

Les échanges de données d'effectuent par l'intermédiaire de six registres de 16 bits. L'unité centrale accède en écriture au registre de chargement (counter Latch) et peut aussi lire la sortie du compteur. Le bus de données ne possédant que 8 bits, donc une opération de lecture ou d'écriture s'effectue en 2 temps.

### C.1.3 - Accès aux registres internes :

Les registres à adresser sont au nombre de 10, parmi eux on trouve 4 registres de 8 bits et 6 registres de 16 bits; étant donné que nous travaillons sur des mots de 8 bits, ceci revient à considérer que nous sommes en présence de 16 registres de 8 bits. Leur adressage se fait par l'intermédiaire des 3 entrées de sélections RSO, RS1, RS2, du signal R/W, ainsi que par le bit CR2.0 (Fig 3.8).

D'après le tableau de la figure 3.8 nous constatons que l'accès à CR1 et CR3 se fait par la même adresse, et selon la valeur de CR (O ou 1) on accède à l'un ou l'autre (respectivement CR3 ou CR1). On voit donc qu'une écriture dans CR1 ou CR3 est toujours précédée par une écriture dans CR2. L'utilisation de R/W en complément d'adressage interdit l'usage d'instructions qui opérent directement en mémoire pour modifier les valeurs contenues dans les registres (DEC, COM, ROL, etc...), en effet à une adresse donnée l'utilisateur n'accède pas au même registre selon qu'il opére en lecture ou en écriture.

### C.2 - Présentation externe

Le MC 6840 se présente sous la forme d'un circuit intégré de 28 pins fabriqué selon la technologie C.MOS. Explicitons le rôle de chaque broche.

### C.2.1 - Signaux vers l'unité centrale

- Do + D; : 8 lignes de données bidirectionnelles à 3 états.

- R/ $\bar{W}$  : Signal de lecture écriture (1 = lecture ; 0 = écriture)

- E : Signal d'activation (en général lié à l'horloge).

- IRO : Signal de demande d'interruption.

- CS1 ; CSO: Servent à la sélection du boitier.

- RSO, RS1, RS2 : servent à la sélection des registres internes.

- RESET : Un niveau bas sur cette entrée initiatise le circuit.

| R/₩ | RS <sub>2</sub> | RS 1 | RS. | Operations                             |

|-----|-----------------|------|-----|----------------------------------------|

| 0   | 0               | 0    | 0   | ecriture de si bit o de cRz = 1        |

| 0   | 0               | 0    | 4   | ecriture de CR2                        |

| 0   | 0               | 1    | 0   | ecriture des poids faibles Timer 1     |

| O   | 1               | 0    | 0   | acriture despoids faibles Timer 2      |

| 0   | 1               | 1    | 0   | ecriture des poids paibles Timer 3     |

| 1   | 0               | 0    | 0   | Lecture du registre d'état             |

| 1   | 0               | 0    | 1   | pas doperation                         |

| 1   | 0               | 1    | 0   | lecture des poids faibles   Compteur 1 |

| 1   | 1               | 0    | 0   | Lecture des poids paibles Compteur 2   |

| 1   | . 1             | 1    | 0   | lecture des poids faibles l'empteur?   |

fig:3.8 : adressage des registres internes du Timer

### C.2.2 - Signaux vers la périphérie

Chaque Timer X est en liaison avec la périphérie grâce à 3 broches :

- G : signal de déclenchement (gate) du compteur X

- O : signal de sortie (out-put) du compteur K

- C : horloge du compteur X.

### C.2.3 - Alimentation

$$-v_{cc} = +5 v$$

La consommation moyenne est de 350 mW.

### C.3 - Modes de fonctionnement

Plusieurs modes de fonctionnement sont possibles permettant, sous le contrôle du logiciel de réaliser facilement des appareils tels que fréquencemètre, chronomètre, générateur d'impulsions, monostable, etc...

Toutes les durées, périodes ou intervalles de temps engendrés par ce circuit sont définis par le comptage d'un nombre entier de périodes d'horloge; ce nombre varie de 0 à 65535. En outre le timer offre la possibilité de travailler sur 16 bits ou 2 fois 8 bits, d'autoriser ou non des demandes d'interruptions en fin de cycle de chaque compteur, de valider ou mon les sorties 0.X.

Les différents modes de fonctionnement sont résumés par le tableau de la figure 3.6. On peut distinguer 3 modes principaux :

- Le mode continu : c'est le multivibrateur ou oscillateur.

- Le mode impulsionnel : c'est le monostable ou temporisateur.

- Le mode mesure de temps qui se divise en deux sous-modes :

- . mesure de périodes ou fréquencemètre

- . mesure de durée ou chronomètre.

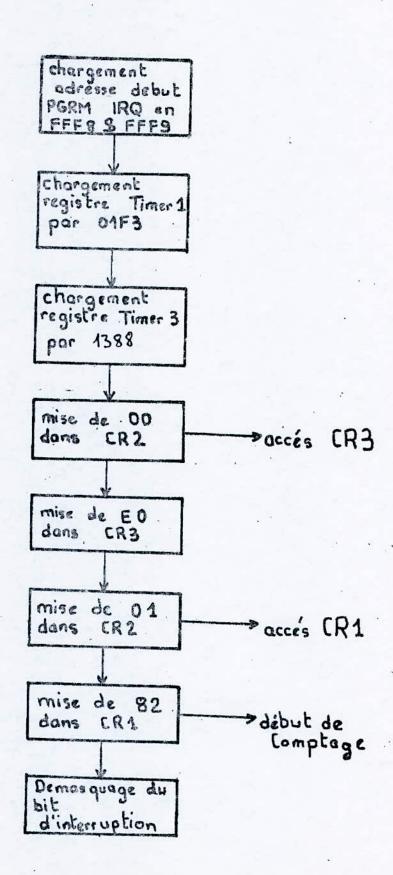

### C.4 - EXEMPLE D'UTILISATION DU TIMER

Mous allons présenter un mode de fonctionnement du Timer nous permettant de générer une demande d'interruption IRO toutes les 5 secondes. Il existe plusieurs manières de procèder, entre autre nous avons opté pour la solution suivante : Timer 1 en multivibrateur

Timer 3 en monostable.

La sortie du Timer 1 sera reliée à l'entrée d'horloge du Timer 3 ce qui constituera la nouvelle entrée d'activation du compteur 3. Le monostable sera programmé pour se déclencher toutes les cinq secondes. Le fonctionnement correct revient essentiellement à la programmation appropriée des registres de contrôle CR1 et CR3.

Le Timer 1 est programmé pour fonctionner en multivibrateur de nériode 1 milliseconde. Le registre de contrôle CR1 est chargé par la valeur 82 ; en nous référant à la figure 3.5 nous décodons aisément cette information :

- Sortie 0.1 validée

- IRO ma squée

- Mode multivibrateur

- Comptage 1 x 16 bits

- Horloge interne (1MHZ)

- Début de comptage autorisé.

Le mode 1 fois 16 bits a été choisi pour disposer d'un signal rectangulaire de période 2(N+1)T avec :

- N = contenu du registre de chargement

- T = 1 microseconde (période de l'horloge interne).

Un petit calcul donne N=499 d'où l'équivalent en notation hexadécimal est N=0.173.

Le chargement du registre de contrôle CP3 par la valeur "E O" s'inimpose au Timer 3 un fonctionnement en mode monostable. La valeur "E O" s'interprète de la manière suivante :

- Sortie O 3 validée

- IRO autorisée

- 'lode monostable

- Comptage 1 fois 16 bits

- Horloge externe (sortie 01 du Timer 1).

Il est à moter que contrairement au Timer 1, la sortie IRC a été validée et ceci afin de permettre le déroulement d'un programme d'interruption toutes les cinq secondes. L'initialisation du registre de chargement se fait par la valeur 1388 (hexadécimale) ce qui confère au dispositif une période de 5 secondes. L'organigramme détaillé de l'initialisation du Timer est donnée en figure 3.9.

figi3.9

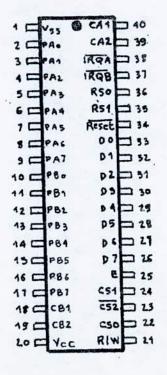

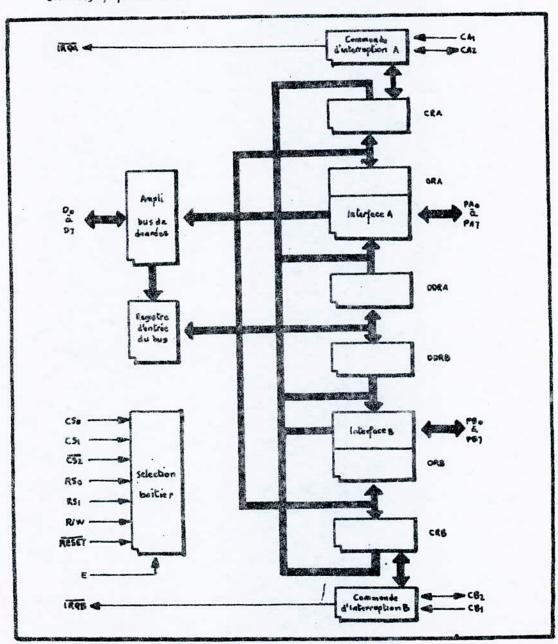

### D - DESCRIPTION DU P.I.A (péripheral Interface Adapter)

C'est une unité d'échange ou adaptateur d'interface, elle permet, sous le contrôle du programme (ou plus exactement du microprocesseur) le transfert des données entre l'unité centrale de traitement et une (ou deux) unité (s) périphérique (s).

Les échanges de données avec chaque unité périphérique se font en parallèle par l'intermédiaire de ports.

Le PIA utilisé pour notre réalisation est le MC 6820 de Motorola.

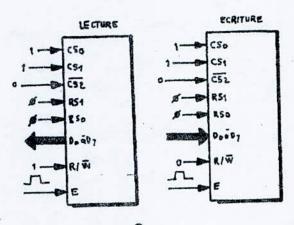

### D.1 - Signaux échangés (Fig. 3.10)

- D.1.1/ Avec le système

- CSO, CS1, CS2 : lorsque CSO, CS1, CS2 = 110, le PIA est sélectionné.

- RS1, RSO: le PIA étant sélectionné, les 4 combinaisons de ces deux bits permettent d'adresser les registres internes. En conséquence, le PIA occupe 4 adresses mémoires.

- E : signal d'activation des échanges, généralement cette entrée est reliée à Ø2 (signal du bus de contrôle).

- R/ $\tilde{W}$ : signal de lecture-écriture (Fig 3.11) : 1 = lecture O = écriture.

- DO à D7: bus bidirectionnel de données. Il aboutit, dans le PIA, à un amplificateur qui peut être activé ou mis à l'état haute impédance par le signal R/M, si le PIA est sélectionné. Par ces 8 fils arrivent les données à transmettre en sortie (vers les périphèriques) ou à lire.

- RESET : mis à zéro, ce signal met tous les registres internes du PIA à zéro.

- IROA, IROB : deux lignes de demande d'interruption destinées à interrompre l'exécution d'un programme Ppar le M.P.U. Ces lignes sont généralement reliées aux entrées IRO et NMI du M.P.U. ou sont placées sur les entrées du contrôleur prioritaire d'interruption (P.I.C 6828).

fig: 3.13

Fig: 3.11

fig: 3.10

D.1.2/Avec la périphérie :

- PAO à PA7 et PBO à PB7 : 16 liunes de données prouvammables individuellement en entrées ou sorties. Ces 2 ports d'entrées sortie reflètent, en sortie le contenu de 2 registres internes de 8 bits dont l'état binaire apparaît sous forme de tensions de sortie (+ 5v : 1 logique et Ov : 0 logique) sions de sortie (+ 5v : 1 logique et Ov : 0 logique) qistres en màintenues tant qu'il n'y a pas de modification dans les requistres.

- CA1, CB1 : deux lignes d'entrées d'interruption.

- CA2, CB2 : deux lignes programmables en entrées d'interruption ou en sorties de commande. Dans ce dernier cas, ils reflètent directement l'état d'un bit d'un registre interne (de contrôle).

- V vs, V cc : deux bornes d'alimentation : V cc = + 5V V vs = V vs = V

550 mW. est d'environ 110 mA et la puissance dissipée  $550~\mathrm{mW}$

D.2 - Organisation interne

Le schéma de la figure 3.1.2 représente le synoptique du MC 6820 Mous remarquons que le MPU peut adresser 6 reqistres en écriture et en lecture. Ces registres sont répartis en deux groupes de 3 registres relatifs à chacun des bornières:

- CRA, CRB : (Fig 3.1.3) contiennent les paramètres de fonctionnement.

- DDRA, DDRB : contiennent le mot fixant le sens de transfert (entrée ou sortie) pour chacune des lignes de donnée. Un état l'définit une broche de sortie et un état O une broche d'entrée.

- OPA, ORB: mémorisent les données en sortie lors d'une écriture.

A la même adresse on peut lire les données présentées en entrées, mais elles devront être mémorisées à l'extérieur.

D.3 - Sélection et adressage des registres du PIA se fait par 2 lignes d'adresses RSO, RSI et le signal R\W.

fig: 3.12 Schema synoptique du MC 6820

Chaque registre peut être lu ou écrit, compte tenu des 2 bits d'adressage, l'accès aux 6 registres ne peut être fait que par le biais d'un bit supplémentaire provenant du registre de contrôle (bit 2) Voir figure 3.14.

D.4 - Fonctionnement du PIA.

Divers modes de fonctionnement sont définis par la programmation des registres de contrôle. Voir figure 3.15.

Les lignes CA1 et CB1 sont contrôlées par les bits 0 et 1 du registre de contrôle.

- Le bit O masque ou permet les interruptions.

bit 0 = 0: masque les interruptions

bit 0 = 1 : interruption permise.

- Le bit 1 détermine le front actif pour le signal entrant :

bit 1 = 1 : le front montant est reconnu comme signal activant une requête d'interruption.

Toute requête d'interruption venant de CA1 ou CB1 met à l'état haut le bit 7 du registre de contrôle du côté A ou B respectivement.

Ces bits sont remis à O par un Reset du PIM, ou une lecture du registre de sortie du PIM.

Les bits 3, 4, 5 servent à la programmation des lignes CA2 et CB2.

Le bit 5 indique la direction entrée ou sortie de la ligne CA2 ou CB2 suivant le registre de contrôle utilisé.

bit 5 = 1 : CA2 (CB2) établie en sortie

bit 5 = 0 : CA2 (CB2) établie en entrée.

La programmation du mode de fonctionnement de la ligne d'interruption CA2 mise en entrée est identique à CA1 si le bit 5 de CRA est à O. Dans ce cas, les bits CRA3, CRA4 et CRA6 jouent le même rôle que les bits CRAO, CRA1 et CRA7.

La programmation de CA2 en sortie de commande s'obtient en écrivant un 1 dans CRA5, CRA4 et CRA3 permettant de définir les modes d'actions de CA2, selon la programmation de ces bits, on distingue les modes de fonctionnement suivant :

Fig : 314

| RS1 | RSO | CRA2 | CRB2 | Registre adressé |

|-----|-----|------|------|------------------|

| 0   | 1   | -    |      | CRN              |

| 0   | 0   | 0    | _    | DDRA             |

| 0   | 0   | 1    | -    | ORA.             |

| 1   | 1   | _    | -    | CRB              |

| 1   | 0   | 1    | 0 -  | DDRB             |

| 1   | 0   | -    | 1    | ORB              |

|     |     |      |      |                  |

Fig : 3.15

| 7       | 6       | 5 4 3       | 2   | 1   | 0       |

|---------|---------|-------------|-----|-----|---------|

| IRO x 1 | IRO x 2 | Cx2 Control | DDR | Cx1 | Control |

x désigne le côté à ou B.

Fig : 3.16

| CRA4 | CRA3 | Modes                      |

|------|------|----------------------------|

| 0    | 0    | Dialogue \ Associá à       |

| 0    | 1    | Impulsionnel   une lecture |

| 1    | 0)   |                            |

| 1    | 1 1  | Programmé                  |

Fig : 3.17

| CRB4 | CRB3 | Modes                     |

|------|------|---------------------------|

| 0    | 0    | Dialogue \ Associó à      |

| 0    | 1    | Impulsionnel une écriture |

| 1    | 0    |                           |

| 1    | 1    | Programmé                 |

Le mode programmé : la sortie CA2 suit la programmation du CRA3.

Les modes impulsionnel et dialogue : CA2 est associé à une lecture. Voir figure 3.16.

Pour le fonctionnement de CB2, il est identique à celui de CA2, sauf dans les modes impulsionnel et dialogue, CB2 est associé à une écriture. Voir figure 3.17.

pour notre réalisation, nous avons utilisé 2 PIL, le premier prévu pour la lecture des données et le deuxième pour la signalisation.

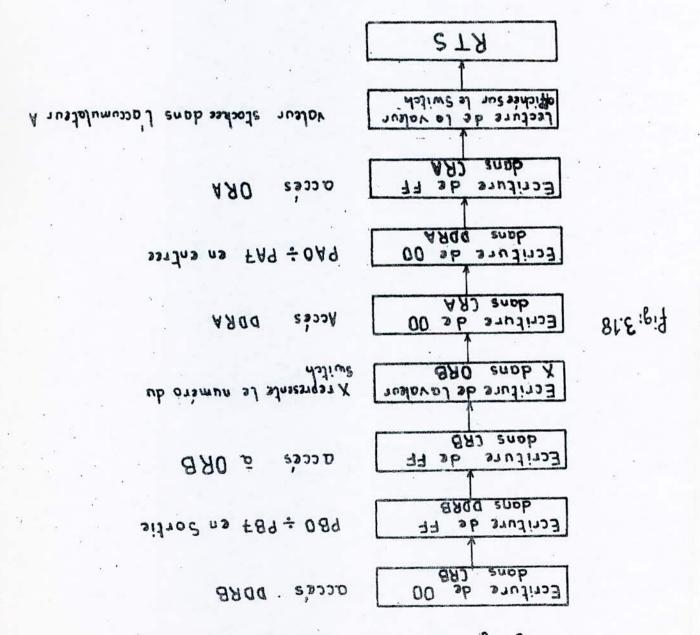

P.I.A. 1: Nous disposons de 10 microswitchs (8 interrupteurs intégrés) associés à 10 latchs et d'un décodeur 1 parmi 16. A l'aide de ce plA on peut sélectionner et lire une des 10 configurations figurant sur les latchs. Le port B est programmé en sortie pour permettre le choix du microswitch (les 4 lignes PBO à PB3 sont reliées aux 4 entrées du décodeur), tandis que le port A est programmé en entrée pour acquérir les données. Un organigramme détaillé pour la programmation de ce plA est données en tigure 3.18.

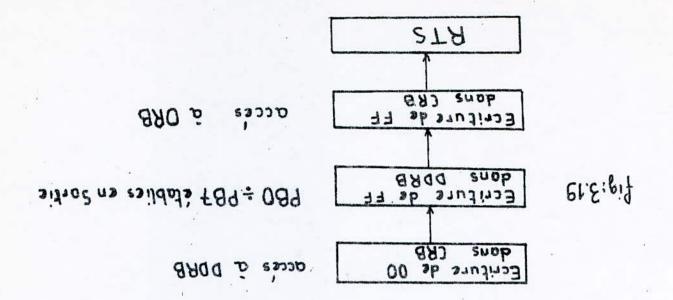

P.I.A. 2 : 3 leds servent A indiquer les différentes situations du réacteur, dans ce but le port B du PIA 2 est utilisé pour les commandes.

L'organigramme présenté en figure 3.19 n'est qu'une initialisous programme 10 puis de charger la configuration correspondante dans sous programme 10 puis de charger la configuration correspondante dans 1988; ces configurations sont les suivantes:

Ol (PBO) : led verte allumée, elle indique le bon fonctionnement du réacteur.

O2 (PBI) : led rouge allumée, elle indique la chute d'urgence

O4 (PB2) : led jaune allumée, elle indique l'autorisation de montée des barres, ainsi que l'attente de la clef de démarrage du réacteur.

### Organigramme Pour PIA1

Organigramme Pour PIAZ

Te controje q, nu rescrent uncjestre bar microprocessent néces-

: ejts

- I scdnisition des paramètres,

- leurs traitement.

(octets de 8 bits). té de pourvoir à une conversion de ces grandeurs en des valeurs numériques les que puissances, périodes, flux neutroniques, etc...,, d'on la nécessi-Tes beremetres a contrôler sont des drandeurs analogiques tel-

Cette fonction peut être réalisée par un convertisseur analogi-

que - numérique.

.I AIG

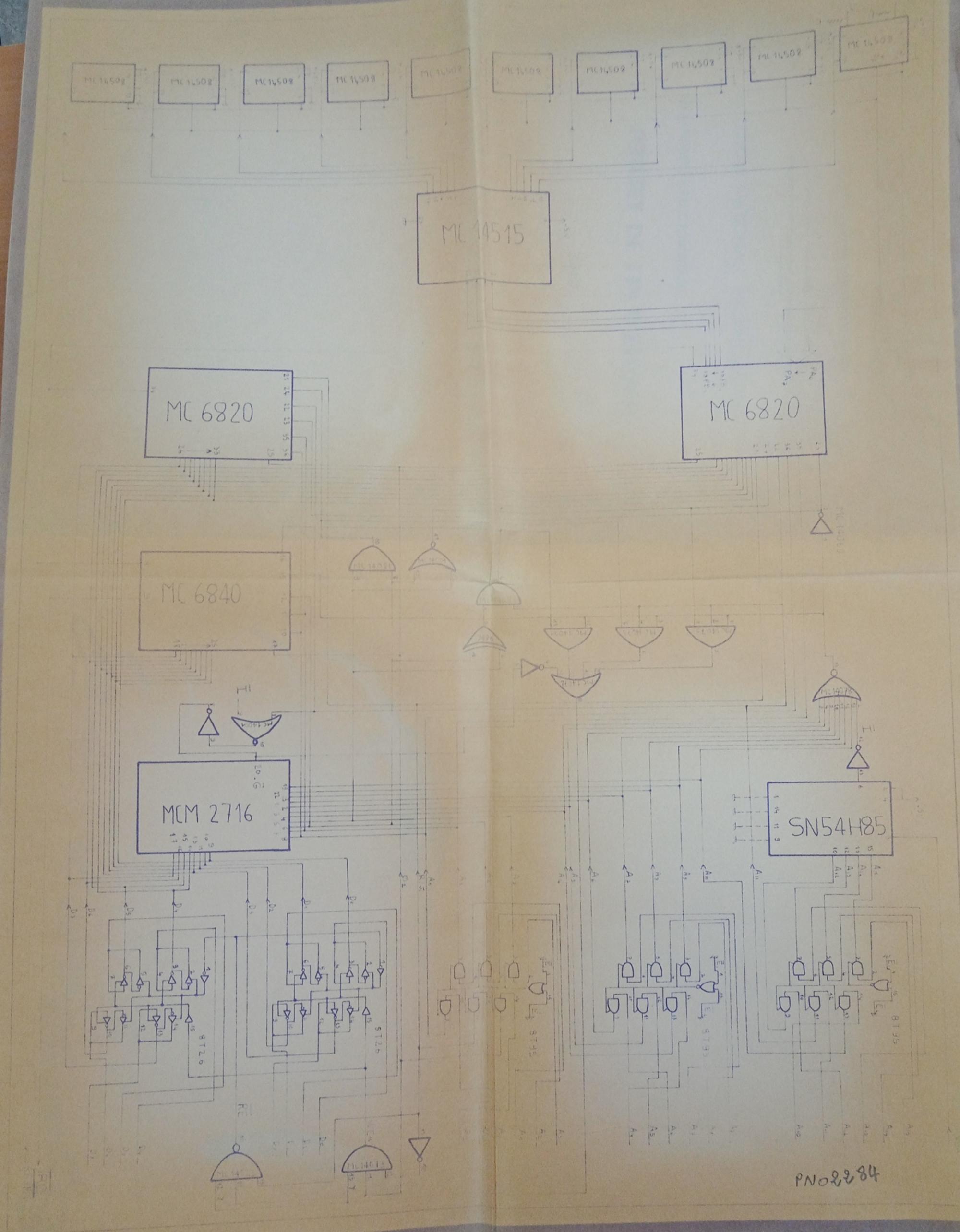

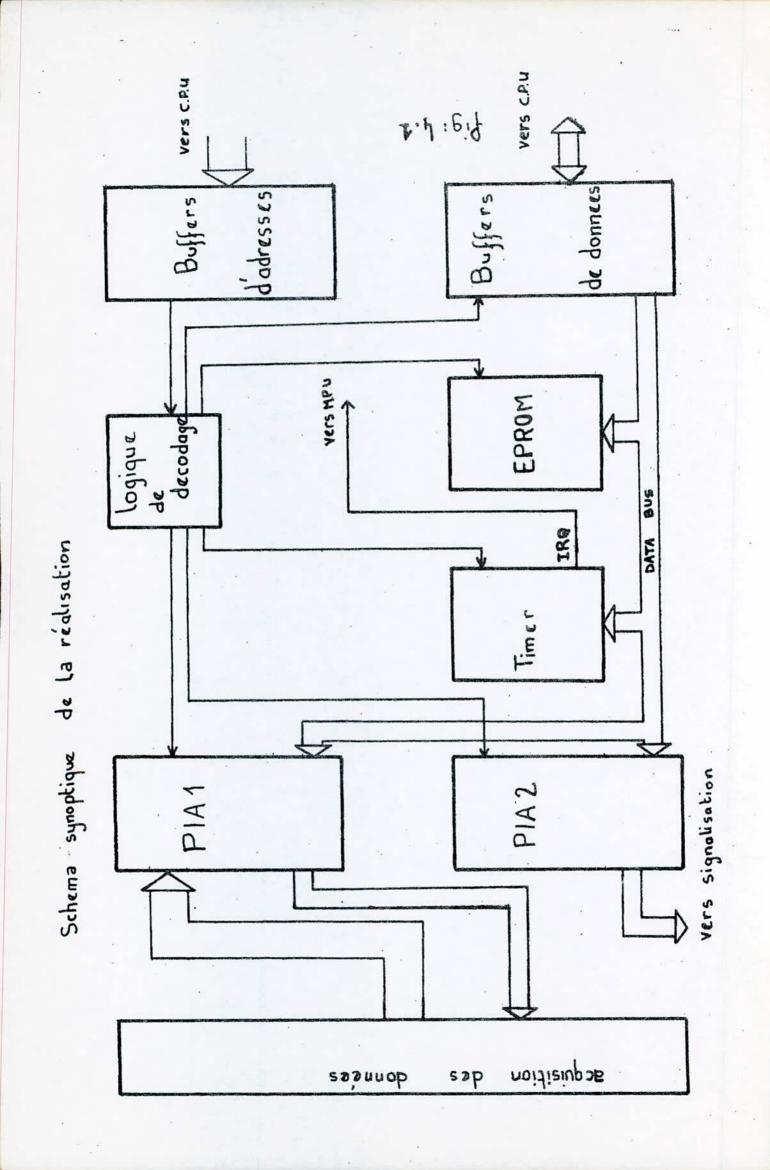

ma synoptique du système est donné par la figure 4.1. d'assurer à l'aide d'un logiciel approprié la gestion du système. Le schéde réaliser un dispositif lui permettant d'acquérir les informations et microprocesseur, il est nécessaire pour pouvoir converser avec ce dernier tion seront simulés par des états logiques. Le traitement se faisant par Vu la non disponibilité d'un cas réel, les paramètres en ques-

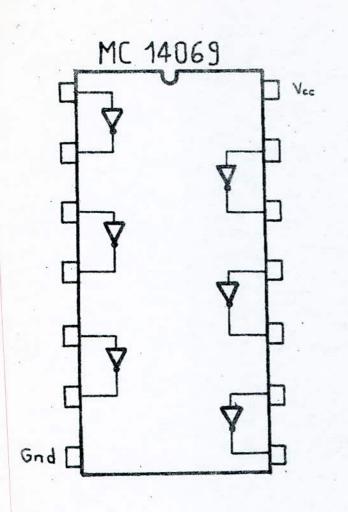

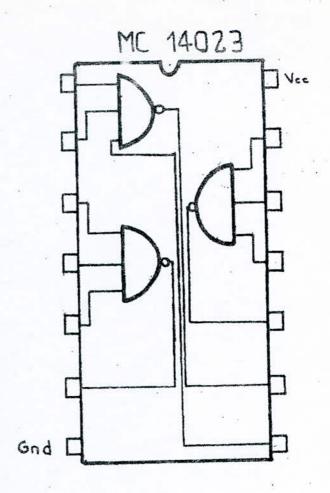

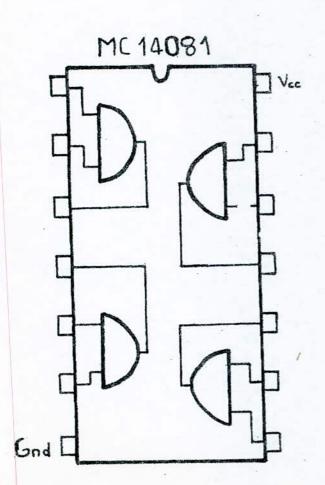

elle comprend essentiellement : strion des données ou plus exactement la simulation des paramètres nucléaires, Une première carte a été réalisée et comporte le système d'acqui-

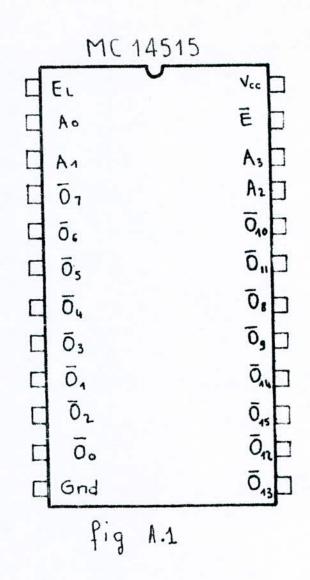

intégrés en boitier dual in line) qui lui est associé. variable en fonction de l'état du microswitch (8 interrupteurs circuits simulers un paramètre et la valeur de celui-ci sera - 10 circuits MC 14508 jouant le rôle de latchs ; chacun de ces

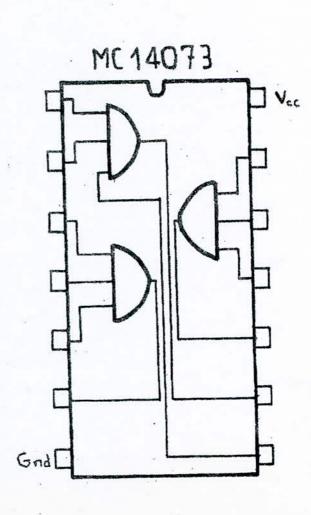

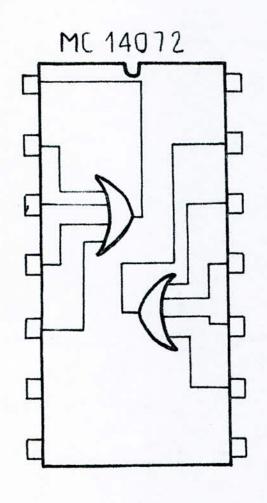

par programme, les entrées du décodeur sont liées à 4 lignes du Port B du seule de ses sorties (Voir Fig A.4) le choix d'un paramètre (latch) se faisant figuration de 4 bits à l'entrée du 14 515 celui-ci me met à l'état bas qu'une sent ties attaquent respectivement les 10 entrées.disables des latchs. Pour une conum décodeur 1 parmi 16 à sorties basses (MC 14 515) dont les 10 premières sorteur traitant les paramètres successivement, nous avons été conduits autiliser (3 et 15), MR (1 et 13) sont à O et strobe (2 et 14) à l'état 1. Le calcula-Le MC 14 508 valide ses 8 sorties lorsque les entrées disables

La deuxième carte comprend :

- 2 PIA

- 1 Timer

- 1 EPROM

- Des buffers d'adresses et de données

- Une logique de décodage.

En premier lieu nous trouvons les buffers d'adresses et de données. Les buffers d'adresses sont des 8T 95, ce sont des amplificateurs 6 bits, unidirectionnels.

L'existance de 16 lignes d'adresses sur le MC 6800, impose l'utilisation de 3 circuits 8T 95, ainsi nous disposons de 18 lignes amplificatrices, les 2 lignes restantes seront utilisées pour l'amplification des signaux R/ $\overline{w}$  et  $\emptyset$ 2 vu qu'ils attaquent plusieurs circuits.

### 4.1 - Adressage des circuits ou décodage

Il nous a fallu concevoir un décodage d'adresse nous permettant d'adresser deux PIA, un Timer et une EPROM.

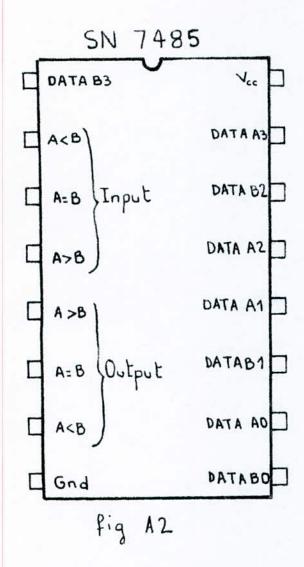

Sur le schéma général on peut remarquer l'existance du comparateur SN 74 H 85 (son brochage et sa table de vérité sont donnés en annexe), il est utilisé pour permettre une translation libre de l'espace mémoire contenant notre carte. Ce procédé offre l'avantage d'avoir 14 possibilités d'adressage c'est à dire qu'on peut fixer le poids fort de l'adresse entre O et D donc sur tout'll'espace utilisateur de l'exorciser.

Le comparateur fonctionne suivant le mode suivant :

Il réalise la comparaison entre les configurations présentes sur ses entrées 15, 13, 12, 10 et 1, 9, 11, 14. Suivant qu'il y a égalité ou non, les sorties prennent des états particuliers. L'utilisation par le comparateur des 4 lignes d'adresses de poids forts permet la translation de l'espace mémoire utilisé de 1000 en 1000.

EXEMPLE: A15, A14, A13, A12 sont liées aux entrées 10, 12, 13, 15 du comparateur. Si on fixe les entrées 1, 9, 11, 14 à 0, 0, 0, 0 on peut adresser donc une zone mémoire comprise entre 0000 et OFFF (la sortie out put A = B est à 1), au delà il n'y aura plus de validation des adresses.

Remarque: Si du point de vue hardware cette modification de zone mémoire ne pose aucun problème, par contre dans le software, il y aura quelques modifications conçernant l'adressage direct ou étendu (on change le poids fort de l'adresse).

Comptabilisons le nombre d'octets mémoire utilisés :

- 2 PIA occupant chacun 4 octets

- 1 Timer occupant 8 octets

- 1 EPROM MC 2716 de 2 K.O = 2048 octets.

Cela donne au total 2064 octets, ce qui correspond à 80F positions mémoires en hexadécimal.

La zone allouée à chaque circuit est donnée par le tableau suivant. Le premier caractère X est utilisé comme variable comprise entre O et D inclus.

| X7FF  | X803    | X80B  | X8OF  |   |

|-------|---------|-------|-------|---|

| EPROM | P.I.A.1 | TIMER | P.I.A | 2 |

Explicitons à présent la logique de décodage de chaque circuit.

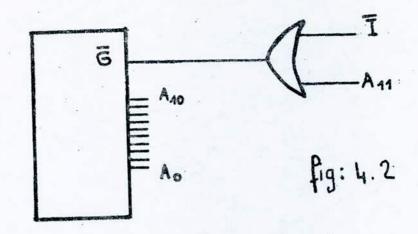

EPROM: elle occupe la zone XOOO à X7FF. On remarque que dans cet espace mémoire on a toujours A11 = 0, en l'associant à I (sortie 6, A = B, du comparateur, inversée) par une porte OR, on peut attaquer le chip select de l'éprom G actif à l'état bas. Ainsi, on a

$$G = I + A11$$

Les entrées d'adresses de l'eprom seront reliées à AO, A1,.... A1O du microprocesseur. Voir figure 4.2.

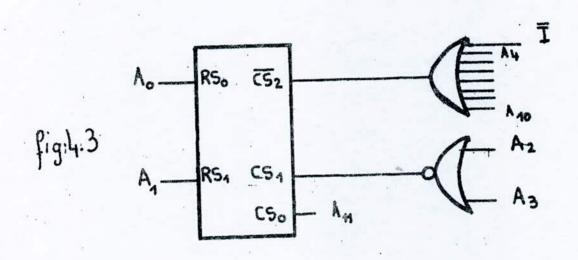

P.I.A.1 : zone mémoire X800 à X803.

Le PIA possède 3 chips selects CSO, CS1 et CS2. On remarque que pour les 2 PIA et le Timer A11 = 1 et A4 à A10 sont à O. Donc pour attaquer les CS des 2 PIA et du Timer, on a utilisé une porte OR à 8 entrées (Î et A4, A5, ..... A10).

Pour le PIA1 on a A2 = A3 = O pour CS1 et AO et A1 variables.

Ainsi: RSO = AO

RS1 = A1

CSO = A11

$CS1 = \overline{A2 + A3}$

$\overline{\text{CS2}} = \overline{\text{I}} + A4 + \dots$  A10. voir figure 4.3

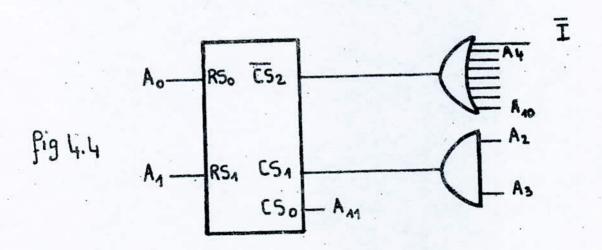

PIA2 : il occupe la zone mémoire X8OC à X8OF, la différence par rapport qu PIA1 réside dans A2 = A3 = 1, donc on aura pour CS1 :

CS1 = A2 . A3

Le reste est inchagé. Voir figure 4.4.

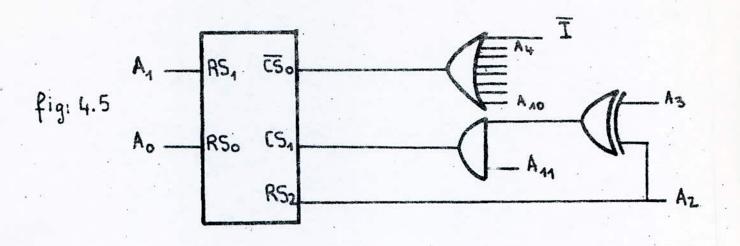

TIMER: Il occupe la zone XSO4 à XSOB, et possède 2 chips select CSO et CS1, ainsi que 3 entrées RSO, RS1 et RS2 pour le choix des registres internes. La différence par rapport aux 2 PIA est le fait qu'on a toujours A2 différent de A3, d'où l'utilisation d'une porte XOR pour la sélection du Timer. Voir figure 4.5.

On aura :

$\overline{\text{CSO}} = \overline{1} + A4 + A5 + \dots + A10$

$CS1 = (A2 \oplus A3) . A11$

RS2 = A2

RS1 = A1

RSO = AO

Remarque: L'utilisation d'un adressage translatable de 1000 en 1000 a été réalisé du fait que l'exorciser est utilisé par plusieurs cartes, occupant différents espaces mémoires. En ce qui nous concerne on aura le choix d'un espace mémoire compris entre 0000 et 0000, c'est à dire dans tout l'espace qu'offre l'exorciser à l'utilisateur.

### 4.2 - Commande des Buffers de données :

Ce sont des 8T26, buffers bidirectionnelles inverseurs à 4 bits l'association en parallèle de 2 circuits 8T26 est nécessaire, vu qu'on dispose d'un bus de données de 8 lignes.

Le 8T26 possède des entrées de validation :

(1) : RE : Read enable

(15): WE : write enable

Suivant ces entrées, on peut avoir soit une lecture, soit une écriture :

$\overline{RE} = WE = 1 = \text{écriture}$

RE = WE = 0 = lecture

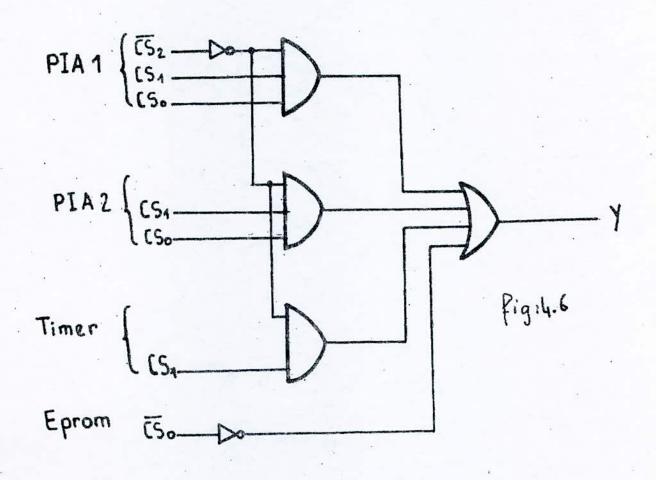

Pour assurer un décodage strict de notre carte, nous avons généré un signal Y permettant l'ouverture des buffers uniquement si un des circuits de la carte est adressé ; donc il y a un échange de données entre le

dispositif et l'extérieur si et seulement si nous adressons l'espace mémoire XOOO à X80F.

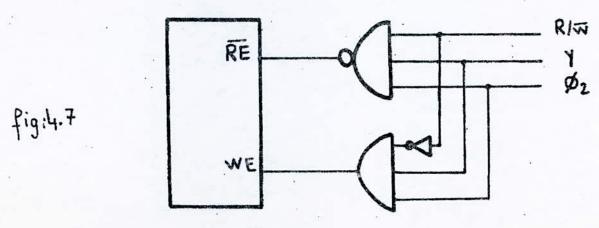

La figure 4.6 montre l'obtention du signal Y. On voit donc que Y ne se met à l'état haut que si un des circuits est adressé, en ajoutant à cela les signaux  $\mathbb{R}/\bar{\mathbb{W}}$  et  $\emptyset 2$ , on commande les 8T26. Voir figure 4.7

$$RE = R/\tilde{W} \cdot Y \cdot \emptyset2$$

$$WE = R/\tilde{W} \cdot Y \cdot \emptyset2$$

EXEMPLE: Pour lire un octet de l'eprom, Y se met à 1 car il y a adressage de cette dernière,  $R/\bar{W}=1$  puisqu'il y a lecture par le microprecesseur et au front montant de  $\emptyset 2$  on aura RE=WE=0

Donc guand  $R/\widetilde{W} = 1$  et  $\widetilde{RE} = WE = 0$ , une lecture a lieu.

### 4.3 - Lignes de contrôles utilisées

Le comparateur est validé par la ligne V.U.A 'Valid user's address). Cette ligne est mise à 1 lorsque l'on adresse la zone mémoire disponible pour l'utilisateur (0000 à E800).

RESET : Cette ligne attaque les 2 PIA (entrées 34) et le Timer (entrée 8), elle sert à la réinitialisation des circuits, elle est active sur une transition négative.

Ø2 : Signal d'horloge issu du microprocesseur, de fréquence 1 MHZ, il attaque les PIA (entré de validation 25) et le Timer (entrée 17).

### 4.4 - Utilisation des circuits

Le PIA1 sert de liaison parallèle entre la première carte (ou carte d'acquisition de données) et le microprocesseur. Le nort A est programmé en entrée (pour les données des paramètres), le port B l'est en sortie ; il adresse un décodeur (1 parmi 16) afin d'assurer le multiplexage des paramètres à l'entrée.

Le Timer est utilisé pour générer une interruption IRO toutes les 5 secondes, ce qui permet de faire l'auto-test. Le programme d'interruption teste alors tous les sous-programmes utilisés pour le traitement des paramètres.

L'eprom contient le logiciel établi.

Ouant au PIA2 seul le port B est utilisé pour contrôler les leds.

#### LISTE DES PRINCIPALES ABREVIATIONS

Ch1 : chaîne de fission : seuil puissance

Ch2 : chaîne logarithmique 1 : seuil puissance

Ch3 : chaîne logarithmique 2 : seuil puissance

Ch4: 7 états logiques tout ou rien

Ch5 : chaîne de fission : seuil période

Ch6 : chaîne logarithmique 1 : seuil période

Ch7 : chaîne logarithmique 2 : seuil période

Ch8 : chaîne de sécurité 1

Ch9 : chaîne de sécurité 2

Ch10: 3 états logiques tout ou rien.

Dans les organigrammes de traitement des chaînes 1, 2, 3, 8, 9, la configuration xX correspond à l'écriture "mantisse-exposant".

### CHAPITRE V - PROGRAMMATION DU SYSTEME

L'élaboration du logiciel permettant de gérer le système se devait de répondre à l'impératifs :

- traitement de la séquence de montée des barres.

- traitement de la séquence de chute d'urgence des barres.

- permettre un auto-test périodique.

Le programme a été scindé en plusieurs subroutines plus ou moins indépendantes ce qui permet un contrôle auto-testant plus aisé et plus fiable. Presque tous les sous-programmes reposent sur la séquence suivante :

- lecture de la valeur du paramètre

- comparaison aux valeurs seuils

- décision.

Notons que la plage de variation des paramètres est très large (10 puissance - 10 à plus de 5.10 puissance + 4) ; à l'aide d'un microprocesseur 8 bits il est impossible de pouvoir toutes les représenter, d'où il a été convenu alors d'utiliser une représentation sous la forme "mantisse-exposant" de 4 bits pour chaque partie. Pour ce qui est du signe de l'exposant, nous supposerons qu'un pré-traitement antérieur a lieu. Avec cette convention d'écriture nous pouvons traiter des valeurs évoluantes dans la plage 15.10 puissance + 15.

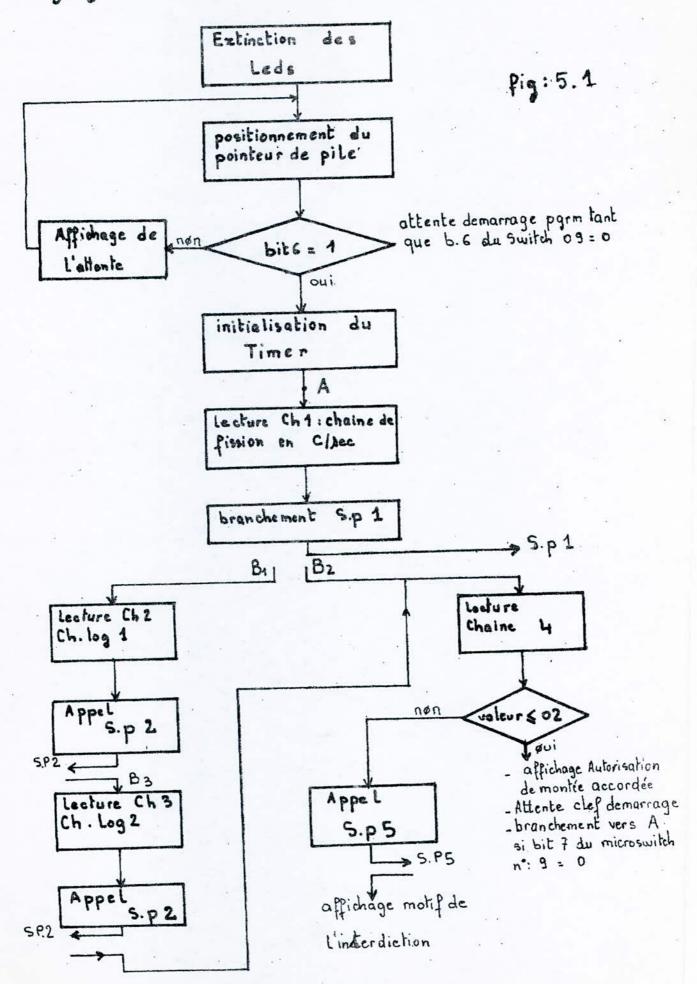

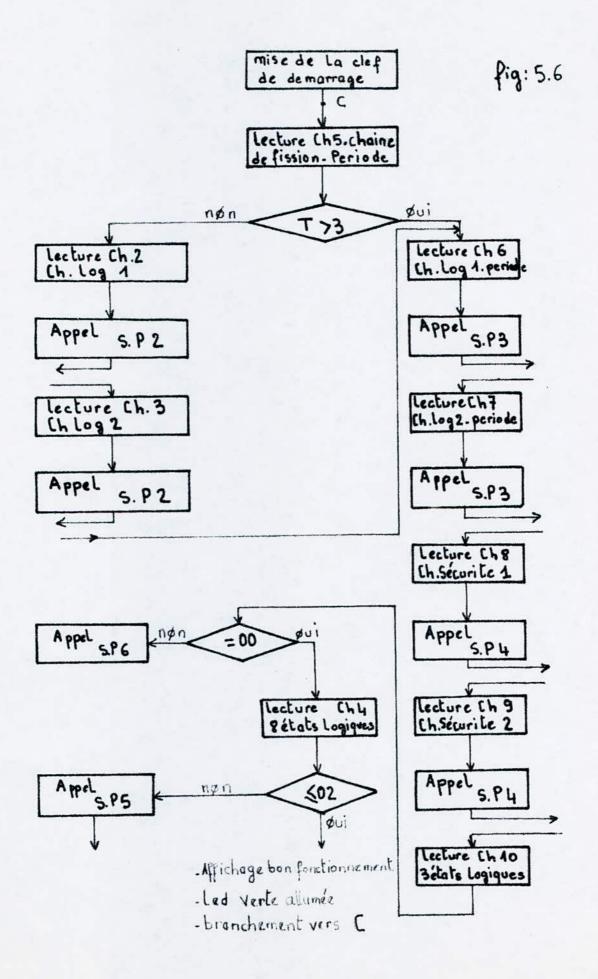

### 5.1 - Boucle d'autorisation de montée des barres.

Le synoptique général est donné en figure 5.1. Dans un premier temps nous trouvons un programme d'initialisation qui consiste en l'extinction des différentes leds et la mise en attente du processeur ; un message apparaît sur l'écran de visualisation ; celui-ci persiste tant qu'une action de l'opérateur n'a pas lieu pour lui permettre de commencer le traitement. Celui-ci débute lorsque le bit 6 du microswitch n° 9 est mis à 1 ; une initialisation du Timer est alors effectuée (voir Fig 3.9)

Le point A indique le début de la **pha**se de contrôle proprement dite, il y a alors :

- lecture du 1er paramètre

- comparaison aux valeurs seuils

- décision.

# Organigramme Pour Autorisation de Montée des Barres

La lecture des paramètres se fait par l'intermédiaire du PIA 1 ; un organigramme détaillé est donné en page figure 3.18

La comparaison se fait par un test vis-à-vis des valeurs seuils conservées en mémoire.

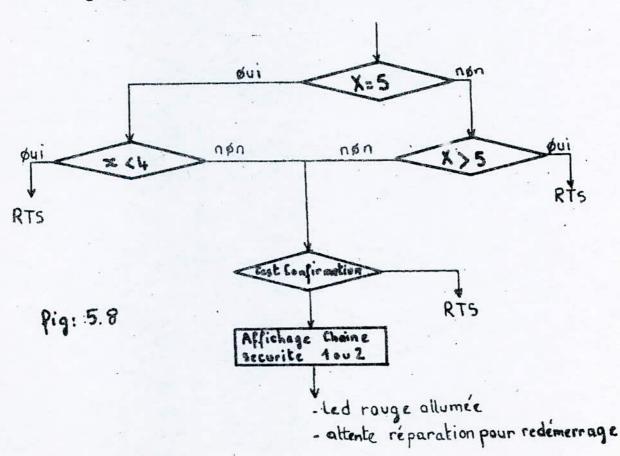

Au niveau de la décision 2 cas peuvent se présenter :

1er cas : le paramètre est correct, il y a alors passage vers la chaîne suivante.

2ème cas : le paramètre est incorrect, le processeur procède alors à une confirmation de la valeur car il y a souvent des écarts aléatoires (ou valeurs pics) qui peuvent fausser le contrôle, si la confirmation a lieu il y a alors affichage de cet état et interdiction de lever les barres. Le message persiste tant qu'une réparation n'a pas lieu, dès que la valeur du paramètre redevient correcte, il y a poursuite du traitement.

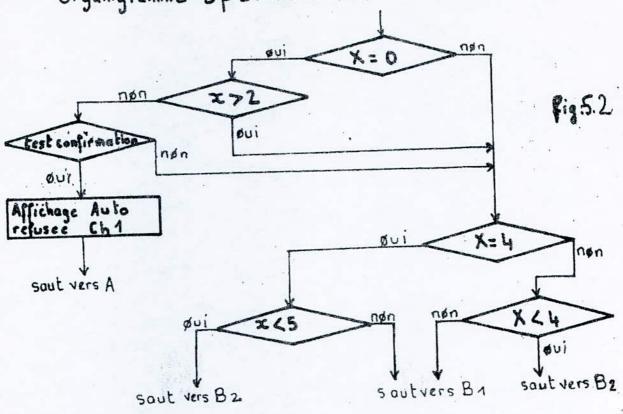

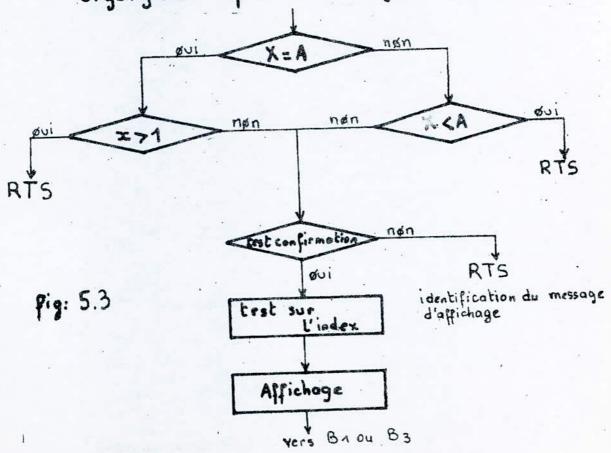

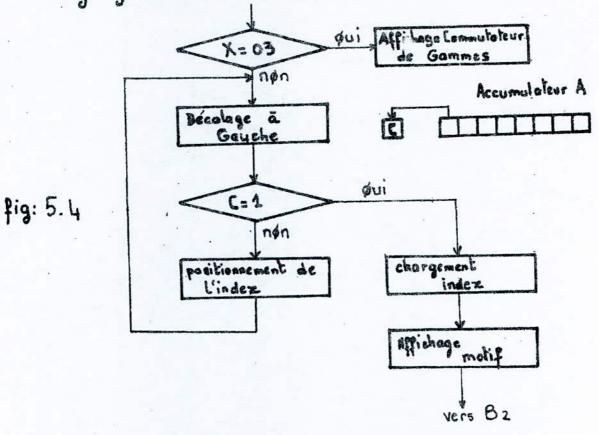

Les organigrammes des différentes subroutines sont données en figure 52, 53, 54.

Si tous les paramètres de la séquence de démarrage sont correctes, il y a affichage d'un message décrivant la situation, attente de la mise de la clé de démarrage et signalisation par la led jaune.

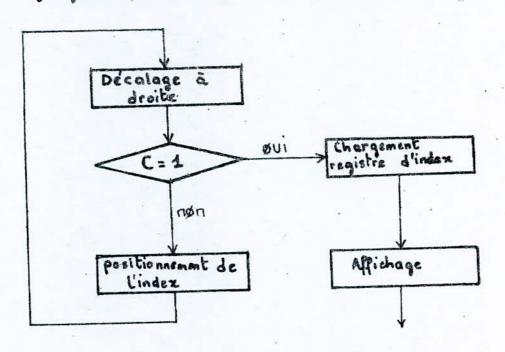

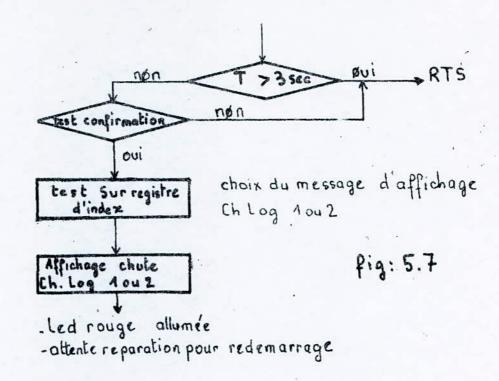

#### 5.2 - Boucle de chute d'urgence :

Une fois que l'autorisation de montée des barres est accordée, il y a passage vers la séquence de traitement de chute d'urgence par l'intermédiaire du bit 7 du microswitch n° 9 (mise à l'état 1) qui simule la mise de la clé de démarrage. L'organigramme détaillé est donné par la figure 5.6. La structure des tests des différentes chaînes est identique à celle du premier programme ; il y a une modification au niveau de la décision puisque dans ce cas :

1er : Si le paramètre est correct, il y a passage à la chaîne de

mesure suivante

2ème : Si le paramètre est incorrect, il y a chute d'urgence des barres avec affichage du motif et signalisation par la led rouge. Le processeur se met alors en attente de la réparation tion et d'une action de l'opérateur sur le clavier pour

# Organigramme Sp1: Chaine de Fission Ch1

# Organigramme Sp2: Chaines Logarithmiques Ch 28Ch3

Organigramme SP5. Troitement des 7 Etats Logiques Ch

Organigramme SP6. Traitement des 3 états Logiques. C 10

Pig: 5.9

## Organigramme Chute d'Urgence

effectuer un nouveau démarrage. Une fois que le défaut a été palié l'opérateur se doit d'introduire le mot "NEXT" pour redémarrer le programme (voir Fig 5.7,58,59).

Dans le cas où tous les paramètres sont corrects, il y a affichage d'un message indiquant cet état de fait tout en surveillant l'évolution des différentes données, il y a alors une signalisation par la led verte.

#### 5.3 - Programme Auto-testant

Pour assurer une plus grande fiabilité de notre dispositif, nous avons prévu un programme auto-testant qui se déroule à chaque fois qu'une IRQ a lieu. Celle-ci est fournie par le Timer toutes les 5 secondes L'organigramme détaillé est indiqué par la figure 5.10. La procédure employée par l'auto-test consiste à traiter toutes les subroutines par des valeurs erronées qui doivent en principe entraîner une interdiction. Si celle-ci a lieu ceci implique que le programme se déroule convenablement ; il est à noter que l'interdiction est inhibée par soft pour éviter de perturber la bonne marche du réacteur.

Le programme auto-testant réalise aussi le contrôle des mémoires RAM utilisées pour s'assurer que le processeur effectue des lectures et des écritures correctes, dans le cas contraire un message indiquant une ammalie au niveau des mémoires RAM est affiché.

Un message d'auto-test positif apparaît toutes les 5 secondes. Son absence témoigne d'une perturbation dans le déroulement du programme.

### 5.4 - REMARQUES CONCERNANT LES DIFFERENTS SOUS-PROGRAMMES

Lors du programme de chute d'urgence, nous avons prévu le contrôle de la chaîne 4 (nécessaire dans la phase de démarrage) et cela pour éviter tout risque d'accident (ouverture de la porte camion pendant le fonctionnement du réacteur par exemple).

La simulation des états "tout ou rien" se fait par les bits suivants :

- microswitch numéro 03 bit 7 : porte camion

- " " bit 6 : bouchon canal 1

- " " bit 5 : bouchon canal 2

- " " bit 4 : clapets

### Organigramme SP3 Chaines Logarithmiques 1 et 2 : Ch6 et Ch7

### Organigramme SP4 Chaines Securites 1et2: Eh8et9

Autotest Organigramme Pour ACCA = 4.0 Appel S.P 1 ACCA = 1.A fig. 5. 10 Appel S.P2 ACCA = 02 Appel s.P3 ACCA = 41 Appel S.PS Appel siph ACC A = 04 ACCA = 04 Appel S. P 6 Test Memoires R.A.M. Affichage Ruto.test

positif reinitialisation RTI

| - r | microswitch | numéro | 03 | bit 3 | 3   | : clef de ronde mécanicien      |

|-----|-------------|--------|----|-------|-----|---------------------------------|

| -   | 14          | 11     | 21 | bit 2 | 2   | clef de ronde électricien       |

| -   | 911         |        | 95 | bit 1 | 1   | commutateur de gammes           |

| _   | 51          | 11     | 19 | bit C |     | commutateur de gammes           |

| - I | nicroswitch | numéro | 09 | bit 2 | 2   | : ordre manuel plongeon         |

| -   | 11          | **     | 18 | bit 1 | L , | ordre manuel pupitre            |

| _   | n e         | 18     | ** | bit 0 | )   | : support mécanique des barres. |

La subroutine assurant le traitement des différents messages à afficher réside dans le programme EXBUG à l'adresse FA 14. Nous leurs avons réservés l'espace mémoire compris entre 0300 et 067F.

L'interruption programmable SWI a été utilisée pour permettre le déroulement de la séquence "d'attente de réparation et l'introduction d'un mot code" pour relancer le programme. Pour ceci il suffit de fournir l'adresse du début de la séquence en question aux adresses FFFA et FFFB.

L'insertion du comparateur SN 74 H 85 permet la translation de la carte dans l'espace mémoire disponible de 1000 en 1000 (voir Chap 4). Nous devons donc procéder à des modifications au niveau du programme et ceci en remplaçant toutes les valeurs marquées d'un astérisque par l'équivalent hexadécimal des 4 bits d'adresses de poids forts validés.

Exemple : espace réservé 5000 5FFF programme

| adresse | code opératio | on opérande | s |

|---------|---------------|-------------|---|

| 5006    | BD            | 52 AO       |   |

| 500B    | BD            | 52 80       |   |

| 500E    | CE            | 53 00       |   |

## Programme 1 : Autorisation de montée des barres

| 000 | 00         | CLR 7290    | 7E 72 90  |                         |

|-----|------------|-------------|-----------|-------------------------|

|     | 3          | LDS #7905   | 8E 79 05  |                         |

|     | 6          | JSR 02A0    | BD *02 AO |                         |

|     | 9          | LDA B # 00  | C6 00     |                         |

|     | В          | JSR 0280    | BD *02 80 | Lecture de la chaine 1  |

|     | ٤          | LDX # 0300  | CE *03 00 |                         |

|     | 11         | JSR OZAA    | BD *O2 AA |                         |

|     | 14         | BRA SP1     | 20 4A     | en 0060                 |

|     | 16         | JSR 02A0    | BD *02 AO |                         |

|     | 19         | LDA B # 04  | C6 04     |                         |

|     | 18         | JSR 0280    | 80 *02 80 | Lecture de la chaine 2. |

|     | <b>4</b> E | LDX #0310   | CE *03 20 |                         |

|     | 21         | TSR 02AA    | BD *02 AA |                         |

|     | 24         | BSR SP2     | 80 74     | en 009A                 |

|     | 26         | JSR 02A0    | BD *02 AO |                         |

|     | 29         | LDA B # 0.2 | C6 02     |                         |

|     | 2B         | JSR 0290    | BD *01 80 | Lecture de la chaine 3  |

|     | 26         | LDX # 0340  | CE *03 40 |                         |

|     | 31         | JSR OZAA    | BD *02 AA |                         |

|     | 34         | BSR SP2     | 8D 64     | en 009A                 |

|     | 36         | CLR 7291    | 7F 72 91  |                         |

| LP2 | 39         | LDAB # 03   | C6 03     |                         |

|     | 38         | JSR 0280    | BD *02 80 | Lecture de la chaine 4  |

|     | 3E         | JSR 02AA    | BD *O2 AA |                         |

|     |            |             |           |                         |

|     | 0041 | CMPA # 02  | 81 02     |                 |

|-----|------|------------|-----------|-----------------|

|     | 43   | BLS LP1    | 23 OB     |                 |

|     | 45   | JSR 023A   | BD *02 3A | Vers SP5        |

|     | 48   | LDX # 05C0 | CE *OS CO |                 |

|     | 4B   | JSR 0780   | BD *07 BO | Pour affichage. |

|     | 4E   | BRA LP2    | 20 E9     |                 |

| LP1 | 50   | LDX # 0360 | CE *03 60 |                 |

|     | 53   | JMP 02C0   | 7E *02 CO | Pour affichage. |

## Sous-programme 1 pour chaine de fission (C1)

|     | 0060 | TAB        | 16       |

|-----|------|------------|----------|

|     | 61   | AND.B # FO | C4 FO    |

|     | 63   | T5 T8      | 50       |

|     | 64   | BEQ LP3    | 27 09    |

| ,   | 66   | ANDA # OF  | BL OF    |

|     | 68   | TST A      | 40       |

|     | 69   | BNE LP1    | 26 20    |

|     | 68   | CMPB # 20  | C1 20    |

|     | 60   | BHI LP1    | 22 1C    |

| LP3 | 6F   | STS 7294   | BF 72 94 |

|     | 72   | LOAB 7294  | FG 72 94 |

| 8   | 75   | CMPB # 78  | C1 78    |

|     | 77   | BEQ LP4    | 27 1C    |

| 8   | 79   | TST 7293   | 7D 72 93 |

|     |      |            |          |

| c   | 070        | BEQ LPS     | 27 08     |              |

|-----|------------|-------------|-----------|--------------|

| LP6 | 7E         | DEC 71.93   | 7A 72 93  |              |

|     | 81         | BNE LP6     | 26 FB     |              |

| LPT | 83         | JMP 0009    | 7E *00 09 |              |

| LP5 | 86         | JSR 0780    | BD *07 B0 |              |

|     | 89         | BRA LP7     | 20 F8     |              |

| LP1 | <b>8</b> B | CMPA # 04   | 81 04     |              |

|     | 80         | BNE LP2     | 26 02     |              |

|     | 8F         | CMPB # 50   | C1 50     |              |

| LP2 | 91         | BLT (0036)  | 2D A3 Ve  | ers chaine 4 |

|     | 93         | BRA (00 16) | 20 81 ve  | ers chaine 2 |

| LP4 | 95         | RTS         | 39        |              |

# Sous-programme 2. pour chaines Logarithmiques 1 et 2.

| o   | APO | TAB        | 16       |

|-----|-----|------------|----------|

|     | 98  | ANDB # FO  | C4 FO    |

|     | 90  | TST B      | 5D       |

|     | 98  | BEQ LP3    | 27 OA    |

|     | AO  | AND A # OF | 84 OF    |

|     | AZ  | CMPA # OA  | 81 OA    |

|     | A4  | BNE LP1    | 26 48    |

|     | A6  | CMPB # 10  | C1 10    |

|     | AB  | BHI LP2    | 22 48    |

| LP3 | AA  | STS 7294   | BF 72 94 |

|     |     |            |          |

|     | OOAD      | LDAB 7294  | F6 72 94  |

|-----|-----------|------------|-----------|

|     | ВО        | CMP B # 78 | C1 78     |

|     | B2        | BEQ LPZ    | 27 3E     |

|     | BA        | TST 7293   | 70 72 93  |

|     | В₹        | BEQ LPS    | 27 07     |

| LP6 | 89        | DEC 7293   | 7A 72 93  |

|     | ВС        | BNE LPG    | 26 FB     |

|     | BE        | BRA LPT    | 20 14     |

| LP5 | CO        | STX 7296   | FF 72 96  |

|     | <b>C3</b> | LDAB 7297  | FG 72 97  |

|     | C6        | CMPB # 20  | C1 20     |

|     | (8        | BEQ LP4    | 27 07     |

|     | CA        | CMPB # 40  | C1 40     |

|     | CC        | BEQ LPL    | 27 03     |

| •   | CE        | JMP OTD6   | 7E *07 D6 |

| LP4 | D1        | JSR 07B0   | BD *07 BO |

| LPI | D4        | STX 7296   | FF 72 96  |

|     | DŦ        | LDA B 7297 | F6 72 97  |

| 2   | DA        | CMP 8 # 20 | C1 20     |

|     | DC        | INS        | 31        |

|     | DD        | INS        | 31        |

|     | DE        | BEQ LP8    | 27 08     |

|     | EO        | CMPB # 40  | C1 40     |

|     | EΣ        | BEQ LP9    | 27 OF     |

|     | E4        | CMPB # AO  | C1 AO     |

|     | E6        | BEQ LP10   | 27 OE     |

| 8)  | E8        | JMP 0122   | 7E *01 22 |

| LP8 C | OEB | JMP | 0019 | 7E *0 | 0 19  |

|-------|-----|-----|------|-------|-------|

| LP1   | EE  | BLT | LP2  | 20 0  | 2     |

|       | FO  | BRA | LP3  | 20 B  | 8     |

| LP2   | FZ  | RTS |      | 39    |       |

| LP9   | F5  | JMP | 0029 | 7E *0 | 00 29 |

| LP10  | F6  | JMP | 0112 | 7E *0 | 1 12  |

## Programme 2: Chute d'urgence des barres

| 0 100 | CLR 7292    | 7F 72 92  |                        |

|-------|-------------|-----------|------------------------|

| 103   | LDS # 7905  | 8E 79 05  |                        |

| 106   | LDA B # 04- | C6 O4     |                        |

| 109   | JSR 0280    | BD *02 80 | Lecture de La chaine 5 |

| 108   | CMPA # 03   | 61 03     |                        |

| 100   | BHI LP1     | 22 21     |                        |

| 10F   | JSR O2A3    | BD *02 A3 |                        |

| 112   | LDA B # 01  | C6 01     |                        |

| 114   | JSR 0280    | BD *02 80 | Lecture de la chaine 2 |

| 117   | JSR OZAA    | BD *02 AA |                        |

| 11A   | LDX # 03A0  | CE 03 A0  |                        |

| 110   | BSR SP2     | 80 DB     | en oofA                |

| 11F   | JSR 02A3    | BD *02 A3 | - X                    |

| 122   | LDAB # OZ   | C6 02     |                        |

| 124   | JSR 0280    | BD *02 80 | Lecture de la chaine 3 |

| 127   | JSR OZAA    | BD *02 AA |                        |

|          | 012A | LDX # 03CO | CE *03 CO |                        |

|----------|------|------------|-----------|------------------------|

|          | 120  | JSR 009A   | BD *00 9A | vers SP2               |

| LP1      | 130  | JSR 02A3   | BD *02 A3 |                        |

|          | 133  | LDAB # 05  | C6 05     |                        |

|          | 135  | JSR 0280   | BD *02 80 | Lecture de la chaine 6 |

|          | 138  | LDX # 03E0 | CE *03 E0 |                        |

|          | 138  | JSR OZAA   | BD *OZ AA | 9                      |

|          | 13E  | BSR SP3    | 8D 5B     | en 019B                |

| £.       | 140  | JSR 02A3   | BD *02 A3 |                        |

|          | 143  | LDAB# 05   | C6 06     |                        |

|          | 145  | JSR 0280   | BD *02 80 | Lecture de la chaine 7 |

|          | 148  | LDX # 0406 | CE *04 06 |                        |

|          | 14B  | JSR OZAA   | BD *O2 AA |                        |

|          | 146  | BSR SP3    | 80 48     | en 019B                |

|          | 150  | JSR OZA3   | BD *02 A3 |                        |

|          | 153  | LDAB# OF   | C6 07     |                        |

|          | 455  | JSR 0280   | BD *02 80 | Lecture de la chaine 8 |

| #3<br>E5 | 158  | LDX # 042C | CE *04 2C |                        |

|          | 15B  | JSR OLAA   | BD *02 AA |                        |

|          | 15E  | BSR SP4    | 8D 68     | en o1CB                |

|          | 160  | JSR 02A3   | BD TOZ A3 |                        |

|          | 163  | LDA B # 08 | C6 08     |                        |

|          | 165  | JSR 0280   | 80 tos 80 | Lecture de la chaine 9 |

|          | 168  | FDX # OFFE | CE *04 4E |                        |

|          | 168  | JSR OZAA   | BD OZ AA  |                        |

|          | 16E  | BSR SP4    | 8D 5B     | en 01CB                |

|          | 170  | LDAB # 09  | C6 09     | *                      |

| 0172    | JSR 0280   | BD *02 80 | Lecture de La chaine 10 |

|---------|------------|-----------|-------------------------|

| 175     | JSR OZAA   | BD *OZ AA |                         |

| 178     | ANDA # OF  | 84 07     |                         |

| 17A     | TST A      | 40        |                         |

| 17B     | BNE LP2    | 26 18     |                         |

| 170     | LDAB# 03   | C( 03     |                         |

| 17F     | JSR 0280   | BD *02 80 |                         |

| 182     | JSR OZAA   | BD *02 AA |                         |