## THESE

Joseph Lea

présentée

M0022/87A

A L'UNIVERSITE DES SCIENCES ET DE L'A

pour l'obtention du grade de

MAGISTER

EN ELECTRONIQUE DES SYSTEMES

par

المدرسة الوطنية المتعددة التقنيات المكستبسة — BIBLIOTHEQUE المكستبسة كالمكافعة المحافظة المح

Fatima OULEBSIR Epouse BOUMGHAR

Conception et réalisation d'un système multiprocesseur pour la simulation d'un processus physique continu : Algorithmes numériques

Soutenue le 03 Juillet devant la commission d'examen :

MM. A. DAHEL

Président

A. ADANE

Examinateurs

H. TEDJINI

R. TOUMI

R. OUIGUINI

B. SANSAL

Rapporteur

H002287

### THESE

présentée

المدرسة الوطنية المتعددة التقنيات المكتبة المكتبة المكتبة المكتبة المكتبة Eeole Nationale Polytechnique

# A L'UNIVERSITE DES SCIENCES ET DE LA TECHNOLOGIE HOUARI BOUMEDIENE

pour l'obtention du grade de MAGISTER EN ELECTRONIQUE DES SYSTEMES

par

Fatima OULEBSIR Epouse BOUMGHAR

Conception et réalisation d'un système multiprocesseur pour la simulation d'un processus physique continu : Algorithmes numériques

Soutenue le 63 Juillet devant la commission d'examen :

MM. A. DAHEL

Président

A. ADANE

Examinateurs

H. TEDJINI

R. TOUMI

R. QUIGUINI

B. SANSAL

Rapporteur

A mon père

A ma mere

A mes freres et soeurs

المدرسة الوطنية المتعددة التقنيات المكتب BIBLICTHEQUE المكتبة Ecole Nationale Polytechnique

A Mohammed

A Yasmine

المدرسة الوطنية المتعددة التقنيات المكتبة -- BIBLIOTMEQUE Ecole Nationale Polytechnique

J'exprime tous mes remerciements à Monsieur le Professeur DAHEL pour m'avoir fait l'honneur , d'assumer la présidence de ce jury .

Que Monsieur le Frofesseur B.SANSAL soit assure de toute ma gratitude et ma reconnaissance, pour m'avoir accueillie dans la post-graduation Electronique des Systèmes, pour m'avoir dirigée et, encouragée tout au long de ce travail.

J'adresse ma sincère reconnaissance à Monsieur BESSALAH

Directeur du CDTA au CEN , pour avoir mis à ma disposition les

moyens du Laboratoire Architecture des Systèmes , ainsi que

pour ses précieux conseils .

J'exprime tous mes remerciements à Monsieur H.TEDJINI , pour avoir suscité en moi l'intérêt pour le multiprocessing et , pour m'avoir guidée dans la phase initiale du projet .

J'adresse tout particulièrement à Monsieur le Professeur R.TOUMI mes sincères remerciements pour ses conseils , et , ses critiques déterminantes , pour mener à termé ce projet .

Je ne manquerais pas d'exprimer mes vifs remerciements ainsi que ma reconnaissance à Monsieur R.OUIGUINI , pour l'immense aide qu'il a prodigué au travail mené .

J'exprime tous mes remerciements à Monsieur le Professeur ADANE , Directeur de l'Institut d'Electronique , pour avoir acceptés de participer à ce jury .

المدرسة الوطنية المتعددة التقنيات المكتبة — BIBLIOTHEQUE المكتبة كا Ecole Nationale Polytechnique

Je remercie trés chaleureusement Mademoiselle A.HELIFA pour sa participation sérieuse au projet et , à qui j'exprime ma profonde gratitude .

Je ne saurais pas oublier le précieux concours de Mademoiselle N.TAFAT , au cours de la réalisation du système ; qu'elle trouve ici ,le témoignage de ma sincère reconnaissance.

Enfin , je remercie toutes les personnes , en particulier le personnel du laboratoire Architecture des systèmes , qui ont de prés ou de loin , aider à la mise en forme du projet .

المدرسة الوطنية المتعددة التقنيات المكتبة -- BIBLICTHEQUE Ecole Nationale Polytechnique

- SOMMAIRE -

INTRODUCTION

#### CHAPITRE I

#### LES ARCHITECTURES PARALLELES

- I. Classification des calculateurs à hautes performances

- I.l. Structure de contrôle séquentiel

- I.2. Structure de contrôle parallèle

- II. Les réseaux d'interconnexion

- II.1. Réseaux d'interconnexion statiques

- II.2. Réseaux d'interconnexion reconfigurables

- III. Quelques exemples de calculateurs spécialisés

### CHAPITRE II

#### STRUCTURES MATERIELLES DES SYSTEMES MULTIMICROPROCESSEURS

- I. Architecture des multimicroprocesseurs

- I.l. Structure logique

- I.2. Structure physique

- I.3. Mode d'interaction

- I.4. Mode de traitement

- II. Evaluation des performances

- II.1 Capacité de traitement

- II.2 Partage des données communes

- II.3. Délai de transmission des messages

- III. Amélioration des performances

#### - CHAPITRE III -

#### DESCRIPTION DE LA MACHINE MULTIMICROFROCESSEUR

- I. Définitions des entités intervenants dans un exécutif

- II. Architecture du système multiprocesseur

- II.1. Choix de la structure multiprocesseur

- II.2. Présentation du système Multimu

- 1. Le processeur principal

- 2. Le processeur secondaire

- . . . 3. Le bus interprocesseurs

- 4. Le logiciel de gestion

- III. Description de la machine Unités de traitement

- III.1. Description matérielle

- III.2. Structure logicielle

#### - CHAPITRE IV -

#### LES UNITES DE TRAITEMENT

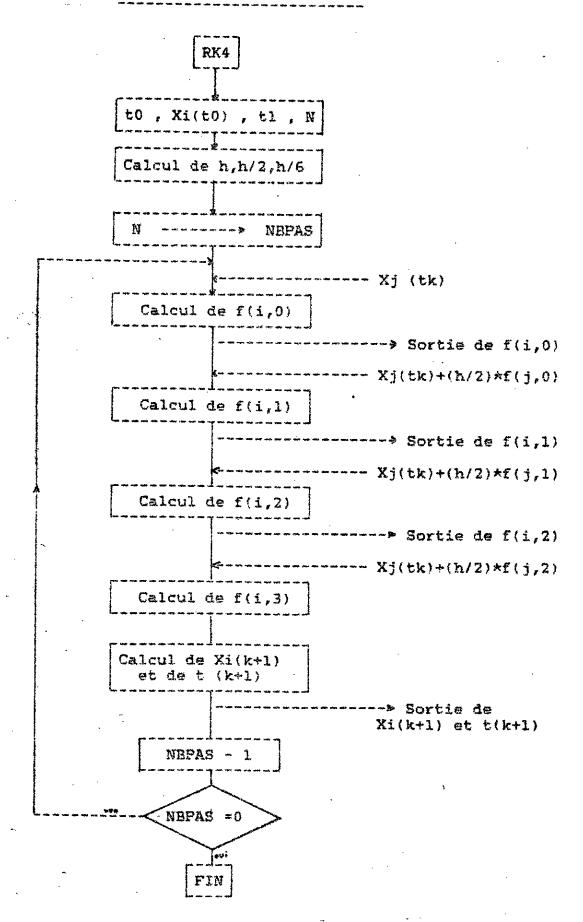

- I. Méthodes numériques

- II. Traitement numérique

- II.1 Position du problème

- II.2 Choix de la méthode

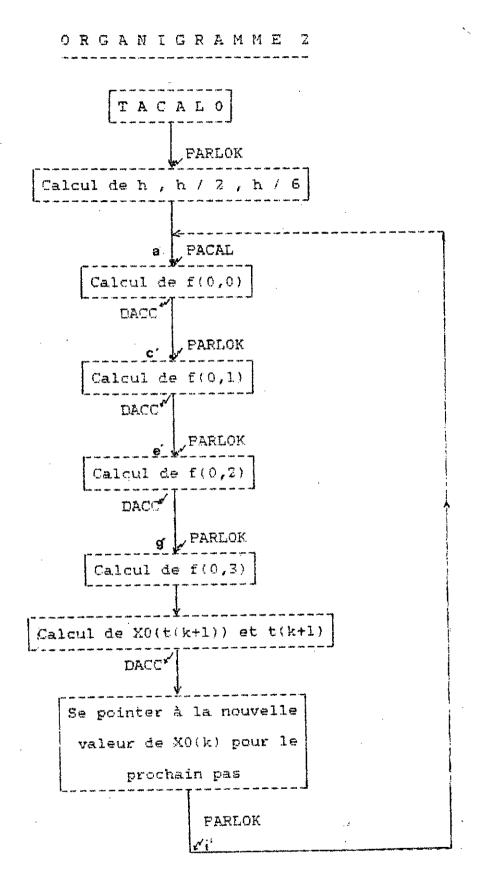

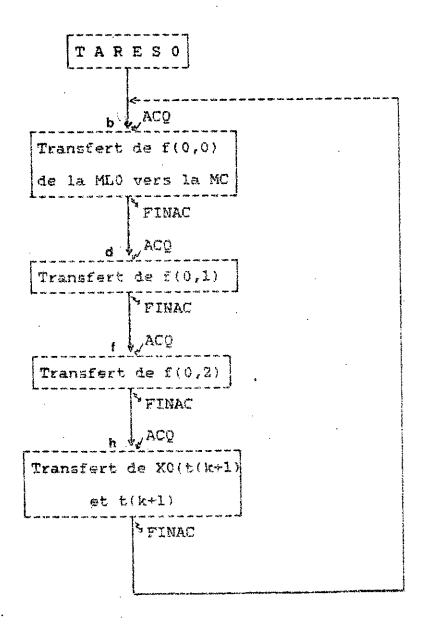

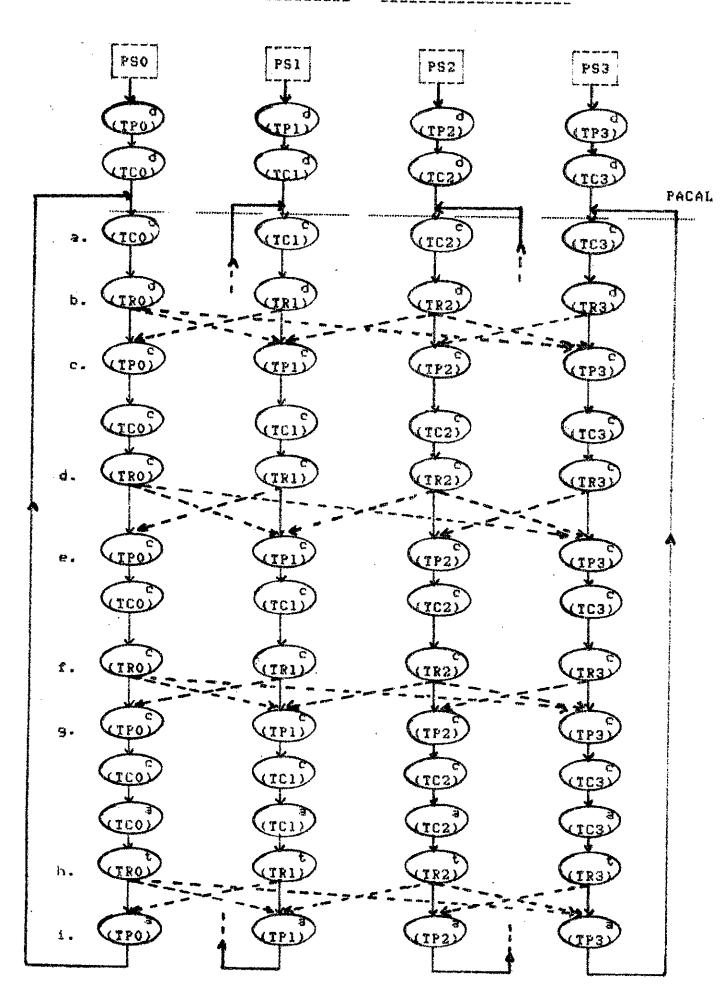

- II.3 Algorithmes numériques et organigrammes

- II.4 Graphe de dépendance

- CHAPITRE V -

RESULTATS ET PERFORMANCES

CONCLUSION

ANNEXES

BIBLIOGRAPHIE

المدرسة الوطنية المتعددة التقنيات | BIBLIOTHEQUE | المكتبة | Ecole Nationale Polytechnique

#### - INTRODUCTION -

La simulation de phénomènes physiques peut s'effectuer, à l'aide des équations du processus en utilisant des outils tels:

- le calculateur analogique .

- le calculateur hybride .

- le calculateur numérique classique .

- le calculateur spécialisé .

Les lois de base d'un processus physique continu , peuvent s'exprimer par un système d'équations différentielles représentant le modèle mathématique du processus à simuler .

Il existe d'autres modes de représentation (telles les équations aux dérivées partielles , les fonctions de transfert , les équations d'état , etc ... )

Le mathématicien peut , avec des conditions initiales préalablement posées , prouver qu'il existe une solution unique au système d'équations régissant le phénomène et décrivant le processus de façon complète . Mais il est souvent impossible , de trouver une expression analytique de la solution exacte , mis à part quelques cas simples . Les méthodes numériques peuvent approcher la solution de façon aussi précise qu'on le désire par augmentation du volume de calcul arithmétique .

Le système d'équations différentielles représentant le processus physique peut se ramener à la forme : d(Xi(t))/dt = fi (t,X1(t),X2(t),...,Xn(t),r(t))

i=1,...,n

où Xi(t) sont les variables d'état du système , et r(t) les entrées ou commandes .

Nous élaborons tout d'abord , une méthode numérique approchée et , pour cela , nous supposerons que les entrées peuvent être échantillonnées avant chaque évaluation des variables d'état [15] .

Le pas d'intégration numérique , h , doit être suffisamment petit pour approcher au mieux la solution .

D'autre part , il ne doit pas être trop faible , pour pouvoir assurer la prérogative temps réel .

Pour chaque point du réseau déduit de la discrétisation du champ physique, plusieurs données numériques doivent être emmagasinées et constamment remises à jour dans la mémoire du calculateur.

De plus , la contrainte temps réel qui apparaît dans certains domaines d'application , a contribué à stimuler l'accroissement des performances des calculateurs .

La puissance des ordinateurs conventionnels n'a cassé de croître grâce , en partie , à l'utilisation de technologies très rapides qui ont permis de diminuer les temps de cycle (unité centrale et mémoire ) . Néanmoins , les besoins en traitement de certaines classes de problèmes sont estimés à une opération flottante , sur 64 bits , par nanoseconde soit mille millions d'opérations flottantes par seconde (1000 MFlops) voire 10 000 MFlops!

La technologie ne peut à elle seule , répondre au problème posé . Des améliorations architecturales ont été alors apportées et ont permis d'atteindre un bon débit de calcul .

Il existe , à l'heure actuelle , des supercalculateurs fournissant de bonnes performances . Les plus puissants : CRAY XMP , VP 200 (FUJITSU) , S 810/20 (HITACHI) , SX-1 (NEC) ont des vitesses théoriques qui varient entre 400 et 800 MFlops. Or , ces machines ont été essentiellement conçues pour traiter des problèmes dont les algorithmes de résolution sont parallélisables . L'exécution d'algorithmes récursifs ou séquentiels constitue un facteur limitatif des performances globales de ces calculateurs .

Les problèmes à traiter sont souvent difficiles à vectoriser ou ne sont que partiellement vectorisables ; le rendement chute alors jusqu'à environ 10% ( voire moins ) .

Ainsi , il ne sert à rien de vouloir augmenter indéfiniment les performances vectorielles si l'on ne peut paralléliser le traitement scalaire .

L'une des voies possibles , pour faire du traitement scalaire en parallèle est le MIMD [2,4,6,10,27] ,où un flot d'instructions traite un flot de données .

Dans la présente étude , nous nous sommes intéressés à la simulation de processus physiques continus dont le modèle mathématique nous a conduit à choisir un calculateur spécialisé de type parallèle. Un système multimicroprocesseur , le Multimu , a été conçu et réalisé pour lever les contraintes de

temps et de précision .

La machine Multimu est d'architecture parallèle de type MIMD . Le contrôle et l'exécution sont parallèles .

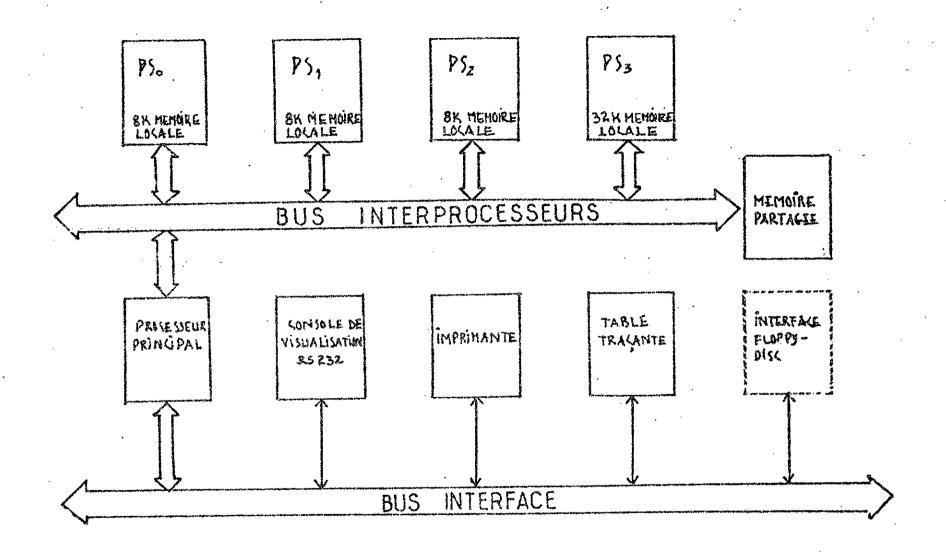

Ce système est constitué d'un processeur principal, ou maître, de quatre processeurs secondaires ou esclaves et d'une mémoire commune. Les échanges interprocesseurs s'effectuent à travers un bus commun E25,261.

Les processeurs secondaires sont chargés d'intégrer, numériquement , un système d'équations différentielles .

Notre contribution a porté , essentiellement sur la conception et la réalisation des unités de traitement numérique de la machine Multimu .

Ce mémoire s'articule autour de cinq chapitres :

- le CHAPITRE I introduit les architectures parallèles .

- au CHAPITRE II , les structures matérielles des machines multimicroprocesseurs seront décrites .

- le CHAPITRE III expose le système Multimu , son architecture et son système d'exploitation .

- au CHAPITRE IV , les unités de traitement numérique seront détaillées .

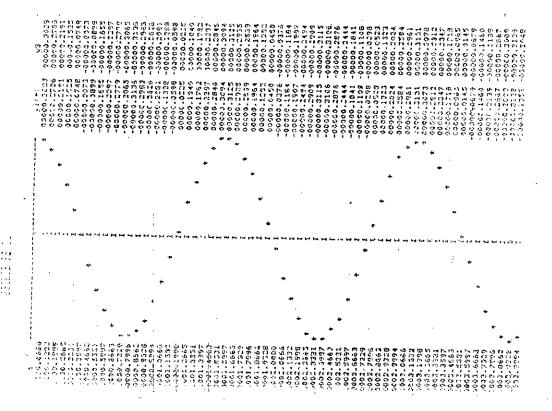

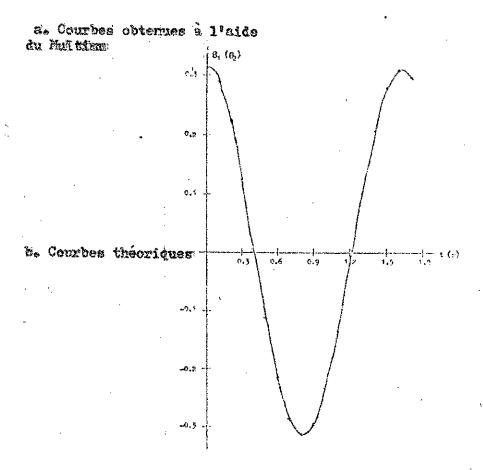

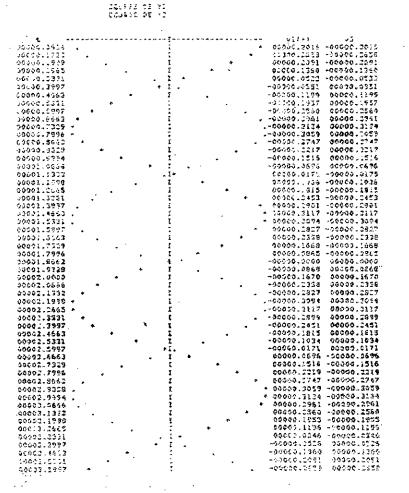

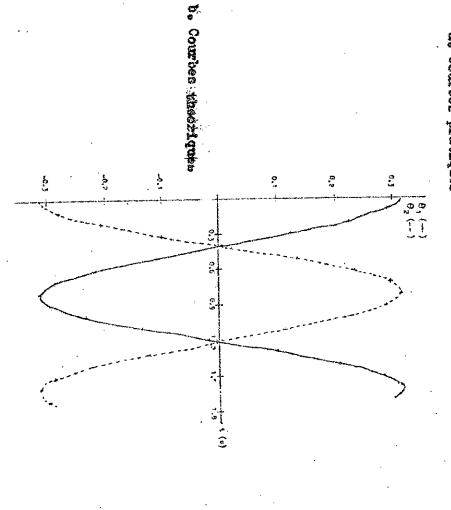

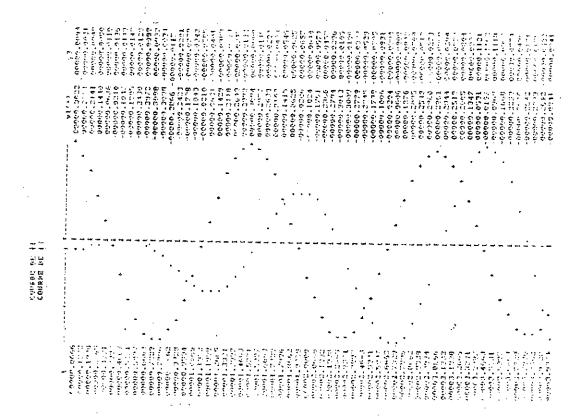

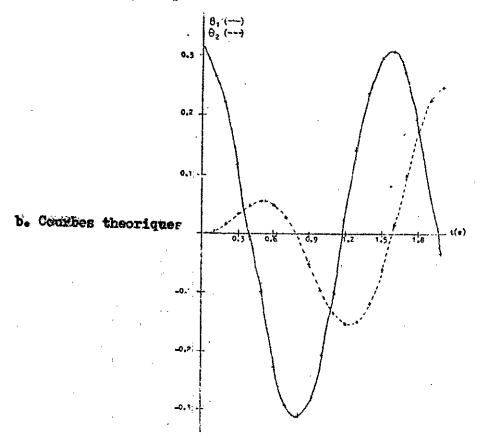

- le CHAPITRE V fournira les résultats obtenus à l'aide de la machine Multimu . La comparaison avec la solution approchée théorique sera faite .

Quelques perspectives seront proposées en conclusion .

#### - CHAPITRE I -

### LES ARCHITECTURES PARALLELES

Le développement récent des calculateurs à hautes performances répond à des besoins considérables en puissance de calcul de certaines classes d'applications .

Cette puissance concerne la précision des données , exprimées en virgule flottante sur 64 bits , ainsi que la contrainte de temps pour laquelle un nombre d'opérations arithmétiques effectuées à la seconde doit être imposé .

Les problèmes qui se posent dans les domaines de l'aérodynamique, la simulation nucléaire, la météorologie, la sismologie, le traitement d'images, la physique des plasmas..., sont caractérisés par leur complexité numérique. Les temps d'exécution sont alors prohibitifs sur les machines conventionnelles ( séquentielles ), de l'ordre de plusieurs jours, ce qui est souvent incompatible avec le problème lui-même ( exemple du traitement d'images de satellite en continu ).

Les chercheurs ont pensé alors à de nouvelles archi-tectures ; un certain degré de parallélisme a été ainsi

introduit .

On compte dans le monde plus de 150 projets de machines à structure parallèle. Certains, ont dépassé le stade de projet en passant à la phase de la construction puis, dans quelques cas à l'étape de la commercialisation.

Les limites du traitement parallèle ne sont pas toutes connues et , des questions restent posées :

- quelle est l'architecture la plus adaptée pour certaines classes de problèmes et , quel est le coût et l'avantage d'une structure spécifique par rapport à celle d'un calculateur universel .

- quel est le réseau d'interconnexion adéquat entre les processeurs .

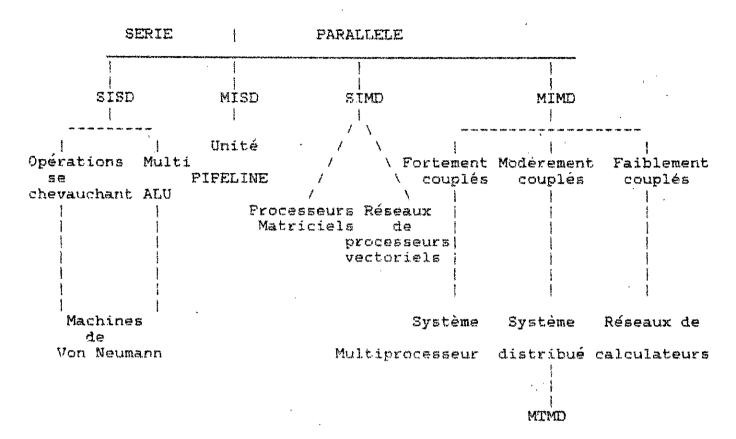

La classification de Flynn E201 concernant la nature de l'exécution d'un programme se divise en quatre catégories :

- \* la machine SISD exécute une seule instruction sur une seule donnée . C'est la machine de Von Neumann .

- \* la machine MISD , ou plusieurs instructions traitent une seule donnée ; l'utilité est perçue par les processeurs pipelines qui segmentent les calculs en stations consécutives .

- \* la machine SIMD , où une seule instruction traite plusieurs données ( donnée vectorielle ) . Ce type de machine a une unité de contrôle pour les adresses et les processeurs . Les processeurs vectoriels , matriciels et réseaux en sont un exemple .

- \* la machine MIMD où plusieurs données sont traitées simultanément par plusieurs instructions. Un ensemble de processeurs exécute chacun sa propre instruction ou programme .

Dans le présent chapitre , la classification des calculateurs parallèles à hautes performances est fournie avec

quelques réseaux d'interconnexions possibles et enfin , des exemples de calculateurs spécifiques seront cités .

### I. CLASSIFICATION DES CALCULATEURS A HAUTE PERFORMANCES.

Le séquencement des instructions se fait dans un calculateur, grâce à sa partie contrôle ; l'exécution de ces instructions se fait par la partie opérative. Ces deux parties sont appelés respectivement structures de contrôle et d'exécution .

La figure I.1 donne une classification arborescente [6] à trois niveaux , des calculateurs à hautes performances :

Organisation des calculateurs a hautee performances Strusture de Structure de controle parallele controls sequential Strusture Structure Structure d'exacutics d'execution d'execution parallele paralisic eorie Arohitee-Architeo-Architec-Architec-Architec-Architec-+ture ture culti--ture -ture SIMD/ -ture -ture MIMD/ MIM Pipeline STAD Pipeline pipelino -pipeline OS TEA ilvinc ia SPRINE IBN 360/91 CYMER 205 CHMP Masp (996). data pecy IBM 5050 STARAN FEF TI ASC PEP LÁU S-F PHOPAL 5mn 100 PROPRIEX CRAY 1

hasp - bunnoises

PICUPE I.1. CLASSIFICATION DES CALCULATRURS A HAUTES PERFORMANCES.

# I.1. Structure de contrôle séquentiel .

L'interprétation des instructions se fait séquentiellement. Ce type de contrôle peut agir sur deux structures d'exécution : série et parallèle ,lesquelles peuvent fonctionner soit en mode synchrone , soit en mode asynchrone .

# I.1.1. Structure d'exécution série ou pipeline [6,7,27]:

Elle repose sur le découpage d'un travail en tâches élémentaires , exécutée chacune par un opérateur spécialisé , de la même façon qu'un produit manufacturé est traité en passant par plusieurs postes de travail dans une chaîne industrielle .

L'opérateur spécialisé est une unité d'exécution .

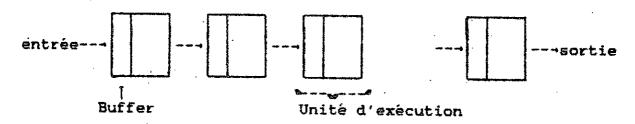

Ainsi , l'exécution d'une tâche sur l'unité d'exécution correspondante , pourra être représentée par un délai At , généralement différent pour chaque unité . Un buffer placé à l'entrée de chaque unité reçoit les résultats produits par l'unité précédente (Fig.I.2).

Le délai est le même pour toutes les unités lorsque le système pipeline est synchrone. Lorsque les unités sont complexes et les délais différents, un fonctionnement asynchrone est le plus adapté.

FIGURE 1.2. ARCHITECTURE PIPELINE .

Une unite d'exécution peut aussi bien être un circuit combinatoire qu'un véritable processeur spécialisé . Cela est précisé par l'application .

L'avantage du traitement pipeline est l'élimination du temps d'accès mémoire, lié au fait que la recherche d'opérandes s'effectue en même temps que l'exécution de l'instruction précédente.

Théoriquement , la puissance de calcul est multipliée par le nombre d'unités en service .

En pratique, le logiciel conditionne l'obtention de bonnes performances. Deux contraintes logicielles apparaissent:

\* les instructions de branchement dégradent les performances

d'un pipeline sur les instructions.

- \* les vecteurs courts ne permettent pas un fonctionnement optimal d'un pipeline sur les données régulières qui sont des vecteurs ou tableaux pleins .

- \* les données scalaires constituent un facteur limitatif des performances globales de la machine :

Pour atteindre un debit de 100 Mflops , la solution monopipeline nécessiterait des temps de cycle du pipeline inférieurs à 10 ns , ce qui est difficile à atteindre avec les technologies actuelles . ( CRAY1 avec une structure plus performante et une technologie ECL obtient un cycle de base égal à 12,5 ns ).

La solution multipipeline est alors nécessaire .

# I.1.2. Structure d'exécution parallèle .

Un travail est réparti sur un ensemble d'unités d'exécution parallèle indépendantes les unes des autres .

Trois architectures appartiennent à la structure parallèle et sont :

- l'architecture multipipeline .

- l'architecture SIMD .

- l'architecture hybride SIMD/multipipeline .

#### I.1.2:a. L'architecture multipipeline .

Les unités sont en général spécialisées dans des fonctions telles la multiplication , la division , les opérations flottantes etc ... Les mêmes principes et contraintes que l'architecture pipeline régissent l'architecture multi-pipeline .

L'interconnexion , la synchronisation et la mise en oeuvre de plusieurs systèmes pipelines spécialisés sont difficiles sur le plan matériel . D'autre part , il n'est pas aisé de réaliser un compilateur capable de faire un découpage fonctionnel optimal .

Les performances de l'architecture multipipeline, tout en étant supérieures à celles d'un monopipeline, restent limitées. Son rapport coût-performance rend cette architecture intéressante pour des applications moyennes. Lorsque les pipelines sont sophistiqués, nous obtenons des machines complexes et chères qui permettent de traiter des problèmes de grande dimension (CYBER 205, CRAYL, TI ASC).

Nous citons quelques exemples de machines :

\* le TI ASC E61 est constitué de quatre pipelines identiques

spécialisés dans le traitement vectoriel . L'efficacité des

pipelines dépend du degré de vectorisation du programme , car les données scalaires dégradent les performances de ces unités . La détection d'opérations vectorisables est fonction à la fois de la nature du problème et du nombre d'unités pipe-lines . Pour améliorer les performances du système , des processeurs périphériques exécutent le système d'exploitation . Les programmes FORTRAN traversent une phase d'optimisation de code (vectoriseur) avant d'être compilés . Le système debite 100 Mflops max à pleine charge .

\* le STAR 100 E61 est constitué de deux processeurs pipelines différents . L'un comporte un additionneur pipeline , une unité fonctionnelle et un diviseur . L 'autre est constitué d'un additionneur pipeline et d'un multiplieur .

Un développement d'outils de détection et de transformation de boucles en instructions vectorielles STAR permet d'utiliser au maximum l'efficacité du matériel disponible Un langage FORTRAN étendu permet la programmation directe d'opérations vectorielles ; en outre le programmeur a la possibilité de coder son application en langage symbolique STAR de façon à améliorer les performances. En conditions idéales , le système débite 100 Mflops .

Pour améliorer les performances réelles des systèmes multipipeline, un processeur scalaire y est parfois ajouté.

C'est le cas des machines CRAY 1 et CDC CYBER 205.

\* le CYBER 205 est constitué d'un processeur scalaire composé de 5 unités fonctionnelles pipeline et d'un processeur vectoriel de quatre unités arithmétiques pipeline. Sa puissance théorique est de 400 Mflops sur 64 bits ou 800 Mflops sur 32 bits.

Ce calculateur est autonome , mais il peut être relié à un calculateur hôte ( CYBER 170 ) pour optimiser son rendement .

La programmation directe d'opérations vectorielles se fait à l'aide d'un FORTRAN étendu . Ce compilateur détecte également les boucles et les transforme en instructions vectorielles .

\* Le CRAY 1 est inspiré de l'architecture du CDC 7600 .

Il est constitué de douze unités fonctionnelles pipeline ,

alimentés à partir de 16 registres tampon , 8 pour les

scalaires et 8 pour les vecteurs . Il possède un compilateur

CFT .

Son mode de fonctionnement est autonome mais il peut être relié à un calculateur hôte . Ses performances théoriques sont supérieures à 200 Mflops ...

# I.l.2.b. L'architecture SIMD .

L'unité de contrôle , pilote les unités d'exécution parallèles que sont les processeurs élémentaires , ou PE . Tous les processeurs effectuent la même instruction vectorielle en synchronisme .

L'arrangement des PE est , en général , matriclel et chaque processeur a sa propre mémoire de travail . Cette architecture présente cependant , des inconvenients :

- la taille de la matrice des PE est en général inférieure

à celles des matrices traitées , ce qui entraîne un découpage et rend ainsi l'écriture du compilateur plus complexe .

- le parallélisme est effectif au niveau des données du programme . Même lorsque des instructions parallèles existent dans le programme , elles sont traitées séquentiellement .

- les intercommunications dégradent les performances du système ( conflits d'accès ) ; les communications se font suivant les axes NORD-SUD EST-OUEST . Celles-ci limitent l'efficacité du traitement .

L'une des premières machines SIMD à vocation scientifique est l'ILLIAC IV [6].

\* L'ILLIAC IV comporte 64 processeurs élémentaires structurés en matrice (8x8). Un PE est constitué d'une unité arithmétique et logique, d'une mémoire de données et d'une logique de communication avec sa mémoire, l'unité de contrôle et ses PE voisins. La technologie MSI la plus complexe a été utilisée; ce qui est pénalisant.

Un logiciel IVTRAN défini comme un FORTRAN étendu, est utilisé .

\* Le BSP [6] : 16 PE sont spécialisés dans le traitement vectoriel . Ils sont synchrones et sont reliés à 17 bancs mémoire par l'intermédiaire d'un Crossbar . Un processeur scalaire se charge du traitement scalaire et de l'interprétation du programme . Le B7700 est prévu comme hôte .

# I.1.2.c. L'architecture SIMD / pipeline

Elle regroupe une exécution globale SIMD et une implémentation pipeline des unités d'exécution ; c'est une structure qui profite du parallélisme vectoriel .

\* NASF CDC 163 est constitué de quatre processeurs pipeline qui, dans le traitement vectoriel , fonctionnent en SIMD , d'un processeur scalaire et d'un processeur assurant la fiabilité .

Un système mémoire à trois niveaux assure les transferts importants de données : une mémoire centrale de 8 Mmots en technologie ECL (très rapide , consommation excessive) avec un temps d'accès à 50 ns , une mémoire intermédiaire de 32 Mmots en technologie MOS et une mémoire de masse de 128 Mmots en technologie CCD ( remplace les mémoires magnétiques ) . Ce projet est destiné à des applications de l'aérodynamique qui nécessitent des performances supérieures à 1000 Mflops effectifs.

\* Les machines systoliques [5,19] constituent une classe particulière de machines pipelines . Un système systolique est un réseau de processeurs au travers duquel circulent des données . Celles-ci sont injectées à l'aide d'un calculateur "hôte" . Les processeurs fonctionnent de façon synchrone par "battement" par analogie avec la systole qui , en cardiologie représente une contraction du coeur .

Au cours d'un "battement", chaque processeur reçoit des données qu'il traite et transmet à ses plus proches voisins . Cette machine a la régularité d'une organisation synchrone SIMD. Son principal intérêt est de permettre de traiter des données au "vol", ce que ne fait pas naturellement une architecture SIMD. Ceci explique les recherches très actives dans ce domaine.

# I.2. Structure de contrôle parallèle .

La disponibilité d'exécution des instructions guide

l'interprétation du programme qui n'est plus séquentiel .

La détection des instructions ou tâches (ensemble logique d'instructions) prêtes à être exécutées, est prise en charge par l'unité de contrôle . Les contraintes de synchronisme ou de ressources et les relations de dépendance entre les instructions (ou tâches) déterminent la disponibilité d'exécution de ces instructions (ou tâches).

Le contrôle de type MIMD exprime tous les parallélismes contenus dans un programme ; nous citerons le parallélisme entre opérations arithmétiques et logiques , et celui des instructions de contrôle .

Le supercalculateur de type MIMD est un vrai multipro--cesseur dans le sens où plusieurs PE exécutent en parallèle des instructions différentes sur des données différentes .

Dans la conception d'une machine MIMD , il existe deux façons de définir le mécanisme de détection du parallélisme :

\* la détection explicite des instructions ( ou tâches )

exécutables , s'effectue par interprétation d'une séquence de synchronisation générée soit , par le traducteur du langage de programmation soit , par l'utilisateur .

\* la détection implicite par Data flow se fait à partir des données prêtes : une instruction ( ou tâche ) s'exécute dès que ses données d'entrée sont calculées .

### I.2.1. Architecture MIMD - Détection explicite .

Citons quelques exemples de telles architectures :

\* le CMMP [6] est un multiprocesseur pour applications non

scientifiques . Il est malgré tout un bon exemple de ce

type d'architecture .

\* NASF Burroughs [6] n'est pas destiné à fonctionner en mode MIMD; cependant, il dispose d'un réseau de communication entre PE et mémoire permettant un asynchronisme total entre PE. Le mode de fonctionnement global est de type SIMD, où tous les PE sont lancés au même instant sur un ensemble d'instructions ( un corps de boucles DO par exemple), et l'exécution se déroule alors de façon autonome sur chaque PE jusqu'à la fin de la séquence. Il atteint des performances de l Gflops max à pleine charge.

### I.2.2. Architecture MIMD / multipipeline .

La mise en oeuvre de PE pipelines permet de profiter au maximum du parallélisme vectoriel . Citons quelques machines de ce type :

\* S-1 [6] est constitué de 16 PE reliés à 16 bancs mémoire par l'intermédiaire d'un réseau Crossbar . Un PE regroupe deux pipelines spécialisés : l'un sur les instructions , le second sur les données ; chacun est constitué d'unités fonctionnelles pipelinées . Un précompilateur , orienté vers des langages de haut niveau , prend en compte le jeu d'instructions des PE et, facilite l'exploitation du parallélisme .

Le S-l est autonome , multiprogrammé et peut débiter jusqu'à 400 Mflops dans des conditions idéales .

\* HEP Denelcor E201 , est un système multiprocesseur modulaire allant jusqu'a 16 PE . Sur chacun d'entre eux coexistent un certain nombre de séquences de code indépendantes ou coopérantes appelés processus . L'interprétation de ces processus est effectuée de façon pipeline . Un Fortran étendu prend en compte les principes d'exécution , liés à la notion de processus .

Ce système est autonome , multiprogrammé , dont les performances avoisinent les 160 Mflops .

\* SPRINT -System Control [6] , est un réseau d'array processeurs API 20 ,extensible jusqu'à 8 .

Le langage Fortran est muni de six commandes qui servent , à transférer des données et à implémenter diverses opérations arithmétiques sur des matrices , vecteurs et sous-ensembles de matrices . Le système est prévu pour un fonctionnement multi (ou mono) utilisateur .

# I.2.3. Architecture MIMD , approche Data -Flow .

Le principe du Data Flow est basé sur la disponibilité des données ; une instruction est déclarée exécutable dès que ses données d'entrée sont calculées . La notion de compteur

ordinal perd son sens . Des mécanismes d'interprétation totalement nouveaux font alors apparaître des architectures multiprocesseurs originales .

# I.2.3.a. Le Data Flow pur

Un graphe data flow permet de représenter un programme .

Deux types de noeuds apparaissent : les chainages et les acteurs

Des "pions" , véhiculés par les arcs du graphe , transportent

les valeurs d'un acteur à un autre . Selon cette structure ,

l'exécution d'un programme est décrite par une séquence de

flashs . Chaque flash se traduit par la mise en opérations de

noeuds activés par l'affectation de valeur à leurs pions

d'entrée . Ce type de machine est étudié au MIT , à

l'Universite de Californie et à Irvine , entre autres .

# 1.2.3.b. Le Data Flow à assignation unique .

Une contrainte logicielle est ajoutée au cadencement par les données . En effet , toute variable ne peut recevoir qu'une valeur au plus durant l'exécution d'un programme . Nous citons pour exemple la machine LAU C21,353 CERT-DERI , qui a permis de démontrer la faisabilité d'une machine data flow , programmée dans un langage évolué , expriment de façon naturelle le parallèlisme d'exécution MIMD .

# II. LES RESEAUX D'INTERCONNEXION .

Le choix d'une structure d'interconnexion adéquate est délicat , d'autant que le nombre de processeurs est élevé .

Si le système contient N processeurs et , que nous choisissons un réseau où chaque processeur est relié aux autres alors , le nombre de connexions est égal à  $E \times N \times (N-1)$  ] , égal environ à  $(N \times N)$ ; le réseau est irréalisable pour une valeur élevée de N .

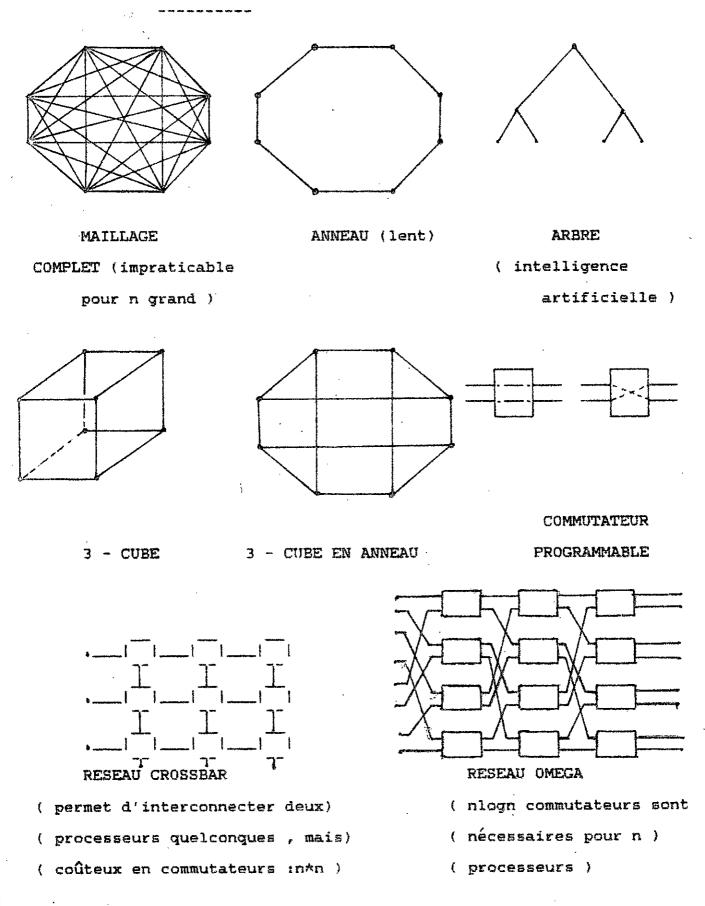

Il existe des schémas d'interconnexion plus économiques (Fig.I.3) .

# II.1. Réseaux d'interconnexion statiques .

Un schéma d'interconnexion sous forme d'anneau a l'avantage de ne nécessiter que deux connexions par processeur quelquesoit le nombre N de processeurs. Mais un message devra traverser en moyenne, N/2 processeurs avant d'atteindre son destinataire, ce qui nécessite trop de temps, pour N grand.

La structure en arbre est utilisée dans beaucoup d'architectures prototypes : chaque processeur peut communiquer avec trois autres ; les processeurs placés dans le bas de l'arbre ("feuilles") ne communiquent pas facilement entre eux .

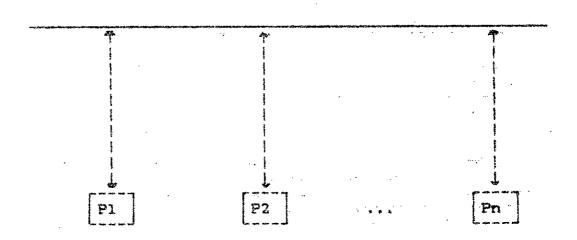

Les processeurs peuvent être connectés en parallèle (à travers des portes d'accès), sur un groupe de lignes omnibus appelé Bus, à travers lequel îls communiquent (Fig.I.4.a). On suppose qu'il existe un mécanisme de contrôle des accès au bus, ou chemin partagé.

Les processeurs peuvent être aussi , connectés en matrice . Le nombre de chemins est réduit , mais le nombre de connexions croît avec N\*N .

#### FIGURE 1.3. RESEAUX D'INTERCONNEXION .

FIGURE 1.4. STRUCTURES A COMMUNICATION DIRECTE RESSOURCE PARTAGEE, AUTOCONTROLE.

b. Matrice .

a. Bus à accès parallèle .

Une structure très prometteuse est l'hypercube . Elle est constituée d'un cube dans un espace de dimension quelconque. En dimension trois , l'hypercube est le cube de la géométrie classique . Chaque processeur est alors relié à trois autres processeurs et , se trouve à une distance maximale de trois connexions de tout autre processeur. Cette structure peut être généralisée dans un espace de dimension k et portera le nom de k-cube binaire : le cube contient (2) sommets et , chacun (ou processeur) est relié à ses k voisins immédiats soit, à un voisin par dimension du réseau . Cette structure a été retenue par les chercheurs du CALTECH (California Institute of Technologie) . Elle a été conçue et réalisée en 1983 sous le nom d'ISPC/d6 et commercialisée en Fevrier 1985 par INTEL . C'est une machine du type MIMD composée de 32 , 64 ou 128 microprocesseurs (80286 d'INTEL) connectés comme un 6-cube binaire . Son rapport

# II.2. Réseaux d'interconnexion reconfigurables .

supérieur à 0,8 , ce qui est bien accepté .

performance / coût est très intéressant . Le taux réel

d'utilisation des processeurs ( ou rendement ) est souvent

Les processeurs sont reliés par l'intermédiaire de commutateurs programmés . Dans les architectures comportant des milliers de processeurs , le réseau reconfigurable ( dynamique ) ne sera pas utilisé -car coûteux - malgré sa grande souplesse .

Par contre , dans les architectures SIMD , des commutateurs seront utilisés entre processeurs et entre processeurs et mémoire . Le réseau est alors reconfiguré par programme entre chaque instruction et, les communications sont synchrones.

Le BSF (Burroughs Scientific Processor) devait posséder 512 processeurs connectés dynamiquement à 521 modules de mémoire (cette machine n'a pas été commercialisée pour des raisons financières) [5].

CEDAR est une machine de l'Université de l'Illinois [5]

(projet) qui possède deux niveaux d'interconnexion . Les

processeurs sont organisés en groupes , eux-mêmes ,

interconnectés par un réseau reconfigurable .

# III. QUELQUES EXEMPLES DE CALCULATEURS SPECIALISES .

Le traitement numérique d'images est une technique dont l'importance ne cesse de croître. De nombreux secteurs de pointe y font appel : en médecine ( scanner ) , robotique , photos transmises par satellite pour la météorologie , la recherche minière , l'archéologie ou l'agriculture .

Ces images sont loin de pouvoir être exploitées en totalité .

Ces applications nécessitent une masse considérable de calculs, souvents répétitifs, sur des images numérisées. La qualité d'une image est obtenue à l'aide de plusieurs millions de points; la contrainte temps réel associée à la qualité d'une image, conduit à des architectures de type parallèle.

Pour effectuer des calculs sur une image , celle-ci est codée en un tableau de nombres qui représentent l'intensité lumineuse en chaque point de l'image , appelé pixel . En associant à chaque pixel , un processeur relié à ses voisins immédiats , une architecture parallèle très régulière adaptée aux calculs locaux entre un point et ses voisins , est obtenue.

Nous citons quelques exemples de calculateurs spécia--lisés .

Dans le traitement d'images :

\* STARAN [18,38] est un calculateur à mémoire associative. Il est constitué d'un certain nombre de mémoires ( au plus 32 ).

Un PE est prèvu pour chaque mot. Les opérations d'entrée-sortie sont prises en charge par l'hôte. STARAN n'est programmable qu'en langage assembleur, appelé APPLE. Il est capable de débiter à 200 Mflops.

\* MPP [18] a été conçu pour la NASA . Il est constitué de 16384 processeurs connectés en matrice 128 x 128 . Ils ont une architecture SIMD .Cette machine utilise le parallélisme image . Une mémoire peut échanger jusqu'à 320 M octets / s avec la matrice de PE , soit l'équivalent de 320 images de 1024 sur 1024 points . Un processeur de contrôle commande les PE et exécute les instructions scalaires . Les PE exécutent les instructions vectorielles ( les processeurs sont regroupés par huit sur un même circuit intégré ) . Chaque processeur a une mémoire de lKbits contenant les données image et , relié à ses plus proches voisins E , O ,N , S sous le contrôle du programme . Les colonnes de gauche et de droite peuvent être connectés en cylindre , ainsi que la première et la dernière ligne . Les performances sont de 6553 M d'additions / s sur des entiers et 216 M d'opérations / s pour une multiplication flottante sur 32 bits . Le cycle de base est de 100 ns permettant les

entrées-sorties à cette vitesse .

\* CYTOCOMPUTER [18,38] est constitué de deux séries parallèles de processeurs connectés en pipeline . Les processeurs sont synchrones et suivent une architecture MIMD . La première série est constituée de 88 processeurs connectés en pipeline pour traiter les images binaires , alors que la deuxième série contient 25 processeurs connectés en pipeline travaillant en parallèle par rapport à la première série pour les images multiniveaux de gris . La vitesse de calcul est de 1,6 M octets / s .

\* CLIP IV [18] est une machine bâtie autour d'une matrice 96 x 96 processeurs booléens . Une fenêtre correspondant à une trame de 96 x 96 x 6 bits peut être mémorisée dans six registres à décalage ( l par plan bit ) . Le plan bit est converti en une matrice binaire 96 x 96 pouvant être transférée dans la mémoire correspondante au tableau matriciel . Une instruction de contrôle commune , est envoyée à tous les processeurs qui sont parfaitement synchronisés . CLIP est performant pour les opérations logiques portant sur une fenêtre 3 x 3 ; l'opération dilatation / rétraction est réalisée en un cycle ( 10 microsecondes ) . Une convolution 3 x 3 exige par contre ,

\* PASM [18,38] est une machine parallèle qui peut être structurée en une ou plusieurs machines SIMD et/ou MIMD indépendantes. C'est un système reconfigurable, pour exploiter au mieux les parallélismes inhérents au traitement d'images et à la reconnaissance des formes.

En traitement du signal ( télécommunications ,..):

un algorithme de traitement du signal consiste à répéter un

même calcul , souvent complexe , sur une suite de données .

Cela est le cas , pour une représentation codée de la parole ,

d'images à transmettre ou encore d'une série de mesures

effectuées sur un système physique ou biologique que l'on

cherche à observer . Dans ce cas , il ne s'agit plus d'associer

un processeur par point de mesure puisqu'il y en a souvent une

infinité . Par contre , les données doivent circuler au rythme

où elles arrivent . C'est ainsi qu'est né le concept

d'architecture systolique .

Les algorithmes de la reconnaissance de la parole sont très coûteux en temps de calcul , mais leur régularité permet une mise en oeuvre systolique . Plusieurs étapes caractérisent la reconnaissance de la parole : reconnaissance de phonèmes puis de mots et enfin de la phrase :

\* API 89 E53 de l'IRISA de Rennes , est constitué de 89 PE . Un processeur est associé à chaque point d'une grille dont les colonnes correspondent aux phonèmes du mot recherché . Cette machine permet de reconnaître 2000 mots en temps réel ( 1000 fois plus rapide que sur un miniordinateur du commerce ) .

\* WARP E5] , en construction à l'université Carnegie Mellon ,a une architecture systolique linéaire programmable. Elle permet le calcul des principaux algorithmes de traitement du signal ( transformée de Fourier rapide , convolution , filtrage ...) . Elle peut atteindre une puissance de 10 M instructions/s avec 10 processeurs seulement .

Les recherches liées aux processus parallèles concerneront bientôt tout le champ de recherches en informatique .

Des architectures multiprocesseurs , massivement parallèles , permettent d'obtenir , grâce à l'avènement de microprocesseurs très performants , un rapport performance - coût très intéressant . Ce ratio ira en croissant avec la technologie WSI ( Wafer Scale Integration ) , qui intègre plusieurs processeurs sur une puce .

### - CHAPITRE II -

# STRUCTURE MATERIELLE DES SYSTEMES MULTIMICROPROCESSEURS

La demande sans cesse croissante de performances de calcul a abouti , à la conception de calculateurs à archi-tecture multiprocesseur .

L'avènement des microprocesseurs bon marché et performants ( 16 bits voire 32 bits ) a encouragé cet engouement et, permet de penser en termes d'architectures massivement parallèles comportant un nombre très important de processeurs d'une puissance égale à celle d'un petit microordinateur .

Ce qui importe , à présent , est l'organisation et la façon dont les processeurs échangent l'information .

En effet , pour que deux processeurs puissent communi--quer , une synchronisation s'impose . Et , cecí nécessite du temps .

D'autre part , la communication s'effectue à travers un support de communication physique qui pourrait être plus coûteux que les processeurs eux-mêmes si l'on n'y prend pas garde .

- I. STRUCTURES MATERIELLES DES MULTIMICROPROCESSEURS .

- I.1. Structure logique .

Il existe deux relations logiques :

#### I.1.1. L'organisation verticale

Dans sa forme simple , une organisation verticale a un seul maître et plusieurs esclaves . Elle présente les caractéristiques suivantes :

- les éléments ne sont pas tous semblables .

- à un instant donné , seul un élément joue le rôle du maître ; cependant , plusieurs éléments peuvent avoir la potentialité de le devenir .

- toutes les communications doivent passer à travers le maître ou être initialisées par le maître .

- le hardware des esclaves peut être identique et , chacun peut être spécialisé dans une tâche par le software . On peut rencontrer une configuration maître-esclave pyramidale .

- I.1.2. L'organisation horizontale requiert plus de coordination . Elle a les caractéristiques suivantes :

- tous les éléments sont logiquement équivalents .

- chaque élement est susceptible d'être maître .

- tous les éléments peuvent communiquer entre eux .

En général , l'organisation horizontale est plus flexible que la première . Cependant , elle n'est pas plus efficace pour des applications ayant des tâches très différentes .

#### I.2. Structure physique Cll .

Cela concerne la méthode d'échange d'information . Elle est fonction de l'organisation de la communication inter-processeurs et de la topologie d'interconnexions .

## I.2.1. Organisation des communications .

#### I.2.1.1. Mode de communication .

Les communications entre les processeurs peuventêtre directes ( Fig.II.1 ) ou indirectes .

$$\begin{bmatrix} P(i-1) & -- & P(i) \end{bmatrix} --- \begin{bmatrix} \dot{P}(i+1) \end{bmatrix} ---$$

FIGURE II.1. Communication directe.

La communication de P(i-1) à P(i+1) est directe si P(i) n'est pas un organe de contrôle .

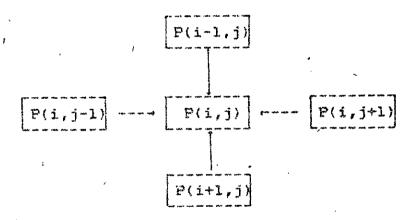

Sinon , nous avons un processeur P(i,j) qui doit décider du routage des messages ; il joue le rôle d'organe de contrôle et nous avons le schéma de la figure II.2 .

## FIGURE II.2. Communication indirecte

## 1.2.1.2. Contrôle de la communication (indirecte):

Si le routage des messages est assuré par un seul organe de décision , le contrôle est dit centralisé . Dans le cas contraire , il est décentralisé ou alors nous avons un mécanisme d'autocontrôle .

## I.2.1.3. Chemins de communication [1]:

Un chemin de communication est de type partagé s'il comporte plus de deux points d'accès . Sinon , il est réservé ou privé .

### . I.2.1.4. Ressources partagées :

Les transferts de données entre processeurs peuvent être échangés :

- soit à travers une structure mémoire commune dite centralisée sans accès direct en mémoire commune .

- soit à travers une structure de bus dite distribuée où un lien logique est établi pour créer un chemin de communication entre les éléments .

Dans les systèmes où les transferts sont fréquents et importants , les organisations précédentes ne sont pas efficaces car les conflits d'accès augmentent pour la ressource partagée . Ce problème est plutôt aggravé dans les systèmes à microprocesseurs par le goulot d'étranglement mémoire - processeur , et par la limitation des capacités d'entrée - sortie .

## I.2.2. Topologie d'interconnexion .

Les quatre schémas de base sont :

- Bus Commun .

- Etoile .

- Anneau .

- Pleine connexion .

D'autres topologies sont des combinaisons de base ou des variations des quatre schémas précédents ( voir Chap.I ).

### I.3. Mode d'interaction

Malgré les innombrables schémas d'interconnexion existants , les systèmes peuvent être classés selon le degré de couplage et la nature de l'intercommunication entre processeurs .

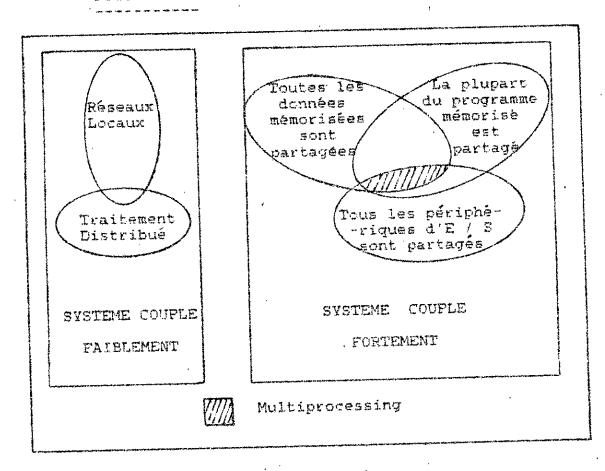

Le couplage se refère à la capacité de partager des ressources communes , avec deux possibilités extrêmes : les systèmes couples faiblement et , les systèmes fortement couplés ( Fig II.3' ) .

## I.3.1. Les systèmes faiblement couplés ou Réseaux [3]

Ils sont caractérisés par deux calculateurs ou plus, dispersés géographiquement. Les différents calculateurs du système sont interconnectés à travers une interface de communication . La communication intercalculateurs suit un protocole rigide .

Chaque calculateur fait son traitement indépendamment des autres . Il a son propre programme et ses données stockées dans sa mémoire , mais il est relié aux autres par les entrées-sorties de données , le contrôle , la communication et / ou l'utilisation commune des périphériques .

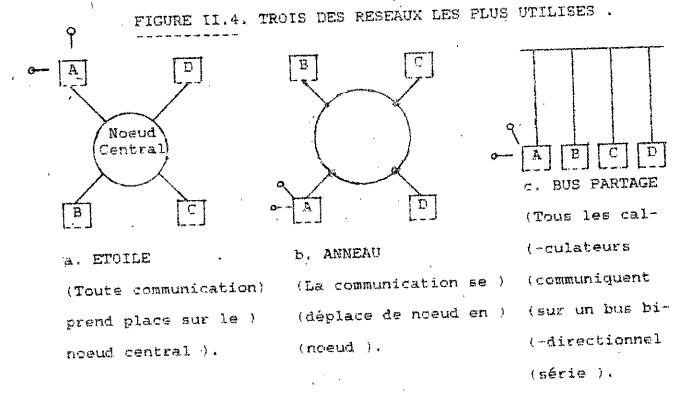

Les structures de réseau les plus communément utilisées sont en :

- étoile .

- anneau .

- bus partagé .

La figure II.4 nous les schématise .

FIGURE II.3. SYSTEMES MULTIPROCESSEURS

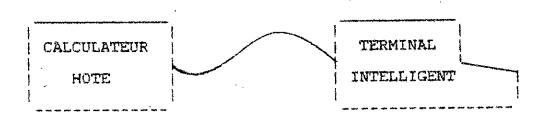

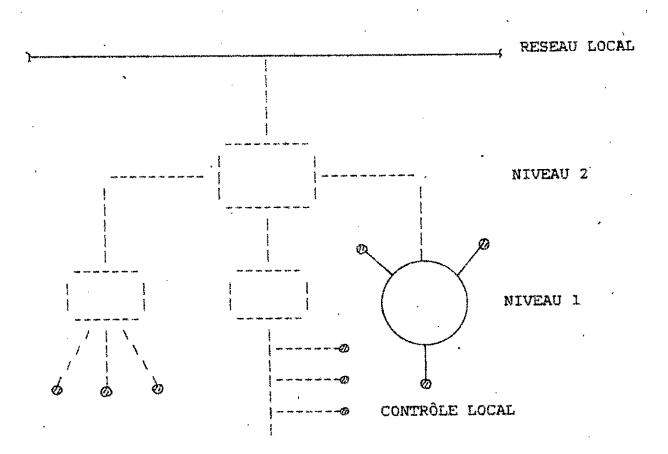

Un réseau faiblement couplé utilise, de façon typique, des chaînages de données série. Cela peut être aussi simple que la Figure II.5.a ou très complexe, comme dans les environ-nements de contrôle industriel. Ceux-ci sont constitués de plusieurs niveaux avec plusieurs types de réseaux (Fig.II.5.b).

L'information circule entre les processeurs sous la forme de paquets de données qui incluent de facon typique l'information concernant la source et la destination de la donnée.

Les systèmes de faible couplage proposent des processeurs dispersés ou distribués , par lesquels le traitement est réalisé et ceci de facon concurrente et asynchrone , tout en ayant des processeurs coopératifs .

Chaque site de calcul a ses propres processeurs ,

mémoire , ressources locales , système d'exploitation et

chemins de communication . Cette structure peut résoudre

certains problèmes ; si un noeud tombe en panne , les autres

processeurs continuent à travailler et peuvent même ,

disgnostiquer le problème au noeud défaillant .

Le réseau le plus important , existe aux USA avec "The Advanced

Research Projects Agency Network " qui connecte environ 50

noeuds à travers les USA .

Les organisations des réseaux de calculateurs ont une communica-

Les organisations des réseaux de calculateurs ont une communication interprocesseurs rigide et des noeuds de traitement extensible, ce qui n'est directement pas applicable aux systèmes à microprocesseurs. Cependant avec l'évolution technologique des microprocesseurs, des versions modifiées des réseaux de calculateurs seront bientôt utilisées.

#### FIGURE 11.5. RESEAU FAIBLEMENT COUPLE

a. Interfaçage entre un terminal intelligent 'et un calculateur hôte .

b. Systèmes de contrôle industriel à noeuds multiples . La circulation série des données , dans les systèmes faiblement couplés , pose des problèmes . En effet , si la chaîne série de données est encombrée , le temps de réponse et l'utilisation de la base de données pourraient baisser considérablement . Ce qui peut être un handicap sérieux dans les applications temps réel . Un système fortement couplé est alors plus approprié .

# I.3.2. Les systèmes fortement couplés .

Ils sont connus également comme systèmes multi-microprocesseurs fortement couplés E31 . Ils contiennent deux ou plusieurs processeurs avec :

- une mémoire commune ( principale ) qui est partagée entre tous les processeurs du système ainsi que la possibilité de posséder une mémoire locale .

- un système d'exploitation commun qui contrôle et coordonne toute interaction entre processeurs et processus .

- des ressources partagées : des facilités d'entrées-sorties et d'autres ressources du système sont généralement partagées entre les processeurs . Cependent , quelques ressources peuvent être attribuées à des processeurs spécifiques .

- la même puissance de calcul : les processeurs sont configurés de facon symétrique et exhibent des capacités similaires .

- le partage de la charge (load sharing) est dynamique E17,31.

La distribution dynamique de la charge d'un processeur saturé

est uniforme à travers tous les processeurs :

- \* autonomie de processeurs : chacun des processeurs ( coopératifs entre eux ) peut exécuter des traitements significatifs individuellement .

- \* synchronisation : elle est nécessaire pour des processeurs qui coopèrent .

La plus grande limitation d'une organisation multi-processeur fortement couplée est l'existence des conflits

d'accès en mémoire commune. Cette restriction tend à

limiter le nombre de processeurs qui peuvent effectivement

être supportés par le système d'exploitation.

La plupart des réseaux de connexion processeur - mémoire tendent à réduire ces conflits d'accès en mémoire commune .

Les trois types d'organisation processeur - mémoire les plus fondamentales sont :

- le Bus Commun , où tous les éléments sont connectés à un seul bus .

- le Crossbar Switch , où les éléments sont connectés à un module distinct appelé le " Grossbar Switch " qui peut fournir plusieurs connexions simultanées entre éléments.

- la mémoire multiport , où chaque élément de mémoire a plus d'un port d'accès , est connectée aux autres éléments à travers un système multibus .

Grâce à l'organisation multimicroprocesseur , plusieurs processeurs lents font le travail d'un processeur très rapide . Cependant , le goulot d'étranglement processeur-mémoire , caractéristique des microprocesseurs , limite son application

aux organisations multiprocesseurs .

Des systèmes multiprocesseurs utilisant des micro-processeurs peuvent être implémentés dans des cas spéciaux

ou un grand nombre de processus similaires , relativement

indépendants , échangent des faibles quantités de

données .

## I.3.3. Les systèmes distribués à microprocesseurs [2] .

Des structures qui combinent au mieux chacune des deux représentations précédentes ( couplages faible et fort ) sont plus appropriées aux systèmes à microprocesseurs. Ces structures multimicroprocesseurs modérément couplés s'appellent les DIMSs ( Distributed Intelligence Microcomputer Systems ) . Dans un système distribué à microprocesseurs , la charge de travail est partitionnée en tâches relativement indépendantes pour être assignées aux divers éléments du système . Un tel système a les principales caractéristiques suivantes :

- les éléments sont autonomes : chaque élément est constitué en genéral d'un CPU , d'un programme propre , d'une mémoire de données et peut utiliser ou contrôler des périphériques additionnels .

- les processeurs sont spécifiques à une tâche. Théoriquement, chaque élément est dédié à une tâche spécifique qui détermine sa relative complexité.

- les processeurs sont de complexité différente. La configuration du système n'est pas nécessairement symétrique puisque les éléments ne sont pas de même complexité.

- il y a une optimisation hardware et software à effectuer .

En effet , chaque élément a un hardware et un software étudiés en fonction de la tâche spécifique qu'il doit réaliser.

il y a communication de données : la communication

- interprocesseurs se fait souvent au niveau des données .

Cependant , dans certaines situations , ces dernières peuvent contenir des commandes .

- processeurs de contrôle et de communication : en général, chaque élément peut gérer le contrôle des entrées-sorties et la communication du système . Dans le cas où la communication est beaucoup plus importante , une des fonctions précédentes peut être attribuée à un autre processeur .

- le partage de la charge ( load sharing ) est statique .

Comme les processeurs sont specifiques ( à une tâche ) , un système minimal ne peut supporter un partitionnement dynamique; ainsi la répartition des tâches ( load balancing ) doit être faite durant la phase de conception . Cependant , des unités additionnelles peuvent être introduites pour faire une fraction du partage du chargement [2,17] .

### I.4. Mode de traitement

La classification de Flynn considère l'exécution au niveau seulement de l'instruction . Ceci est trop restrictif

Danc sa forme la plus générale , un système multi-processeurs capable d'exécuter de facon concurrente un nombre donné de tâches , chacune utilisant des groupes différents de données , peut être appelé MTMD (Multiple Task , Multiple Data).

Nous pouvons établir une classification arborescente pour les multiprocesseurs (Fig II.6).

## II. EVALUATION DES PERFORMANCES .

## II.1. Capacité de traitement du système .

### II.1.1. Coût - Performance .

Compte tenu de l'évolution technologique des microprocesseurs , il est intéressant sur le plan économique , d'en utiliser plusieurs pour augmenter les performances du système .

Néanmoins , et sans considérer les coûts du logiciel de haut niveau , les coûts des différents éléments tels les périphèriques et les connecteurs ne décroissent pas aussi rapidement que ceux des microprocesseurs et des mémoires .

Ainsi , la réduction du rapport coût - performance risque d'être annulée par les autres coûts du système .

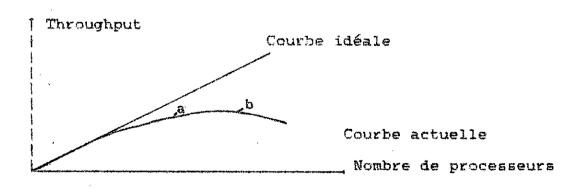

### II.1.2. Throughput [2,17,27] .

Le "throughput" d'un système, défini comme étant

l'inverse du temps nécessaire pour exécuter un groupe donné

d'algorithmes, est un indicateur approprié de la performance

du système. Il est mesuré en nombre d'opérations par unité

de temps.

Théoriquement , le "throughput" augmente avec le nombre de processeurs supplémentaires au système multiprocesseur .

## FIGURE II.6. CLASSIFICATION ARBORESCENTE DES MULTIPROCESSEURS .

### PIGURE II.7. EFFET DE SATURATION .

- a) Dénivellement

- b) Déclin

En pratique , nous avons la courbe actuelle de la Figure II.7 , à cause de la saturation .

Le "throughput" sature à partir d'un nombre incrémental de processeurs ajoutés. Cet effet peut être attribué aux conflits d'accès des ressources partagées, qui augmentent avec le nombre de processeurs.

Les points de dénivellement (levelling off) et de déclin (decay) , peuvent être différents pour des architectures multiprocesseurs différentes .

Théoriquement , le souhait est de travailler sur la partie linéaire de la courbe ; celle-ci peut être étendue en réduisant les conflits d'accès et les communications inter-processeurs . Ce résultat peut être obtenu , en partitionnant le travail principal en petites tâches indépendantes avec une intercommunication minimale .

## II.1.3. Ressource partagée .

Cela peut être aussi bien une imprimante , une carte mémoire ou alors un processeur arithmétique à haute vitesse .

Le temps partagé de la ressource s'effectue de façon à éviter la surcharge de la ressource et les conflits d'accès .

Des sémaphores peuvent être utilisés ( à l'aide de système d'exploitation ) comme mécanisme de blocage pour protéger la donnée dans la mémoire partagée .

## II.2. Partage des données communes

Pour éviter la transmission de données volumineuses

d'un processeur à un autre ( ou plusieurs autres ) , on stocke ces données dans une mémoire commune . Ces conflits d'accès à cette mémoire ralentissent le système .

On peut regrouper les circuits d'accès aux mémoires communes en classes suivantes :

## II.2.1. Accès par ligne omnibus .

Les processeurs accèdent à la mémoire commune à travers une ligne omnibus sur laquelle ils sont connectés en parallele. Il peut exister un arbitre pour régler les conflits d'accès. On peut avoir , également , un système d'autoarbitrage . La bande passante du bus limite la fréquence des accès à la mémoire d'un processeur . Cette bande passante doit croître avec le nombre de processeurs pour leur permettre un rythme de travail constant .

L'avantage de cette connexion est sa simplicité matérielle et logicielle .

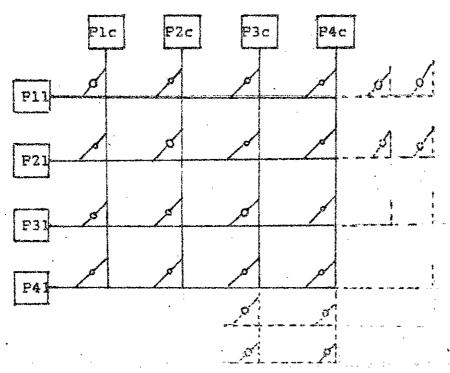

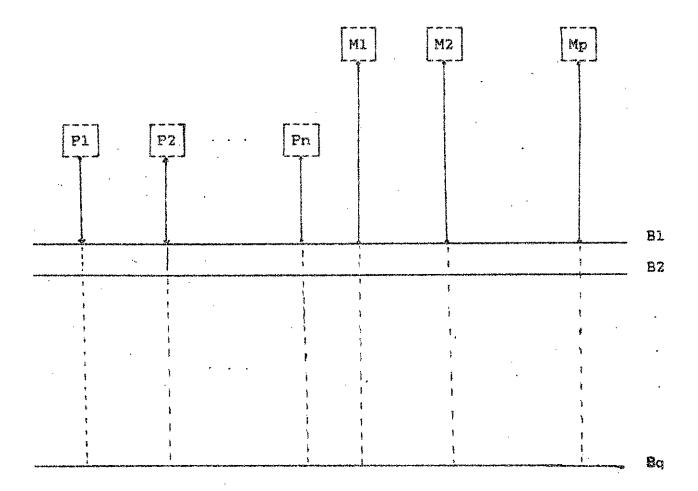

## II.2.2. Accès par réseau de sélection matricielle [1].

La mémoire est fractionnée en bancs M1,M2,...,Mp

bien que fonctionnellement elle puisse être toujours considérée

comme un espace continûment adressable. Les processeurs

P1,P2,...,Pn et les bancs de mémoire sont interconnectés, à

travers une matrice de connexion; p parmi les n processeurs

peuvent accéder simultanément aux p bancs mémoire. Par contre,

la logique d'aiguillage et d'arbitrage devient très compliquée

dès que p et n deviennent grands.

#### TT.3.3. Multibus .

C'est une solution intermédiaire par rapport aux deux précédentes . Elle fait le compromis coût - performance ; q parmi les n processeurs peuvent accéder simultanément à q parmi p bancs de mémoire à travers les q bus ( Fig. II.8 ) .

### II.2.4. Mémoire multiaccès .

Chacun des bancs mémoire comporte n circuits d'accès auxquels sont reliés les n processeurs . Une logique de priorité câblée permet de hiérarchiser les demandes d'accès simultanées .

## II.3. Délai de transmission des messages.

Est fonction de :

\* La distance interprocesseur "d": elle est mesurée , par

exemple , en nombre de noeuds de commutation que doit traverser

un message du processeur source au processeur destinataire .

Pour un réseau à interconnexion 2 à 2 , d=0 .

Pour un réseau à interconnexion matricielle , d=1 .

Pour un n-cube , 'd' est au maximum égale à n .

Pour un anneau , tout message doit faire le tour de l'anneau pour des besoins de synchronisation du système . Pour un réseau à accés total , comportant N processeurs , Benes a montré qu'il fallait au moins ( N & log N ) points de commutation , "d" valant environ Log N .

FIGURE II.8. LE MULTIBUS

\* temps de séjour dans les files d'attente .

En cas de demandes simultanées d'accès à un même chemin , il se forme une file d'attente .

Le temps d'attente moyen [1] est donné par :

$$E(A) = 1 / (I(B) - \overline{N} * Im)$$

Im : nombre moyen d'informations qu'un processeur demande à transmettre , quand il se présente au bus .

$\overline{N}$  : nombre moyen de processeurs utilisateurs de bus à un moment donné .

I(B) : nombre d'informations que le bus peut acheminer par unité de temps .

Si le nombre de processeurs augmente , pour un temps d'attente constant , I(B) devra augmenter proportionnellement à  $\overline{N}$  . La structure à bus unique est vite limitée par la bande passante de celui-ci .

### III. AMELIORATION DES PERFORMANCES .

Le problème de concurrence et de conflit peut être traité indépendamment de la structure physique, en utilisant les concepts de tâche, d'évènement et de communication comme équivalents logiques de structures physiques.

Four obtenir une opération harmonieuse, le système doit être capable de suivre les aspects de contrôle : arbitrage, allocation et coordination .

#### III.l. Arbitrage .

Les conflits d'accès au bus des processeurs peuvent être résolus de diverses façons ; nous ne citerons que les disposi-tifs simples d'allocation de bus (ou arbitres) .

Un arbitre de bus permet une transparence au niveau logiciel ; chaque processeur ignore les autres processeurs ; il affiche des adresses et si le bus n'est pas libre , le déroulement de l'instruction en cours est bloqué jusqu'à ce que le bus lui soit alloué .

Le débit de communication varie avec le nombre de processeurs utilisés, de leur débit de requêtes et du débit des mémoires ou interfaces au bus. Le débit de communication peut être bon si les élements précédents sont correctement équilibrés.

Deux types d'arbitre peuvent se concevoir :

- arbitres synchrones par multiplexage temporel [9] : le temps

est divisé en tranches dont la durée est égale au temps d'accès

élémentaire au bus . Chaque tranche est allouée à un même

processeur avec une périodicité égale au nombre de processeurs .

Cette méthode est simple et peu coûteuse . De plus , dans le

cas où les processeurs ont des cycles de lecture / écriture

périodiques et où l'on peut faire coincider les deux périodes ;

des performances très élevées seront obtenues .

Lorsque le nombre de processeurs croît , les performances

- arbitres asynchrones [9] : l'arbitre reçoit les requêtes des processeurs et alloue le bus à un processeur en fonction de celles-ci .

Plusieurs types d'arbitre :

chutent .

- \* priorité tournante : efficace et peu coûteuse .

- \* priorité fixe : se justifie lorsque les temps d'accès des processeurs sont très différenciés .

\* file d'attente : est optimale car minimise l'espérance du temps de chaque processeur .

Les arbitres asynchrones sont plus performants et plus coûteux que le multiplexage temporel .

( Dans le système Multimu , la gestion des priorités s'effectue par software . Nous n'utiliserons pas d'arbitre de bus propre--ment dit ) .

## III.2. Allocation de tâches .

Nous avons vu dans le paragraphe II.1.2 que , le "throughput" décroit à partir d'un certain nombre incrémental de processeurs ajoutés . Ceci peut se produire à partir de 3 ou 4 processeurs si le système est improprement désigné . Cette décroissance est due à la communication interprocesseurs (IPC) excessive .

L'allocation de tâches est le procédé d'attribution de modules aux processeurs avec un IFC minimal [2,17] .

Le partitionnement des tâches se refère au découpage d'une tâche en plusieurs modules individuels avec une communication intermodule (IMC) minimale.

Le partitionnement des tâches et l'allocation des tâches sont deux étapes nécessaires pour minimiser l'IPC .

Il est commode de considérer un module comme une entité indivisible , la plus petite unité d'opération viable . Une tâche est une simple entité de traitement .

Le procédé du partitionnement des tâches sera réalisé par la partie software et chaque tâche arrivera dans le système de traitement distribué , déjà partitionnée en groupes de modules . Le partitionnement des tâches est un problème important dans les systèmes de traitement distribué et , il est loin d'être résolu .

Des méthodes sont développées pour accomplir l'allo--cation de tâches et minimiser le coût total du traitement . Ces méthodes peuvent être statiques ou dynamiques .

## III.3. Coordination entre les tâches .

Dans un système multiprocesseur, une coordination entre plusieurs tâches concurrentes est nécessaire. Les problèmes de coordination associés aux processeurs concurrents peuvent etre établis en termes de synchronisation, temps mort et exclusion mutuelle.

## III.4. Système d'exploitation (ou executive) .

Tous les aspects de contrôle cités ci-dessus sont du ressort d'un système d'exploitation . L'implémentation d'un multimicrocalculateur effectif est très influencée par la conception propre de son "executive" . Celui-ci utilisera quelques concepts deja utilisés dans les systèmes d'exploitation temps réel pour des systèmes monoprocesseurs .

Il est donc intéressant d'implémenter des systèmes multimicroprocesseurs lorsqu'il s'agira par exemple :

- d'élaborer des applications de contrôle de processus ayant des traitements diversifiés et des contraintes temps réel . Pour

la plupart de ces applications , les traitements volumineux excèdent de loin les capacités d'un système monoprocesseur .

- des applications qui nécessitent une bonne fiabilité mais, à cause des contraintes économique et / ou d'espace , ne peuvent supporter une redondance massive .

- des applications avec un traitement d'E/S extensif .

La nécessite d'interfacer avec des processus d'E/S variés impose généralement un contrôle inacceptable sur un système monoprocesseur et cause une dégradation sévère de la souplesse du système.

Par contre , il sera déconseillé d'utiliser un système multimicroprocesseur dans l'un des deux cas suivants :

\* l'application à traiter nécessite seulement une puissance de calcul plus élevée . Il sera alors plus avantageux d'utiliser un CPU plus puissant ou alors ajouter un ou plusieurs processeurs spécialisés pour certaines tâches £21 .

\* la tâche globale à exécuter ne peut être partitionnée en tâches relativement indépendantes avec des besoins de communication intertâches les plus faibles .

## - CHAPITRE III -

## DESCRIPTION DE LA MACHINE MULTIPROCESSEUR

La possibilité de décomposer le modèle d'un processus physique continu nous a conduit à des sous modèles . Ceux-ci sont tels que leur interaction est minimale .

L'implémentation des algorithmes correspondants aux sous-modèles s'effectue au niveau des unités de traitement ou processeurs secondaires , du système multiprocesseur conçu . Un processeur principal - PP ou maître - et quatre processeurs secondaires - PS ou esclaves - constituent ce système .

La fonction contrôle de la machine est dévolue au PP . Le pas de calcul est à cet effet , émis par l'intermédiaire d'une ligne omnibus PACAL à tous les esclaves et , ceci de façon simultanée . Ainsi , le contrôle est parallèle .

Lorsque les transferts de coefficients et paramètres nécessaires au traitement sont réalisés sur la mémoire locale de chaque PS , l'exécution des tâches s'effectue simultanément sur tous les processeurs secondaires . L'exécution est dite parallèle .

Ainsi le système multiprocesseur conçu est de type MIMD ( multiple instruction , multiple data ) .

Le maître supervise tout échange interprocesseurs au niveau de la mémoire commune via un bus partagé.La logique

de la structure est verticale car , constituée d'un seul maître et de plusieurs esclaves .

Il est nécessaire avant tout , de présenter quelques notions élémentaires utiles à la compréhension de ce chapitre .

## I.DEFINITIONS DES ENTITES INTERVENANTS DANS UN EXECUTIF .

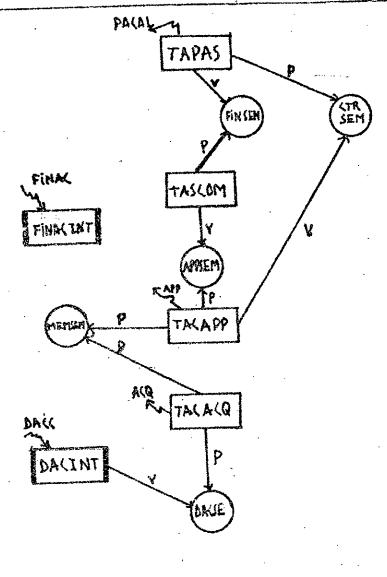

### I.l. La tâche .

C'est un agent actif responsable de l'exécution, par une machine, d'un programme. Elle possède un nom et des attributs ; est caractérisée par :

- un contexte physique comprenant l'ensemble des informations nécessaires à son exécution par un processeur.

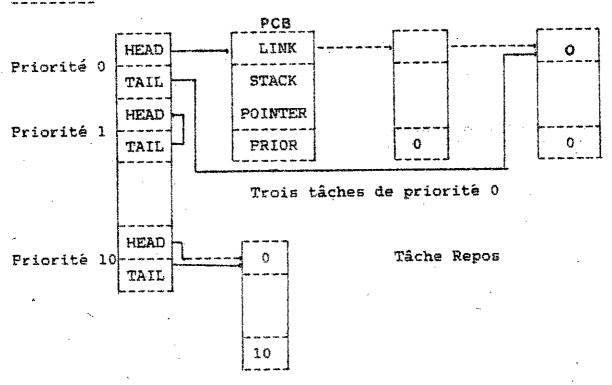

- un descripteur logique qui rassemble les données nécessaires à sa gestion nom , priorité , adresse du S.P , etc...

Dans notre cas , la tâche a deux descripteurs ;

\* un descripteur statique défini dans la configuration du

système et contient les informations statiques de la tâche .

\* un descripteur dynamique appelé PCB ou process control bloc ,

généré par le système d'exploitation à l'initialisation du

système à partir des informations données par le descripteur

statique .

### I.2. Les ordonnanceurs .

On appelle ordonnanceur , un module chargé de gérer un ensemble de processeurs pour le compte d'une famille de tâches.

Cette gestion consiste à attribuer les processeurs , libres ou libérés , aux tâches prêtes à commencer ou à continuer leur exécution et , à reprendre les processeurs affectés à

certaines tâches . Il existe deux types d'ordonnanceur :

- l'ordonnanceur câblé dont l'algorithme de choix est souvent basé sur les priorités associées aux interruptions :

- . il examine séquentiellement les priorités à partir de la plus élevée .

- . sauvegarde le contexte de la tâche immédiate de priorité courante lorsque l'interruption associée à la tâche de priorité p est arrivée et qu'elle n'est pas masquée ; la tâche de priorite p est alors démarrée .

Cet algorithme peut être exécuté par le processeur en tout point d'interruptibilité de la tâche en cours . La fin de l'exécution d'une tâche immédiate , relance la tâche de plus grande priorité prête à être exécutée .

- l'ordonnanceur des tâches différées - ou ordonnanceur programmé - gère les tâches en suivant un algorithme imposé par le type de l'exécutif à réaliser .

## I.3. La gestion des tâches .

Selon l'état où se trouve une tâche , à un instant donné , une des opérations ci-dessous est appelée lorsque le processeur doit décider du sort d'une tâche . Il s'agit de :

- . DEMARRER ( une tâche ) : la tâche passe de l'état

- " hors service " à l'état " en service " .

- . ARRETER ( une tâche ) : la tâche est mise dans l'état

- " hors service " ; pour toute réactivation ultérieure , on utilise l'opération CONTINUER .

- . CONTINUER (une tâche ) : la tâche est mise dans l'état

"en service" après avoir été arrétée .

SE TERMINER : la tâche courante est retirée à son processeur ; elle est mise à l'état " hors service " . Toute réactivation ultérieure nécessite l'opération DEMARRER .

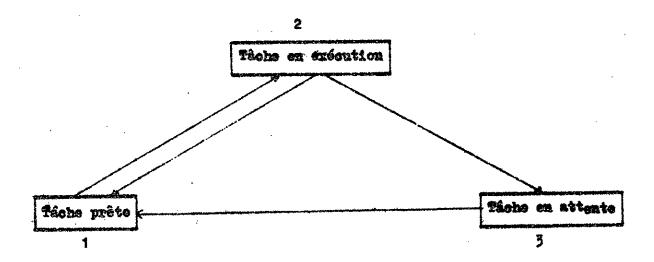

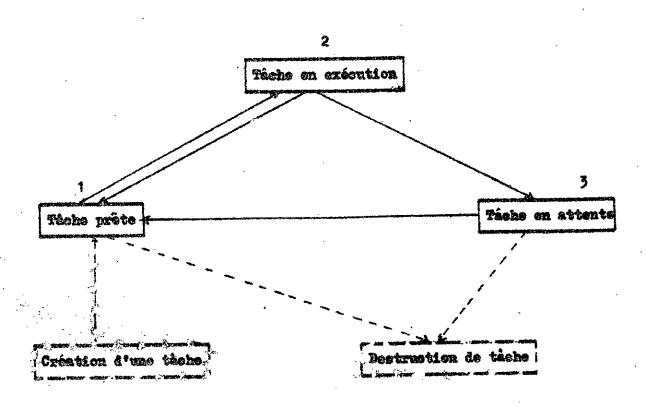

Le module ordonnanceur se charge de faire appel à l'une de ces opérations . La fig.III.l présente l'évolution d'une tâche .

#### I.4. L'évènement .

C'est l'outil de signalisation entre les tâches . On peut soit signaler un évènement , soit attendre un évènement .

Une tâche émettrice peut ,après avoir effectué un traitement tl , signaler un évènement à une tâche réceptrice en attente de cet évènement qui lui permettra de réaliser le traitement t2 . Sur le plan hardware , l'évènement est une interruption câblée .

### I.5. Gestion des régions :

Le parallélisme des tâches induit un phénomène de compétition pour la manipulation des ressources partagées . Un mécanisme d'exclusion mutuelle est nécessaire pour gérer les conflits possibles . Ce mécanisme assure que les exécutions de séquences d'instructions manipulant un même objet partagé soient disjointes dans le temps , indépendamment de l'ordre dans lequel ces séquences sont invoquées . Ces sections sont dites " critiques " .

La région est marquée occupée pendant tout le temps où une tâche est dans une section critique. Ceci est matérialisé par un masquage des interruptions ( avec l'analogie évènement -

#### FIGURE III.1. REATS D'UNE TACKE .

1.a. Table permanente

1.b. Tâcho temperaire

interruption ) . Lorsqu'un évènement est arrivé , le traitement d'interruption qui en découle nécessite l'exécution d'une "section critique" qui implique l'entrée dans une région (masquage des interruptions ) . A la sortie de cette région , on effectuera un démasquage des interruptions (I.T) .

La manipulation des régions se fait par les deux opérations suivantes : ENTRER (dans) et SORTIR (de) la région .

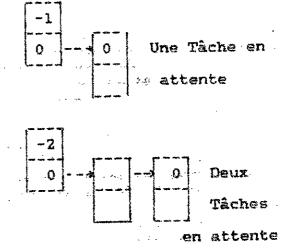

#### I.6. File .

C'est une stratégie de gestion de communication entre tâches. Nous avons la file des tâches en attente, la file des messages etc...

Le noyau gère les files à stratégie FIFO . Les opérations de manipulation des files sont :

- ENVOYER et/ou RETIRER ( élément , file ) .

Le paramètre élément peut aussi bien être une tâche (c'est alors son PCB qui est manipulé ) qu'un message .

## II . ARCHITECTURE DU SYSTEME MULTIPROCESSEUR .

## II.1. Choix de la structure multiprocesseur .

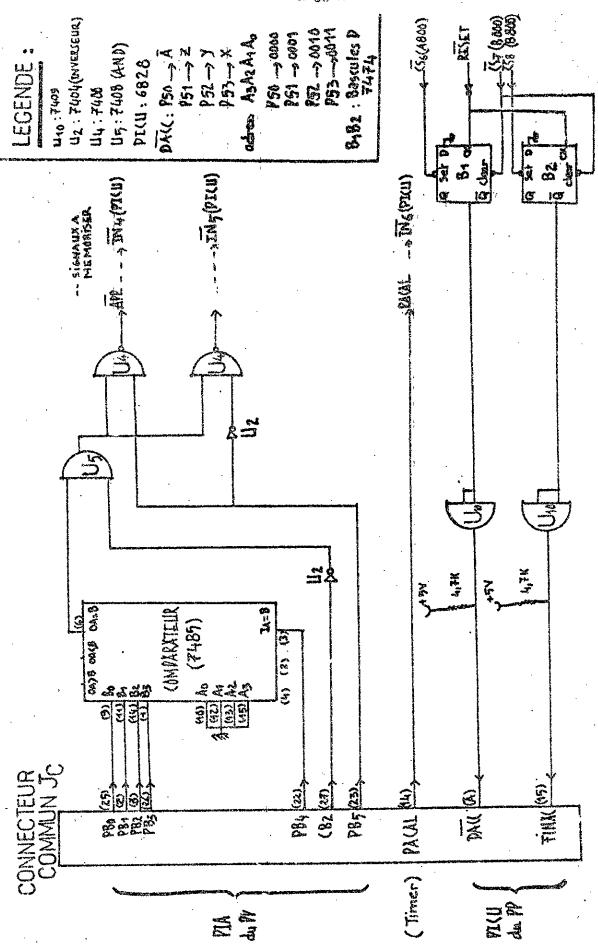

La simulation de processus physiques continus peut se ramener à la simulation de sous-systèmes représentés par des équations différentielles. Ces sous-systèmes seront attribués chacun à un processeur, pour le traitement numérique.

Ces sous-modèles étant en général interdépendants , un couplage interprocesseurs assez important s'impose . Nous obtenons alors une structure multiprocesseur à fort couplage .

Chaque processeur sera chargé d'intégrer une équation

différentielle. Cette opération sera subdivisée en tâches. L'enchaînement des tâches doit être ordonné. Ceci nous conduit à un contrôle centralisé ou à une structure maître - esclave.

Pour accélérer les temps de réponse dans le traitement des informations, nous avons préféré attribuer à chaque processeur son propre ordonnanceur et les objets du noyau au niveau de sa mémoire privée ou locale.

L'évolution des tâches implémentées sur les différentes unités de traitement appelées processeurs secondaires (PS) se fait de manière indépendante avec transfert d'informations entre les PS, sous le contrôle d'un processeur principal (PP). Celui-ci impose un pas de calcul commun de façon à obtenir un démarrage synchrone. Durant ce pas, l'exécution est asynchrone.

Les transferts d'information entre PS se font dans la mémoire commune (MC) à travers un bus partagé . Une demande d'accès à la MC est formulée par le PS en envoyant une interruption au PP qui supervise l'accès en MC .

Le bus partagé est l'un des schémas d'interconnexion multiprocesseur les plus classiques ; il reste intéressant pour la connexion d'un petit nombre de processeurs , vue sa bande passante limitée .

## II.2. Présentation du système Multimu .

Le simulateur est conçu autour d'un PP qui contrôle quatre PS et une MC à travers un bus partagé . Une extension à huit processeurs ( voire seize ) est possible .

Tout dialogue PS - PS passe par la MC sous le contrôle du PP .

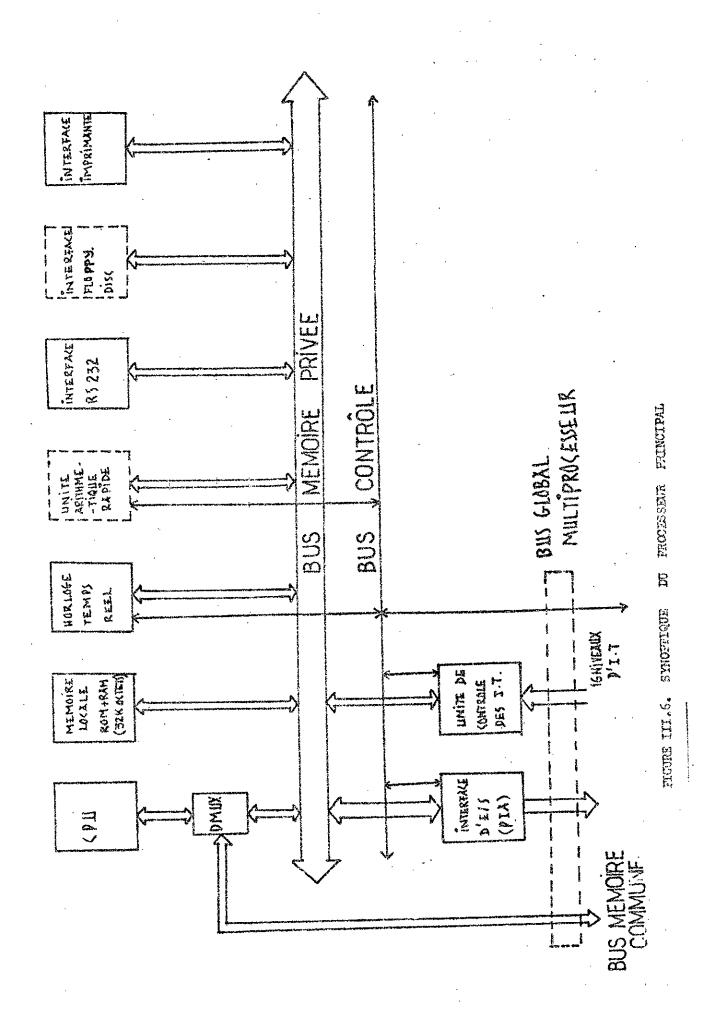

## II.2.1. Le processeur principal .

#### Il a pour fonction :

- d'assurer l'entrée des paramètres du modêle du processus à simuler .

- de prendre en compte les commandes destinées à définir les conditions de la simulation .

- de distibuer les tâches aux PS .

- de lancer la simulation .

- de contrôler l'accès à la MC et au bus commun .

- -de synchroniser l'ensemble à travers le pas de la simulation .

#### Il se compose :

- d'un microprocesseur MC6800 .

- d'une mémoire privée .

- d'une interface série ACIA pour la liaison avec une console de service .

- d'une interface série pour l'imprimante .

- d'un timer programmable pour synchroniser l'évolution des tâches au rythme d'un pas de calcul .

- d'un dispositif d'entrées-sorties parallèles destiné à la génération du bus interprocesseurs .

- de circuits de gestion d'interruptions telles que les demandes d'accès à la MC ,etc ...

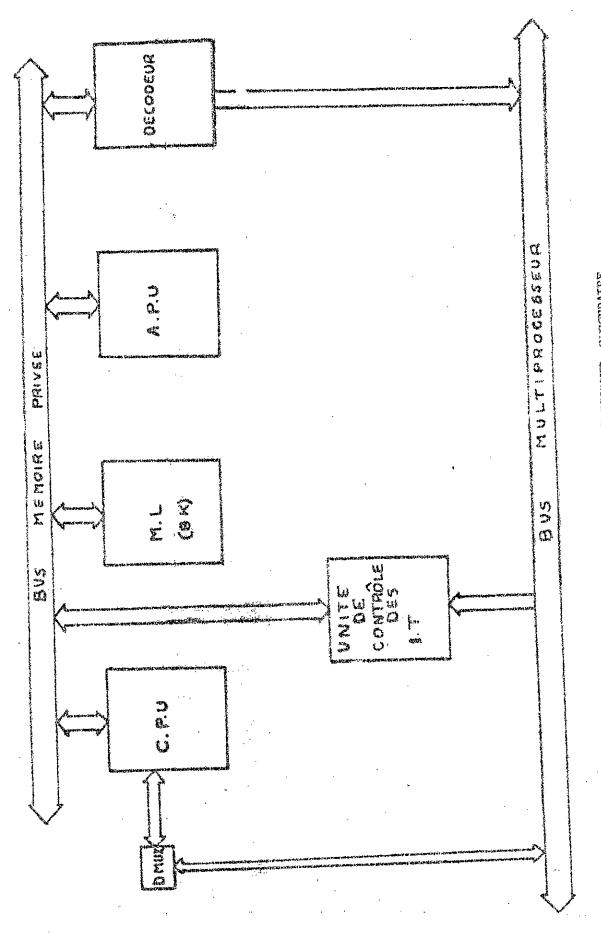

### II.2.2. Le processeur secondaire .

#### Il assure :

- la recherche en MC des paramètres de la simulation (PARO).

- le calcul numérique correspondant à la tâche qui lui incombe (TACAL) .

- La recherche en MC des résultats intermédiaires calculés par les autres PS (FAR1) .

- Le transfert des résultats obtenus par ce PS vers la MC pour leur utilisation par les autres PS ( TARES ) .

Les sous-tâches PARO et PARI appartienment à la tâche TAPAR que nous définitons ultérieurement .

Le PS est constitué :

- d'un microprocesseur MC6800 .

- d'une mémoire locale de programmation et de données (8Kbytes ) .

- d'une logique de dialogue interprocesseurs .

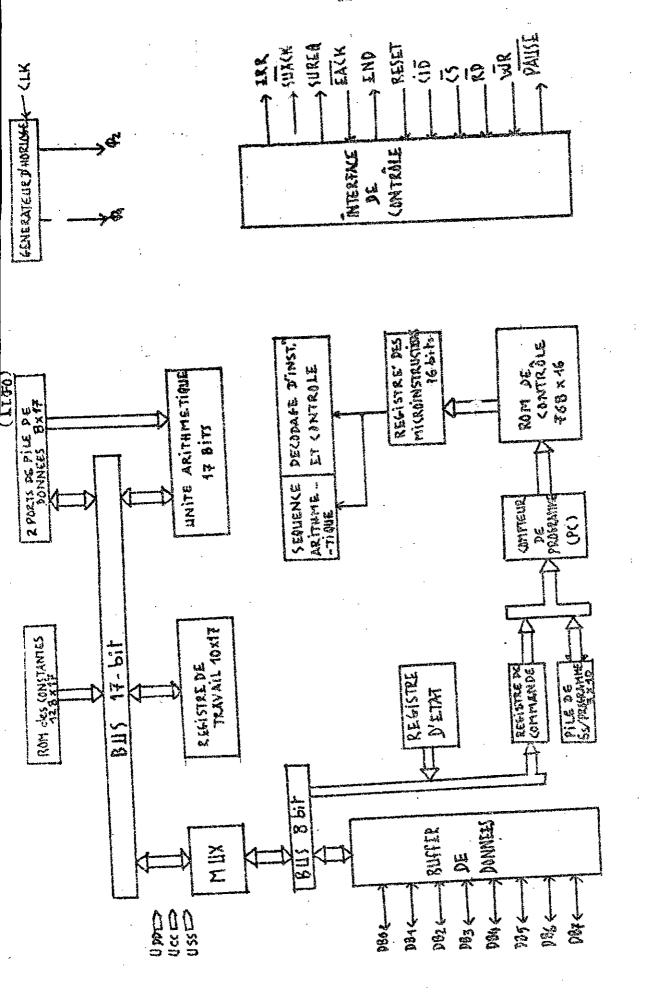

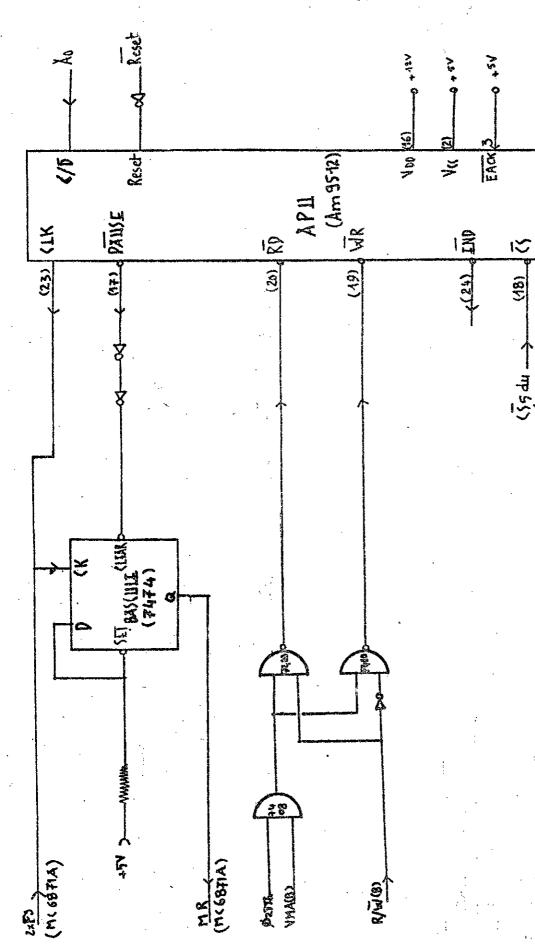

- d'un coprocesseur arithmétique Am9512 et sa logique d'interfacaça au microprocesseur .

#### II.2.3 . Le bus interprocesseurs .

Il se compose de deux parties :

- \* le bus mémoire partagée , contient les signaux habituels d'adresses , de données , et de contrôle .

- \* le busdinterconnexion , contient l'ensemble des signaux de synchronisation .

Lorsque l'un les processeurs utilise le bus ,les autres doivent être en haute impédance par rapport au bus ; ils ne peuvent alors travailler qu'en local . Le PP synchronise l'évolution parallèle des tâches assignées aux PS . De plus , il élimine les conflits d'accès entre les PS .

Pour ce faire , le partage des ressources communes est réalisé au moyen de lignes d'interruptions à priorité entre le PP et le PS .

Les signaux d'interruption assurant l'interconnexion sont :

- le signal DACC : demande d'accès à la MC de la part d'un PS à la fin de son transfert d'information .

- le signal PACAL : donne le pas de calcul aux PS .Il est généré par le PP .

- le signal ACQ : acquittement envoyé par le PP au PS qui a formulé une demande d'accès . Le PP vérifie préalablement si l'accès en MC est libre . Ce signal consiste à autoriser le PS à accèder au bus commun pour effectuer un transfert de données en MC .

- le signal APP : est un appel envoyé par le PP au PS pour signaler que des informations sont prêtes en MC . Une sélection d'adresse doit être faite par le PP de façon à ce que ce signal ne soit reconnu que par le PS sollicité .

Cette logique permet d'adresser chacun des PS ( de l'adresse 0 à 7 ) .

Le bus interprocesseurs a pris forme à partir du bus Exorciser de Motorola ; celui-ci est un bus monoprocesseur . Cependant , les lignes non utilisées de ce bus ont été répertoriées et ensuite affectées aux signaux précédents de façon à utiliser ce bus en multiprocessing ( Fig.III.2 ) .

## II.2.4. Le logiciel de gestion .

L'évolution des tâches avec la contrainte du pas de calcul et les contraintes aléatoires dûes aux interruptions entre PP et PS , nous a orientés vers un système d'exploitation multi-tâches temps réel distribué .

## FIGURE III.2. SIGNAUX DU BUS INTERPROCESSEURS

| A0 - A1     | 15 2           | BUS ADRESSE     | 1                                                                                                               |                 |

|-------------|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| D0 - D7     |                | BUS DONNEE      |                                                                                                                 | BUS             |

|             |                |                 |                                                                                                                 |                 |

| VMA         |                |                 |                                                                                                                 | MICROPROCESSEUR |

| Ø2 · · ·    |                | BUS CONTRÓLE    |                                                                                                                 |                 |

| RESET<br>PP | PS             |                 | ,<br>a                                                                                                          |                 |

| PBC - E     | PB4 Dign       | es de sélection | 1                                                                                                               | •               |

|             |                | d'un PS         | Lignes                                                                                                          |                 |

|             |                |                 | permettant                                                                                                      |                 |

|             |                | 1               | la                                                                                                              |                 |

| FB5 -       | <del>-</del> > |                 | génération                                                                                                      | Lignes omnibus  |