السكرية إلى الهادة الهادة الهادة الهادة الهادة الهادة المادة الهادة اله

UNIVERSITE DES SCIENCES ET DE LA TECHNOLOGIE D'ALGER ÉCOLE NATIONALE POLYTECHNIQUE DÉPARTEMENT D'ÉLECTRICITE

## PROJET DE FIN D'ÉTUDES (INGÉNIORAT EN ÉLECTRONIQUE)

ÉTUDE DU SYSTÈME TÉLÉMESURE TÉLÉSIGNALISATION 7KR1035 INTRODUCTION DE LA LOGIQUE TTL

Sujet proposé par: Mr BAGHLI Med Ingénieur d'état chargé de cours associé

Etudié par MM: DJAMAH B. OUSLIMANI A.

Promotion Juin 1980

## UNIVERSITÉ DES SCIENCES ET DE LA TECHNOLOGIE D'ALGER

## ÉCOLE NATIONALE POLYTECHNIQUE

Département d'éléctricité

THÈSE DE FIN D'ÉTUDES INGÉNIORAT EN ÉLECTRONIQUE

# TÉLÉSIGNALISATIONS TÉLÉMESURES.

ÉTUDE DU SYSTÈME 7KR1035

Sujet proposé par:

Mr BAGHLI Mohamed

É tudié par MM: DJAMAH Boouz OUSLIMANI Achour

Promotion 1979 \_ 1980

Nous formulons l'expression de notre profonde reconnaissance à notre promoteur Mr.BAGHLI Med chargé de cours à l'école nationale polytechnique d'alger qui nous a proposé ce sujet de fin d'études et qui ne cessede responsabiliser l'élève ingénieur en le mettant face à la réalité industrielle du pays.

Que toute l'équipe de la SONELGAZ:

Mr.BOUAFIA

Mr . BENGHANEM

Mr. HADDAD

Mr. BAGHLI Amine

Mr. HADJI

Mr. BENZAID

trouve ici nos remerciements les plus sincères.

Nous ne manquerons pas d'exprimer toute notre gratitude à tout le personnel du centre nodal de la RTA (Bouzareah) qui a bien voulu nous prendre en charge et nous réserver un accueil chaleureux au sein de son organisme:

Mr. KADDOUR BENKADA

Mr.BOUNAB Arezki

Melle LAGHOUATI

Mr. DRARENI Med

Mr BENSLAMA

Mr.NAZEF Belaid

Mr REZZAGUI

Mr. NAIT-DJOUDI Bachir .

En particulier, à Mrs:

TALIGANTE Salah

BOUCHEMLA Cherif

pour leur attachement remarquable à notre travail.

Nos remerciements vont **s**galement aux personnes qui nous ont aidé à la frappe du texte et au tirage dessehémas:

Mr BOUTELDJA

Mr. OUMELLAL Med

Melle DJABALI

Melle ZEMMACHE Mina

QUE TOUS CEUX QUI ONT CONTRIBUE POSITIVEMENT A

L'ELABORATION DE CE TRAVAIL TROUVENT ICI L'EXPRESSION

DE NOS REMERCIEMENTS ISS PLUS DISTINGUES.

Il importe que le langage de la téchnologie ne soit pas l'apanage de cercles limités que la force des choses finit par transformer en milieux fermés vivant en marge du contexte social du pays.

Par ailleurs le moment est venu pour le pays de proncuveir le progrès téchnologique à partir de ses propres ressources humaines et du potentiel qu'il a déjà accumulé dans la demaine de la téchnologie.

CHARTE NATIONALE/

A la mémoire de mon père.

A ma mère.

A mon frère qui a toujours joué son rôle du père.

A tous mes amis.

Ashour.

A mes parents qui ont tant attendu ce jour.

A tous mes frères et soeurs.

A mes amis.

Baouz.

A tous ceux qui se sont donnés pour une algérie libre et démocratique.

#### \_INTRODUCTION

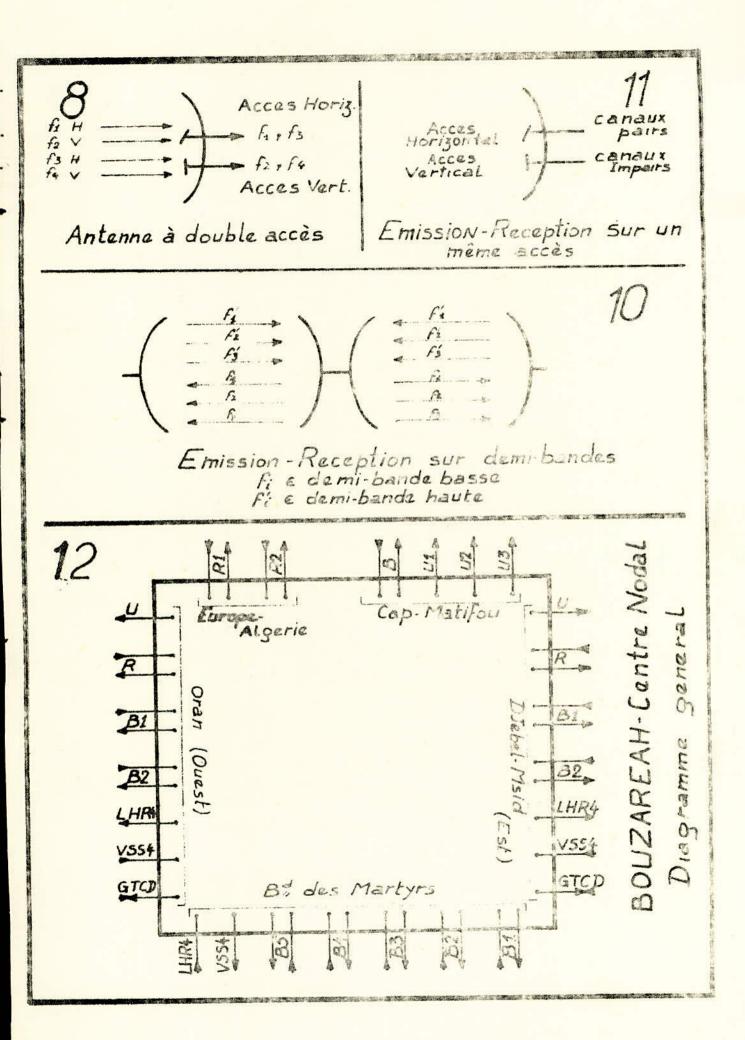

LE centre faisceaux hertziens de la Bouzareah est un centre nodal qui doit recevoir et distribuer tous les programmes Radio et Télévision d'algérie, tant en production nationale qu'en transit international.

Cette station comporte cinq grandes dirèctions qui sont:

- L'est algérien et la tunisie.

- Laouest algérien et le maroc.

- Le centre de production ( Bd des martyrs).

- La station d'émission d'alger ( Cap-Matifou).

- L'europe.

Pour ce faire une multitude de stations asservies sont disséminees à travers le territoire national permettant ainsi l'acheminement des programmes à la destination voulue.

De plus, pour assurer cette fonction dans de bonnes conditions, le centre nodal de Bouzareah joue le môle de poste de commande, à partir duquel on surveille l'état de fonctionnement de chacune des stations asservies, et la qualité de la transmission des programmes. De ce fait, tout un système de télésurveillance, faisant l'objet de notre étude, et de télécommande est prévu dans ce centre.

### SOMMAIRE

| _ | Généralités | - |

|---|-------------|---|

|---|-------------|---|

|                                                  | 1483      |     |

|--------------------------------------------------|-----------|-----|

| I- Introduction                                  |           |     |

| I-1- Notions sur les faisceaux hertziens         | 1         |     |

| I-2- Transmission simultanée de plusieurs        |           |     |

| faisceaux hertziens                              | 4         |     |

| II- Faisceau auxiliaire                          |           |     |

| II-1 - Informations de service                   |           |     |

| II-2- Transmission des informations de service . | 5         |     |

| III- Plan de fréquences utilisé par le           | E         |     |

| centre nodal de BOUZAREAH                        |           |     |

| IV- Notions d'information et de codage           | • • • • 1 |     |

| - Emetteur télémesures - télésignalis            | ations -  |     |

| ( 7KR1035 )                                      |           |     |

| I- Introduction                                  |           |     |

| THE Cycle de transmission                        | 12        | )   |

| TT-Système d'emission télémesures-télésignalisat | ions 16   | C   |

| TTT-1- Circuits communs d'emission               | 16        | )   |

| TIT-2- Entrées mesures                           | 2         | )   |

| III-3- Entrées signalisations                    | 40        | )   |

| - Récepteur télémesures-télésignalisa            |           |     |

| ( 7KR1035 )                                      |           |     |

| 175 Branders Novac S                             | 4         | 1   |

| I - Récepteur télégraphique                      | 4         | 1   |

| II- Circuits communs                             | 7         | 1   |

| III- Circuits de sortie                          | 7         | 1   |

| III-1- Sorties signalisations                    | 7         | 1.1 |

| TIT O CONTIGO MOSILIES                           |           |     |

#### A - GENERALITES

#### 1.1 - NOTIONS SUR LES FAISCEAUX HERTZIENS

#### 1.1. Définition

Un faisceau Hertzien est un support de transmission utilisant les ondes radioélectriques de fréquences élevées supérieures à 1,7GHz, qui permet une liaison point à point entre un poste d'émission et un poste de réception.

### 1.2. Classification des faisceaux Hertziens

Si on considère les caractéristiques des faisceaux hertziens, on peut classer ces derniers en 2 catégories :

- les faisceaux hertziens fonctionnant en visibilité directo

- les faisceaux hertziens transhorizon.

Du point de vue modulation, les faisceaux hertziens peuvent être séparés en 2 autres catégories :

- les faisceaux hertziens analogiques

- les faisceaux hertziens numériques.

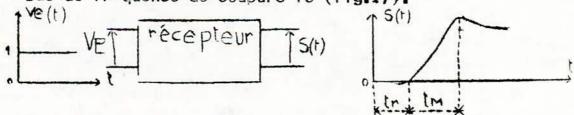

## 1.7 - icceaux hertziens er visibilité directe (fig.1)

La structure des liaisons hertziennes est conditionnée par l'emploi des fréquences élevées. En effet, la diffraction des ondes centimétriques au delà de l'horizon s'accompagne d'un affaiblissement considérable. Par conséquent, si l'on désire établir une liaison en n'éméttant que de faibles puissances, il est nécessaire qu'il n'y ait aucun obstacle entre les antennes, de plus ces antennes ne doivent pas être très éloignée l'une de l'autre pour respecter le billes de puissance. Pour ce faire, un ou plusieurs bands sont

### 1.2.2. Faisceaux hertziens transhorizon

C'est une liaison indirecte qui utilise la diffusion refraction des ondes électromagnétiques dans la troposobère. Ce type de liaisons met en jeu des puissances considérables (Fig.2).

#### 1.2.3. Faisceaux hertziene analogiques

Son utilisés pour :

- la transmission des images T.V. et les voies de son qui leurs sont associées

- des multiplex analogiques de téléphonie.

#### 1.2.4. Faisceaux hertziens numériques

Sont réservés pour l'acheminement

- des données à grande vitesse

- des multiplex numériques de téléphonie

- du visiophone de la TV codée,

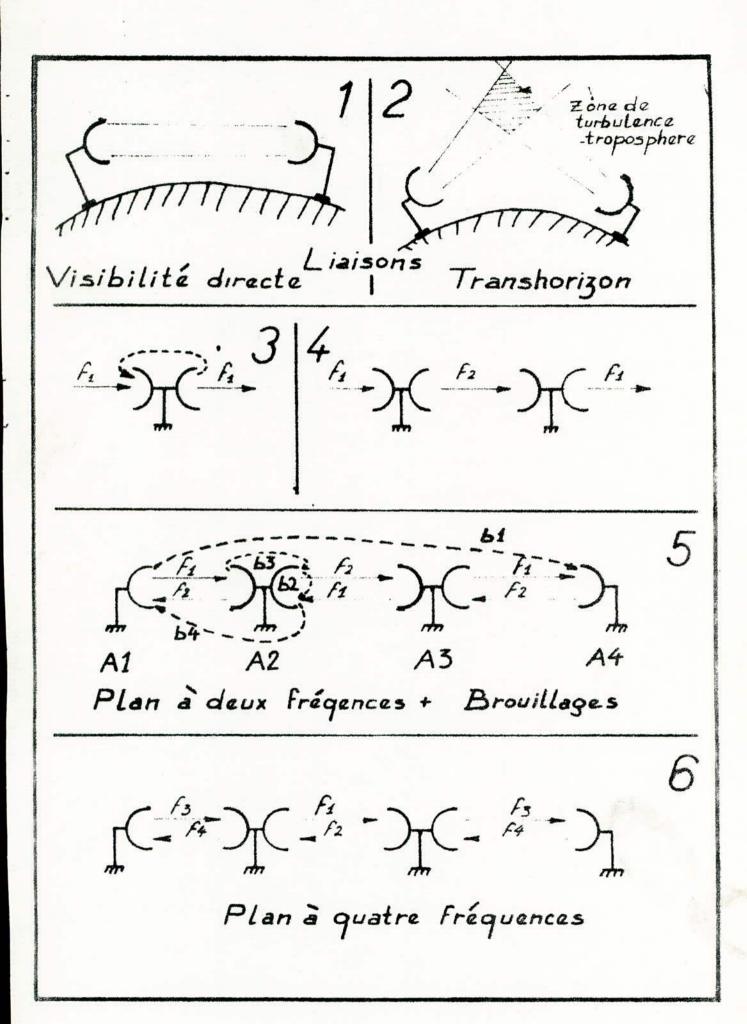

#### 1.3. Types de lisisons (fig.7)

Suivant les besoins du trafic, les voies hertziennes étalbies peuvent être :

- unilatérales

- réversibles

- bilatérales

## 1.3.1. Liasons unilatérales et liaisons reversibles (fic. 24)

Dans ce type de liaisons, la transmission se fait dans un seul sens.

Si on utilise la même fréquence à l'émission et à la réception au niveau de la même station, un couplage entre les antennes d'émission et de réception apparait. Pour parer à cet effet deux variantes sont possibles :

fréquence émission > fréquence réception fréquence émission < fréquence réception

Dans le cas de plusieurs bonds successifs, on adopte alternativement l'une ou l'autre des variantes pour éviter tout risque d'interférence.

#### 1.3.2. Lieisons bilenárales (fig.5)

Dans ce cas, la transmission se fait dans les 2 sens. Daux fréquences au moins, sont nécessaires pour transmettre bilatéralement un signal sur un trajet donné. En effet, dans une station relais, la puissance du signal reçu est très faible et celle du signal remis est relativement élevée. Ce qui conduit comme on l'a vu dans le cas

Des liaisors unilatérales à un couplage possible entre antenne de même support.

Pour remédier à celà, on utilisera la même fréquence à l'émission dans les 2 sens l'autre fréquence servant à la réception.

#### 1-4.- Brouillages possibles dans le cas d'une voie bilatérale (Fig.5)

- B.1 : Couplage entre l'antenne d'émission 1 et l'antenne de réception 4. Ce type de brouillage s'évite facilement étant donné la distance séparant les stations et l'absence de propagation notable au delà de l'Horizon. Il suffit que les antennes correspondantes ne soient pas en visibilité directe, ce qui conduit à ce que les bonds ne soient pas alignés.

- B.2 : Phénomène qui a toujours lieu au sein d'une antenne transmettant des voies bilatérales. Une partie de l'énergie émise est captée par la même antenne. Un écart convenable entre les fréquences démission et de réception ainsi qu'un bon filtrage des signaux reçus permet d'éviter ce brouillage.

- B.3:- L'antenne 2 orientée vers 3, capte une certaine énergie par son lobe atrière. Ce phénomène est dû au manque de directivité des antennes. Pour y remédier il convient d'utiliser des antennes trés directives.

- B.4: L'antenne 2 orientée vers 3 rayonne, par son lobe arrière une partie de son énergie émise vers l'antenne 1. Ce phénomène est aussi dû au fait qur la directivité des antennes est imparfaite. Pour éviter ce brouillage, il convient aussi d'utiliser des antennes trés directives.

#### CONCLUSION.

Des antennes de bonne directivité permettant l'utilisation de 2 fréquences porteuses pour la transmission bilatérale d'un signal. Dans chaque station on fait un croisement de fréquence entre les 2 sens de transmission. Cette solution est bonne sur le plan de l'encombrement spectral mais onereuse puisque utilisant des antennes trés directives. Si l'in dispose d'un réseau peu dense, on peut utiliser un plan à 4 fréquences (Fig. 6).

## 1.2. TRANSMISSION SIMULTANEE DE PLUSIEURS SIGNAUX

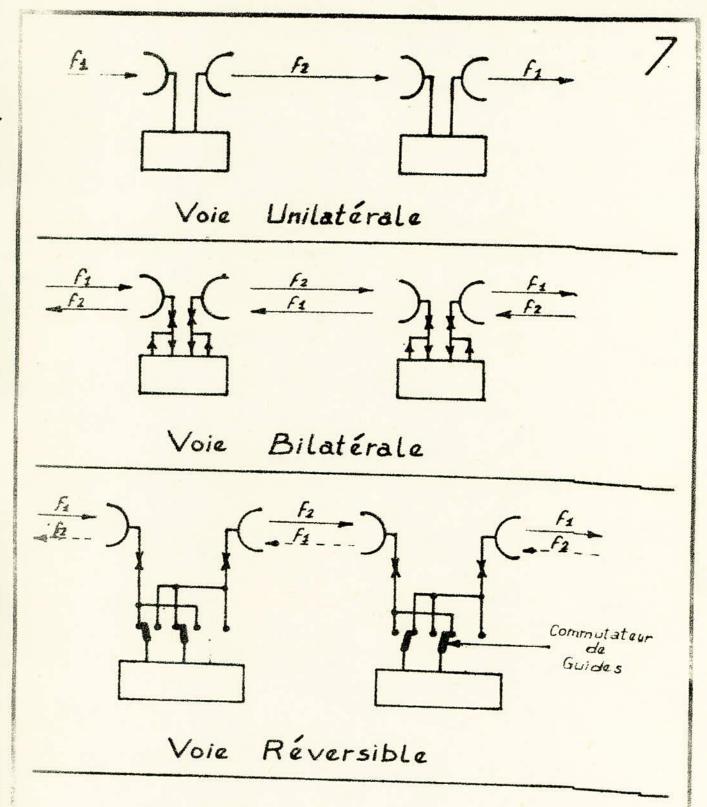

Pour augmenter la capacité des systèmes hertziens on regroupe sur un même trajet la transmission de plusieurs signaux du même type, à des fréquences voisines.

On peut obtenir d'excellents résultats en alternant les polarisations des ondes émises : sur un bond donné et dans un sens donné si le canal n°1 est émis en polarisation horizontales, le N°2 est émis en polarisation verticale.

Pour celà, on emploie une antenne à double accès qui émet une partie des signaux sur une polarisation, et l'autre partie sur une polarisation. (fig. 8)

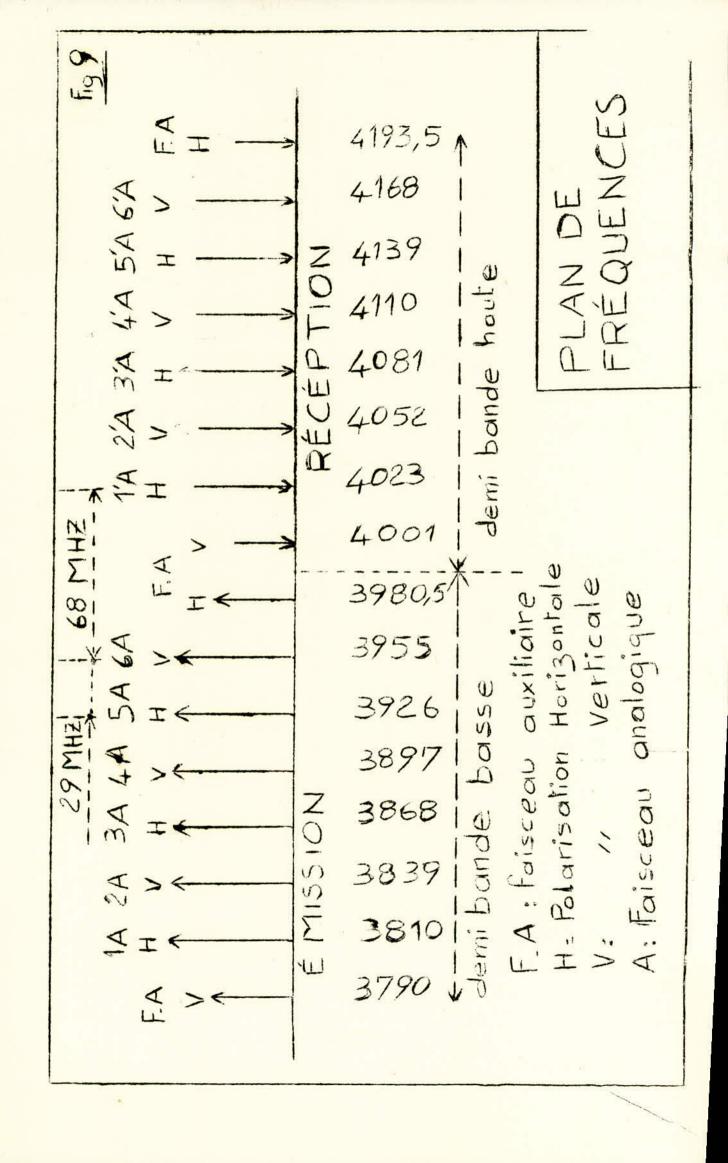

Pour éviter tout danger de prouillage d'émission sur réception par couplage dans une même station, on regroupe toutes les fréquences servant à l'émission dans une station et toutes celles servant à la réception, et à éloigner ces 2 groupes de telles façon qu'ils peuvent être séparés par filtrage(fig.9). Ainsi chaque station émet vune demi-bande et reçoit dans l'autre demi-bande. A la station suivante, la situation est inversée (fig.10).

Les fréquences Fn (émission) et Fn' (réception) ont les mêmes polarisations. L'émission et la réception ont lieu sur le même accès pour un canal donné. Il y a donc un accès de l'antenne destiné aux canaux de rang pair et un cautre à ceux de rang impair.

Pour celà, une seule antenne à double accès et deux lignes en hyperfréquences reliant l'antenne et les équipements radio suffisent (fig.11).

## II - FAISCEAU AUXILIAIRE

Les faisceaux hertziens auxiliaires sont utilisés pour l'acheminement des informations de service entre les stations et éventuellement des commutations de canaux.

## II.1. INFORMATIONS DE SERVICE

Il y a trois catégories d'informations de service

## 1.1. Voies de services

assurent les liaisons téléphoniques à l'usage du personnel d'exploitation.

## 1.2. Télésignalisation et télémesures

- \* Télésignalisation : Ce sont des informations d'état

- Ex : Fonctionnement ou non fonctionnement d'une station surveillée.

- \* Télémesure : Informe le poste surveillant sur les p circimèlresessentiels des équipements.

#### 1.3. Télécommande

- Consiste en l'émission d'ordres à partir du poste de commande vers le poste surveillé. Cet ordre peut être une mise en marche ou arrêt ou une demande de mesure d'un paramètre surveillé.

- On peut envoyer une télécommande et recevoir une télémesure ou une télésignalisation.

- Les télécommandes peuvent être déclenchées manuellement ou automatiquement dans le cas d'une commutation de canaux.

## 11.2. TRANSMISSION DES INFORMATIONS DE SERVICE

Il y a deux types de faisceaux auxiliaires. Ils peuvent :

- être totalement indépendants du faisceau hertzien principal

fonctionnant dans une bande de fréquence à part.

- Utiliser les mêmes aériens et les mêmes lignes de transmission que la liaison principale.

La liaison entre les émetteurs-récepteurs du faisceau auxiliaire et les lignes en hyperfréquence du faisceau principal est assurée par des aiguillages.

Dans ce cas, le faisceau auxiliaire utilise la même bande de fréquences que le faisceau principal. Les fréquences qu'il emploie sont situées aux extrémités des demi-bandes de la liaison principale (fig.9).

## III - PLAN DE FREQUENCES UTILISE PAR LA R.T.A. BOUZAREA

- Bande exploitée : 3,8 4,2 G Hz.

- L'écart entre les fréquences porteuses est de 29 MHz.

- Lécart entre la porteuse la plus élevée de la demi-bande basse et la porteuse la plus basse de la demi-bande hauto est de 68 MHz (fig.9).

- utilisent 8 canaux dont 2 sont réservés au F.H.A. à l'émission et de même pour la réception.

- <u>Puissances émises</u>: dépendent des distances: 500mW; 2W; 7W; 10W pour la visibilité directe 280W pour les liaisons transhorizon.

- <u>Puissances reçues</u> : très faibles, de l'ordre de 10<sup>-6</sup> en général.

- <u>Capacité d'information</u>: La capacité max. de chaque canal est de 300 à 1800 voies téléphoniques.

| F.H.A   | Bande de<br>fréquence     | Nombre de<br>canaux           | Capacité/Canal                    | Modulation | Multiplexage                         |

|---------|---------------------------|-------------------------------|-----------------------------------|------------|--------------------------------------|

| mations | Aller 6MHz<br>Retour 4MHz | 4 dont 2<br>non uti-<br>lisés | 600 à 1800 voies<br>téléphoniques | Phase      | Par répar-<br>tition de<br>fréquence |

## Remarque:

- La même voie de service est utilisée pour toutes les stations (pourvues de personnel ou non).

- Cette voie n'est pas sélective.

- On n'utilise pas de commutation pour les F.H.A. (mais il existe un contrôle par C.A.G. qui est inversement proportionnelle au champ.

- Entre le Bd des Martyrs et Bouzareah sont utilisées 48+1A.

## - Valeur de champ :

Champ nominal : -30 db Seuil : -80 db Champ de travail : -40 db

## IV - NOTIONS D'INFORMATION ET DE CODAGE

#### IV .1. QUANTIFICATION

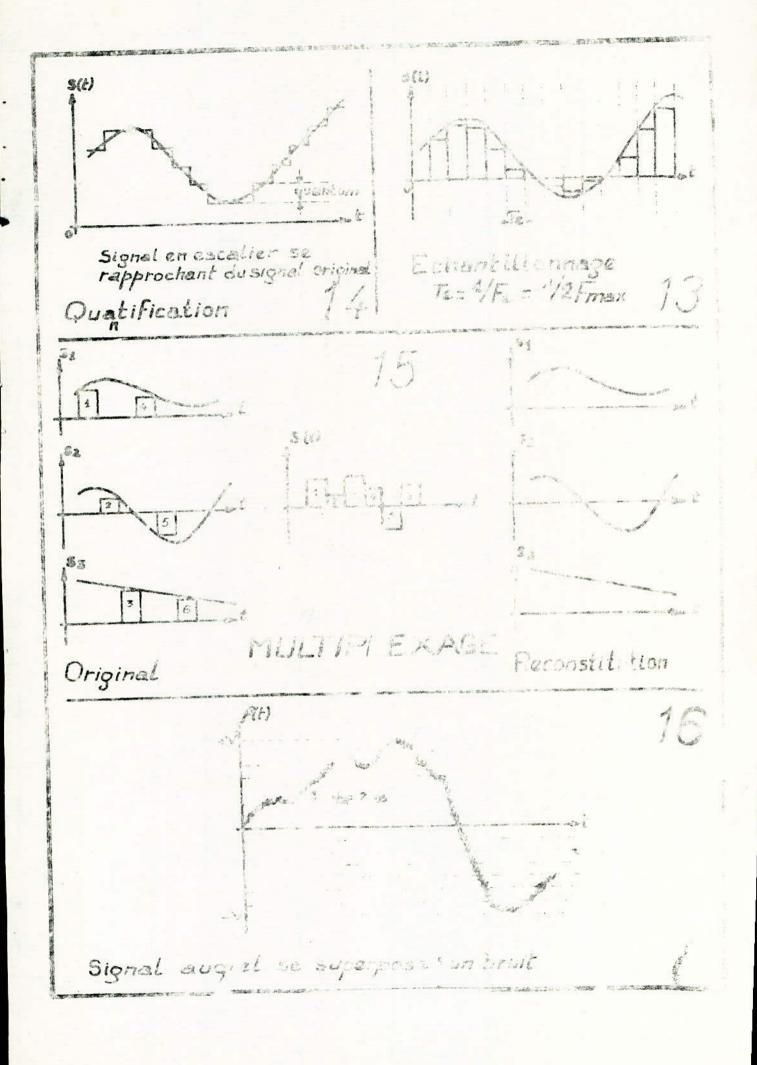

Un signal dont l'amplitude varie continuellement dans une gamme déterminée peut être reconstitué à la réception compte tenu d'un certain degré de distorsion même s'il a été converti en un signal en escalier. Plus le signal en escalier se rapproche du signal original moins la distorsion est forte.

La différence entre deux niveaux consécutifs est appelé "quantum" et le procédé par lequel on transforme le signal original en un signal en escalier est appelé "Quantification" (fig.14).

## IV.2. ECHANTILLONAGE (fig.13)

- Consiste à prélever des échantillons de tension à fréquence fixe pour un signal donné.

- La fréquence d'échantillonage Fe est donnée par le théorème de Shanon suivant :

Pour restituer un signal, la fréquence d'échantillonage Fe, doit être supérieure ou égale au double dela fréquence maximum fm du signal à transmettre, soit :

fe > 2fmax.

## Remarques:

En pratique, la fréquence d'échantillonage fe est toujours prise légèrement supérieure à 2fmax.

(où fmax = fréquence max. du signal à transmettre).

Ex : Cas de la Téléphonie :

- bande occupée : 300 3400 Hz

- fréquence d'échantillonnage fe = 8000 Hz d'où Te =  $\frac{1}{\text{fe}}$  = 125  $\mu$  s.

-7-

- 2 L'échantillonnage n'introduit aucune perte d'informations dans le signal et permet le multiplexage temporel. Il est réalisé à des intervalles réguliers appelés intervalles d'échantillonnage et permet la mesure des variations rapides de signaux.

- 3 Chacune des valeurs des amplitudes est dite "ECHANTILLON".

## IV.3. MULTIPLEXAGE TEMPOREL

IV.3.1. Le multiplexage est utilisé dans des buts de transmission simultannée, sur une même voie, de plusieurs informations.

- Le multiplexage temporel consiste, à partir de plusieurs signaux élémentaires si (t), à former un signal S(t) dit "Signal Multiplex" en prélevant des échantillons successifs de chacun des signaux élémentaires à des intervalles de temps fixes. On émet ainsi successivement une salve d'échantillons dans l'ordre des signaux élémentaires si (t) espacés de:

n = nombre de signaux élémentaires si (t)

fmax = fréquence max à transmettre

fe

$$> \frac{1}{2 \text{fmax}} = \text{fréquence d'échantillonnage (fig.15)}$$

- Le multiplexage temporel doit donc comporter une synchronisation entre l'émission et la réception.

### IV.4. CODAGE

Après échantillonnage et quantification le signal est converti en un train d'impulsions dont les amplitudes ne peuvent prendre qu'un nombre N limité de niveaux prédéter mines.

Si l'on attribue à chacun de ces niveaux un terme d'une série numérique, il est possible de convertir chacun des N nombres en l'une des N combinaisons. Autrement dit, au lieu de transmettre une impulsion dont l'amplitude est voisine du niveau du signal à un instant donné, on trancun groupe d'impulsions dont la combinaison des états (présence ou absence) représente le nombre attribué à ce niveau.

On a donc : N combinaisons Pour N niveaux possibles ---

Soit b = nbre d'états possibles de l'impulsion n = nbre de moments

Alors  $N = b^n$

En général, on utilise le code binaire : b = 2

→ N = 2n combinaisons

### IV.5. CAPACITE DE L'INFORMATION

- Soit N = nbre de niveaux possibles des impulsions (symbôles) on appelle mesure de l'information, la quantité

- Si la communication comporte seulement M symbôles parmi les N disponibles alors on aura:

- la densité d'information est définie comme suit :

$$d := Q/M = log_2N$$

bits/symbole

## IV.6. VITESSE D'INFORMATION

- C'est la quantité d'information transmise en une unités de temps soit :

$$R = 0/t = \frac{M}{t} log_2N bits/sec.$$

- Si les M symbaler choisis sont émis à raison de n/sec alors M = nt d'où : R = nlog<sub>2</sub>N bits/sec

- la vitesse d'information est une grandeur caractéristique de la transmissibilité d'un message.

## IV.7. CAPACITE D'UNE VOIE DE TRANSMISSION

- Pour déterminer le nombre N de niveaux possibles il faut comple tenir du seuil imposé par le bruit.

Il s'agit donc tout d'abord de calculer le nombre de niverux différents que le récepteur peut distinguer sans erreur :

- soit s(t) le signal à transmettre. En l'absence de bruit s(t) passe entre 2 niveaux d'amplitude "+ V" et "-V". Soit l'amplitude max de fluctuation du bruit qui se superpose au signal s(t):  $\triangle V = 2VB$ .

A chaque instant la mesure du signal utile s(t) est déterminée à ± VB près.

Par conséquent, pour que deux mesures instantanées, du signal s(t), soient discernables, il faut que leur écart soit au moins égal à 2VB-.

- Le nombre de niveaux parfaitement distincts entre les amplitudes + Vs et -Vs est donc

$$N = \frac{2V}{2VB} = \frac{V}{VB} = \sqrt{\frac{P}{PB}}$$

où Ps = Puissance du signal s(t)

P<sub>R</sub> = Puissance du bruit

On a donc :  $Q = \frac{1}{2} M \log_2 \frac{P_S}{P_B}$  (fig.16).

On d'donc opéré une quantification du signal.

- Pour définir complètement la possibilité de transmission du système il faut tenir compte de la rapidité de réponse du récepteur :

On peut toujours assimiler un récepteur, à un filtre passe bande ou si on transpose les fréquences, à un filtre passe bas de fr quence de coupure fc (fig.17).

Si on applique à l'entrée du filtre passe bas un échelon unité, le signal de sortie S est en retard d'1 temps t? par rapport àVE et n'atteint sa valeur définitive qu'après un temps de montée tM qui est lié à la fréquence de coupure fc:(tM  $_1$  ).

#### CONCLUSION

Pour que le récepteur puisse distinguer une suite de niveaux successifs analogues à une suite d'échelons, il faut que

l'intervalle de temps entre un passage d'un niveau à l'autre soit supérieur au temps de montée tM.

En 1 seconde, il est donc possible de distinguer au plus n=2f signaux différents espécés régulièrement de 1/2 fc seconde.

On a donc la vitesse d'information max. :

$$R_{\text{max}} = n \log_2 M = 2fc \log \sqrt{\frac{P_S}{P_B}} = fc \log \frac{P_S}{P_B} \text{ bits/s}$$

or la puissance P = Ps + Pp ==>

$$R_{\text{max}} = \text{fc log}_2(1 + \underline{P_s}) \text{ bits/sec}$$

$$\underline{P_g}$$

Ces résultats s'énoncent sous la forme du théorème de Shanon :

"La vitesse d'information R d'un signal continu de puissance moyenne Ps, dont le spectre occupe une largeur de bande B et qui est soumis à l'influence d'un bruit de puissance moyenne PB est Rmax. avec

$$R_{\text{max}} = \mathcal{D} \log_2(1 + \frac{P_s}{P_B}) \text{ bits/sec.}$$

La capacité C d'une voie de transmission s'identifie à la vitesse d'information maxumum qu'il est possible de transmettre dans cette voie

- Dans l'attente des transmissions, le problème le plus important consiste en l'adaptation des caractéristiques du message, à savoir sa vitesse "Rmessage", à celles de la voie de communication, sachant qu'une voie est caractérisée par sa capacité C.

- Le théorème de TULLER-SHANNAN exprime la relation fondamentale liant ces deux caractéristiques : "Une voie de capacité C peut théoriquement transmettre un message ayant une vitesse d'information R & C, abstraction

faite de la nature du message et de la voie".

TYPES DE LIAISONS PAR VOIES HERTZIENNES

## DU CENTRE NODAL BOUZAREAH - (7 KR 1035)

#### I)- INTRODUCTION:

Le 7 KR 1035 utilise le principe de transmission cyclique des informations. Chaque grandeur surveillée échantillonnée et transmise à intervalles réguliers.

Ma durée qui sépare deux échantillons succéssifs correspond à la durée du cycle.

#### II)-CYCLE DE TRANSMISSION:

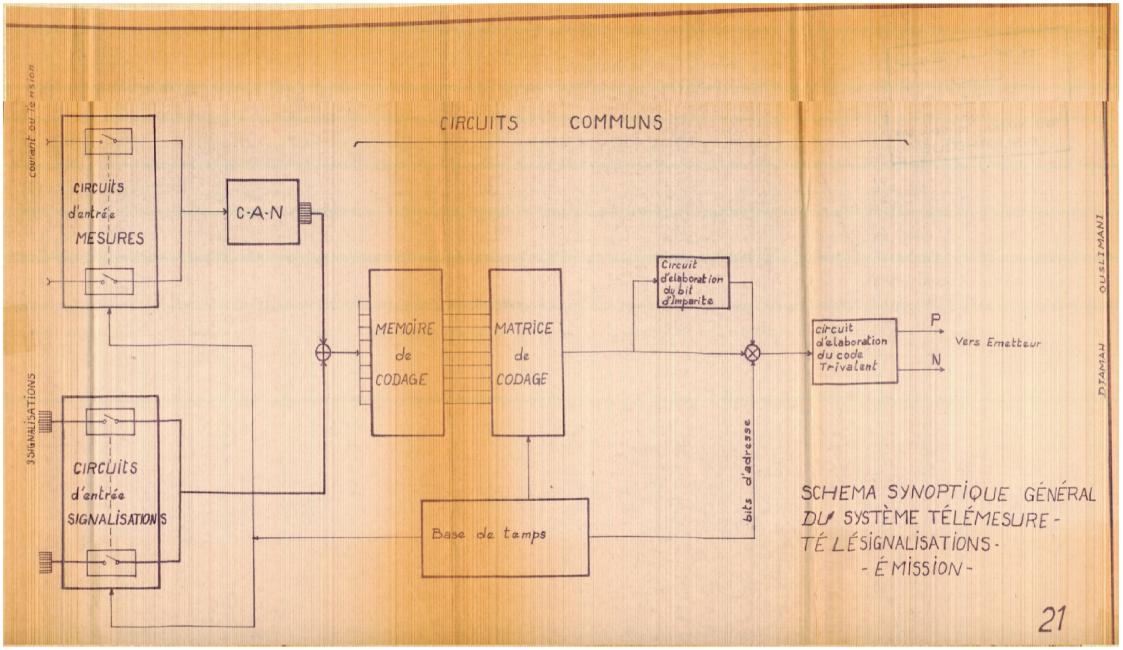

## II-1- FONCTIONNEMENT: Fig 21

-Au départ, un circuit d'entrée délivrant 9 informations véhiculées sur 9 Fils en parallèlle servant de support d'information est sélectionné parmi d'autres.

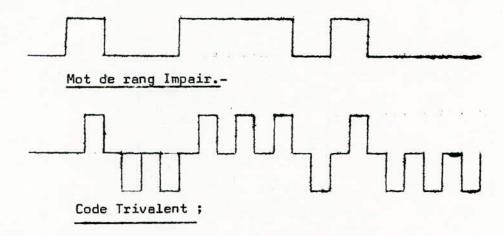

Ces informations sont ensuite codées suivant un code détecteur d'erreur par contrôle d'imparité puis adressées avant d'être restituées décalées dans le temps (en série) à l'émetteur télégraphique qui va se charger de les transmettre en code trivalent par déplacement de fréquence. On emetainsi un suite de mots complets formant le cycle.

-Les codages et adressage sont réalisés afin de protéger les informations lors de la transmission en ligne, de permettre la détermination exacte de la position du mot dans le cycle et la détection d'erreurs éventuelles à la réception.

#### II-2- SYSTEME D'ADRESSAGE ADOPTE.

A l'émission, chaque mot est muni d'une adresse partielle.

Ainsi pour déterminer complètement la position du mat dans le cycle

il est nécessaire de considerer 2 adresses successives.

Dans le cas d'1 cycle à 16 mots, la constitution des adresses se fait comme suit:

\* S'il s'agj + d'un mot de rang pair, l'adresse sera fournie par les états des 2 bascules de plus fort poids (poids, 8 et poids 4) du compteur de mot.

\* S'il s'agit d'un mot de rang , impair, l'adresse sera fournie par l'état de la bascule de poids 2 du comptemme de mot.

Le rang du mot sera donné par la bascule de plus faible poids du compteur de mot En effet sile mot est de rang pair cette bascule est toujours à 0, si le mot est de rang impair elle est toujours à 1.

| Décimal | .i. (255)    | Dit rang   | Adresse  |

|---------|--------------|------------|----------|

| 0       | 000          | ! 0        | 0 0      |

| 1       | 000          | 1 1        | ! 0      |

| 2       | 0 0 1        | 0          | ! 0 0    |

| 3       | 0 0 1        | 1 1        | ! 1      |

| 4       | 010          | ! 0        | 0 1      |

| 5       | 010          | 11         | ! 0      |

| 6       | 011          | . 0        | 0 -11    |

| 7       | 011          | 1 1        | 1 1      |

| 8       | 100          | ! 0        | 1 0      |

| 9       | 100          | 1 1        | <u> </u> |

| 10      | 101          | . 0        | 1 0      |

| 11      | 1 0 1        | 1 1        | ! 1      |

| 12      | 110          | ! 0        | 111_     |

| 13      | 110          | <u>i</u> 1 | . 0      |

| 14      | ! 1 1 1      | . 0        | 1 1      |

| 15      | !<br>! 1 1 1 | <u> </u>   | . 1      |

- On remarque une caractéristique de ce système d'adressage inégal suivant le rang du mot qui est en elle même une information du rang du mot ce qui rend inutile la transmission du bit de plus faible poids du compteur de mot.

- -La combinaison constituée par les adresses de 2 mots consécutifs ne se retrouve jamais 2 fois dans le cycle.

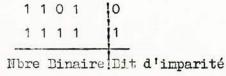

#### II-3/: CODE DETECTEUR D'ERREUR.

- \* La transmission d'informations peut se faire avec une ou plusieurs erreurs (changement d'un 0 en 1 ou d'un 1 en 0).

- C'est pour celà qu'on utilise des codes permettant leur détection.

- -Dans le cas considéré, le code utilisé est celui détectant une erreur. 6'est le contrôle d'imparité: dans les codes à bits on ajoute un(M+1) è pe bit appelé "bit de parité".

On donne alors à ce bit la valeur 0 ou 1 de façon à ce que le nombre de 1 parmi les (M+1) variables soit toujours impair.

#### REMARQUE:

On a choisi un code détacteur d'une seule erreur vu que la probabilité d'avoir plusieurs erreurs en même temps est suffisamment faible, réalisant ainsi une économie en matériel.

Exemple: Code à 4 bits:

- Soit à transmettre les nombres binaires:

A la réception le détection d'un nombre pair de 1 décelera une erreur.

#### II-4 - CONSTITUTION DU MOT:

Chaque mot du cycle est constitué:

- \* D'1 bit signal début de mot qui est toujours à l'état 0 .

- \* De 9 bits comportant l'information à transmettre .

- \* D'1 bit de contrôle d'imparité.

- \* D'1 ou d'2 bits d'adresse suivant que le mot est de rang impair ou pair.

La longueur du mot varie donc suivant son rang:

- \* 13 bits sirle not est de rang pair

- \* 12 bits si le mot est de rang impair.

#### II-5 - CARACTERISTIQUE DE TRANSMISSION.

- La transmission télégraphiques s'éffectue par déplacement de fréquence.

- Le code exploité est (un code) trivalent utilisant 3 fréquences pour la transmission de 3 états (S,P,N).

- La vitesse de transmission utilisée étant de 50 bauds: Les canaux de transmission sont de 120 Hertz conformément aux recommandations du C.C.I.T.T. L'excursion de fréquence ∠)F est dans ce cas de 30 Hz.

Dans une voie télégraphique on peut superposer jusqu'à 24 canaux de 120 Hz.

- La durée du cycle dans la vitesse de modulation 50 bauds: est donnée par le tableau suivant:

| Longueur du Cycle | Durée eh sec. |

|-------------------|---------------|

| 2 mots            | 1             |

| 4 Mots            | 2             |

| 6 mots            | 3             |

| 8 mots            | 4             |

| 10 Mots           | 5             |

| 12 mods           | 6             |

| 14 modis !        | 7             |

| 16 mots           | 8             |

- Chaque intervalle de transmission correspondant à l'émission d'1 bit(40 ms) est divisé en 2 sous phases de longueur 20 ms. Pendant la 1ère sous phase seule fréquence centrale FO est émise, pendant la 2ème sous phase l'information proprement dite est transmise sous forme d'un déplacement de fréquences (Df = 30 Hz) positif ou négatif.

Le signal "début de mot " est caractérisé par l'émission de la fréquence centrale pendant les 2 sous phases.

Soit à transmettre le mot suivant:

La probabilité d'inversion d'un bit (1 remplacé par 0 ou inversement) au riveau du récepteur en présence de bruit aléatoire sur la ligne, est trés faible devant la probabilité de disparition d'i bit c'est à dire le remplacement d'un bit d'information par un signal de synchronisation début de mot". Le côde trivalent permet en plus une synchronisation simple et sûre au niveau du bit et du mot. Ceci contribue à la protection des informations transmises.

#### CONCLUSION:

La durée de transmission d'1 mot peut être divisé en plusieurs phases:

- \* 1 phase To d'introduction du groupe de 9 informations sélectionné.

- \* 9 phases T1 à T9 d'envoi succéssif des 9 informations vers l'émetteur télégraphique.

- \* 1 phase T 10 d'envoi du bit de contrôle d'imparité.

- \* 1 phase T 11 ou 2 phases T 11 et T 12 d'envoi de l'adresse vers l'émetteur suivant que le mot est respectivement impair ou pair.

On a ainsi 13 ou 12 phases par mot suivant qu'il est pair ou impair.

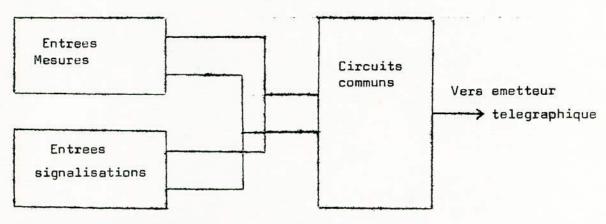

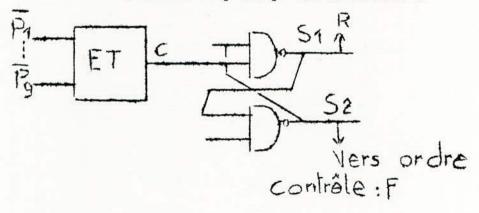

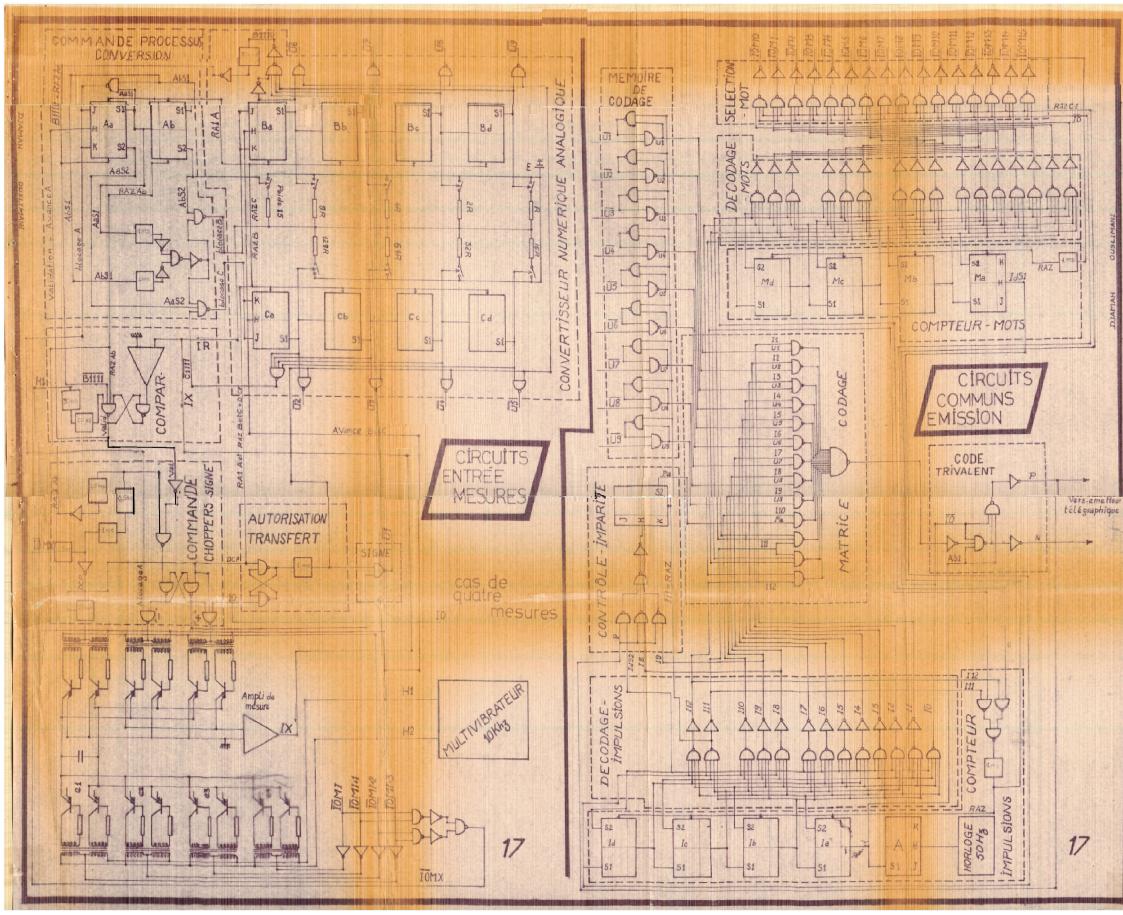

#### III - SYSTEME D'EMISSION TELESIGNALISATION - TELEMESURES. (fig. 21)

#### Il comporte:

- Les circuits d'entrée signalisation

- Les circuits d'entrée mesures

- Les circuits communs d'émission.

#### III-1 - CIRCUITS COMMUNS EMISSION//

#### Ils ont pour rôle :

- \* d'élaborer tous les rythmes nécessaires au fonctionnement des différents circuits.

- \* De conserver l'information pendant tout le temps nécewsaire à sa transmission en ligne.

- \* D'élaborer le bit de parité(code détecteur d'erreur) et l'adresse de transmission.

- \* De coder l'information en trivalent.

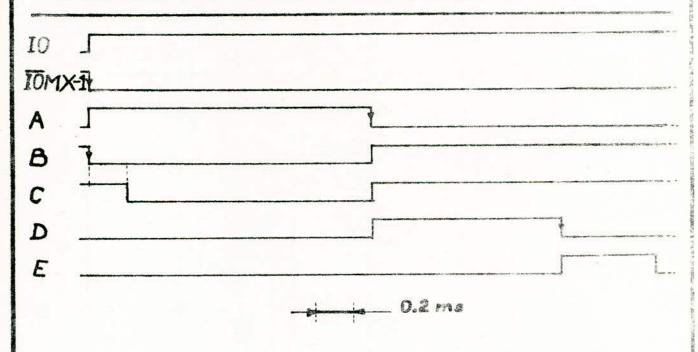

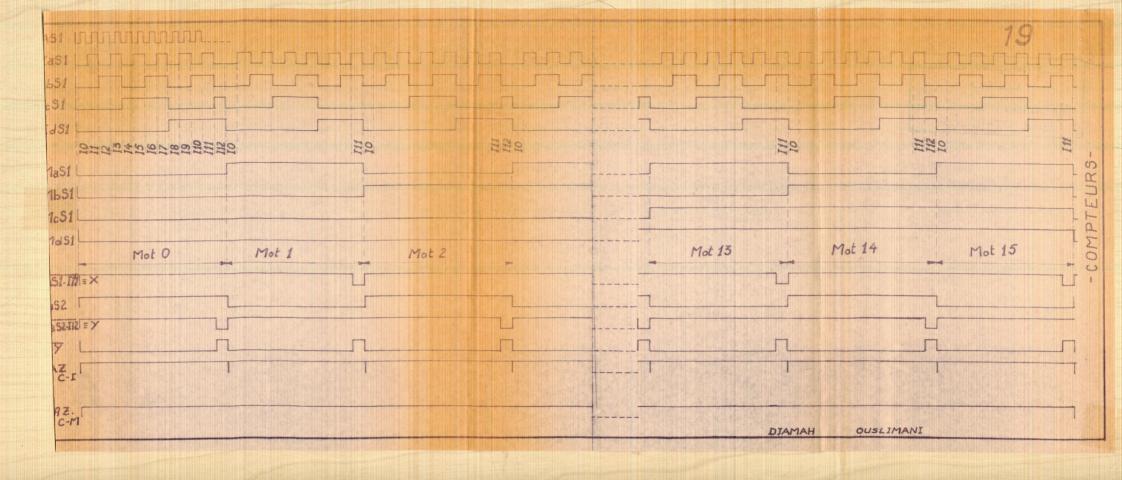

#### III-1-1 GENERATION DES SEQUENCES (BASE DE TEMPS)

L'élaboration des rythmes nécessaires au fonctionnement des différents circuits et en particulier des circuits de sélection des entrées est assurée paf un généraleur de séquences composé de deux compteurs assynchrones.

Le premier commandé par une horloge délivrant un signal carré de rapport de forme unitaire dont la période correspond à la durée d'émission d'un bit (40 mS) servira à mesurer le mot( comptage des différentes phases de chaque mot) dont la longueur varie en fonction du rang. (voir adressage) c'est le compteur d'impulsions (C.I).

Le deuxième, commandé par la bascule de plus fort poinds du compteur d'impulsions servira à mesurer le cycle dont la longueur (Nbre de Man) est choisie par l'utilisateur en fonction du nombre d'informations à transmettre (les longueurs de cycles possibles sont 2,4 ...., 14,16 mots). C'est le compteur de mots.

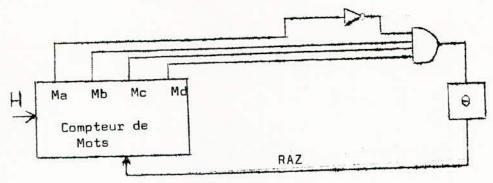

## III-1-1-1/ LE COMPTEUR DE MOTS (Fig. 17 et 19)

En verti de ce qui a été dit auparavant, le nombre de positions possibles du C.M sera fonction de la longueur du cycle choisi.

Vu que le système étudié permet l'utilisation de cycles dont la longueur peut atteindre 16 mots, autrement dit il permet l'utilisation de 16 circuits d'entrée puisque chaqueun d'eux correspond à un mot, le compteur de mot sera constitué de 4 bascules en cascade.

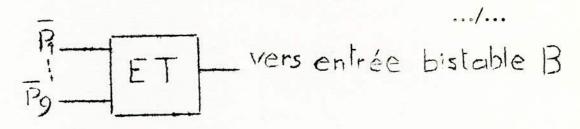

La remise à Zéro du compteur de mot, dépendra donc de la longuemm du cycle choisi. Elle se fera par un signal correspondant à la dernière position du compteur.

Exemple: Dans le cas d'un cycle à 8 mots, la remise à Zéro du compteur de mot se fera à la fin de l'état 7 (0111) conformément au schéma suivant:

1' willies mon c' m

L'adjonction d'un retardateur ⊖ permet la remise à 0 du C.M à la fin de l'état 7. (voir annexe).

#### III - 1.1.2 LE COMPTEUR D'IMPULSIONS (Fig 17 et19)

- D'aprés le système d'adressage adopté (voir adressage)

la longueur du mot varie, suivant qu'il est de mong pair ou de rong impair

Le compteur d'impulsions chargé de mesurer la longueur du mot verra donc

sonhombre de positions possibles varier :

- \* Si le mot consideré est le rong pair ; 13 positions

- \* Si le mot consideré est de rang impair : 12 positions

Le compteur d'impulsions sera donc constitué de 4 bascules dont la remise à zero sera fonction du rang du mot consideré et de la dernière position possible.

Ce rang est donné par la bascule de plus faible poids du compteur de mot comme vu auparavant.

Le ratardateur ici à le même rôle que le retardateur dans le cas de la renise) à zero du compteur de mots. En effet :

Rang pair = ) Mas 1 = 0

$$\rightarrow$$

Mas 2 = 1

=) e 2 = M a 52 · I 12 = 1  $\leftarrow$  I 12

Rang imp = ) M a 51 = 1 =) e = Ma51 · I11=1 $\rightleftharpoons$

- A chaque fois que le C.I est remis à zero, le C.M avance d' 1 cran.

- Ou élaboré ainsi avec le compteur d'impulsions 12 ou 13 phases Ii (suivant le rang du mot) qui ne sont rien d'autre que les T i definies auparavant. Soit :

- Io = Phase d'introduction des informations dans les circuits d'émission qui va correspondre aussi à la phase de remise à zero des compteurs, qui sera prise comme phase de debut de mot.

- I1 à 19 = Phase d'émission de l'information (signalisations ou mesures)

- I10 = Phase d'émission du bit de contrôle de parité.

I11 = Phase d'émission du bit d'adresse

I12 = Phase d'émission du 2ème bit d'adresse dans læ cas d'un not de rang pair.

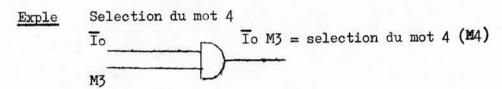

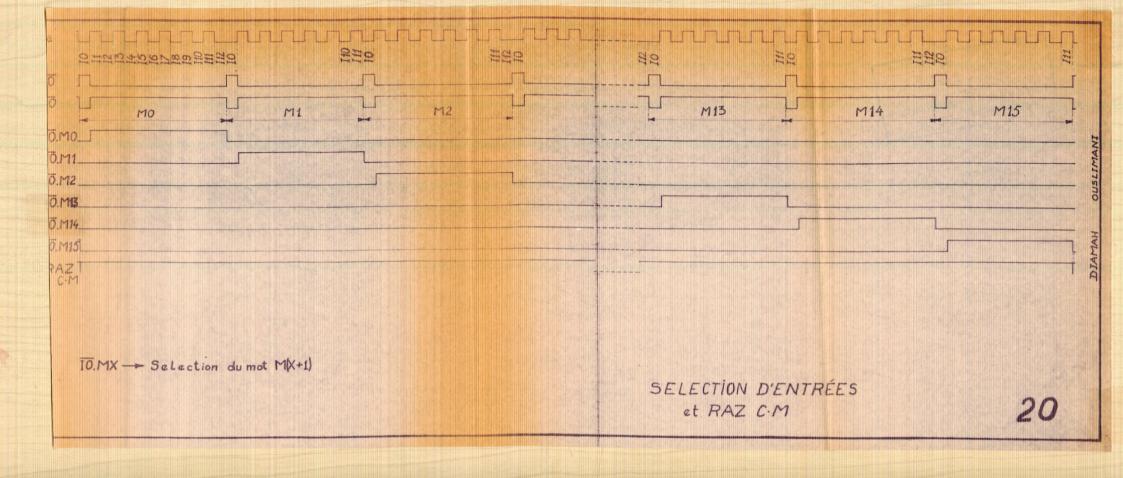

### III - 1.2 CIRCUIT DE SELECTION DES ENTREES (Fig 17et 20)

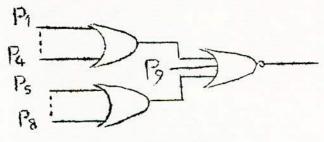

Le selection des circuits d'entrée correspondant chacun à un mot du cycle se fait d'une façon sequentielle: Elle est réaliseé en décodant les positions succesives occupées par le compteur de mots.

Cette selection doit durer pendant tout le temps necessaire à l'émission du mot en cours sauf pendant la phase debut de mot Io .

- Une telle fonction sera réaliseé à l'aide d'une porte AND.

- Dans le cas d'utilisation d'un cycle à 16 mots, ou aura 16 portes identiques chacune affectée à un mot (entrée) du cycle.

#### REMARQUE :

On a vu que le nombre de positions possibles du compteur de mot dépendait de la longueur da cycle choisi, la commande de remise à zero de ce dernier sera assurcé par la sortie de selection du circuit d'entrée correspondant à la dernière position choisie ( dernier mot du cycle ), à travers un retardateur dans le rôle est d'assurer la remise à zero à la fin du signal selection d'entrée, c'est à dire à la phase (Io) suivante.

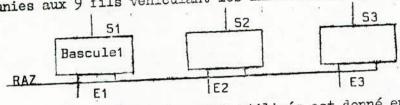

## III 1-3: INTRODUCTION DES INFORMATIONS ( PHASE Io ) ( Fig 17)

L'introduction des informations, correspondant au mot MX, dans les circuits d'émission se fait durant la phase Io grace à un signal delivré par un retardateur commandé par le signal selection de mot ToM (X-1). (voir circuit d'entrée).

Ces informations apparaissent au même et unique temps, correspondant à l'apparition du bit d'introduction des informations, sur 9 fils parallelles servant de support d'information. Il est donc necessaire de les mettre en memoire avant de les restituer decalées dans le temps vers l'émetteur.

Pour ce faire, on utilisera 9 bascules dont les entrées sont réunies aux 9 fils vehiculant les informations conformement au Schema suivant :

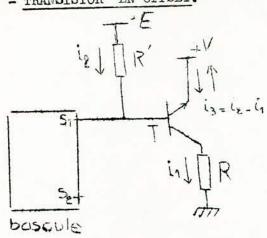

(Le type de bascules utilisés est donné en annexe)

La remise à zero de ces bascules est assurée par le signal III c'est à dire aprés l'envoi sur l'émetteur des 9 bits informations et du bit contrôle d'imparité, et en même temps que la remise à zero de la bascule delivrant ce dernier.

A la fin de la phase Io les 9 informations seront transferées dans les 9 bascules qui vont constituer ainsi une memoire de codage.

## III1-4 CODAGE DE L'INFORMATION ( PHASES I1 à 19 ) ( Fig 17 )

Pour retrouver ces 9 informations (bit) decalées dans le temps, il suffit d'effectuer les produits respectifs des contenus des bistables avec les phases (Impulsions) I1 à I9.

On élabore ainsi un circuit qui va permettre l'exploration sequentielle des 9 étages bistables de la mémoire de codage.

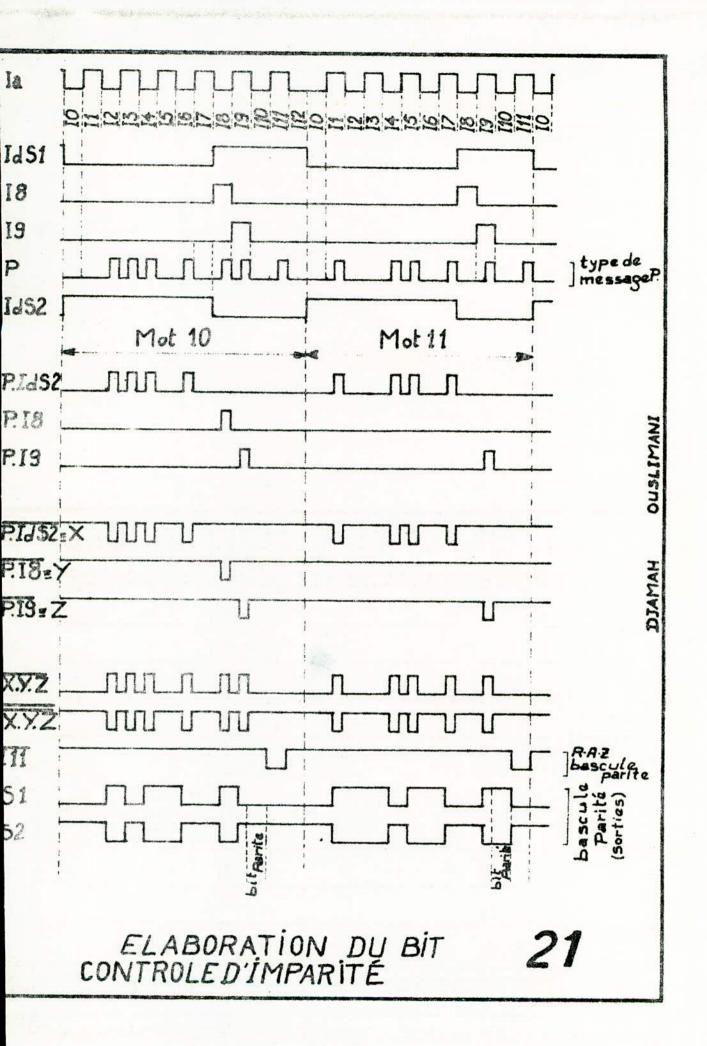

## III 1-5 ELABORATION DU BIT DE PARITE ( PHASE I10 ) ( Fig 21)

\* Le côde utilisé étant un code detecteur d'erreur par contrôle d'imparité, c'est à dire que le nombre de bit 1 contenus dans les 10 premiers bits doit toujours être impair.

On doit donc élaborer un circuit qui comptera le nombre de bits 1 emis pendant les phases I1 à I9 et qui suivant que ce nombre est pair ou impair fournir respectivement un bit 1 ou un bit 0 qu'on emet à la phase I10 à la suite des 9 bits informations.

On doit donc élaborer un circuit qui comptera le nombre de bits 1 emis pendant les phases I1 à I9 et qui suivant que ce nombre est pair ou impair fournir respectivement un bit 1 ou un bit 0 qu'on emet à la phase I10 à la suite des 9 bits information?

- L'emission de ce bit de contrôle de parité sera, comme pour les 9 bits d'information, assurée par une porte "AND" sous condition de l'impulsion I10 et d'une bascule P delivrant le bit contrôle de parité.

- Tous les bits 1 sauf ceux correspondants à l'adresse(phases I11 et I12) sont présentés à l'entrée de la bascule qui devra donc se mettre à 1 si leur nombre est pair et à 0 si leur nombre est impair.

- \* D'aprés le principe même des bascules, cette dernière réagit lorsque se présente à son entrée un front négatif. Et chaque bit 1 possède un seul front négatif

Si on fait la synthèse des états successifs que prend la bascule au fur et à mesure que des bits 1 se présentent à son entrée on aura :

- Au départ la bascule est à 0.

- Au front descendant du 1er bit 1 qui se présente, elle se met à 1 i.e S1 = 1  $S2 = \overline{S1} = 0$

- Au front descendant du 2ème bit 1 qui se présente à son entrée elle se remet à 0 i.e S1 = 0 S2 = 1

- Au front descendant du 3ème bit qui se présente on aura S1 = 1 S2 = 0 etc...

- On remarque qu'on doit plutôt utiliser la sortie S2 de la bascule.

#### REMARQUE:

Le changement d'état de la bascule s'effectue dans à la fin de chaque bit 1 conformement au diagramme suivant .

#

Dans le cas où le 9ème bit d'information est un 1 . le changement d'état de la bascule s'eff ctuera à la fin de ce bit qui correspond à la fin de la phase I9 c'est à dire au debut de la phase I 10 qui est celle d'emission sur ligne du bit de contrôle de parité. On a donc interêt à inverser le signal d'attaque. P de la b scule de façon à provoquer son changement d'état chaque debut de bit 1 qui se présente.

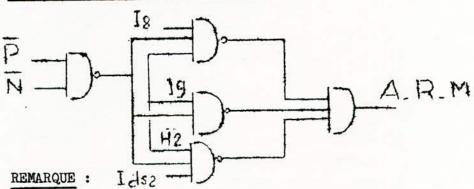

De plus pour se limiter aux 9 bits d'information on utilisera une porte "AND" qui sera sous condition du signal P et d'un signal qui durera juste le temps d'émission des 9 bits d'information. Ce signal sera en fait constitué de 3 signaux distincts dont la somme des durées est celle voulue Ce sont les signaux d'états:

- \* La bascule de plus fort poids du compteur d'impulsion donné par sa partie complémentaire I dS2 qui est à un du debut de la phase Io è fin de la phase I 7.

- \* Des phases I 8 et I 9.

On aura ainsi, le circuit d'élaboration du bit de contrôle de parité . Conformément au Schema de la fig 17

## III -6 ELABORATION DE L'ADRESSE (PHASES I1 ET I12) (Fig 17)

MdS1

T11

On a vu que suivant le rang du mot, le contenu de l'adresse varie :

- \* 1 bit pour les mots de rang impair

- \* 2 bits pour les mots de rang pair

Conformement au système d'adressage adopté (voir adresse) le compteur de mots va delivrer l'adresse du mot qui sera transmise sur la ligne aux phases I 11 et I 12 grâce à des portes "AND" comme pour les informations precedentes.

On a le circuit délaboration et de transmission en ligne de l'adresse suivant :

#### CONCLUSION

- On a ainsi constitué une matrice de codage recevant des informations à son entrée sur des fils en parallelle et les restituant, sur 1 seul fil en sortie.

- A la sortie de cette matrice on a 1 mot complet.

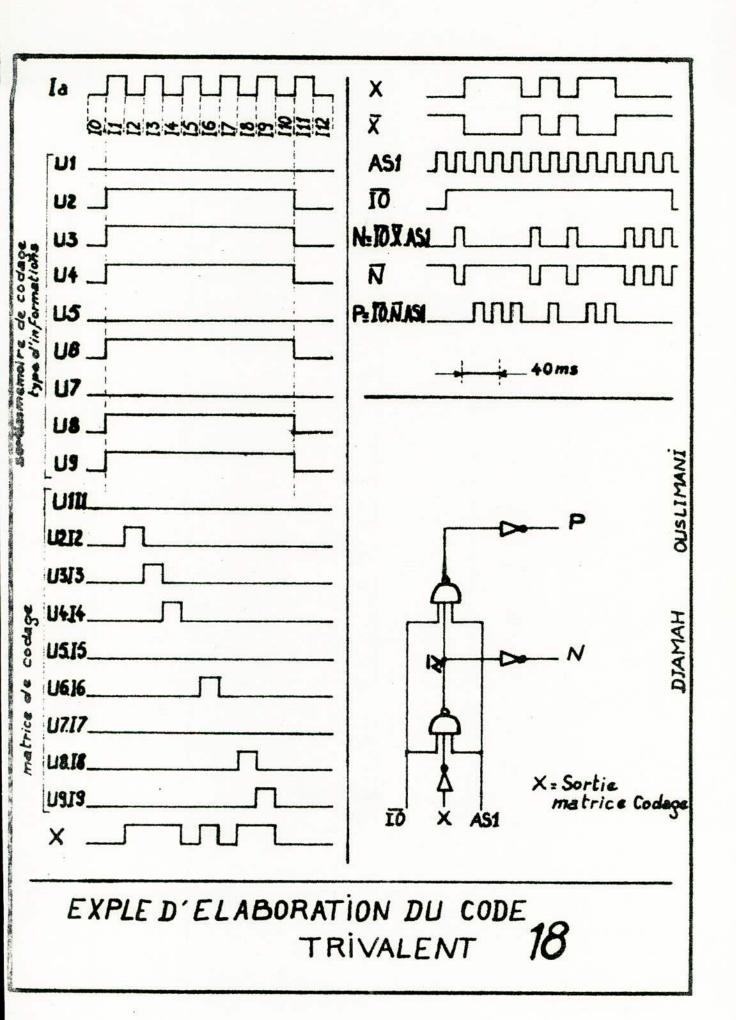

## 1111 -7 ELABORATION DU CODE TRIVALENT (Fig 18)

- Le côde de transmission utilisé est trivalent (voir caractéristique de transmission).

- Le côde obtenu en sortie de matrice de codage est appliqué sur 2 fils P et N à l'entrée de l'émetteur télégraphique. Le marquage du fil P provoque l'émission en ligne d'1 bit P, de même pour le fil N. L'absence simultanée d'exitation en des 2 fils se traduit par l'émission en ligne de l'état S.

- \* on a vu de plus que la phase d'émission d'1. bit d'information se fait en deux (2) sous phases égales. La première correspondant à l'émission de la fréquence centrale, l'autre à l'information proprement dite. Pour ce faire on utilisera des portes "AND" sous condition d'une bascule A delivrant un signal de période égale à la durée d'1 bit. La commande To permet la transmission de la fréquence centrale lors du bit debut de mot.

L'élaboration du contrôle trivalent est assurée par le circuit donné à la fig 18

#### 1 - INTRODUCTION

-Effectuer une mesure revient à prendre la valeur maximale du signal considéré. Si de plus on veut la transmettre à distance, on doit la convertir en un signal exploitable.

#### 2 -FONCTIONNEMENT

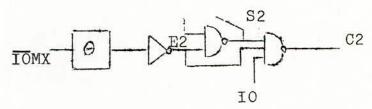

-Tout comme pour les signalisations, le choix de l'entrée mesure se fait par le biais du signal TOMX, qui détermine le rang du mot affecté au codage de la mesure dans le cycle de transmission, isst des circuits de sélection d'entrées.

Pour effectuer une mesure, on procéde en deux étapes:

- \* 1 étape de prélèvement de la valeur de la mesure qui se fera durant le signal IOMX .

- \* 1 étape de conversion de la valeur ainsi prélevée en un signal numérique, qui de ce fait ne débute qu'à partir du mot M (X:+1) suivant.

#### REMARQUE.

- La phase de conversion est variable suivant la valeur de la grandeur à mésurer, elle est cependant toujours inférieur à 8 mS.

#### 3 - CIRCUIT DE PRELEVEMENT DE LA GRANDEUR.

-Le prélèvement de la valent maximale de la mesure est éffectué par charge d'une "capacité réservoir".

Le problème est de ne charger cette capacité qu'au moment voulu et de la mesure choisie.

On a vu que le choix de la mesure est réalisé par le signal TOMX .

#### CONCLUSION:

-On doit donc avoir un circuit qui ne doit travailler qu'à TOMX et de plus doit réaliser la liaison des bornes de l'entrée choisie parmi d'autres avec les bornes de la capacité réservoir.

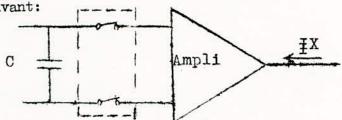

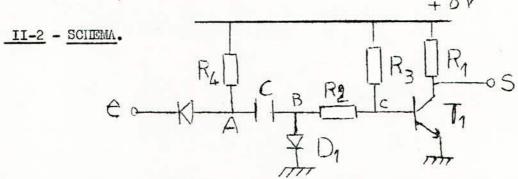

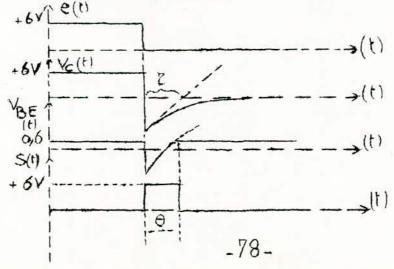

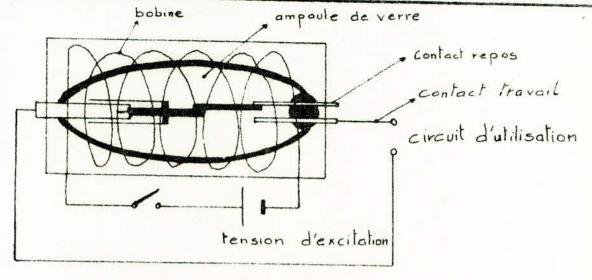

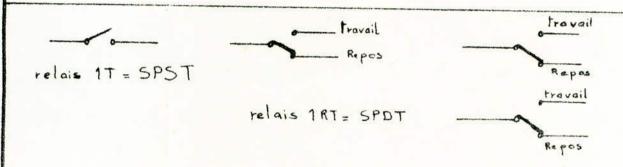

Un tel circuit sera chopper électronique équivalent deux relais électromagnétiques, commandé par le signal TOMX conformément au Schéma.

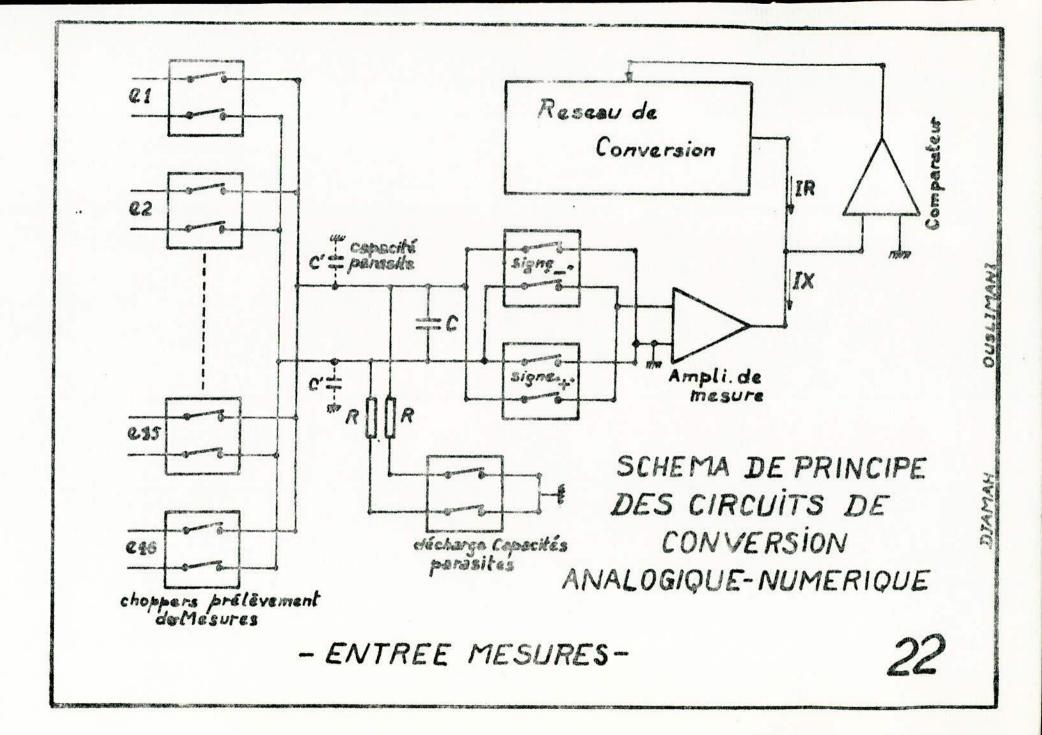

## 4 - DECHARGE DES CAPACITES PARASITES. (fig.22)

- Une fois la valeur de la grandeur prélevée, on entame la phase de conversion.

Durant cette phase, on génère un courant IX proportionnel à la tension aux bornes de la capacité réservoir, en appliquent cette dernière aux bornes d'un amplificateur de mesure.

Le courant IX dest ensuite comparé à un courant de référence variable IR délivré par des circuits qu'on verra plus loin.

#### - Un problème apparait:

En effet, en appliquant la capacité réservoir aux bornes. de l'amplificateur de mesure, l'une des extrémités de cette dernière sera à la masse d'où risque de décharge des capacités parasites disposées symétriques par par fapport au condendateur réservoir à travers de dernier. Ce qui aura pour effet de modifier la tension existant à ses bornes.

On a donc intérêt à décharger ces capacités parasites avant d'entamer la conversion.

Pour décharger une capacité il suffit d'appliquer l'une de ses bornes à la masse, or en faisant cela on décharge aussi la capacité réservoir.

- Pour surmonter ce problème, on va jouer sur les temps de décharge des différents condensateurs. En effet, la capacité réservoir est choisie telle que son temps de décharge soit trés élevé devant celui mes capacités parasites de façon à ce qu'elle n'ait pas le temps de se décharger sensiblement.

#### CONCLUSION:

- On doit réaliser un circuit qui va mettre les capacités parasites à la masse juste à la fin du signal TOMX et ce perdant un temps trés court(1,5mS). Or ces condensateurs parasites sont disposés symétriquement par rapport à la capacité réservoir.

Notre circuit va donc mettre alternativement à la masse l'une ou l'autre des bornes de la capacité réservoir de manière à permettre la décharge des capacités parasites.

Ce circuit sera unahopper électronique (voir annexe) commandé par une impulsion de durée 1,5mS et ayant lieu à la fin du signal TOMX.

Une telle impulsion est obtenue grâce à un retardateur(voir annexe) sous commande de IOMX .

On aura ainsi le schéma de figure. 22

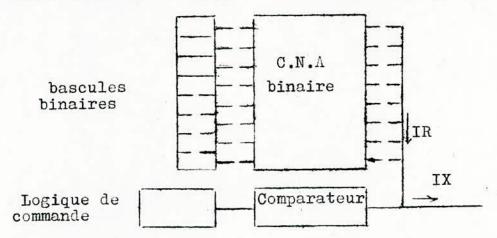

#### 5 - CONVERSION ANALOGIQUE - NUMERIQUE.

#### 5-1- PRINCIPE:

-La conversion consiste en la transformation du signal analogique correspondant à la grandeur prélevéeen un signal asmérique.

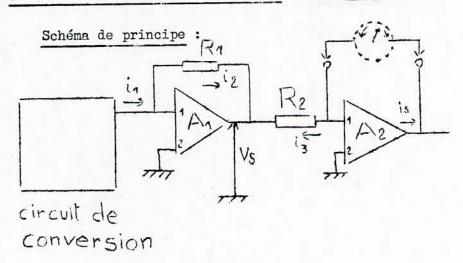

-Les circuits assurant cette transformation sont les convertisseurs analogiques.Numériques ou C.A.N dont le schéma de principe test donné en figur

Un courant IX proportionnel à la tension aux bornes de la capacité réservoir est comparé à un courant de référence IR proportionnel à une valeur mémérisúe contenue dans un registre binaire.

Op fait varier le courant IR jusqu'à équilibrer le courant IX au niveau d'un comparateur. A cet instant, la valeur numérique de IX est contenue dans le registre.

Ce type de conversion est dit à " Approximations Successived! .

## 5-1-1- GENERATION DU COURANT DE REMERENCE VARIABLE I.R . (fig.17)

- La production du courant de référence variable IR est assurée par un convertisseur Numérique - Analogique ou C.N.A.

••••/••••

#### -1-2 - PRINCIPE DU C.N.A.

- L'information numérique d'entrée est inscrite dans un registre binaire composé de 8 bascules.

Chacune de ces bascules va déterminer l'état ouvert ou fermé d'un commutateur selon que le nombre binaire dans la bascule vaut 0 ou 1 conformémént à la figure.

$$2^{x}$$

$\stackrel{E}{\longrightarrow}$   $\stackrel{R}{\longrightarrow}$   $\stackrel{IR}{\longrightarrow}$

Les valeurs relatives des résistances correspondent aux puissances successives de 2. La fermeture d'un contact provoque l'injection d'un courant inversement proportionnel à la valeur de la résistance associée, ces courants ont donc des valeurs qui correspondent aux poids binaires 128, 64, 32, 16, 8 4, 2, 1.

Au point commun des résistances du réseau, les courants des différentes branches sont additionnés, leur somme constitue le courant de référence IR.

- Les 8 bascules sont séparées en deux groupes de quatre, chaque groupe est cablé en compteur binaire à 16 positions:

- \* Le compteur d'Unités . C

- \* Le compteur de Seizaines. B

#### -1-3 - VALEUR DE LA RESISTANCE R .

La valeur de la résistance R dépend de la valeur pleine échelle" I" utilisée.

"I" va correspondre à n =  $2^8$  = 256 pour convertisseur à 8 bits . La valeur du quantum sera  $q = \frac{I}{256}$ .

Or le quantum correspond à la commutation du seul poids 2°, d'où:

$$\frac{E}{128R} = \frac{I}{256}$$

—)  $R = \frac{256}{128}$   $T$

- Les commutateurs sont constitués de transistors fonctionnant en offset (voir Annexe).

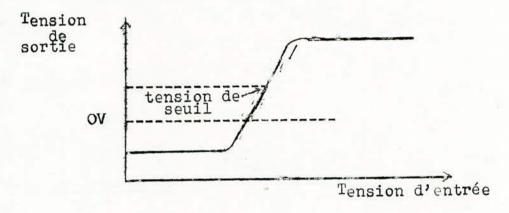

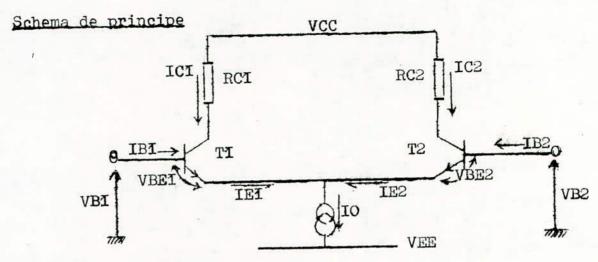

#### 5-1-4' - COMPARATEUR.

- C'est un amplificateur différentiel constitué de deux transistors appariés.

L'équilibre est obtenu lorsque les deux bases sont au même potentiel (0 V), c'est à dire lorsque les courants IR et IX sont égaux. (voir Annexe).

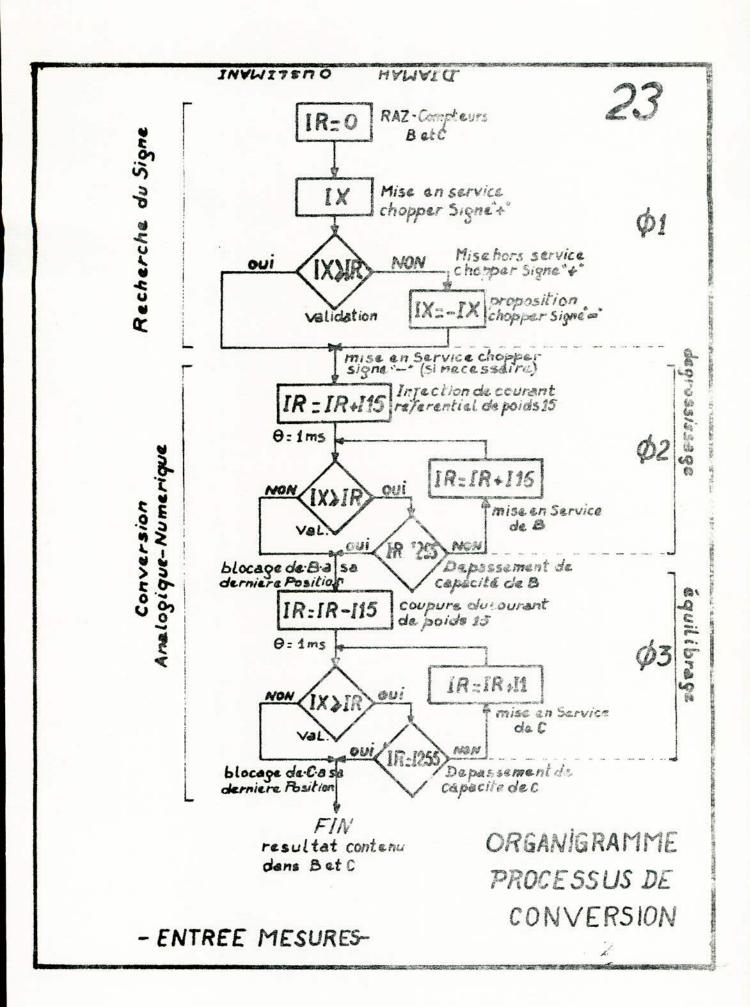

## 5-2 - PROCESSUS DE CONVERSION .NALOGIQUE - NUMERIQUE. (fig. 22)

- Le processus de conversion analogique- numérique peut se résumer suivant l'organigramhe de la Fig. 23.

-Comme note sur l'organigramme: ,la conversion Analogique-Numerique se fait en 3 (trois) phases successives:

- Ø1= phase de recherche du signe

-Ø2= phasede degrossissage

- Ø3=phase d'equilibrage

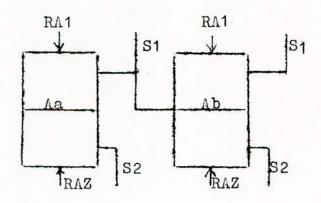

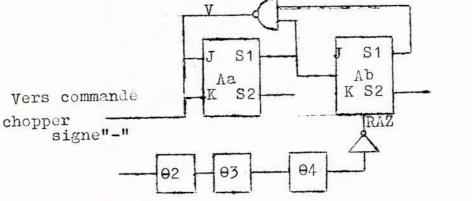

Le déroulement de ces opérations sera donc réglé par un compteur(A) à quatre positions possibles , donc constitué de deux bascules reperées par : 'Aa'et'Ab'

bascule Aa

bascule Ab

.../....\*

## 5-2-1/ - PHASE DE RECHERCHE DU SIGNE ( Ø 1)

-Cette phase va correspondre à la position de repos du compteur A.

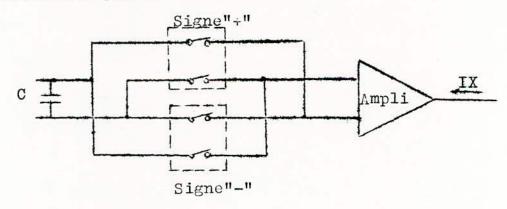

-On attaque le processus de conversion, en appliquant la tension aux bornes de la capacité réservoir à l'entrée d'un amplificateur de mesure délivrant un courant IX proportionnel à cette dernière.

Pour ce faire, on procède de la même manière que précedemment en utilisant un chopper électronique (voir nnexe) conformément au au schéma suivant:

Un problème surgit:

- Dans le cas où la tensjon aux bornes de la capacité réservoir est négative, le courant IX à la sortie de l'amplificateur de mesure aura son sens inversé de façon à ce qui an niveau du comparateur il s'ajoute au courant de référence IR. Le comparateur ne pourra plus détecter l'équilibre.

Pour y remedier on change le sens du courant IX en inversant les branchements des bornes du condensateur réservoir à l'ampli de mesure.

Cette nouvelle liaison est assurée par un autre chopper électronique qui doit se déclencher dés que le comparateur détecte une tension négative aux bornes de la capacité réservoir. En même temps, le chopper précedent est mis hors service.

Le schéma de principe sera le suivant:

#### REM\_RQUE/:

- On peut considérer ces opérations comme celles définissant le signe de la mesure. En effet, il suffit d'avoir à ce moment IR = 0. Si la grandeur est positive, le comparateur indiquera IX > IR donc IX > 0, dans le cas contraire il indiquera IX < IR donc IX < 0, et l'inversion des branchements de la capacité réservoir est réalisée.

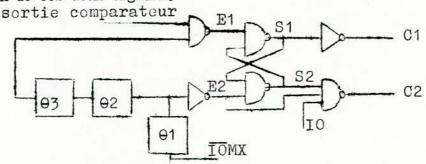

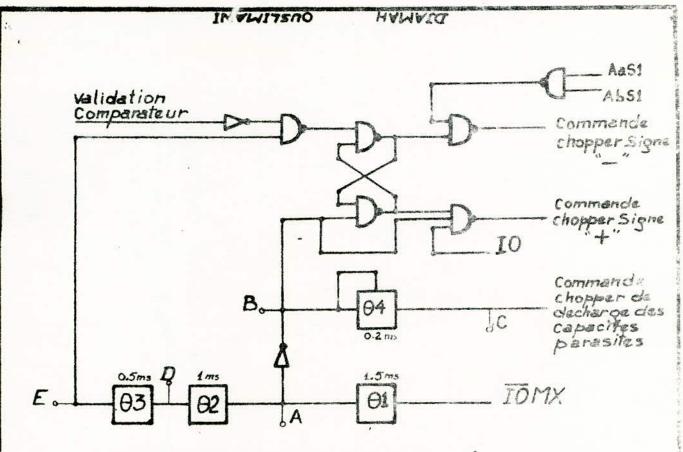

- Circuits de Commande du Signe (Fig.24..)

En vertu de ce qui a été dit, on doit élaborer un circuit qui:

- \* Au départ on met hors service les deux choppers signe.

- \* A la fin de la décharge des capacités parasites met en service le chopper signe " - " .

- \* Si le comparateur détecte une mesure négative, il y a proposition du signe " ", c'est à dire qu'on tient prêt le chopper signe" " sans pour autant le mettre au travail, tout en inhibant le chopper signe "+ ".

- \* Met au travail (si nécessaire) le chopper signe " " à la fin de la phase Ø 1 .

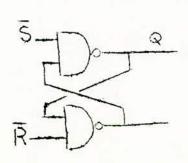

On voit que dans le cas d'une mesure négative, on doit réaliser un basculement entre les états des deux choppers signe. Ce basculement vera assuré par une bascule R-S formée de 2 portes "Nand" (voir Annexe) dont les sorties seront utilisées comme commandes des choppers signe.

#### Rappel:

- -Les choppers sont mis à l'état travail dés qu'un niveau bas(état 0) est appliqué à leurs commandes.

- -Avant le choix de l'entrée mesure, les choppers signes sont hors service: leurs commandes respectives sont au niveau haut (état 1).

Pour celà on doit avoir les sorties de la bascule à 1 toutes les deux ce qui est le cas si on applique l'état 0 aux entrées de cette dernière

Pendant la phase décharge des capacités parasites les choppers doivent rester bloquées, jusqu'à sa fin(1,5mS). A ce moment il ya mise en service du chopper correspondant au signe " + " tout en gardant le chopper signe " - " bloqué.

On se voit donc dans l'obligation d'inverser l'attaque de la bascule .

Or en faisant ceci, la sortie S2 n'est à 1 que durant la phase décharge des capacités parasites. C'est à dire que l'un des choppers signe commandé par S2 est à l'état travail avant et durant la phase sélection des entrées. Ce qui n'est pas autorisé.

Or, comme on l'a vu, les deux choppers doivent être bloqués avant la fin du signal décharge des capacités parasites: on introduit un inverseur au niveau de la sortie S1 conformément au schéma suivant:

Si on laisse le circuit tel quel, on remarque que quelque soit l'entrée E2 on a toujours S2 = 1. Et ceci même aprés la phase décharge des capacités parasites.

Pour surmonter ce problème, on va introduire une porte "NAND" qui sera sous condition de la sortie S2 et de l'impulsion IO qui n'est à l'état 1 qu'aprés le signal sélection de mot TOMX

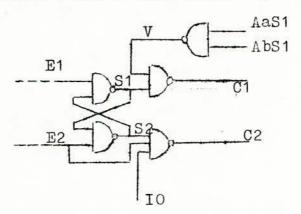

$$\begin{array}{c|c}

\hline

\text{mot } \overline{\text{IOMX}} & \underline{\text{S1}} & \underline{\text{C1}} \\

\hline

E2 & \underline{\text{S2}} & \underline{\text{C2}} \\

\hline

10 & \underline{\text{C2}}

\end{array}$$

On a ainsi les commandes des 2 choppers au niveau haut (état1)durant la phase sélection de l'entrée. Mais le chopper commandé par la sortie S2 de la basculs se met au travail dés le début de la phase IO ; c'est à dire pendant la phase décharge des capacités parasites. Ce qu'il ne faut pas .

Pour éviter ce cas, on inverse le signal à l'entrée E2 et on met la porte de commande du chopper C2 sous condition de cette dernière conformément au schéma suivant:

A la fin du signal décharge des capacités parasites, le chopper signe " + " doit se mettre à l'état travail. Sa commande est alors au niveau bas; ce qui est le cas pour la sortie C2 qui va ainsi constituer la commande du dit choppet.

La sortie C1 restant toujours à 1 assurera la commande du chopper signe"-".

A partir de cet instant, la capacité réservoir est branchée aux bornes de l'amplificateur de mesure. Le comparateur se met en service.

On donne un laps de temps (1 mS) pour la recherche du signe. C'est à dire que le basculement (si nécessaire) n'a lieu qu'aprés ce temps.

On doit donc élaborer un signal qui sera en fonction d'une impulsion ayant lieu 1 ms aprés l'impulsion décharge des capacités parasites, et du signal validation délivré par le comparateur. Ce signal comme dit auparavant, doit faire basculer les états des chappers: Il sera appliqué en E1 qui était à l'état 1 et donc passenuà l'état 0. Pour ce faire, il suffit de mettre la porte de sortie E1 sous condition de ces deux signaux.

On a vu que le branchement du chopper signe "- " n'a lieu qu'à la fin de la phase recherche du signe, donc au début de la phase dégrassissage. Pour concretiser celà il suffit de mettre la porte de commande du chopper signe " - " ( de sortie C1) sous condition du signal délimitant la phase recherche du signe.

Ce signal est donc celui correspondant à l'état repos du compteur A .

Un tel signal est obtenu à la sortie d'une porte " NAND" sous conditions des sorties Aa S1 et Ab S2 .

Ce qui nous mène à prendre l'état 11 comme état de repos du compteur A.

A la fin de la phase recherche du signe, on doit avoir C1 = 0 - donc V = 1. Ce qui nous mène à n'utiliser que les états C1 et C1 du compteur A pour la phase conversion.

#### REMARQUE:

Une fois le chopper signe " - " branché, quelque soit l'état du comparateur, C1 est toujours à l'état 0 . En effet c'est S2 = 0 qui détermine l'état de C1 .

## 5-2-2/- PHASE DE CONVERSION ( Ø 2 et Ø 3) (fig.25)

- Elle s'effectue en deux sous phases successives:

\*Sous phase Ø 2 de degrossissage qui consiste en la détermination de l'ordre de grandeur de la mesure c'est à dire: mesure infémieure ou supérieure à une valeur référentielle.

Cette sous phase va correspondre à l'état 01 du compteur A.

\*Sous phase Ø5 d'equilibrage quiconsiste à déterminer la valeur éxacte de la mesure. Cette sous phase correspondra à l'état 10 du compteur A.

## 5-2-2-1/- SOUS PHASE DE DEGROSSISSAGE ( Ø 2)

- L'opération de dégrossissage est éffectuée par comparaison de la mesure IX prélevée, à un courant réferentiel IR correspondant au poids 15.

- Cette sous phase va correspondre à l'état 01 de " A " .

- -On se voit donc dans l'obligation de mettre d'abord le compteur A à l'état requis (O1) et ceci par remise à Zéro forcée de la bascule Ab juste à la fin de la phase recherche du signe.

A ce moment on aura V = 1 -> le chopper signe " - " (si nécessaire) est branché - Le processus de conversion commence.

On a vu que la conversion commence par comparaison de la mesure à un courant de poids 15.

On doit donc élaborer un circuit supplémentaire qui dés que le compteur A est à l'état 01, va prinduire un courant IR de poids 15: Ce sera un transistor fonctionnant en "Offset" (voir Annexe). Commandé par la sortie S2 de la bascule Ab alors est à 1.

Deux cas peuvent se présenter au niveau du comparateur:

- \* IX > IR

- \* IX < IR

Avec IR de poids 15.

#### Cas IX > IR.

-Le poids de IX est supérieur ou égal à 15.

Une fois débloqué, le compteur B va progrésser au rythme d'ume horloge locale(10 Khz). Et ceci judqu'à avoir le cas suivant:

#### IX < IR.

Dans ce cas le comparateur va délivrer une validation qui doit:

- \* Mettre hors service l'étage supplémentaire de poids 15.

- \* Bloquer le compteur B à sa dernière position.

- \* Mettre en service le compteur C d'unités.

## 5-2-2-2/- SOUS PHASE D'EQWILIBRAGE ( Ø 3)

- -Cette sous phase consiste à équilibrer d'une manière plus précise les courants IX et IR .

- Mise hors service de l'étage de poids 15: Elle est réalisée par mise à l'état 0 de la sortie S2 de la bascule Ab.

Pour ce faire il suffit de faire avancer le compteur à sa position suivante (état 10), par l'intermédiaire du signal validation du comparateur, qui va aindi jouer le rôle d'horloge pour le compteur .

- Le blocage d'un compteur à sa dernière position est réalisé par mise à Zéro (0) des deux entrées de sa lère bascule. Cette mise à Zéro sera assurée par la sortie S2 de la bascule Ab.

- La mise en service du compteur C d'UNITés sera assurée par la sortie S2 qui alors doit être à 1.

Cette sortie sera appliquée aux 2 entrées de C qui alors va compter au rythme de l'horloge locale ( 10 Khz).

## 5-2-3 / - CIRCUITS DE CONVERSION.

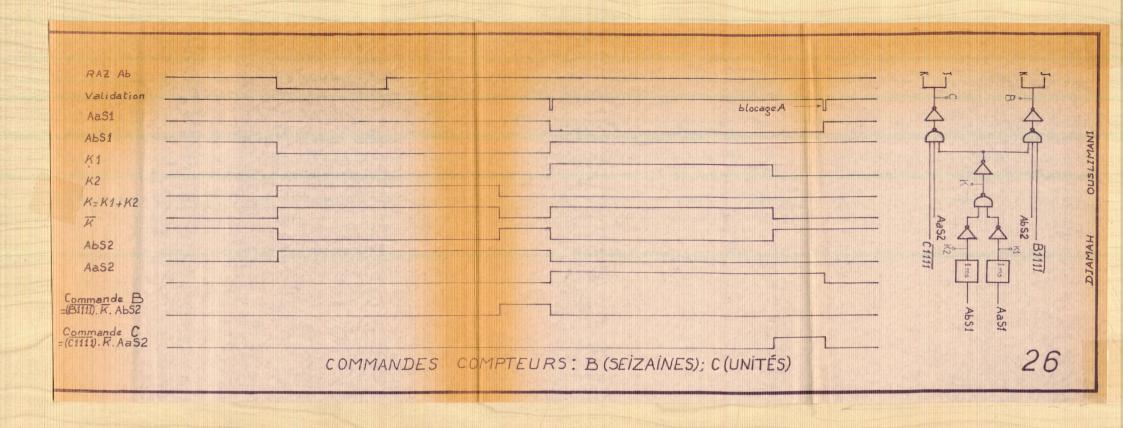

## 5-2-3-1/- RECAPITULATION - COMMANDES DES COMPTEURS B et C (Fig. 26.).

- On vient de voir qu'à l'état de repos (11) du compteur A, les compteurs B et C sont à Zéro et bloqués. Blocage assuré par les sorties S2 des bascules Ab et Aa.

- Le déblocage de B se fait à l'état 10 de A par le biais de la sortie S2 de Ab De plus ce déblocage se fait 1 mS aprés la mise à l'état 01 du compteur A.

- Le déblocage de C est réalisé par le biais de la sortie S2 de Aa à l'état O1 du compteur A , et ceci 1 mS aprés la mise à son nouvel état de A .

#### REMIRQUE:

Un autre cas, dans la conversion de la mesure est à considérer: cas où IX est supérieur à la capacité maximum que peuvent affichérles compteurs B et C . Il faudrait alors afficher l'état 1 sur toutes les bascules de B et C (soit la valeur 255). Car dans ce cas, le comparateur ne donne plus de signaux de validations.

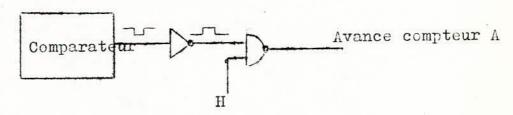

## 5-2-3-2/- COMLANDE DU COMPTEUR A. (fig.17)

- Le compteur A doit avancer d'un cran, à partir de l'état 01, dés qu'un signal validation est délivré par le comparateur.

Ce signal va donc donstituer l'horloge de 1.

Pour que le compteur réagisse au début du signal horloge il importe d'avoir un signal validation correspondant à l'état O. C'est à dire:

- \* Tant que IX > IR (absence de validation) la sortie du comparateur est au niveau haut.

- \* Dés que IR > IX (validation); la sortie du comparateur se met au niveau bas.

- Il faut, de plus, synchroniser les compteurs Λ; B et C.

Ces deux derniers étant attaqués par une horloge locale H= 10 Khz, on

se voit dans l'obligation d'utiliser pour Λ une horloge de même fréquent

Une première approche du circuit de commande du compteur 1 est donnée

par la figure suivante.

.../...

Ainsi le Signal validation (IR > IX), n'est pris en compte que lors d'une impulsion d'horloge locale, à partir de son front montant. En même temps, le compteur A bascule de l'état 01 à l'état 40, ce qu'à pour effet la mise hors service de l'étage délivrant le courant correspondant au poids 15 et le blocas du compteur de seizaines à sa dernière position. A ce moment IR = IR- I15 et on aura IX > IR (voir organigramme figure 23).

La smrtie du comparateur se remet à 1 entrainant l'annulation de la validation.

- La forme du signal validation est étroitement liée au type d'éléments utilisés et éssentiellement au comparateur qui est un organe analogique (amplificateur différentiel à transistors appariés. Voir (Annexe) qui peut être source d'erreurs (temps de réponse, de montée, de descente) causant une modification du signal "Horloge" de A.

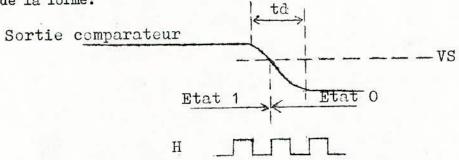

En effet, le comparateur ne pouvant être parfait, le signal validation est de la forme:

- A cause du temps de descente et de la tension seuil de basculement des portes logiques, on risque d'augmenter le courant IR d'un palier aprés le signal validation, ceci parcequ'une deuxième impulsion horloge locale(10Khz) peut intervenir avant que le signal validation ne soit pris en compte.

La

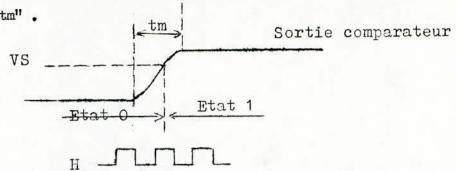

- Une fois, la validation prise en compte, sortie du comparateur se remet à l'état 1, mais cette fois-éi avec un autre retard correspondant au temps de montée "tm".

- A cause de ce temps de montée de la tension seuil de basculement des portes logiques, on risque d'avoir deux signaux de basculement du compteur A pour une seule validation.

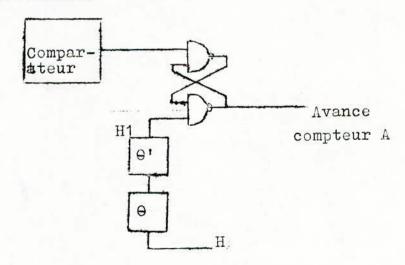

- -- Pour parer à ces effets on modifie le circuit comme suit:

- \* On retarde le signal délivré par l'horloge locale avant de l'appliquer à la porte de commande du compteur A de façon le front montant de l'impulsion correspondant à la dernière position du compteur B ait lieu au lelà de VS (tension seuil de basculement des portes logiques) (30 mS).

- \* La sortie du comparateur sera reliée à l'entrée d'une bascule formée de 2 portes "NAND" servant à comfirmer l'état de la sortie du comparateur.

- \* Le signal validation sera de courte durée (10 ms). On aura ainsi le circuit suivant:

De cette façon, on donne au comparateur, le temps d'éffectuer la comparaison d'une façon éxacte avant d'effectuer le blocage des compteurs, ce dernier n'ayant lieu qu'à peu ptés au milieu du dernier état du compteur en cours de fonctionnement.

#### REMARQUE:

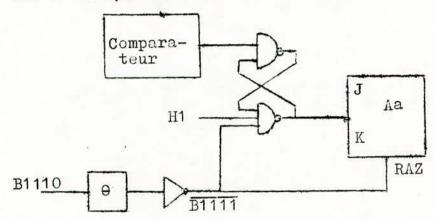

On a vu qu'un cas de dépassement de capacité peut se présenter (IX) poids 255). Il faut alors bloquer le compteur B a sa position extrémale (état 1111) et mettre hors service l'étage délivrant un courant de poids 15.

Pour réaliser ces deux opérations, il suffit de faire basculer le compteur la la fin du signal B 1110.

Pour ce faire, on utilisera le circuit suivant:

- Le cablage sortie inverseur entrée porte commande horloge A, est réalisé afin d'interdire toute validation durant 200 ps du signal B 1111.

- Le dépassement de capacité du compteur d'Unités est contrôlé par le signal C 1111.

#### P . S:

Dans le cas du dépassement de capacité du compteur B, on n'utilise pas le signal B 1111 pour la remise à Zéro de la bascule Ad, car on risque d'avoir des perturbations lors de la remise à 1 de cette dernière (état de repàs de A.)

Le mircuit final de commande du compteur A est donné à la figure 17.

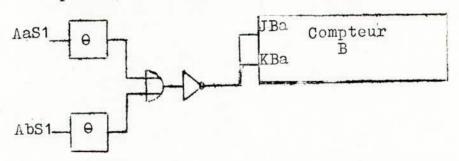

## 5 - 3/ CODAGE DU RESULTAT/:

-A la fin de la phase d'équilobrage, le nombre binaire qui représente la valuur de la mesure est disponible dans kes compteurs B et C et le signe est contenu dans la bascule du circuit de commande des choppers signe.

Ces informations doivent être introduites dans la mémoire de codage avant de les transmettre (voir circuits communs émission).

La mise en mémoire de ces informations va s'effectuer à la fin du signal 10 (début de mot) et ce pendant 1 mS.

On doit donc élaborer une impulsion qui n'aura lieu qu'à la fin du signal IO et de durée 1 mS. Ce sera le signal autorisation de transfert.

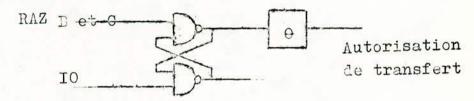

Pour ce faire, on utilisera le circuit suivant:

#### REMARQUE:

Les compteurs B et C, ne sont remis à Zéro qu'aprés le signal IOMX correspondant à l'introduction de la mesure à éffectuer. Tant que ce signal ne se présente pas( c'est à dire durant qu'on s'occupe des autres mesures) les compteurs gardent leurs informations, alors que le signal IO est présent au début de chaque mot. Ce qui nous mène à utiliser une bascule R-S dont l'une des entrées est sous condition de IO, l'autre sous dondition de la R.A.Z des dompteurs, Ainsà le signal autorisation de transfert, des informations contenues dans les compteurs et de signe, vers la mémoire de codage n'est présent qu'à la fin de IO correspondant à la phase de conversion de la mesure en cours et elle seule, et ceci par remise à Zéro du bistable (ce bistable est systématiquement mis dans l'état 1 au début de IO par la R.m.Z de B et C.

Le transfert des informations se fera par le biais de 9 portes "NAND" respectivement sous condition des differents etats des bascules formant les compteurs B et C et de la bascule du circuit de commande des choppers signe, et du signal autorisation de transfert précédemment élaboré.

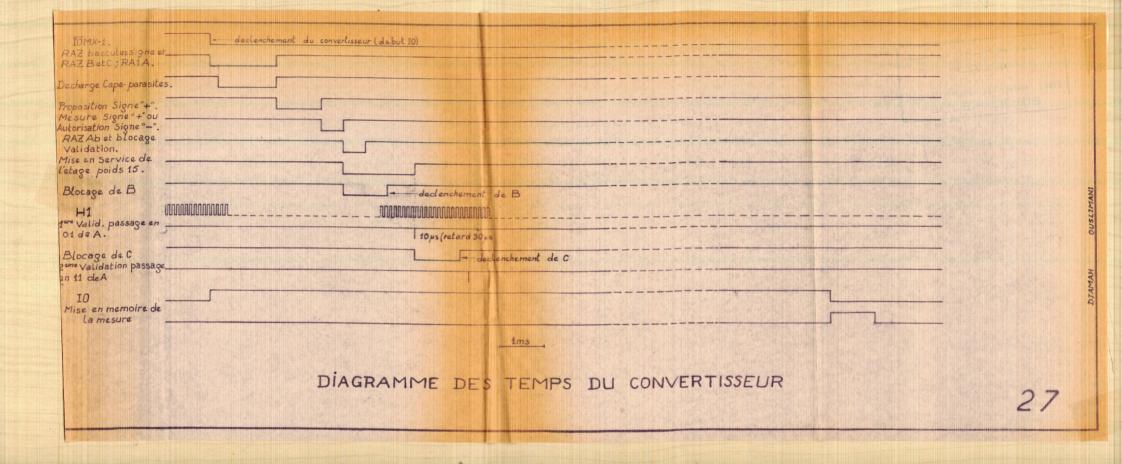

Le diagramme des temps du convertisseurs est donné en figure huméro 27.

# COMMANDES CHOPPERS SIGNE ET DECHARGE DES CAPACITES PARASITES

24

B = Position du Compteur B C = Position du Compteur C

EXEMPLE DE DETERMINATION DE LA VALEUR ABSOLUE D'UNE MESURE

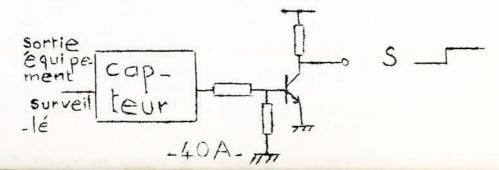

#### III- 3/- ENTREES SIGNALISATIONS.

#### I /- INTRODUCTION.

- Une signalisation est une information d'état d'un équipement donné, d'une station donnée.

Le signal signalisation sera donc à deux niveaux:

- \* Niveau haut pour le cas où le signal délivré par le bloc surveillé

est supérieur ou égal au niveau requis.

- \* Niveau bas pour le cas où ce signal est inférieur au niveau requis.

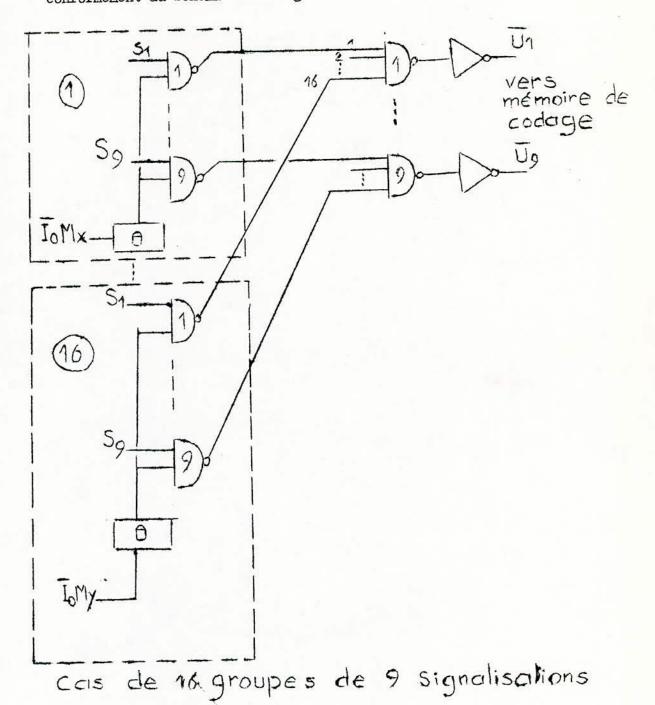

- Les signalisations sont émises par groupes de neuf(9), constituant les 9 bits informations

#### II/- CHOIX DU GROUPE DE SIGNALISATIONS.

- Le signal IOMX issi des circuits de selection d'entrées, vus ultérieurement(voir citcuits communs émisssion), va permettre le choix d'un mot du cycle affecté à un groupe de 9 signalisations.

- Le signal IOMX est arriqué à l'entrée d'un retardateur qui va décaler le signal sélection d'un mot entier. C'est à dire que le retardateur n'est déclenché qu'à la fin du signal TOMX; au début du mot suivant MX+1.

Ceci a pour effet de déceler d'un rang le numéfo du mot en cours duquel l'information sélectionnée sera transmise.

#### Exemple:

- Pour transmettre un groupe de signalisations dans le mot 14, il faudra relier l'entrée du retardateur de sélection au fil IOM 13 sur lequel apparait le décodage du mot 13.

#### Remarque:

- Cette particularité est due au principe de fonctionnement des circuit d'antrées des mesures (voir entrées mesures).

#### III/- PREMEVEMENT DE L'ETAT DES EQUIPEMENTS SURVEILLES.

-Le prélèvement de l'état de l'équipement surveillé se fait à l'aide de capteurs délivrant en sortie un signal électrique continu proportionnel au signal à leur entrée.

Le niveau continu ainsi obtenu est appliqué à la base d'un amplificateur délivrant des créneaux S de niveau adéquat. Ces créneaux S vont constituer les bits d'information.

Les crénaux S élaborés sont alors appliqués aux circuits d'entrées signalisation.

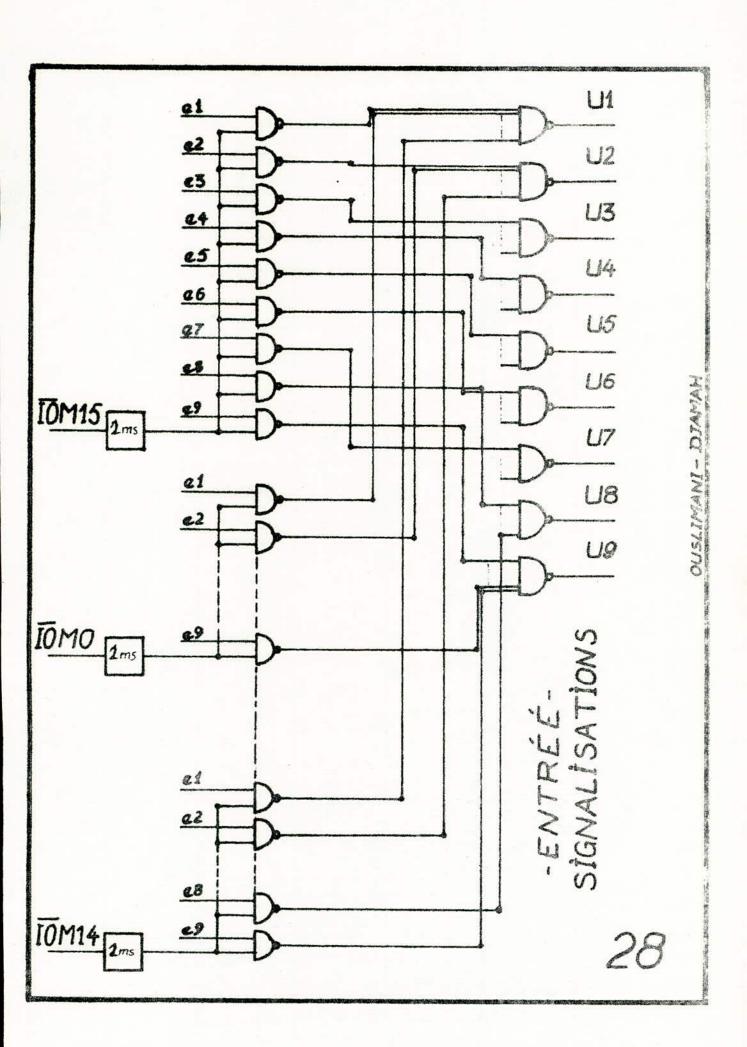

## IV/- CIRCUITS D'ENTREES SIGNALISATIONS.

En vertu de ce qui a été dit ultérieurement, les circuits d'entrées signalisations sont sous condition des états des équipements considérés et du signal sélection IOMX correspondant.

Ces circuits seront principalement constitués de portes logiques "NAND" conformément au schéma de la Fig:

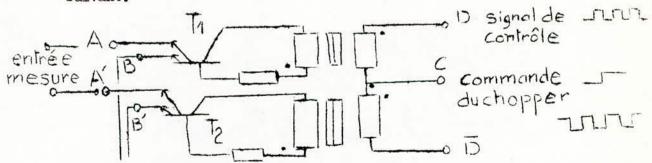

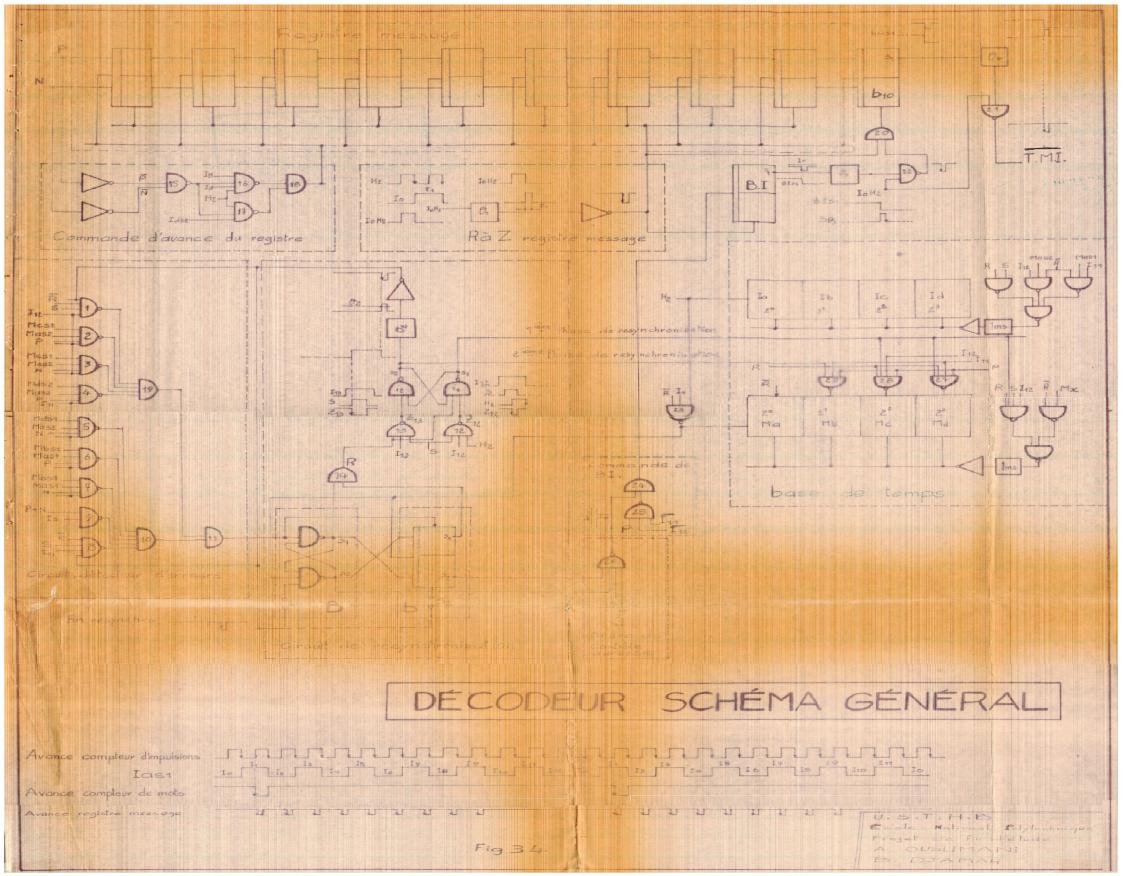

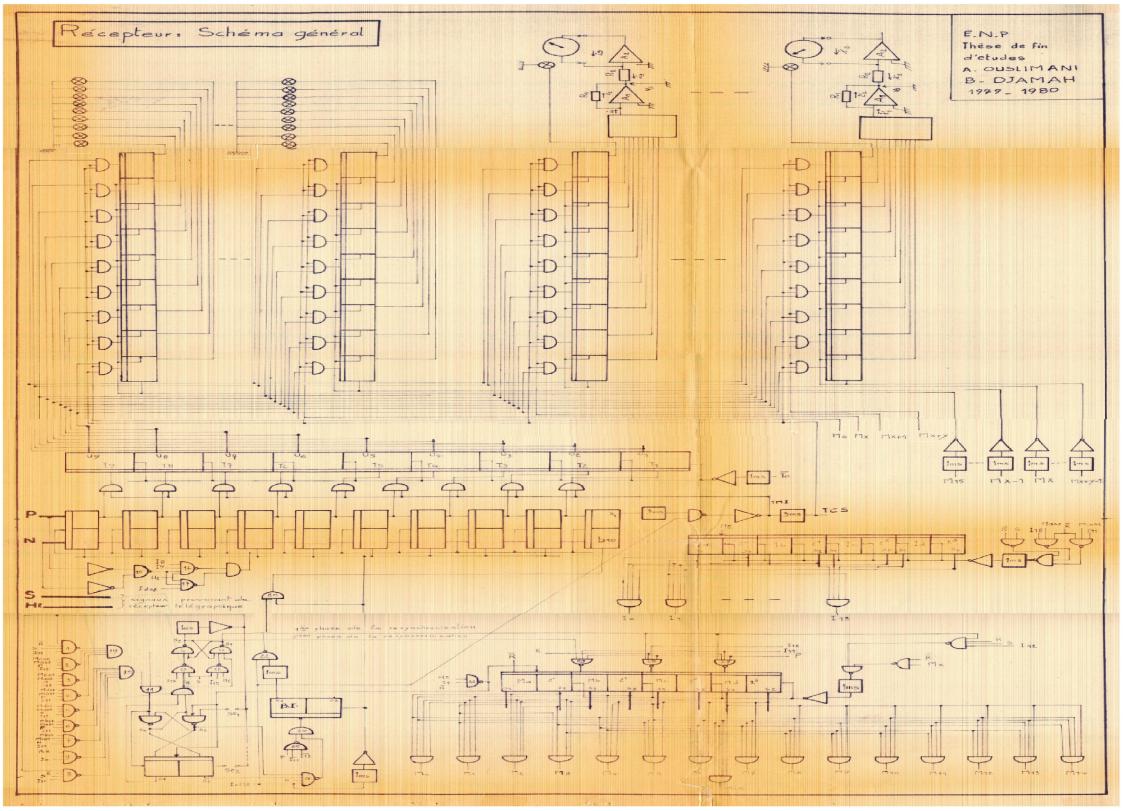

#### PARTIE 2 : RECEPTEUR SYNOPTIQUE GENERAL :

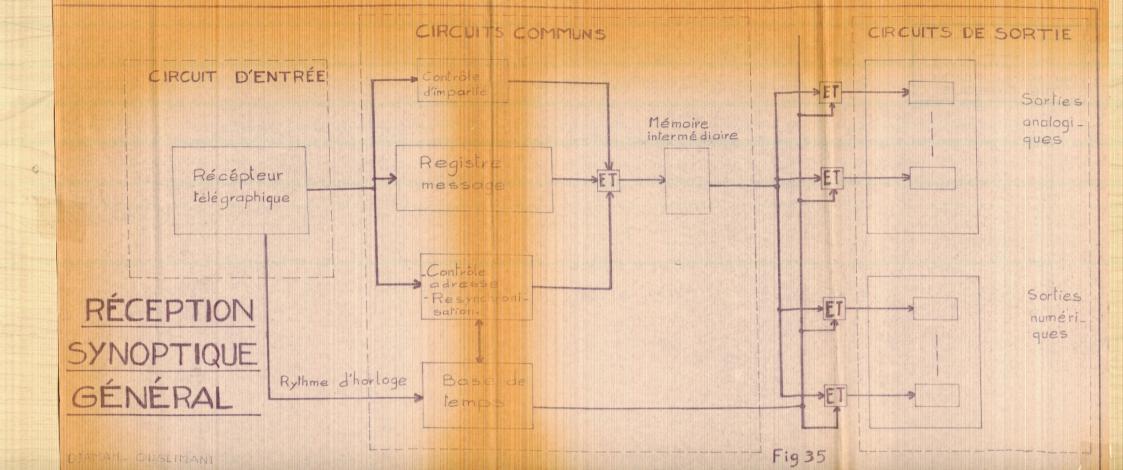

Les méssages sont reçus par le récépteur télégraphique. Celui-ci exécute, le filtrage, la correction, l'amplification, la détection et la synchronisation des bits.

Les signaux délivrés par le récépteur télégraphique (circuit d'entrée) attaque le décodeur (base de temps locale, registre méssage, contrôle d'adresse et resynchronisation, contrôle d'imparité).

Le décodeur délivre le méssage contrôlé à la mémoire intermédiaire qui sous l'ordre de transfert et de sélection le passe au circuit de sortie correspondant ( sorties signalisations, sorties mesures ).

#### I - RECEPTEUR TELEGRAPHIQUE :

#### I - 1 - SYNOPTIQUE :

Le récépteur télégraphique comprend les éléments suivants :

- 1 Transformateur d'isolement.

- 2 Amplificateur coupleur.

- 3 Filtre passe-bande.

- 4 Amplificateur écrêteur.

- 5 Ligne d'affaiblissement.

- 6 Circuit de contrôle de niveaux.

- 7 Discriminateur.

- 8 Synchronisateur de bits.

Les éléments 1, 2, 3, 4, constituent le circuit d'entrée du récépteur télégraphique. Les éléments 1, 2 assurent l'adaptation d'impédance, celle-ci doit rester constante dans toute la bande ( 300 HZ - 3.400 HZ ). Les signaux filtrés attaquent l'entrée d'un amplificateur écrêteur. Ce dernier comme son nom l'indique permet d'écrêter les niveaux élevés du signal reçu. Au niveau des circuits de contrôle, si les niveaux des signaux reçus sont faibles en valeur absolue, c'est à dire inférieurs à un certain seuil de référence, un circuit de commutation permet à la fois de déclencher l'alarme et d'interdire le passage des impulsions au circuit suivant.

Dans le cas contraire, cas où le niveau du signal est jugé bon, les signaux reçus attaquent l'entrée du discriminateur.

.../...

Celui-ci se compose de deux circuits résonnants du type série dont l'un est accordé sur la fréquence f 0 + △ f et l'autre sur la fréquence f 0 - △ f, f 0 étant la fréquence centrale émise correspondant à l'état N = 0 ; P = 0, c'est à dire l'état S qui est le signal début de mot.

f

$$0 + \triangle$$

f correspond à l'état  $N = 1$  et  $P = 0$ .

f  $0 - \triangle$  f " "  $N = 0$  et  $P = 1$ .

- Un redresseur à double alternance.

- Un filtre passe-bas du type RC, qui suit chaque redresseur. Ce filtre **6li**mine les résidus des porteuses présents après détection et améliore la discrimination.

Les deux tensions redressées Vp et Vn attaquent deux circuits de commutation qui créent alors les impulsions P, N, et S.

#### Nota:

Des cirquits de correction permettent de tenir la fréquence f 0 proche de la valeur théorique.

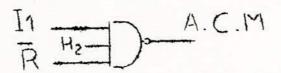

Les impulsions délivrées par le discriminateur sont recueillies par le circuit de synchronisation. Celui-ci permet de fabriquer des impulsions fines. Il contient un multivibrateur synchronisé par les impulsions du code reçu. Ce multivibrateur délivre le signal d'horloge H<sub>2</sub> qui commande la base de temps des circuits communs.

Le circuit de synchronisation permet aussi la remise en forme des signaux reçus.

#### CONCLUSION :

Le récépteur télégraphique délivre trois signaux P, N, S formant 12 cycle transmis, plus un signal H<sub>2</sub> servant d'horloge pour tout le système.

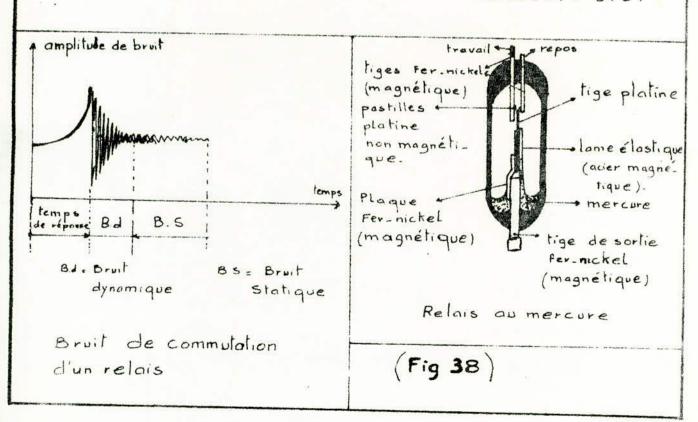

II - CIRCUITS COMMUNS : ( Voir schéma général ) Fig. 34

\_\_\_\_\_ 0 \_\_

II - 1 - BASE DE TEMPS LOCALE :

II - 1 - 1 - COMPTEUR D'IMPULSIONS :

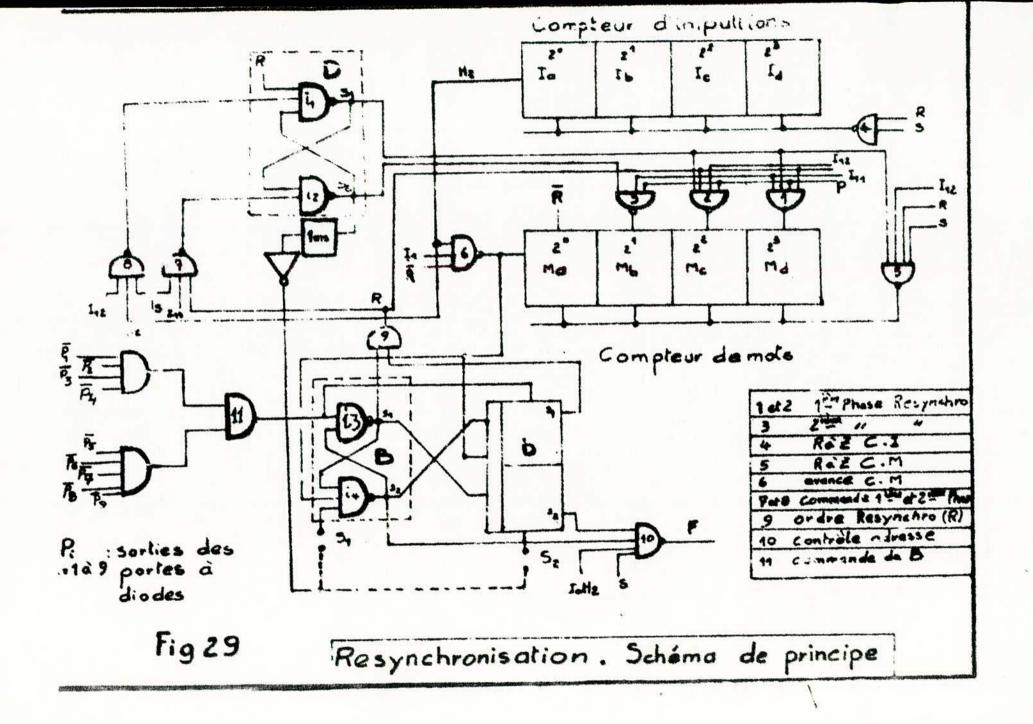

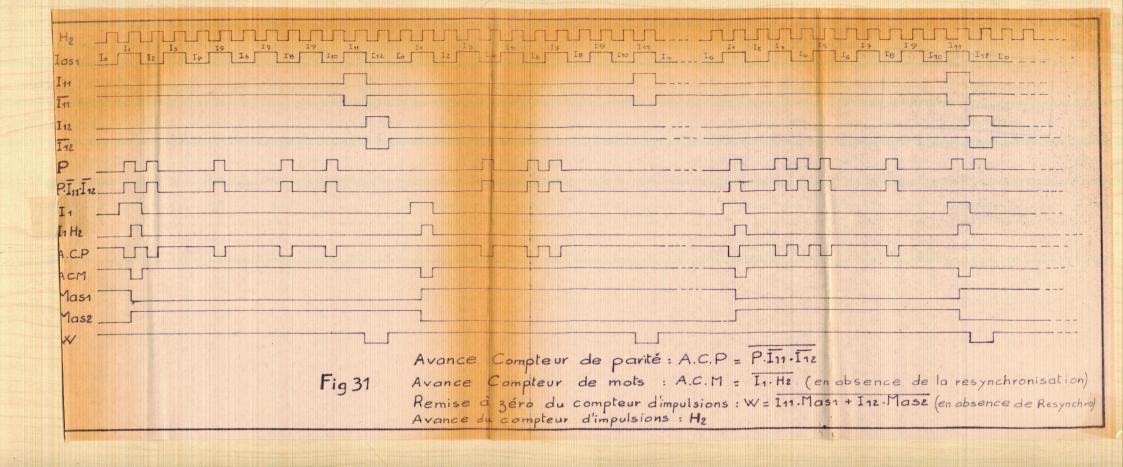

Chaque mot transmis par l'émetteur, contient selon qu'il est pair ou impair, 12 ou 11 bits, plus un bit de début de mot. Le compteur d'impulsions doit donc fournir 13 impulsions de I o à I 12 dans le cas d'un mot pair, et 12 impulsions de I o à I 11 dans le cas d'un mot impair. Ceci nécessite au minimum 4 bascules. La commande d'avance du compteur d'impulsions est effectuée par les signaux d'horloge H 2 ; délivrés par le multivibrateur du récépteur télégraphique.

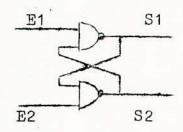

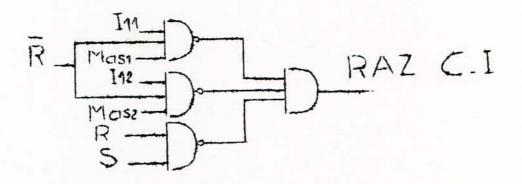

## - CIRCUIT DE REMISE A ZERO DU COMPTEUR D'IMPULSIONS :

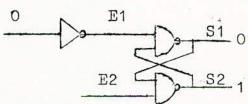

En absence de la resynchronisation, c'est à dire quand le méssage ne comporte pas une adresse fausse, dûs à une supression ou une inversion d'un bit, la remise à zéro est donnée par le schéma logique suivant :

.../...

Où Ma  $S_1$  = sortie 1 de la bascule du plus faible poids du compteur de mot.

Ma  $S_2 = \overline{Ma} S_1 = \text{sortie } S_2$  de la bascule de poids 2° du compteur de mots.

I<sub>11</sub> délivré quand le **compteur** d'impulsion arrive au nombre binaire 1011.

$I_{12} = I_{11} + 1.$

Ce compteur est de type asynchrone, chaque état de la bascule d'un étage joue le rôle d'une horloge pour la bascule suivante.

#### - ROLE DU COMPTEUR D'IMPULSIONS :

Ce compteur délivre des impulsions Io à I<sub>12</sub> (mot pair) Io à I<sub>11</sub> (mot impair). Chaque impulsion a, comme à l'émission, une durée de 40 ms soit 2 fois la durée de l'impulsion d'horloge H2. Ces impulsions permettent la vérification du synchronisme. En effet, l'impulsion Io est présente quand le signal début de mot S transmis par l'émetteur est lui aussi présent.

Ce compteur d'impulsions commande l'avance du compteur de mots.

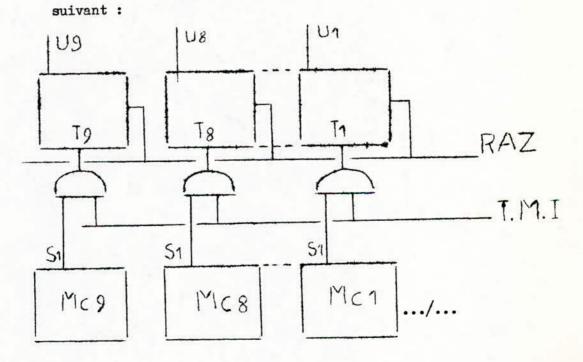

#### II - 1 - 2 - COMPTEUR DE MOTS :

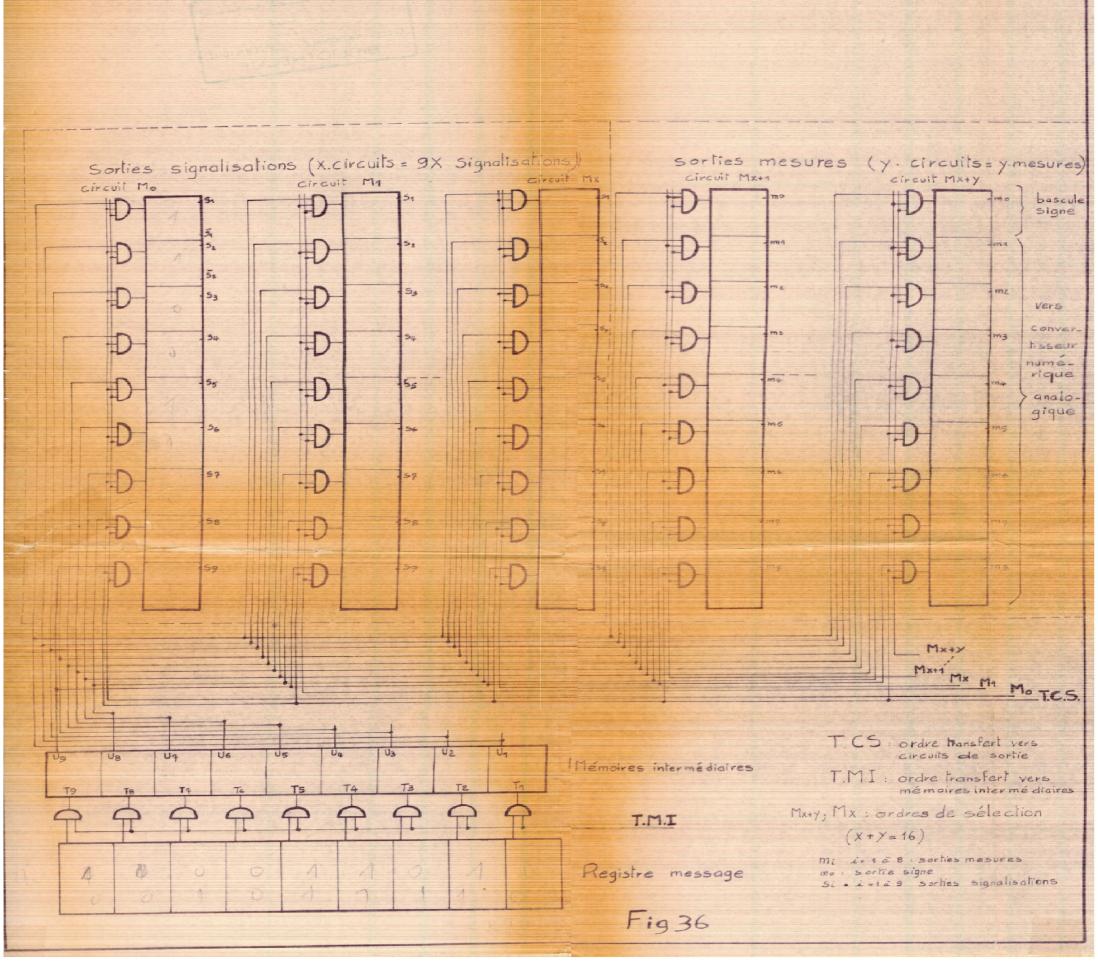

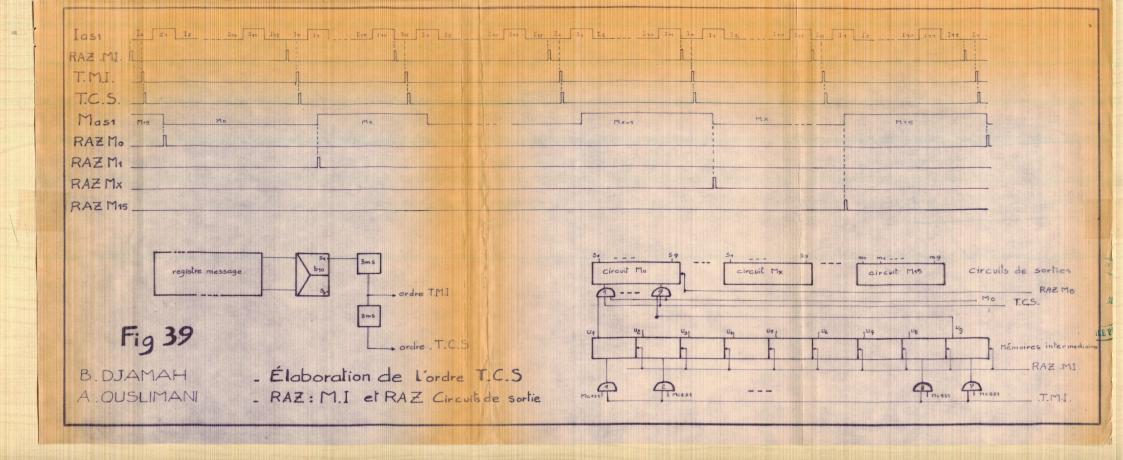

Les informations transmises étant du type cyclique chaque cycle contient au moins deux mots. Comme l'émetteur possède une capacité de 16 mesures ou de 144 signalisations, le nombre de mots maximum est donc 16. Ce compteur doit donc avoir 4 bascules, ce qui permet de compter de Mo à M<sub>45</sub>.

Comme la longueur du cycle est variable suivant l'utilisation, un strapp est prévu pour fixer le nombre de mots utilisés ( ce nombre est <u>(</u> 16 ).

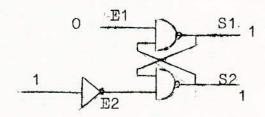

# - CIRCUIT DE COMMANDE D'AVANCE DU COMPTEUR DE MOTS : (Voir fig. 34 porte

La partie supérieure de l'impulsion I<sub>1</sub> délivrée par le compteur d'impulsion (I<sub>1</sub> H<sub>2</sub>) joue le rôle d'horloge pour le compteur de mots. Ce compteur est de type asynchrone.

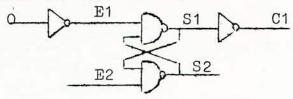

En absence de la resynchronisation le circuit de commande d'avance est :

#### - MISE A ZERO DU COMPTEUR DE MOTS :

Alla fin de la longueur du cycle choisi le compteur de mots doit reprendre son état initial.

Si  ${\tt M}_{{\tt X}}\,$  est le dernier mot du cycle, le circuit de R à Z est :

En absence de la resynchronisation  $R = o \Rightarrow -R = 1$

#### REMARQUE :

Il y a un décalage de temps entre la R à Z du compteur d'impulsions et la commande d'avance du compteur de mots ce décalage correspond à 60 ms ( Io +  $I_{\frac{1}{2}}$  )

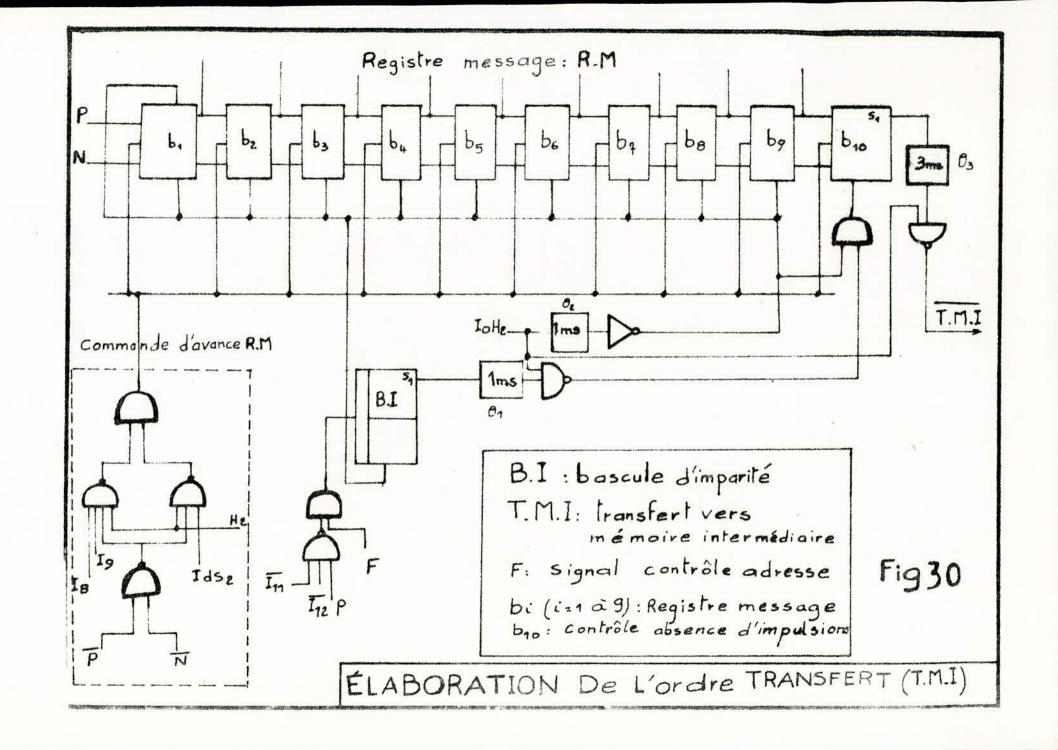

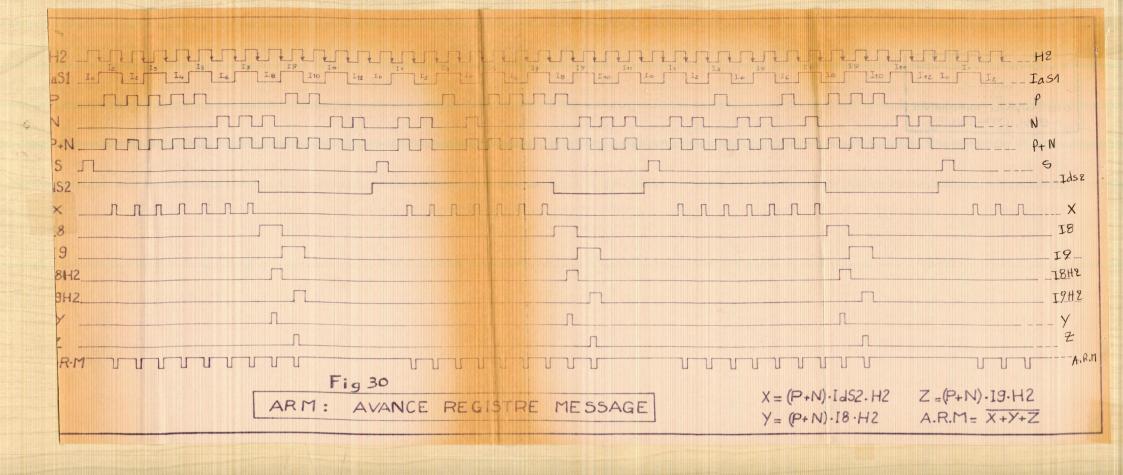

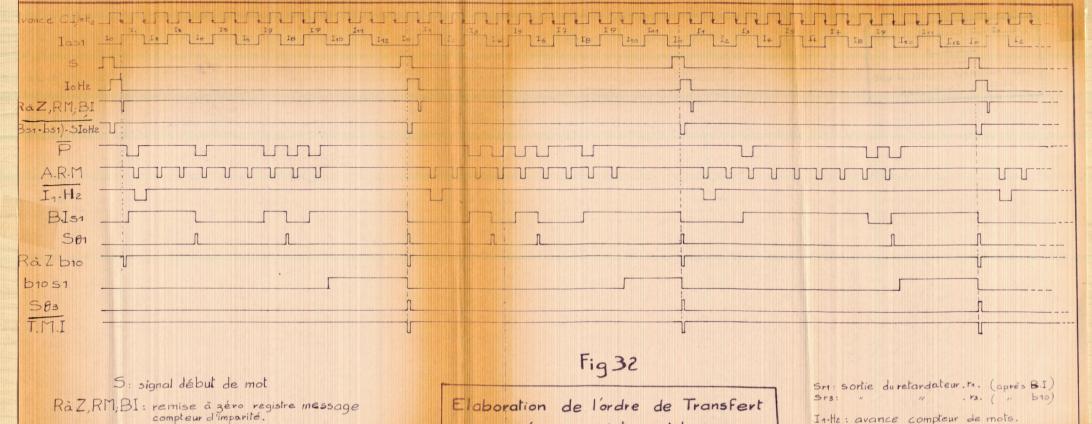

II - 1 - 3 - REGISTRE MESSAGE: 1934

En absence de toute détection d'erreur, l'impulsion début de mot S est reçu en Io du compteur d'impulsions, la lière impulsion d'information en  $I_1$ , la 2ème en  $I_2$ , , la 9ième en  $I_3$ . En I 10 on doit recevoir le bit contrôle d'imparité, en  $I_{12}$  ou  $I_{11}$  et  $I_{12}$  les bits d'adresse.

Les 9 impulsions d'information sont stockées dans le registre méssage au fur et à mesure de leur arrivée. Ce registre méssage doit avoir 9 bascules, pour garder les informations jusqu'à ce que les contrôles d'adresse, et de format du code aient permis leur transfert. Cette durée est de 140 ms, pour un mot long et 100 ms pour un mot court. Soient 3 impulsions et demi pour un mot long et 2 impulsions et demie pour un mot court. Ce registre méssage doit être mis à zéro avant l'arrivée des impulsions d'information. Cette remise à zéro est donc effectuée à l'impulsion Io soit exactement à Io Ho

RàZ = Io·H<sub>2</sub> Von logignamme

R. M fig 3?

Ce registre qui en effet, constitue un registre à décalage possède en plus de 9 bascules d'information; une 10 ième bascule. Celle-ci servira de contrôle d'absence d'impulsion.

A l'impulsion Io H 2, mise à part la lière bascule du registre méssage qui est mise à 1 toutes les autres y compris la 10 ème sont mises à zéro. Au fur et à mesure de l'arrivée des informations, l'état 1 de la lière bascule se décale. Au bout de 9 impulsions d'avance du registre méssage l'état 1 qui était dans la lière bascule doit normalement se retrouver dans la 10 ième bascule. Dans le cas contraire, l'une des impulsions est absente ou alors une défaillance quelconque a atteint la circuiterie. En effet si au bout de 9 impulsions l'état 1 n'a pas atteint la bascule 10 une impulsion aura manquée à la commande d'avance du registre et le décalage des informations ne sera pas effectué d'une façon normale.

Ceci constitue une vérification qui conditionne l'accéptation d'un mot.

# - CIRCUIT DE COMMANDE D'AVANCE DU REGISTRE MESSAGE : ( Voir fig. 34 porte18)

Le but cherché est de stocker dans le registre méssage uniquement les 9 bits d'information et que ce stockage commence de l'impulsion I<sub>1</sub> à l'impulsion I<sub>9</sub> c'est à dire l'introduction de la 1ière impulsion d'information se fait à l'mpulsion I<sub>1</sub> et la 9ième à I<sub>9</sub>.

Ponc on doit éviter d'introduire les bits arrivant aux impulsions Io,  $I_{10}$ ,  $I_{11}$  dans le cas du mot impair et Io,  $I_{10}$ ,  $I_{11}$ ,  $I_{12}$  dans le cas du mot pair. La R à Z du registre méssage se fait à la moitié supérieure de l'impulsion Io ce qui évite au signal début de mot de s'introduire dans le registre méssage. Le signal capable d'éliminer les bits  $I_{10}$ ,  $I_{11}$ ,  $I_{12}$  est celui recueilli à la sortie  $S_2$  de la bascule de poids  $2^3$  du compteur d'impulsions. Ce signal est noté I d  $S_2$ .

.../...

L'inconvénient est que I d  $S_2$  nous élimine 2 bits d'information, ce qui nous oblige d'utiliser les signaux  $I_8$  et  $I_9$  ( $I_8$  = 0 de Io à  $I_7$ ;  $I_8$  = 1 à  $I_8$ ,  $I_9$  = 0 de Io à  $I_8$ ;  $I_9$  = 1 à  $I_9$ ) pour les récupérer.

D'autre part les signaux transmis (P et N ) ont une durée de 20 ms et sont tels que, quand  $P=1 \Rightarrow N=0$  et vice-versa. Le signal (P + N) a exactement le même aspect que le signal d'horloge  $H_2$ , on pourra donc l'utiliser pour la commande d'avance du registre més-sage pour assurer une bonne synchronisation.

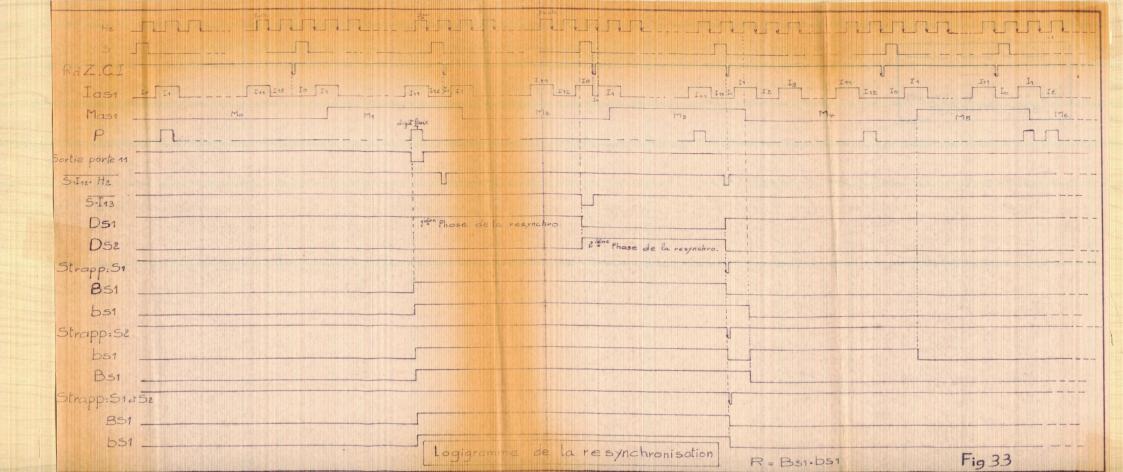

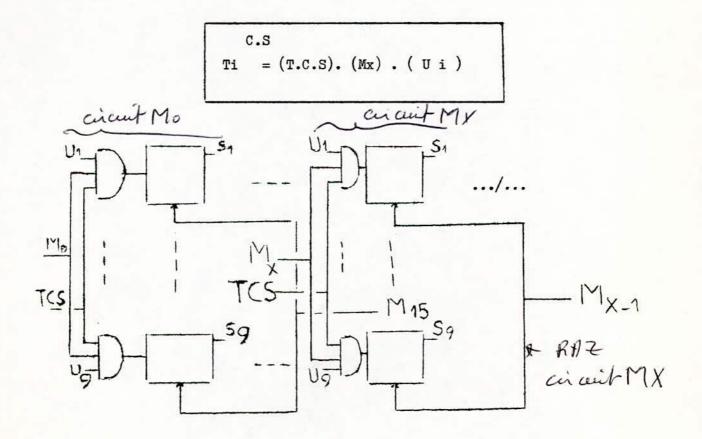

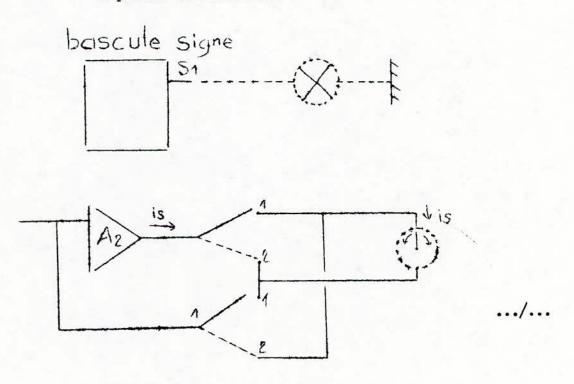

#### EN RESUME :