# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

# ECOLE NATIONALE POLYTECHNIQUE

# DÉPARTEMENT D'ÉLECTRONIQUE

Mémoire de projet de fin d'études pour l'obtention du diplôme d'ingénieur d'état en Électronique

# thème:

# Implémentation sur FPGA d'un décodeur LDPC pour les communications sans fils

# Idris ACHOURI

Sous la direction de M. Mohamed TAGHI

Présenté et soutenue publiquement le (21/06/2018)

### Composition du Jury:

Président M. Boualem BOUSSEKSOU, Cc ENP Promoteur M. Mohamed Oussaïd TAGHI, Mr ENP Examinateur M. Lies SAADAOUI, Dr ENP

# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

# ECOLE NATIONALE POLYTECHNIQUE

# DÉPARTEMENT D'ÉLECTRONIQUE

Mémoire de projet de fin d'études pour l'obtention du diplôme d'ingénieur d'état en Électronique

# thème:

# Implémentation sur FPGA d'un décodeur LDPC pour les communications sans fils

# Idris ACHOURI

Sous la direction de M. Mohamed TAGHI

Présenté et soutenue publiquement le (21/06/2018)

# Composition du Jury:

Président M.Boualem BOUSSEKSOU, Pr USTHB Promoteur M.Mohamed Oussaïd TAGHI, Mr ENP Examinateur M.NLies SAADAOUI, Dr ENP

# D'edicace

Ce travail est dédié à nos chers parents,

A nos professeurs,

A nos familles,

A nos frères et sœurs,

Et à nos amis,

A tous ceux que je n'ai pas cités et que je n'oublierai jamais leurs soutiens et leurs aides.

# Remerciements

En premier lieu, nous remercions Dieu le tout puissant de nous avoir donné le courage, la volonté et la patience pour réaliser ce travail.

Nous remercions nos parents, qui nous ont soutenus tout au long de nos études.

Nos remerciements les plus vifs s'adressent particulièrement à Monsieur Mohamed TAGHI, notre promoteur à l'Ecole Nationale Polytechnique pour son aide, sa confiance et sa disponibilité, ainsi que les membres du jury d'avoir accepté l'examination de ce mémoire.

Nous remercions aussi tous nos amis qui nous ont soutenus dans les moments difficiles.

Ce travail, fruits de notre cursus et notre volonté, n'a été possible que grâce au tous nos enseignants dont nous louons les efforts qu'ils ont consentis durant toutes ces années.

تمثل رموز اختيار التكافؤ منخفض الكثافة (LDPC) رموز مصححات الخطأ الأكثر فعالية لأنها تسمح بالحصول على نتائج قريبة من تلك المعرفة ب نهاية شانون (SHANON) للرموز ذات المجموعات الواسعة جدا فيما يخص جودة تصحيح الخطأ هذه الدراسة خصصناها لتصميم تخطيط نصف متوازي مرن لجهاز فك الرموز بالاعتماد على نظام الحلول الحسابية (خوارزمية) لفك الترميز Min-Sum تم تأكيد كفاءة هذه الخوارزمية عن طريق المحاكاة على جهاز الكمبيوتر. تخطيط جهاز فك الرموز تم دمجه في بطاقة FPGA بعد تقليص حجم رموز ال (LDPC) الخاص بهذا العمل بسبب متطلبات الاختبار. في الأخير تم ربط نتائج التركيب مع الأنماط البيانية المولدة من لغة وصف الأجهزة LDL الخاصة بهذا التخطيط.

كلمات مفتاحيه: اختيار التكافؤ منخفض الكثافة (LDPC), جهاز فك الرموز HDL, بطاقة FPGA, التخطيط, لفك الترميز.. Min-Sum

# Abstract:

Low-density parity-check (LDPC) are among the most powerful forward error correcting codes since they achieve error correction performance very close to the Shannon limit for large block lengths. LDPC block. In this thesis, we investigate into the design architecture of an array type LDPC code based on min-sum algorithm. The performance of the decoding algorithm was first validated via simulations. The detailed design of the decoding architecture was implemented on a field-programmable gate array (FPGA) kit with a short block length as an example. The schematics generated have been documented along with the synthesis results.

**Key words**: LDPC, FPGA, HDL, Min-Sum, Decoder, Architecture, Implementation.

# Résumé:

Codes de contrôle de parité à faible densité(LDPC) codes font partie des codes correcteurs d'erreur les plus performant, puisque ils permettent d'atteindre une performance de correction d'erreur très proche de la limite de Shanon pour des codes en block très larges. Nous avons consacré notre travail à la conception d'une architecture semi parallèle, flexible d'un décodeur LDPC basée sur l' de décodage Min-sum. Les performances de cet algorithme de décodage ont été validé dans un premier temps par le biais d'une simulation. La conception de l'architecture du décodeur a été ensuite implémentée sur la carte FPGA après réduction de la taille du code LDPC considéré pour ce travail, à cause des exigences de test. Les schémas générés par la description HDL de cette architecture ont été associé aux résultats de synthèse.

Mots Clés: LDPC, FPGA, HDL, Min-Sum, Décoder, Architecture, Implémentation.

# Table des matières

| Ta            | Table des figures |          |                                                               |            |

|---------------|-------------------|----------|---------------------------------------------------------------|------------|

| $\mathbf{Li}$ | ste d             | les tab  | leaux                                                         |            |

| Li            | ste d             | les abr  | éviations                                                     |            |

| Li            | ste d             | les not  | ations                                                        |            |

| In            | trod              | uction   | Générale                                                      | 15         |

| 1             | Gér               | néralité | és sur le codage canal et codes correcteurs d'erreurs         | 18         |

|               | 1.1               | Introd   | luction                                                       | 18         |

|               | 1.2               | La cha   | aîne de communication numérique                               | 19         |

|               |                   | 1.2.1    | Le codage de source                                           | 20         |

|               |                   | 1.2.2    | Codage canal                                                  | 20         |

|               |                   | 1.2.3    | La modulation                                                 | 20         |

|               |                   | 1.2.4    | Le canal de communication                                     | 2          |

|               |                   | 1.2.5    | La capacité d'un canal                                        | 26         |

|               |                   | 1.2.6    | Le théorème fondamental du codage canal                       | 2          |

|               | 1.3               | Les co   | odes correcteur d'erreur                                      | 28         |

|               |                   | 1.3.1    | Définitions et notation                                       | 28         |

|               |                   | 1.3.2    | Mesure des performances d'un code correcteur d'erreur         | 29         |

|               |                   | 1.3.3    | Concaténation de codes                                        | 3          |

|               |                   | 1.3.4    | les classes des codes correcteurs d'erreurs                   | 3.         |

|               | 1.4               | Les ty   | rpes des codes correcteurs d'erreurs                          | 3          |

|               |                   | 1.4.1    | les codes en bloc                                             | 3          |

|               |                   | 1.4.2    | Les codes convolutifs                                         | 35         |

|               |                   | 1.4.3    | Comparaison des performances entre quelques codes correcteurs |            |

|               |                   |          | d'erreurs                                                     |            |

|               | 1.5               | conclu   | sion                                                          | 39         |

| 2             | Coc               | lage L   | DPC                                                           | <b>4</b> ] |

|               | 2.1               | Histor   | ique                                                          | 41         |

|               | 2.2               | Défini   | tions et notations                                            | 42         |

|               | 2.3               | Les cla  | asses de codes LDPC                                           | 43         |

|   |     | 2.3.1 Les codes réguliers                                                    | 43               |

|---|-----|------------------------------------------------------------------------------|------------------|

|   |     | 2.3.2 Les codes irréguliers                                                  | 44               |

|   |     | 2.3.3 Comparaison entre les codes réguliers et irréguliers                   | 45               |

|   | 2.4 | Construction des codes LDPC                                                  | 46               |

|   | 2.5 | Représentation graphique des codes LDPC                                      | 48               |

|   |     | 2.5.1 Le profil d'irrégularité des nœuds de données et des nœuds de contrôle | 49               |

|   |     | 2.5.2 La notion de cycle                                                     | 50               |

|   | 2.6 | Les codes quasi-cycliques                                                    | 50               |

|   | 2.7 | Opérations d'encodage                                                        | 51               |

|   | 2.8 | conclusion                                                                   | 53               |

| 3 | Alg | orithmes de décodage LDPC                                                    | <b>55</b>        |

|   | 3.1 | Introduction                                                                 | 55               |

|   | 3.2 | Algorithme bit flipping                                                      | 56               |

|   | 3.3 | Algorithme Sum-Product                                                       | 58               |

|   | 3.4 | Algorithme Min-Sum                                                           | 63               |

|   |     | 3.4.1 Avantages de l'algorithme Min-Sum                                      | 66               |

|   |     | 3.4.2 Inconvénients de l'algorithme Min-Sum                                  | 67               |

|   | 3.5 | Étude des performances des codes LDPC                                        | 67               |

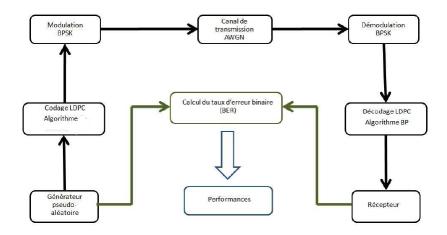

|   |     | 3.5.1 Présentation de la chaîne de simulation                                | 67               |

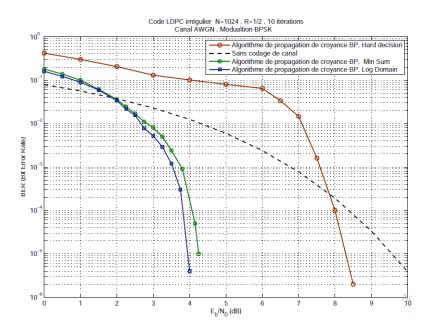

|   |     | 3.5.2 Comparaison entre les différents algorithmes de décodage LDPC          | 67               |

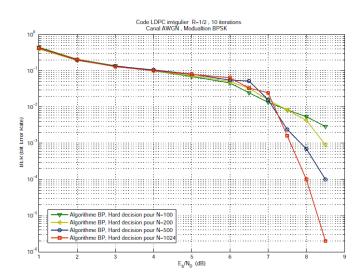

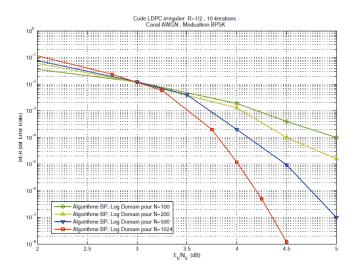

|   |     | 3.5.3 Influence de la taille du code sur les performances                    | 69               |

|   |     | 3.5.4 Influence du nombre d'itérations du processus de décodage sur les      |                  |

|   |     | 1                                                                            | 71               |

|   |     |                                                                              | 73               |

|   | 3.6 | Conclusion                                                                   | 74               |

| 4 |     |                                                                              | <b>7</b> 6       |

|   | 4.1 |                                                                              | 76               |

|   | 4.2 | 1                                                                            | 77               |

|   |     | 4.2.1 Architecture entièrement parallèle                                     | 77               |

|   |     | 1                                                                            | 78<br><b>7</b> 8 |

|   | 4.0 | 4.2.3 Architecture série                                                     | 79<br>70         |

|   | 4.3 | Comparaison des deux conceptions                                             | 79               |

|   | 4.4 |                                                                              | 80               |

|   |     |                                                                              | 80               |

|   |     |                                                                              | 80               |

|   |     | 4.4.3 Variable Node Unit                                                     | 81               |

| 5 | _   | plémentation sur FPGA d'une architecture basée sur l'algorithme              | 00               |

|   |     |                                                                              | 82               |

|   | 5.1 | •                                                                            | 82               |

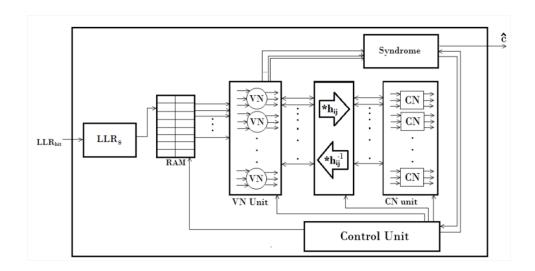

|   | 5.2 | Architecture du décodeur implémenté sur l'FPGA                               | 83               |

| 5.3     | Les bl  | ocs générés dans Xilinx ISE                                     | 84 |

|---------|---------|-----------------------------------------------------------------|----|

|         | 5.3.1   | Unité du nœud de contrôle (CNU)                                 | 84 |

|         | 5.3.2   | Unité du nœud de variable (VNU) $\dots \dots \dots \dots \dots$ | 85 |

|         | 5.3.3   | Syndrome Unit                                                   | 86 |

|         | 5.3.4   | Unité du décodeur                                               | 86 |

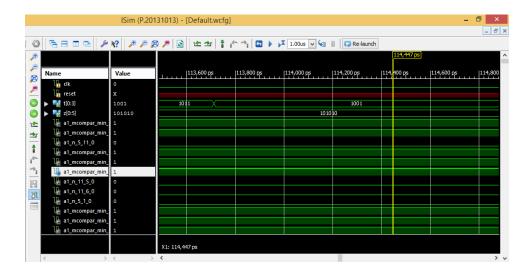

| 5.4     | Simula  | ation du décodeur                                               | 87 |

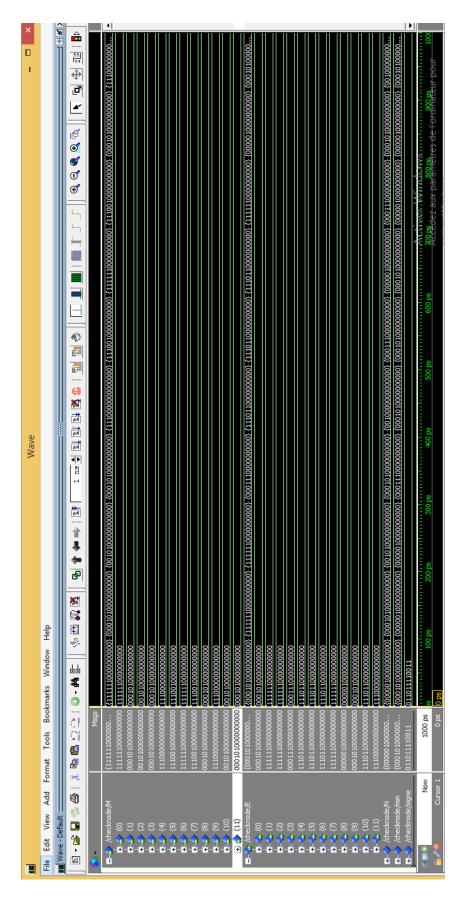

|         | 5.4.1   | Simulation fonctionnelle                                        | 88 |

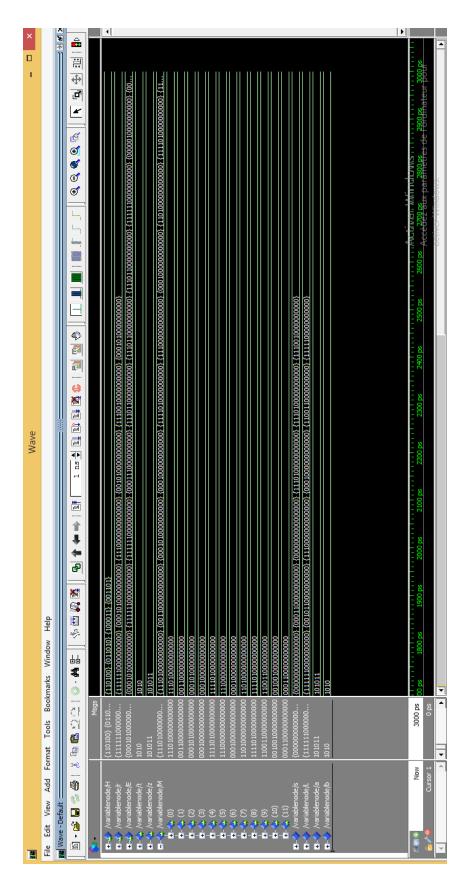

|         | 5.4.2   | Simulation temporelle                                           | 89 |

| Conclu  | sion g  | énérale                                                         | 96 |

| Bibliog | graphie |                                                                 | 98 |

# Table des figures

| 1.1  | Schéma fondamental d'une communication numérique : le paradigme de                                                         |   |

|------|----------------------------------------------------------------------------------------------------------------------------|---|

|      | Shannon                                                                                                                    | 1 |

| 1.2  | Schéma simplifié d'un codeur de source                                                                                     | 2 |

| 1.3  | Exemple de modulations numériques                                                                                          | 2 |

| 1.4  | (a) Le canal binaire avec effacement BEC.(b) Le canal binaire symétrique.                                                  | 2 |

| 1.5  | Le canal binaire avec effacement BEC.(b) Le canal binaire symétrique                                                       | 2 |

| 1.6  | Propagation par trajets multiples                                                                                          | 2 |

| 1.7  | Effet doppler                                                                                                              | 2 |

| 1.8  | schéma récapitulatif des différents types d'évanouissement                                                                 | 2 |

| 1.9  | schéma représentatif de l'information mutuelle                                                                             | 2 |

| 1.10 | Capacité d'un Canal Gaussien de quelques modulations M-aires linéaires                                                     |   |

|      | en fonction du $E_b/N_0$                                                                                                   | 2 |

| 1.11 | Schéma simplifié d'un codeur/décodeur de canal                                                                             | 2 |

| 1.12 | Illustration des régions caractérisant les performances d'un code correcteur                                               |   |

|      | d'erreurs                                                                                                                  | 3 |

| 1.13 | Concaténation de deux codes correcteurs d'erreurs                                                                          | 3 |

| 1.14 | la hiérarchie des codes correcteurs d'erreurs                                                                              | 3 |

| 1.15 | le codage d'un message.                                                                                                    | 3 |

| 1.16 | Exemple d'un code convolutif                                                                                               | 3 |

| 1.17 | Exemple d'un diagramme en Treillis                                                                                         | 3 |

| 1.18 | (a) Un code non-systématique (NSC) (b) Un code récursif systématique                                                       |   |

|      | $(RSC). \dots \dots$ | 3 |

| 1.19 | Schéma de principe d'un turbo-code.                                                                                        | 3 |

| 1.20 | Schéma de principe d'un turbo-decode                                                                                       | S |

| 1.21 | Comparaison entre les performances des codes de parité, de <i>Hamming</i> et                                               |   |

|      | de $Golay$ (Courbes reproduites de la référence[13])                                                                       | S |

| 1.22 | Comparaison entre les performances des codes convolutifs, Reed-Solomon                                                     |   |

|      | et les techniques de codage avancées (LDPC et Turbo-codes)[2]                                                              | 3 |

| 1.23 | Comparaison des performances des codes correcteur d'erreurs                                                                | 4 |

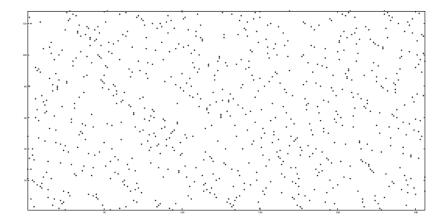

| 2.1  | Matrice de contrôle d'un code LDPC régulier $(3,6)$ de taille $n=256$ et de                                                |   |

|      | rendement $R = 0, 5[20]$                                                                                                   | 4 |

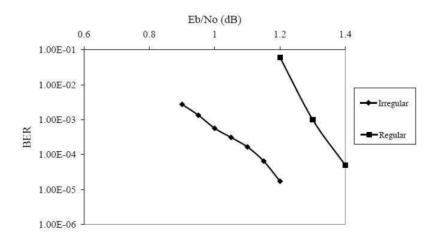

| 2.2              | Comparaison de performances entre les codes LDPC réguliers et irréguliers     |      |    |

|------------------|-------------------------------------------------------------------------------|------|----|

|                  | de taille $N=16000$ et de rendement $R=1/2$ (Graphes reproduits de la         | 1 -  |    |

| 0.0              | référence [24])                                                               | 45   |    |

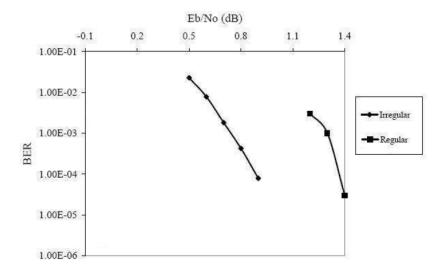

| 2.3              | Comparaison de performances entre les codes LDPC réguliers et irréguliers     |      |    |

|                  | de taille $N=16000$ et de rendement $R=1/4$ (Graphes reproduits de la         |      |    |

|                  | référence [3])                                                                | 45   |    |

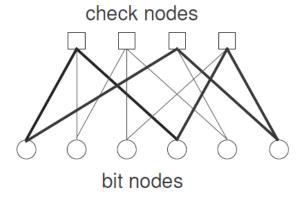

| 2.4              | Graphe de Tanner de la matrice de contrôle de parité 2.11. Un 6-cycle est     |      |    |

|                  | affiché en gras.                                                              | 49   |    |

| 2.5              | Graphe bipartite dit de Tanner de la matrice 2.12                             | 49   |    |

| 2.6              | Exemples de cycles de longueur 4, 6 et 8                                      | 50   |    |

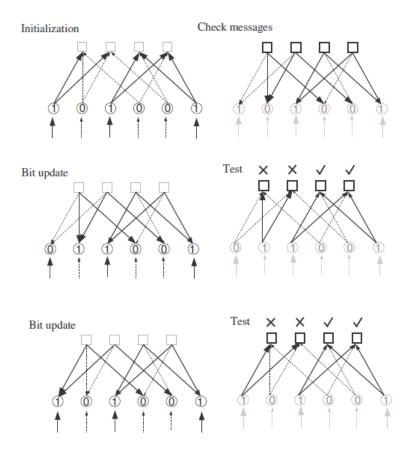

| 3.1              | Algorithme de décodage bit flipping[34]                                       | 57   |    |

| 3.2              | Illustration de l'algorithme de décodage Bit flipping                         | 58   |    |

| 3.3              | Illustration de l'algorithme de décodage "Sum-Product[41]                     | 61   |    |

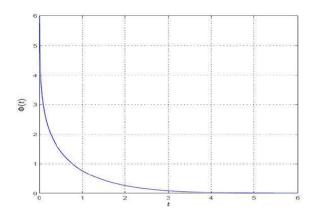

| 3.4              | représentation graphique de $\phi(x)$                                         | 64   |    |

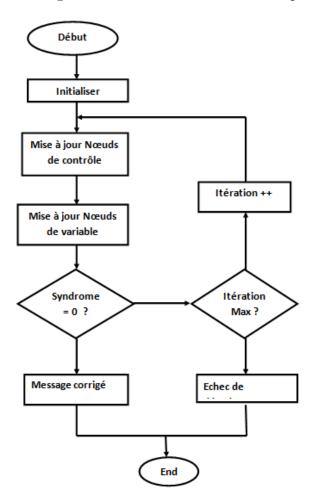

| 3.5              | Organigramme de l'algorithme de décodage                                      | 65   |    |

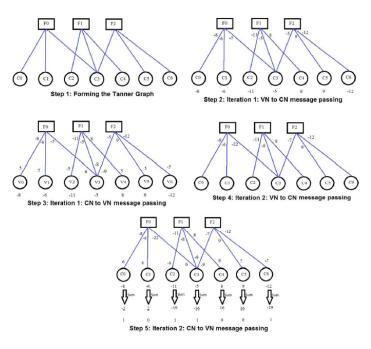

| 3.6              | Exemple d'algorithme Min-Sum expliqué avec un graphique Tanner où l'er-       |      |    |

|                  | reur la correction se produit dans la deuxième itération[35]                  | 66   |    |

| 3.7              | Le modèle de simulation utilisé pour l'évaluation des performances des        |      |    |

|                  | codes LDPC.                                                                   | 68   |    |

| 3.8              | Comparaison des performances entre les différents algorithmes de décodage     | 00   |    |

| 0.0              | pour l'algorithme BP                                                          | 69   |    |

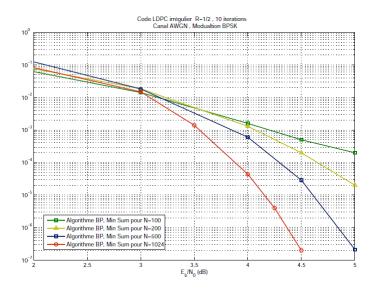

| 3.9              | Influence de la taille du code sur les performances pour un décodage Hard.    | 70   |    |

| 3.10             | Influence de la taille du code sur les performances pour l'algorithme de      | 10   |    |

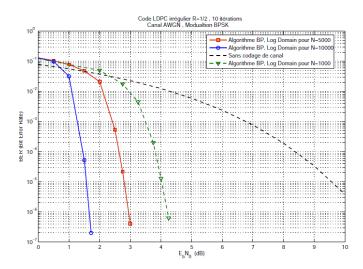

| 5.10             | décodage Log-Domain                                                           | 70   |    |

| 2 11             | Influence de la taille du code sur les performances pour l'algorithme de      | 10   |    |

| 5.11             |                                                                               | 71   |    |

| 2 10             | décodage Min-Sum                                                              | 11   |    |

| 3.12             |                                                                               | 71   |    |

| 9 1 <del>9</del> | décodage Log-Domain.                                                          | 71   |    |

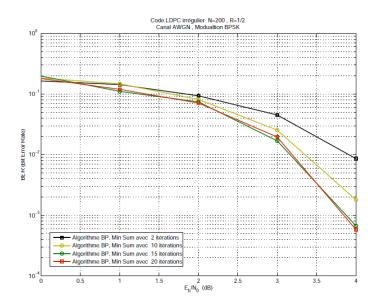

| 5.15             | Influence du nombre d'itérations sur les performances des codes LDPC pour     | 70   |    |

| 0.14             | N=200 et un décodage Min-Sum                                                  | 72   |    |

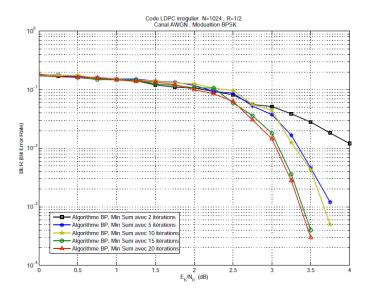

| 3.14             | Influence du nombre d'itérations sur les performances des codes LDPC pour     | 70   |    |

|                  | N=1024 et un décodage Min-Sum                                                 | 72   |    |

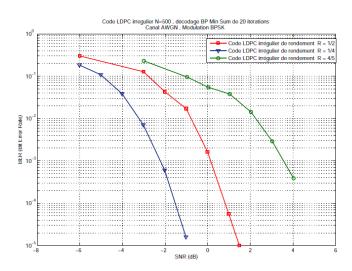

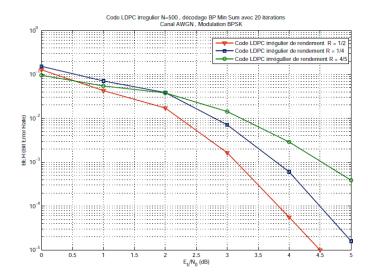

| 3.15             | Influence du rendement $R$ sur les performances des codes LDPC (BER =         |      |    |

|                  | f(SNR))                                                                       | 73   |    |

| 3.16             | Influence du rendement R sur les performances des codes LDPC (BER= $f(E_b/N)$ | (0). | 74 |

| 4.1              | Chemin de donnée d'une architecture entièrement parallèle. cette figure est   |      |    |

|                  | dérivée de[37]                                                                | 78   |    |

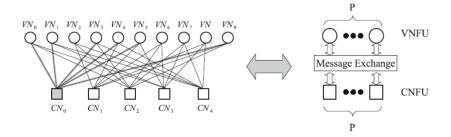

| 4.2              | Mapping du décodeur semi-parallèle à partir du graphe de $Tanner$             | 79   |    |

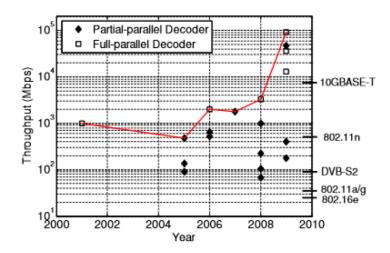

| 4.3              | Exigence et variation du débit pour quelques décodeur LDPC parallèle et       |      |    |

|                  | semi-parallèle en fonction de l'année<br>[38]                                 | 80   |    |

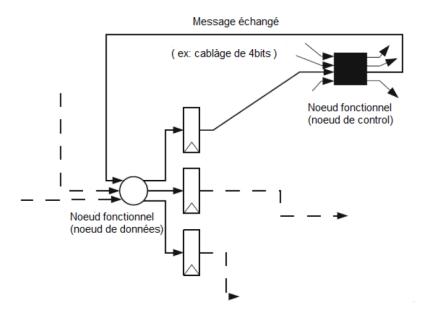

| 4.4              | Architecture de base de niveau supérieur[35]                                  | 81   |    |

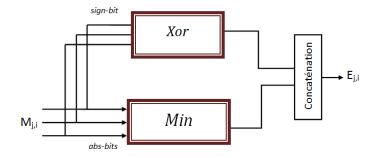

| 4.5  | Schéma général d'une unité du nœud de contrôle                                        | 81 |

|------|---------------------------------------------------------------------------------------|----|

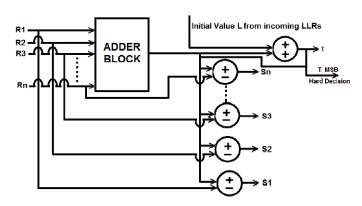

| 4.6  | Schéma général d'une unité du nœud de variable[42]                                    | 81 |

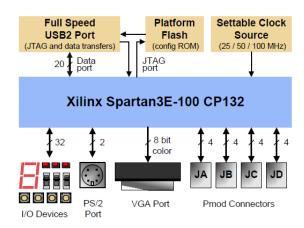

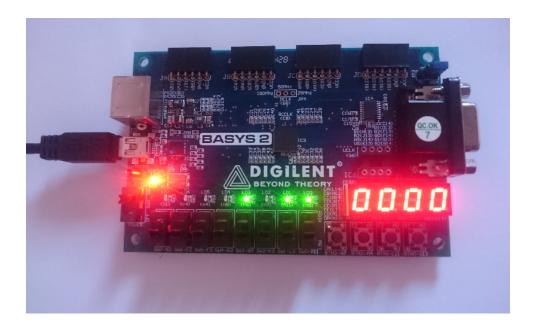

| 5.1  | La carte FPGA Basys2                                                                  | 83 |

| 5.2  | Diagramme de bloc de la carte FPGA-Basys2                                             | 83 |

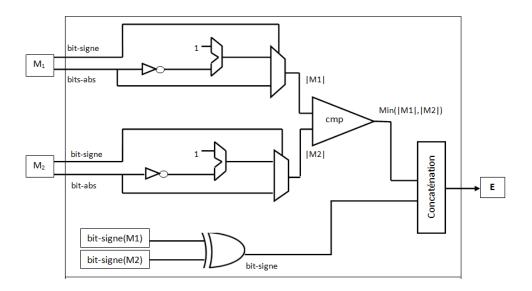

| 5.3  | Schéma de l'unité de contrôle élémentaire                                             | 84 |

| 5.4  | Schéma du décodeur LDPC entièrement parallèle                                         | 84 |

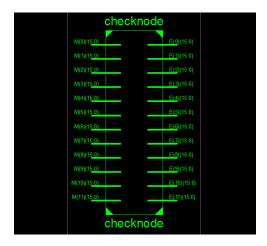

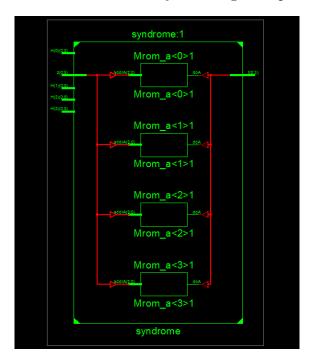

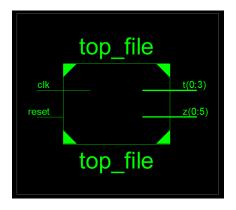

| 5.5  | Bloc de l'unité du nœud de contrôle généré par Xilinx-ISE                             | 85 |

| 5.6  | Schématique du bloc noeud de contrôle généré par Xilinx-ISE                           | 85 |

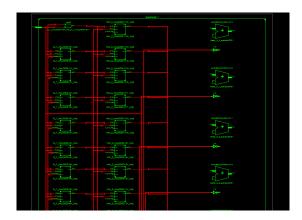

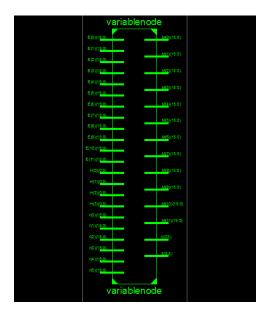

| 5.7  | Bloc de l'unité du nœud de variable généré par Xilinx-ISE                             | 86 |

| 5.8  | Schématique du bloc noeud de variable généré par Xilinx-ISE                           | 86 |

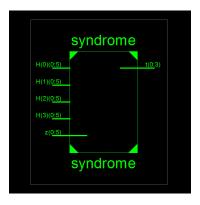

| 5.9  | Bloc de l'unité du Syndrome généré par Xilinx-ISE                                     | 87 |

| 5.10 | Schématique du Syndrome généré par Xilinx-ISE                                         | 87 |

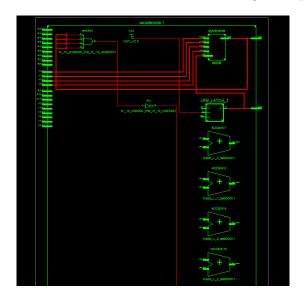

| 5.11 | Bloc général de l'unité du décodeur généré par Xilinx-ISE                             | 88 |

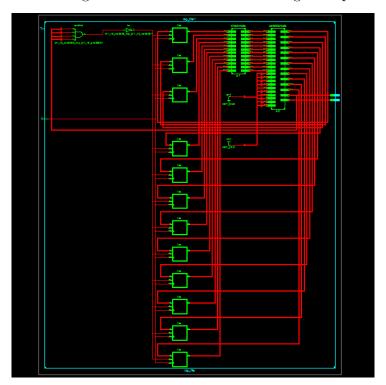

| 5.12 | Schéma de l'architecture du décodeur généré par Xilinx-ISE                            | 88 |

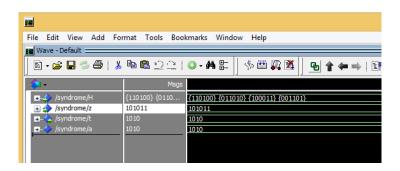

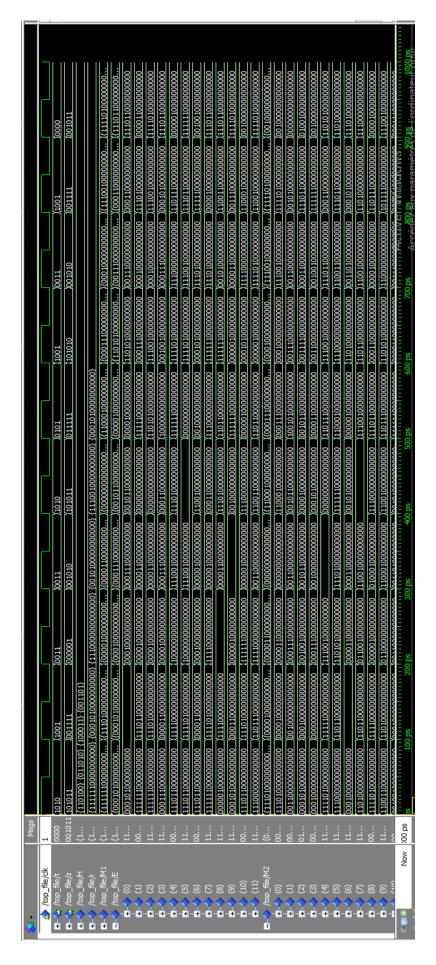

| 5.13 | Résultat de la simulation fonctionnelle du CNU sur ModelSim                           | 91 |

| 5.14 | Résultat de la simulation fonctionnelle du VNU sur ModelSim                           | 92 |

| 5.15 | Résultat de la simulation fonctionnelle de l'unité de syndrome sur ModelSim           | 93 |

| 5.16 | Résultat de la simulation fonctionnelle du décodeur sur Model<br>Sim<br>$\ .\ .\ .$ . | 94 |

| 5.17 | Illustration de la simulation temporelle du décodeur sur Xilinx-ISE                   | 95 |

| 5.18 | Résultat du test obtenus sur la carte BASYS-2-FPGA                                    | 95 |

| 5.19 | Rapport de synthèse                                                                   | 95 |

|      |                                                                                       |    |

# Liste des tableaux

| 1.1 | addition et multiplication dans le corps de Galois $F_2$                 | 29 |

|-----|--------------------------------------------------------------------------|----|

| 3.1 | Les paramètres de simulation utilisés pour évaluer les performances des  |    |

|     | codes LDPC                                                               | 68 |

| 3.2 | Exemples de techniques de codage utilisées par quelques standards de té- |    |

|     | lécommunication.                                                         | 74 |

# Liste des abréviations

**APP** A Posteriori Probability

AWGN Additive White Gaussian Noise

BCH Bose-Chaudhuri-Hocquenghem

**BEC** Binary Erasure Channel

BER Bit Error Rate

**BPSK** Binary Phase Shift Keying

**BP** Belief Propagation

**BSC** Binary Symmetric Channel

DVB-S2 2nd Generation Digital Video Broadcast Spatial

DVB-T Digital Video Broadcast Terrestrial

**FER** Frame Error Rate

**GSM** Groupe Signaux Multidimensionnels

i.i.d indépendant identiquement distribué

**IEEE** Institute of Electrical and Electronics Engineers

LDPC Low Density Parity Check

LLR Log Likelihood Ratio

MAP Maximum A Posteriori

NRNSC Non Recursive Non Systematic Code

NSC Non Systematic Code

**QAM** Quadrature Amplitude Modulation

**QPSK** Quadrature Phase Shift Keying

**RSC** Recursive Systematic Code

SNR Signal to Noise Ratio

SP Sum Product

WiFi Wireless Fidility

WIMAX Worldwide Interoperability for Microwave Access

# Liste des notations

| . ( )   | т  | c ·      |       |

|---------|----|----------|-------|

| sign(.) | La | fonction | signe |

|         |    |          |       |

- | . | La valeur absolue

- $(.)^t$  La transposée d'un vecteur ou d'une matrice

- $(.)^{H}$  L'opérateur Hermitien c.à.d le conjugué de la transposée d'une matrice

- (.)\* Le conjugué

- $\oplus$  Somme modulo-2

- LLR(.) Le log-rapport de vraisemblance

- ☐ La fonction d'entrelacement

- $\Pi^{-1}$  La fonction de dés-entrelacement

- c Le vecteur de la séquence d'information

- $M_{y/x}$  Matrice de transition d'un canal

- C La capacité du canal

- $d_s$  Le débit symbole de la source

- x Le vecteur du mot de code

- K La taille de la séquence d'information

- N La taille du mot de code

- M Le nombre de bits de redondance ou de parité

- R Rendement de codage de canal

- $F_q$  Corps de Galois de q éléments

- $d_H$  La distance de Hamming

- $w_H$  Le poids de Hamming

- $d_{min}$  La distance minimale

- G Matrice génératrice de code

- H Matrice de contrôle de parité

$w_r$  Le poids des lignes de la matrice H

$w_c$  Le poids des colonnes de la matrice H

$E_b/N_0~$  Le rapport de l'énergie transmise par bit d'information sur la densité de puissance du bruit

$E_s/N_0\,\,$  Le rapport de l'énergie transmise par symbole d'information sur la densité de puissance du bruit

# Introduction Générale

De nos jours, nous vivons dans un monde extrêmement numérique où les technologies des communications sans fils jouent un rôle primordial. Ainsi que dans ces deux dernières décennies, le monde a connu une énorme évolution notamment avec le développement et l'explosion de l'électronique moderne et l'apparition des nouvelles technologies et techniques avancées des systèmes de communications numériques. Cet extraordinaire essor que connaît le monde est principalement dû aux développements considérables dans le domaine de télécommunication.

Ce développement technologique a donné naissance à une forte expansion de la communication numérique. Ainsi, le codage du canal est devenu un élément essentiel et indispensable car il permet d'assurer la protection de l'information transmise en contrôlant les erreurs de transmission. Son principe est de découper le message à transmettre en blocs de k bits, qui sont alors traités séparément par le codeur. Les codes classiques ne permettent pas d'atteindre la limite de Shannon. On a donc développé d'autres systèmes de codages appelé codes convolutifs. Le principe de ces codes, inventés par Peter Elias en 1954, est de le considérer comme une séquence semi-infinie de symboles qui passent à travers une succession de registres à décalage, dont le nombre est appelé mémoire du code.

Les codes LDPC ont été découverts par Gallager au début des années 1960. Cette découverte remarquable a été largement ignorée par les chercheurs pendant près de 20 ans, jusqu'au travail de Tanner en 1981, dans lequel il a fourni une nouvelle interprétation des codes LDPC d'un point de vue graphique. Le travail de Tanner a également été ignoré par les théoriciens pendant environ 14 ans jusqu'à la fin des années 1990, lorsque certains chercheurs en codage ont commencé à étudier les codes graphiques et le décodage itératif. Leurs recherches ont mené à la redécouverte des codes de Gallager. Ils ont montré qu'un long code LDPC avec un décodage itératif basé sur la propagation de croyance permet une erreur de performance représentant seulement une fraction de décibel de la limite de Shannon [4] [6]. Cette découverte fait des codes LDPC de puissants concurrents par rapport aux codes turbo pour le contrôle des erreurs lorsqu'une haute fiabilité est requise. Les codes LDPC ont l'avantage des codes turbo, il ne nécessite pas un long entrelacement pour atteindre une bonne performance d'erreur. Ainsi, en 2004, un code LDPC a d'abord été standardisé dans une émission satellite DVB-S2.

En 2004, les codes LDPC ont été introduits pour la première fois dans la norme de

télédiffusion numérique par satellite(DVB-S2)[1], et à partir de cette année, les applications de ces codes ne cessent d'augmenter surtout dans les communications sans fils, en effet, ils ont été adopté quelques années plu tard par plusieurs standard récents, tels que le WiMAX WLAN802.16e[1], le G.hn/G.9960 pour les réseaux domestiques filaire[2], et le 10GBASE-T standard pour les 10Giga bit Ethernet(802.3an)[3]. L'intégration des techniques de codage dites avancées, telles que les codes LDPC se généralise donc dans les standards de communications. Dans ce contexte l'objectif de notre travail est d'étudier en largeur et en profondeur les codes LDPC notamment les algorithmes de décodage et les différentes techniques architecturale et matérielle existantes, afin de proposer une architecture d'un décodeur LDPC.

# Organisation du document :

L'objectif principale de ce projet est d'implémenter sur la carte Xilinx FPGA BASYS-2 un décodeur LDPC pour les communications sans fils. Pour cela, ce mémoire est organisé comme suit :

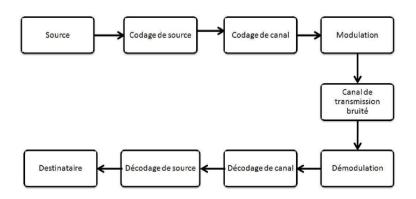

Le **premier chapitre**, décrit brièvement les concepts généraux liés à la théorie de l'information et au codage canal, une description de la chaîne de communication est initialement introduite en suite détaillée, en indiquant le rôle de chaque élément, suivit d'une définition générale des codes correcteur d'erreurs et finalement une comparaison de performance entre les codes correcteurs d'erreurs les plus connus.

Dans le **second chapitre**, une large présentation des codes LDPC est proposée, incluant les notations et outils mathématiques indispensables à la compréhension, particulièrement au sujet d'encodage situé dans la dernière section, Ce chapitre traite également la classe des codes LDPC, et de la construction des codes LDPC afin de discuter les différents types d'architectures possible lors de l'implémentation d'un code LDPC, ce chapitre introduira de plus, la représentation de ces codes et en fin le concept des codes cycliques et leur avantage à augmenter la flexibilité du décodeur.

Le **chapitre troisième** est divisé en deux parties, dans un premier temps, une profonde description des algorithmes de décodage des codes LDPC dérivée de la théorie du chapitre précédent et d'une logique mathématique qui finit par une déduction de l'algorithme Min-sum, qui fera l'objet de notre architecture, tandis que la deuxième partie est consacrée pour une étude des performances des différents algorithmes de décodage conçu pour différents types de codes LDPC.

Une description architecturale des différentes implémentations des codes LDPC est présentée au **chapitre quatre**, en déduisant les avantages et inconvénients de chacune d'elles, afin de faire une comparaison des différents types de conceptions.

Enfin dans le **dernier chapitre5**, Une présentation de la carte FPGA-BASYS-2 est donnée et sur laquelle l'implémentation de notre travaille à été effectuée, nous proposons deux types d'architecture basée sur l'algorithme Min-sum sur avec lequel nous avons travaillé tout au long de notre projet, Le détail de conception, une présentation des différents blocs généré par la plate-forme Xilinx-ISE Spartane-3E sera exposés, et enfin une simulation accompagnée d'une discussion des résultats obtenus.

Une **conclusion** et quelques perspectives sont finalement données à la fin de ce document.

# Chapitre 1

# Généralités sur le codage canal et codes correcteurs d'erreurs

Ce premier chapitre a pour objectif de présenter des principes et les concepts fondamentaux qui seront utiles pour la compréhension des codes LDPC en commençant par illustrer et présenter la chaîne de communication en expliquant brièvement le rôle et l'intérêt de chaque bloc de la chaîne, avant de donner quelques rappels sur la théorie du codage. Puis, nous introduisons les différents types des codes correcteurs d'erreurs en focalisant sur la famille des codes linéaires en blocs, et finir par une comparaison de leur performance.

# 1.1 Introduction

Dans un système de communication numérique l'objectif est toujours de faire passer un message transmis en un point à partir d'un autre point. mais le problème qui se pose, est que le canal est généralement soumis à des perturbation telles que le bruit et les interférences. Alors, comment faire pour établir une communication fiable dans ces conditions?

Les premières tentatives d'évaluations de performance datent des contributions de Nyquist en 1924[4] et de l'ingénieur Américain R.Hartetly en 1928[5], mais l'étape décisive fut franchie en 1948 par Claude E.Shannon, lorsque parut son article fondateur de la théorie de l'information, intitulé "The Mathematical Theory of Communication"[6].

A la croisée de la théorie de l'information, des mathématiques et de l'électronique, le codage correcteur d'erreurs (codage de canal) a connu de nombreux développements depuis les travaux fondateurs de Shannon. Du simple code de Hamming (1950) aux récents turbo codes(1993) en passant par les codes LDPC (1962), le codage de canal a considérablement évolué et a intégré des concepts de plus en plus sophistiqués, en particulier le traitement probabiliste de l'information.

# 1.2 La chaîne de communication numérique

Une chaîne de communication numérique modélise les différentes étapes autorisant le transfert de l'information d'une source vers un destinataire. Une chaîne de transmission peut différer grandement selon la nature du système de transmission, qui peut aussi bien être un système de stockage de données qu'un système de télécommunication. Néanmoins certaines étapes sont applicables dans tous les contextes. Ainsi, le couple codeur décodeur de source peut être employé pour réduire la taille du message à transmettre par une opération de compression-décompression réalisée avec ou sans perte d'information. Par contre, le couple codeur-décodeur de canal augmente la taille du message à transmettre afin d'accroître la qualité de l'information transmise sur le canal.

Le canal, justement, comprend toutes les étapes entre la sortie du codeur et l'entrée du décodeur. Cela intègre le lieu physique de la transmission, dans lequel le signal transmis est bruité d'une façon aléatoire, et le couple modulateur-démodulateur, qui est utilisé dans la plupart des systèmes pour transformer l'information numérique en un signal continu compatible avec le milieu de transmission et vice-versa.

On désigne par le paradigme de Shannon (voir Figure 1.1) le schéma fondamental d'une communication numérique. Une source engendre un message à l'intention d'un destinataire. La source et le destinataire sont deux entités séparées, éventuellement distantes, qui sont reliées par un canal qui est le support de communication d'une part, mais qui d'autre part est le siège des perturbations[7].

FIGURE 1.1 – Schéma fondamental d'une communication numérique : le paradigme de Shannon

La suite de cette section illustre un peu plus en détail chacune des étapes d'une chaîne de communication en se contraignant au cas de la chaîne de communication sans fil présentée dans la figure au dessus.

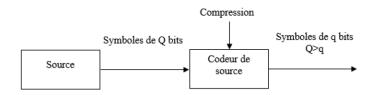

#### 1.2.1Le codage de source

Le codage de source vise à la concision maximale. L'usage d'un canal coûte d'autant plus cher que le message est long, le verbe "coûter" devant s'étendre ici en un sens très général, celui d'exiger l'emploi de ressources limitées telles que le temps, la puissance et la bande passante. Pour diminuer ce coût, on cherche à représenter le message avec le moins débits possibles, c'est-à-dire le compresser. Pour ce faire, on essaye d'éliminer la redondance contenue dans le message transmis par la source[8]. Un point essentiel dans le codage de source est le critère de Fidélité. Ce critère varie selon l'application et sur tout selon l'importance du domaine d'utilisation. Les applications où la compression de données doit se faire sans perte, utilisent un codage de source appelé réversible <sup>1</sup>, tandis que, les applications où les pertes sont tolérables, utilisent un codage dit non-réversible <sup>2</sup>[9].

FIGURE 1.2 – Schéma simplifié d'un codeur de source

#### 1.2.2Codage canal

Alors que le codage de source élimine la redondance indésirable dans les informations à envoyer, la finalité du codage de canal est de protéger le message contre les erreurs et les perturbations du canal pouvant résulter des imperfections et du bruit du canal par l'ajout d'une redondance à l'information utile du message à transmettre. La redondance et l'information utile sont liées par une loi donnée. La sortie du codeur de canal est un mot de code à partir d'un code de canal, A la réception, le décodeur de canal exploite la redondance produite par le codeur dans le but de détecter, puis de corriger si c'est possible les erreurs introduites lors de la transmission[10]. Ce point sera détaillé encore plus dans les sections suivantes.

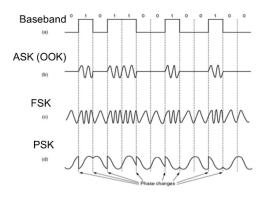

#### 1.2.3 La modulation

La modulation consiste à effectuer un codage dans l'espace euclidien, espace généralement adapté aux canaux rencontrés en pratique. Pour une modulation M-aire, on associe à chaque mot de L bits un signal  $x_i(t)$ , i = 1,...,M de durée T choisi parmi les M = 2L

<sup>1.</sup> Réversible :le message envoyé sera exactement restitué au niveau du récepteur (sans perte ou distorsion).

<sup>2.</sup> Par exemple, dans la norme MPEG4, la compression des données multimédia est faite avec une distorsion tolérable par l'observateur (critère de fidélité), et cela à cause des défauts de l'œil (persistance rétinienne) et de l'oreille humaine(l'effet de masquage).

signaux. Quant à la démodulation, son rôle est d'extraire les échantillons et de décider en faveur des symboles les plus probablement émis[11]. Les données fournies par l'unité de démodulation seront traitées par ce que l'on appelle le décodeur. On distingue deux types de décodeurs, le premier est appelé décodeur à décision dure(Hard decision), car il fonctionne à partir des données fermes ('0'ou'1'). Le second type est appelé décodeur à décision pondérée(Soft decision), car le démodulateur fournie au décodeur une valeur ferme accompagnée d'une mesure de fiabilité[12].

Figure 1.3 – Exemple de modulations numériques

#### 1.2.4 Le canal de communication

Le canal de communication est le support physique permettant d'acheminer un message entre une source et un ou plusieurs destinataires. Au sens des communications numériques, et comme représenté dans la Figure (1.1), inclut le milieu de transmission (support physique entre l'émetteur et le récepteur : câble, fibre, espace libre,...), le bruit (bruit de fond, bruit impulsif, parasite, évanouissement, distorsion, défaut, panne), et les interférences (provenant des autres utilisateurs du milieu de transmission, de brouilleurs intentionnels ou non). Il existe plusieurs type de canaux, mais en théorie d'information, les canaux les plus utilisés sont appelés canaux discrets<sup>3</sup>. Un canal discret est un système stochastique acceptant en entrée des suites de symboles définies sur un alphabet de sortie Y, reliés par une loi de transition  $P_{Y|X}$  i.e. une matrice stochastique  $M_{Y|X}$ .

$$M_{Y|X} = \begin{pmatrix} P_{y_1|x_1} & \cdots & P_{y_j|x_1} \\ \vdots & \ddots & \vdots \\ P_{y_1|x_k} & \cdots & P_{y_j|x_k} \end{pmatrix}$$

$$(1.1)$$

Le canal sera donc défini par :

$$T = (X, Y, M_{Y|X}) \tag{1.2}$$

<sup>3.</sup> Pour plus de détails sur les autres types de canaux, le lecteur peut se reporter aux références suivantes:[13],[11],[12]et[14].

Le canal est dit sans mémoire si le symbole courant de sortie ne dépend que du symbole courant d'entrée et il ne dépend pas des précédents ni des suivants.

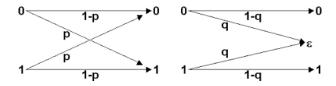

# Les canaux binaires BEC et BSC

Le canal binaire symétrique (BSC), présenté par le schéma de droite de la Figure 1.4, est le canal le plus simple qu'on puisse imaginer. Ce canal est caractérisé par des alphabets d'entrée et de sortie binaires, une probabilité d'erreur p et une matrice de transition  $M_{Y|X}$  donnée par la relation. L'autre canal, présenté par le schéma de droite de la Figure 1.4, est appelé canal binaire avec effacement(BEC), ce canal est binaire à l'entrée, mais ternaire en sortie (aux deux symboles notés '0' et '1' est adjoint un troisième, noté  $\varepsilon$ ). Ce canal est caractérisé par une probabilité d'erreur p et une matrice de transition  $M_{Y|X}$ donnée par la relation.

$$M_{Y|X(BSC)} = \begin{pmatrix} 1 - P & P \\ P & 1 - P \end{pmatrix} \tag{1.3}$$

$$M_{Y|X(BEC)} = \begin{pmatrix} 1 - P & P & 0 \\ 0 & P & 0 \end{pmatrix}$$

(1.4)

FIGURE 1.4 – (a) Le canal binaire avec effacement BEC.(b) Le canal binaire symétrique.

### Le canal à bruit Blanc Additif et Gaussien

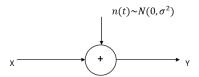

Parmi les canaux stationnaires le plus utilisé, celui sur lequel l'évaluation des performances des systèmes de communications est aussi la plus simple, est le canal à Bruit Blanc Additif et Gaussien (BABG ou AWGN en anglais : Additive White Gaussian Noise en anglais). Ce dernier est le modèle de bruit de base le plus utilisé et le plus rencontré en théorie de l'information pour rendre compte des nombreux processus stochastiques qui se produisent dans la nature. Il a les caractéristiques suivantes :

Additif: car il est ajouté au bruit intrinsèque du système.

Blanc : car sa puissance est uniforme sur toute la bande fréquentielle du système. C'est une analogie avec la couleur blanche, qui correspond une émission uniforme sur toutes les fréquences du spectre visible.

Gaussien: car il a une distribution normale dans le domaine temporel avec une moyenne nulle.

Le modèle mathématique le plus simple pour un canal de communication est le canal à bruit additif. Dans ce modèle, le signal transmis s(t) est corrompu par un processus de bruit aléatoire additif n(t). Physiquement, le processus de bruit additif peut provenir de composants électroniques et d'amplificateurs au récepteur du système de communication, ou des interférences rencontrées dans la transmission, comme dans le cas de la transmission du signal radio. Si le bruit est introduit principalement par des composants électroniques et des amplificateurs au récepteur, il peut être caractérisé comme un bruit thermique.

Ce type de bruit est caractérisé statistiquement comme un processus de bruit gaussien. Par conséquent, le modèle mathématique résultant pour le canal est habituellement appelé le canal additif de bruit gaussien. L'atténuation des canaux est facilement incorporée dans le modèle. Lorsque le signal subit une atténuation lors de la transmission à travers le canal, le signal reçu est :

$$r(t) = as(t) + n(t) \tag{1.5}$$

tel que a représente le facteur atténuation.

FIGURE 1.5 – Le canal binaire avec effacement BEC.(b) Le canal binaire symétrique.

Le bruit introduit dans ce canal est modélisé par un signal aléatoire n(t), dont la distribution de probabilité suit la loi Gaussienne :

$$f_N(n) = \frac{1}{\sqrt{2\pi\sigma^2}} \exp\frac{-(n-\mu)^2}{2\sigma^2}$$

(1.6)

tel que

$$\mu = E[n(t)] = 0$$

$\operatorname{et}$

$$\sigma^2=E[n(t)-\mu]^2=E[n^2(t)]$$

représentent respectivement la moyenne et la variance.

Dans la suite, nous allons introduire les problèmes techniques que peut rencontrer une chaîne de transmission. ce qui nous permet de bien comprendre par la suite les différents concepts.

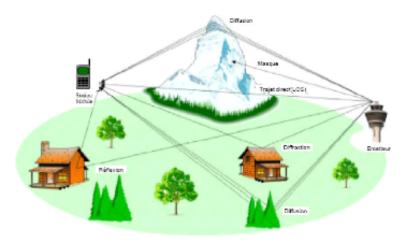

# Trajet multiples (Multipath)

La Propagation multi-trajets apparait comme conséquence de réflexion, dispersions, atténuation de l'énergie du signal et diffractions par différents obstacles des ondes électromagnétiques émises. Cela a pour conséquence des retards à la réception, des changements de phases et des atténuations différentes[15]. Ces phénomènes sont causés par les obstacles naturels qui s'opposent à la propagation du signal radio comme les montagnes, les bâtiments,..etc. Ces réflexions obligent le signal à suivre des chemins différents pour arriver au récepteur, ce qui donne naissance au phénomène de trajets multiples. La propagation multi-trajets apparait lorsqu'un signal émis par un émetteur prend plusieurs chemin pour arriver aux récepteurs. Le récepteur reçoit des versions retardées du signal émis et les voit comme des échos avec différents temps d'arrivé et d'amplitudes.

FIGURE 1.6 – Propagation par trajets multiples

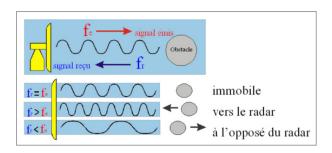

# Effet Doppler

Quand la source et le récepteur se déplacent l'une par rapport à l'autre, la fréquence du signal reçue au récepteur n'est pas identique à celle de la source, la distance entre l'émetteur et le récepteur varie au cours du temps, on obtient donc un décalage fréquentiel[8]. L'effet Doppler représente ce décalage de fréquence. Cette différence entre la fréquence émise et reçue appelée fréquence Doppler peut s'écrire sous la forme :

$$f_d = \frac{v f_c cos(\alpha)}{c} \tag{1.7}$$

tel que

$f_d$ : Fréquence Doppler.

v: est la vitesse de déplacement du récepteur.

c: est la vitesse de propagation de l'onde électromagnétique dans le vide.

$\alpha$ : est l'angle entre v (vitesse de déplacement) et k (direction de propagation du champ).

FIGURE 1.7 – Effet doppler

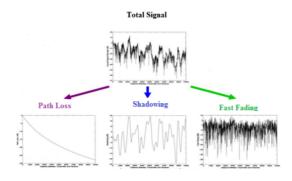

# Effet de masquage (shadowing)

L'effet de masquage est un phénomène aléatoire plus local (sur quelques centaines de longueur d'onde), causé par l'obstruction des ondes qui se propagent, par de grands obstacles, tels que des collines, des édifices, des murs, des arbres...etc, ce qui cause une atténuation, plus ou moins importante, de la force du signal. Sa variation due à l'effet de masque est appelée évanouissement lent (slowfading) et peut être décrite par une distribution log-normale[15]. Les variations de la puissance reçue dues aux pertes par parcours et à l'effet de masque peuvent être neutralisées d'une manière efficace par le contrôle de puissance. Dans ce qui suit, on ne prendra en considération que l'évanouissement rapide.

# Pertes par parcours (pathloss)

Les pertes par parcours représentent l'atténuation que subit la puissance moyenne du signal transmis le long de la distance entre l'émetteur et le récepteur. En espace libre la puissance moyenne du signal est inversement proportionnelle au carré de la distance  $r^2$ . Ce pendant dans un canal radio mobile ou, en générale, il n'a pas de visibilité (no line of sight), la puissance moyenne est inversement proportionnelle à L(tel que  $r^3 < L < r^5$ ) [15]. la figure 1.8 résume tous les types d'évanouissement.

FIGURE 1.8 – schéma récapitulatif des différents types d'évanouissement

#### 1.2.5La capacité d'un canal

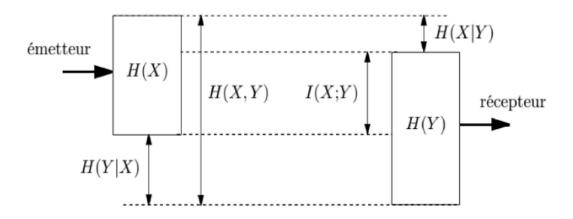

On définit la capacité d'un canal (exprimée en bit/s) comme le maximum de l'information mutuelle moyenne I(X;Y), elle représente donc la plus grande quantité d'information pouvant transiter entre l'émetteur et le récepteur[11], comme le montre la figure 1.9.

$$C = \max_{P(X)} I(X, Y) \tag{1.8}$$

On désigne par H(X) l'entropie de la source qui représente la surprise moyenne ou la quantité d'information délivrée par une source d'information. Par contre, H(X|Y) représente l'information requise pour supprimer l'ambiguïté sur l'entrée.

$$H(x) = \sum_{i}^{N} P_i \log_2 P_i \tag{1.9}$$

$P_i$ : la probabilité d'apparition des lettres de l'alphabet de la source.

La capacité C s'exprime en Shannon par symbole ou bit par symbole. Il est également possible de l'exprimer en Shannon par seconde, on parle alors de capacité par unité de temps [13]. Pour la distinguer de la capacité par symbole, on trouve généralement dans la littérature la notation suivante :

$$C_s = Cd_s \tag{1.10}$$

FIGURE 1.9 – schéma représentatif de l'information mutuelle

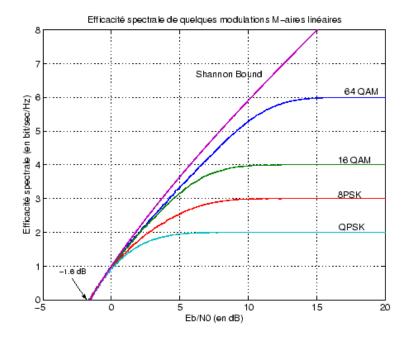

Dans le cas d'une transmission sur deux voies en quadrature sur un canal gaussien de largeur W(Hz), et pour un rapport signal sur bruit par symbole  $E_s/N_0$ , où  $E_s$  est l'énergie par symbole émis et  $N_0/2$  la densité spectrale de puissance du bruit, la capacité maximale est donnée par :

$$C = W \log_2(1 + \frac{E_s}{N_0})(bit/s)$$

(1.11)

La figure 1.10 illustre l'évolution de cette capacité dans le cas de quelques formes d'onde M-aires en fonction du rapport  $E_b/N_0$  pour un canal Gaussien.

FIGURE 1.10 – Capacité d'un Canal Gaussien de quelques modulations M-aires linéaires en fonction du  $E_b/N_0$

#### Le théorème fondamental du codage canal 1.2.6

En 1948, Shannon a annoncé dans son article intitulé A Mathematical Theory of Communication communication [6], le théorème fondamental de la théorie de l'information (Deuxième théorème de Shannon):

"Pour une source à débit d'information  $R_D$  et un canal de capacité C, si  $R_D < C$ , il existe un code ayant des mots d'une lonqueur N tel que sa probabilité d'erreur soit arbitrairement petite".

une autre façon d'annoncer le théorème :

"Tout canal de transmission admet un paramètre C, appelé capacité du canal, tel que pour tout C > 0 et pour tout R < C, il existe un code de taux R permettant la transmission du message avec un taux d'erreurs binaire de R".

En d'autres termes, nous pouvons obtenir des transmissions aussi fiables que l'on veut, en utilisant des codes de taux plus petits que la capacité du canal.

Ce théorème affirme l'existante de codes dont la probabilité de décodage erroné est arbitrairement petite, mais ne montre pas comment ces codes peuvent être construits. Ce théorème affirme également une chose tout à fait surprenante, à savoir que, quelque soit le niveau des perturbations d'un canal, on peut toujours y passer des messages avec une probabilité d'erreur aussi faible que l'on veut. Ce théorème a causé un énorme développement dans la théorie de codage de canal [14].

Cependant, ce théorème n'indique pas le moyen de construire de tels codes, nous cherchons donc à construire des codes ayant un taux le plus élevé possible (pour des raisons de temps et de coût) et permettant une fiabilité arbitrairement grande. Les codes classiques ne permettent pas d'atteindre cette limite. Nous avons donc développé d'autres systèmes de codages.

#### 1.3 Les codes correcteur d'erreur

Il existe une grande variété de codes correcteurs d'erreurs, dont les performances et les applications sont variables. Mais, le principe de base reste le même : ajouter de la redondance intelligemment et utiliser cette sur information pour déterminer la Fiabilité du message (détection d'erreur), puis, si c'est possible reconstruire le message d'origine au mieux (correction d'erreur). Mais en revanche, l'ajout de la redondance dans le message à transmettre, entraîne une perte d'efficacité du système. En effet, les bits de redondance introduits ne véhiculent pas de l'information utile. Cependant, cette perte est à mettre en balance avec le gain de qualité obtenu par l'utilisation du codage[16].

#### 1.3.1 Définitions et notation

• Le codeur de canal permet de générer un mot de code X de N bits à partir d'un mot d'information c de K bits. Ce code engendre donc M bits de redondance, avec M = N - K, appelés bits de parité, que nous noterons par le vecteur p (voir la Figure 1.11)

FIGURE 1.11 – Schéma simplifié d'un codeur/décodeur de canal.

$\bullet$  Un code est dit systématique si les symboles de c apparaissent explicitement dans x. On appelle aussi rendement de codage R, le rapport entre le nombre de bits d'information et le nombre de bits du mot de code transmis :

$$R = \frac{K}{N} \tag{1.12}$$

• Les symboles du message information c et du mot de code x prennent leurs valeurs dans un corps fini  $F_q$  à q éléments, appelé corps de Galois et dont les principales propriétés sont illustrées dans la référence[16]. Pour la majorité des codes, les symboles sont binaires

et prennent leur valeur dans le corps  $F_2$  à deux éléments. Les opérations élémentaires d'addition et de multiplication dans le corps  $F_2$  sont données dans le Tableau 1.1.

| a | b | a+b | $a \times b$ |

|---|---|-----|--------------|

| 0 | 0 | 0   | 0            |

| 0 | 1 | 1   | 0            |

| 1 | 0 | 1   | 0            |

| 1 | 1 | 0   | 1            |

Table 1.1 – addition et multiplication dans le corps de Galois  $F_2$

- $\bullet$  On appelle distance de Hamming entre deux codes  $x_i$  et  $x_j$ , le nombre de composantes où les deux codes sont différents, on la note par  $d_H(x_i; x_i)$ . On appelle poids de Hamming, noté  $w_H(x)$ , le nombre d'éléments non nuls présents dans un mot de code.

- $\bullet$  On appelle distance minimale  $d_{min}$  la plus petite distance de Hamming entre deux mots de code  $x_i$  et  $x_i$ .

$$d_{min} = \min_{x_i, x_j \in Z} d_H(x_i, x_j)$$

(1.13)

où Z représente l'ensemble des mots de code possibles.

• Le pouvoir de détection et de correction d'un code est déterminé par sa distance minimale  $d_{min}$ . Pour détecter e erreurs pouvant intervenir dans le mot de code, il faut que:

$$d_{min} = e + 1 \tag{1.14}$$

Pour la correction de e erreurs pouvant intervenir dans le mot de code, il faut que :

$$d_{min} = 2e + 1 (1.15)$$

#### 1.3.2 Mesure des performances d'un code correcteur d'erreur

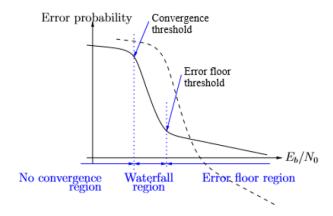

On appelle gain du codage, l'écart d'énergie par bit utile entre deux systèmes pour un taux d'erreur donné (voir Figure 1.12). Dans le cas de l'utilisation de techniques de codage avancées, l'évolution de la performance du code peut se diviser en trois régions comme l'illustre la Figure 1.12. La première région correspond à un comportement où le décodage ne converge pas pour des SNR faibles, le décodage dégrade les performances par rapport à un système non codé, on parle alors de la région de non convergence. A partir d'un certain rapport signal sur bruit SNR, appelé seuil de convergence, le décodage rentre dans une phase où la probabilité d'erreur diminue très rapidement avec le SNR, on parle de la région du Waterfall.

Enfin, il existe une région où la probabilité d'erreur diminue de manière moins rapide que la région du Waterfall. Ce comportement est spécifique de la région du plancher d'erreur ou error floor.

La performance d'un couple codeur/décodeur se juge en premier lieu en termes d'erreurs résiduelles à la sortie du décodeur, lorsqu'on s'est fixé un cadre bien précis d'évaluation : type de perturbation, longueur de message, taux de redondance ou rendement de codage etc. D'autres aspects, comme la complexité du décodage, les latences introduites par le codeur et le décodeur, le degré de flexibilité du code (en particulier son aptitude à se conformer à différentes longueurs de message et/ou à différents rendements de codage) sont également à considérer de plus ou moins près suivant les contraintes propres au système de communication. Les erreurs résiduelles que le décodeur n'est pas parvenu à corriger se mesurent à l'aide de deux paramètres. Le taux d'erreurs binaires (TEB) est le rapport entre le nombre d'erreurs binaires résiduelles et le nombre total de bits d'information transmis. Le taux d'erreurs de mots, de blocs ou de paquets (TEP) est le nombre de mots de code mal décodés (au moins un des bits d'information est faux) ramené au nombre total de mots de code émis. Le rapport entre TEB et TEP est la densité d'erreurs moyenne  $\delta_e$  dans la partie systématique d'un mot mal décodé :

$$\delta_e = \frac{TEB}{TEP} \tag{1.16}$$

FIGURE 1.12 – Illustration des régions caractérisant les performances d'un code correcteur d'erreurs.

### Remarque:

Dans les systèmes de communications, le critère utilisé pour évaluer les performance est donné en taux d'erreur binaire BER (Bit Error Rate en anglais) en fonction du SNR (rapport signal sur bruit), mais pour avoir des résultats plus exacts, sur tout quand on compare des codes de rendements différents, on utilise un autre critère qui donne le BER

en fonction de  $E_b/N_0$  [13]. avec :

$E_b$ : L'énergie transmise dans un bit d'information.

$N_0$ : La densité spectrale du bruit.

## 1.3.3 Concaténation de codes

La concaténation de codes consiste à combiner plusieurs codes élémentaires de taille raisonnable, de telle sorte que le code global (résultant) possède un pouvoir de correction élevé(  $d_{min}$  élevée) et qu'il soit aisément dé-codable. Le premier schéma de codage composite, appelé concaténation de codes, à été introduit par Forney dans son travail de thèse en 1965(voir Figure 1.13)[17]. Ce schéma est constitué d'un premier codeur, dit codeur extérieur, permettant de fournir un mot de code à un deuxième codeur, dit codeur intérieur ,pour générer un code concaténé. Si les deux codes sont systématiques, le code concaténé est lui-même systématique.

FIGURE 1.13 – Concaténation de deux codes correcteurs d'erreurs.

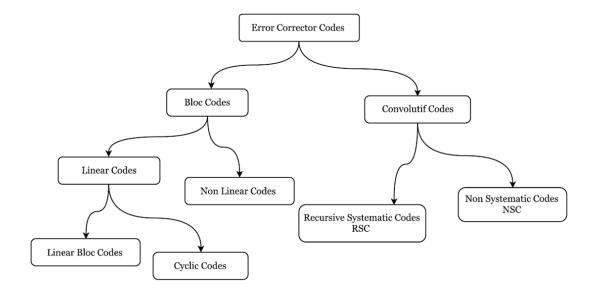

## 1.3.4 les classes des codes correcteurs d'erreurs

Un code est dit linéaire si la fonction de codage est une application linéaire, si non il est dit non-linéaire. Lorsque les traitements requis pour obtenir les propriétés de détection ou de correction ont lieu par bloc de N symboles, on dit qu'on a affaire à un code en bloc. Lorsque les symboles générés par la source ne sont pas traités par des blocs, mais de manière continue, on dit qu'on a affaire à un code convolutif. Pour la suite de ce chapitre, nous allons parler uniquement des codes en bloc et des codes convolutifs, ainsi que notre étude sera focalisée sur les codes linéaire en bloc.

# 1.4 Les types des codes correcteurs d'erreurs

### 1.4.1 les codes en bloc

Une grande famille de codes correcteurs d'erreurs est constituée des codes par blocs. Dans notre projet nous ne traiterons que ces types des codes. Pour ces codes l'information est d'abord coupée en blocs de taille constante et chaque bloc est transmis indépendamment des autres, avec une redondance qui lui est propre. La plus grande sous-famille de ces codes rassemble ce que l'on appelle les codes linéaires (Figure 1.14).

Le but de l'opération de codage en bloc est d'associer à chaque mot d'information composé de K symboles q-aire un mot de code composé de N symboles q-aire. Cette

FIGURE 1.14 – la hiérarchie des codes correcteurs d'erreurs.

opération peut être représentée par une application g de l'ensemble  ${\cal F}_K^q$  vers l'ensemble  $F_N^q$

$$g: F_K^q \longrightarrow F_N^q$$

$c \longrightarrow x = g(c)$

L'information de la source est mise en trames de longueur fixe que nous devons transmettre c'est le message ou le mot initial. Le codage prend ce message pour en faire un mot de code : Nous appelons mot de code, la suite de n bits obtenue après un codage (k,

FIGURE 1.15 – le codage d'un message.

n). Le nombre n de bits qui composent un mot du code est appelé la longueur du code. La dimension k étant la longueur initiale des mots. Le message est constitué de k caractères soit  $2^k$  messages possibles. Le mot de code utilisé sera lui aussi de longueur fixe de ncaractères soit  $2^n$  mots de code possibles. Avec n > k il y'aura donc n - k caractères du mot de code qui sont redondants et serviront à traiter les erreurs éventuelles. Par ailleurs,  $2^n>2^k$ donc un certain nombre de mots de code ne correspondent pas à un message mais seulement à des erreurs de transmission. On parle ainsi d'un code de bloc (n, k) et du rapport ou le rendement du code défini par le rapport entre k et n.

Un cas particulier des codes en blocs est celui des codes où le message apparaît explicitement sur ses k caractères c'est à dire "en clair". A côté de ces k caractères seront donc ajoutés n-k caractères redondants. Nous obtenons alors un code dit code systématique.

Selon le classement donné par la Figure 1.14, Les codes linéaires se divisent en deux grandes parties :

# Les codes cycliques :

sont ceux où les mots de codes ont considérés comme étant des éléments dans unea lgèbre, à savoir des polynômes[18].

### Remarque:

Pour la suite, nous ne nous intéresserons qu'aux codes en bloc linéaires binaires (q = 2).

### Les codes linéaires en bloc :

sont ceux où les mots de code sont considérés comme étant des éléments dans un espace vectoriel

## Remarque:

Pour la suite, nous ne nous intéresserons qu'aux codes en bloc linéaires binaires (q = 2).

Les codes linéaires en bloc sont caractérisés par une matrice G de taille (K,N) appelée la matrice génératrice[11]. Cette matrice transforme un message d'information c de K bits en un mot de code x de taille N (N > K) par l'opération matricielle suivante :

$$x = c.G (1.17)$$

avec

$$G = \begin{pmatrix} g_{11} & \cdots & g_{1N} \\ \vdots & \ddots & \vdots \\ g_{K1} & \cdots & g_{KN} \end{pmatrix}$$

(1.18)

Chaque mot de code est une combinaison linéaire des vecteurs  $G_i$  de G. Ainsi donc, un code en bloc linéaire peut être défini comme un sous espace vectoriel à K < N dimensions construit suivant la relation 1.17[13]. Pour faciliter l'opération de codage, il est toujours possible de mettre la matrice G sous la forme systématique, en combinant les lignes entre elles  $^4$ .

$$G_{syst} = \left[ R^t | I_K \right] \tag{1.19}$$

<sup>4.</sup> On désigne par  $(.)^t$  la transposé d'une matrice ou d'un vecteur.

$$I_K = \begin{pmatrix} 1 & \cdots & 0 \\ \vdots & \ddots & \vdots \\ 0 & \cdots & 1 \end{pmatrix} \tag{1.20}$$

et

$$R^{t} = \begin{pmatrix} r_{11} & \cdots & r_{1M} \\ \vdots & \ddots & \vdots \\ r_{K1} & \cdots & r_{KM} \end{pmatrix}$$

(1.21)

Les codes linéaires en bloc sont aussi caractérisés par une autre matrice H de taille (N,M) appelée matrice de contrôle de parité[11]. La propriété principale  $^5$  de cette matrice est :

$$H.x^t = 0 (1.22)$$

$$H.G^t = 0 (1.23)$$

Dans le cas symétrique la matrice H devient comme suit :

$$H_{syst} = \left[ I_M | R \right] \tag{1.24}$$

avec

$I_M$ : la matrice identité d'ordre M.

et

$$R = \begin{pmatrix} r_{11} & \cdots & r_{1K} \\ \vdots & \ddots & \vdots \\ r_{M1} & \cdots & r_{MK} \end{pmatrix}$$

(1.25)

Une fois l'opération de codage est terminée, le message x sera transmis à travers un canal qui est généralement bruité, un bruit n s'ajoute à ce dernier. A la réception, le message reçu r sera donné par la relation suivante :

$$r = x + n = c.G + n \tag{1.26}$$

A partir de 1.22 et 1.26, on aura:

$$H.r^{t} = H.x^{t} + H.n^{t} = H.n^{t} (1.27)$$

<sup>5.</sup> En remplaçant la relation 1.17 dans la relation 1.22 on obtient  $H.(c.G)^t = H.G^t.c^t = 0$ , et comme cette relation est valable pour n'importe quelle séquence d'information c, donc  $H.G^t = 0$ .

On appelle le produit  $H.r^t$  un syndrome, si le résultat de ce produit est un vecteur nul, alors r est un mot de code, si non le vecteur r contient des bits erronés.

Le calcul de syndrome est la méthode utilisée par la plupart des codes en bloc, pour détecter la présence d'erreur, puis en fonction de l'algorithme de décodage, corriger si c'est possible ces erreurs[18].

### Exemples de codes en bloc

Les premiers codes en bloc sont les codes de *Hamming*, introduits en 1950 par *Richard* Hamming[19]. Ces codes donnaient des résultats médiocres par rapport aux critères de Varshamov et Gilbert [20], c'est la raison pour laquelle de nouveaux codes correcteurs d'erreurs ont été développés, on peut citer par exemple : Les code Reed-Solomon qui sont une classes particulière des codes cycliques BCH. Ces codes, développés par I.S.Reed et G.Solomon[21], sont largement utilisés pour la correction d'erreurs groupées dans la plupart des supports de données numériques comme les CD,DVD, blu-ray Discs, et dans de nombreux standards comme DVB-T[22]. Il existe beaucoup d'autres classes de codes en bloc, qu'on ne va pas détailler dans ce manuscrit comme : les codes de Goppa [23] qui sont très utilisés dans les crypto-systèmes de McEliece et Niederreiter, les codes Reed-Muller [24], les codes Golay [25]...etc. La classe de codes en bloc la plus puissante jusqu'à présent, est appelée les codes LDPC (Low Density Parity Check). Cette famille sera l'objet de notre étude par la suite, qu'on présentera dans le chapitre 2.

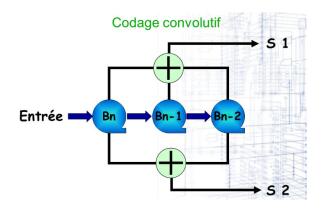

#### 1.4.2Les codes convolutifs

Les codes convolutifs, inventés en 1954 par Peter Elias [26], constituent une famille de codes correcteurs d'erreurs, dont la simplicité de codage et de décodage sont à l'origine de leur succès. Le principe est non plus de découper le message en blocs finis, mais de le considérer comme une séquence semi-infinie  $a_0a_1...a_n$  de symboles qui passent à travers une succession de registres à décalage, dont le nombre d'étages m est appelé mémoire du code et  $2^m$  le nombre d'états possibles. La quantité  $\mu=m+1$  est appelée longueur de contrainte du code et le rapport  $R = \frac{K}{N}$  est appelé le rendement de codage.

Pour illustrer le principe des codes convolutifs, voici un exemple présenté par la Figure 1.16, pour K=1, m=2 et N=2.  $a_t$  parvient au codeur à l'instant t, les bits de sortie X et Y sont calculés par les relations suivantes :

$$\begin{cases} X = a_t + a_{t-1}a_{t-2} \\ Y = a_t + a_{t-2} \end{cases}$$

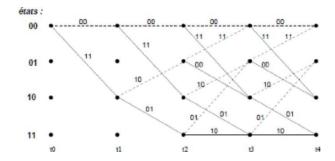

Supposons que le codeur reçoive le message 1011, les registres étant initialement tous les deux à 0. A la sortie on obtient la séquence codée suivante 11100001, et les registres seront finalement à l'état 11. Le diagramme en Treillis (voir Figure 1.18 (b)) est une représentation utile pour l'algorithme de Viterbi, l'algorithme de décodage le plus utilisé pour les codes convolutifs[27],[28].

FIGURE 1.16 – Exemple d'un code convolutif.

Figure 1.17 – Exemple d'un diagramme en Treillis.

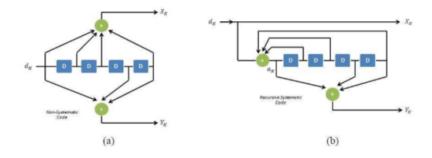

#### Les codes NSC et RSC

On désigne par NSC les codes non-systématiques (Non-Systematic Code en anglais) et par RSC les codes récursifs et systématiques (Recursive Systematic Code en anglais). Un code convolutif est dit récursif si la séquence passante dans les registres à décalages est alimentée par le contenu de ses registres (voir la Figure 1.18(b)). Si les K symboles d'information à l'entrée du codeur se retrouvent explicitement dans le code, alors le code est dit systématique, si non il est dit non-systématique [12] (voir la Figure 1.18(a)). Les codes non-systématiques et non-récursifs présentent, pour des SNR élevés, des performances meilleures qu'un code systématique et non-récursive et l'inverse pour les SNR faibles[29], [30]. Pour cette raison, les codes NSC ont été principalement étudiés et utilisés jusqu'au début des années 1990. On rappelle que la puissance d'un code (capacité de correction d'erreurs) et la complexité du décodeur augmentent avec l'augmentation de la mémoire m de ce code. Quant aux codes récursifs systématiques(RSC), ils sont utilisés par les turbo-codes, car ils sont les seuls susceptibles d'atteindre la limite de Shannon [29].

FIGURE 1.18 – (a) Un code non-systématique (NSC) (b) Un code récursif systématique (RSC).

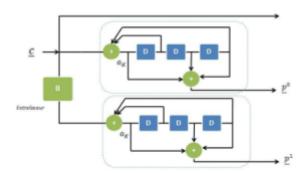

#### Les turbo-codes

Le plus célèbre des codes convolutifs est sans doute le turbo-code inventé par C. Berro, A. Glavieuxet, P. Thitimajshima en 1993[6]. Ces codes et les codes LDPC forment ce que l'on appelle les techniques de codage avancées. Le turbo-code utilise deux (ou plusieurs) encodeurs de type convolutifs. La Figure 1.19 montre le cas d'une concaténation parallèle, constituée de deux codes convolutifs récursifs systématiques identiques et un entre laceur pseudo-aléatoire. A chaque mot d'information c, on associe une redondance p, qui peut être divisée en une redondance  $p_0$  issue du premier encodeur et une redondance  $p_1$  issue du deuxième encodeur. Pour la première fois, un décodeur itératif est introduit. L'idée, très simple en soi, consiste en un décodeur comportant deux sous-ensembles de décodages échangeant de l'information. Le principe de ce récepteur est illustré dans la Figure 1.20. Pour expliquer le fonctionnement d'un tel décodeur, la notion d'information extrinsèque fut introduite. C'est cette information qui est échangée entre les décodeurs au cours des itérations. Après un certain nombre d'itérations, la décision ferme est prise sur l'information a posteriori. Cette information regroupe à la fois l'information issue de l'observation du canal et les informations extrinsèques issues des différents décodeurs[16].

FIGURE 1.19 – Schéma de principe d'un turbo-code.

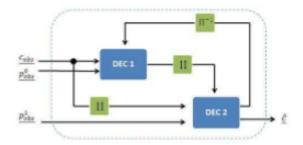

FIGURE 1.20 – Schéma de principe d'un turbo-decode.

#### 1.4.3 Comparaison des performances entre quelques codes correcteurs d'erreurs

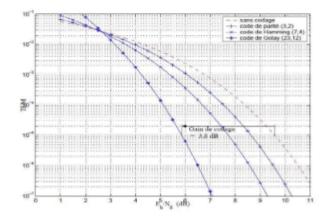

Avant de clôturer ce chapitre, nous allons donner une comparaison des performances entre les codes correcteurs les plus utilisés. Pour un canal à bruit blanc additif et gaussien AWGN, la Figure 1.21 montre que le code de Golay donne des performances meilleures par rapport au code de Hamming et le code de parité. Pour une probabilité d'erreur égal à  $10^{-5}$ , Le code Golay (23,12) apporte un gain de codage de 3,8 dB, et le code de Hamming (7,4) apporte 1,8 dB, tandis que le code de parité apporte uniquement 1 dB par rapport au cas sans codage. Malgré cela, les performances de ces codes restent toujours médiocres par rapport aux critères de Varshamovet Gilbert. C'est pour cette raison que ces codes sont généralement utilisés dans des applications simples, par exemple dans le télétexte : on utilise le code de *Hamming* étendu (8,4)[13].

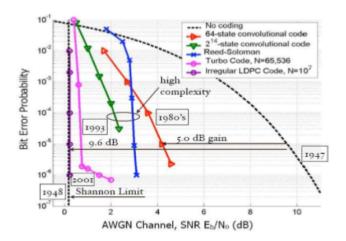

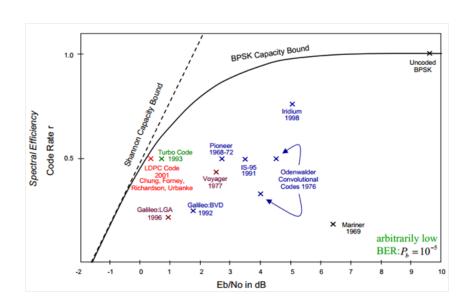

Par contre, la Figure 1.22 montre dans un ordre chronologique, l'évolution des performances des codes correcteurs. A première vue, on constate que seules les techniques de codage avancées peuvent approcher la limite de Shannon, par exemple pour une probabilité d'erreur égal à  $10^{-5}$ , un code LDPC irrégulier de taille N = 107 et de rendement R = 1/2 apporte un gain de 9,6dB et il approche la limite de Shannon de 0,04dB (Les détails sur les codes LDPC seront illustrées dans le chapitre suivant). Quant au Turbocode avec un entre laceur de tailleN=65536, le gain apporté est de 9dB et il fonctionne à moins de 0,5dB de la limite de Shannon. Pour les autres codes : le code convolutif avec 214 états, le code R-Set le code convolutif avec 64 états, ils apportent respectivement des gains de 6.5, 6 et 5dB pour un taux d'erreur égal à  $10^{-5}$ . La figure 1.23 présente une comparaison des performances des codes correcteurs d'erreurs les plus utilisées en communication. La courbe est donné présente la variation du rendement de codage en fonction de SNR.

En analysant ce résultat, on constate que seules les techniques de codage avancées comme les codes LDPC peuvent fonctionner très proche de la capacité du canal et atteindre la limite de Shannon dans des rapports signal / bruit très faibles. C'est la raison pour laquelle les codes LDPC sont utilisés dans plusieurs standard.

FIGURE 1.21 – Comparaison entre les performances des codes de parité, de Hamming et de Golay (Courbes reproduites de la référence[13]).

FIGURE 1.22 – Comparaison entre les performances des codes convolutifs, Reed-Solomon et les techniques de codage avancées (LDPC et Turbo-codes)[2].

#### conclusion 1.5

Dans ce chapitre, nous avons introduit, dans un premier temps, le schéma fondamental d'une communication numérique, en expliquant brièvement chacune de ses parties.

Ensuite, nous avons présenté quelques notions fondamentales sur le codage de canal, en introduisant le théorème fondamental de codage de canal et les différentes classes de code correcteur d'erreurs.

A la fin de ce chapitre, nous avons présenté quelques résultats sur les performances des codes correcteurs les plus connus. En analysant ces résultats, nous avons constaté que seules les techniques de codage avancées (turbo-codes et codes LDPC) peuvent fonctionner très proche de la capacité du canal et atteindre la limite de Shannon. Pour ce qui suit, notre étude sera focalisée sur des codes LDPC.

FIGURE 1.23 – Comparaison des performances des codes correcteur d'erreurs

## Chapitre 2

## Codage LDPC

Dans ce chapitre, nous entamerons la première partie du projet qui est l'étude des codes LDPC. Pour cela, nous commencerons d'abord par un bref historique sur les codes LDPC, ensuite, nous présenterons les différentes classes des codes LDPC ainsi que leurs présentations matricielle et graphique et de comprendre les différents concepts qui nous permettent d'entamer les chapitres qui se suivent.

## 2.1 Historique

Les codes LDPC ont été découverts par Gallager [21] au début des années 1960. Cette découverte remarquable a été largement ignorée par les chercheurs pendant près de 20 ans, jusqu'au travail de Tanner en 1981, dans lequel il a fourni une nouvelle interprétation des codes LDPC d'un point de vue graphique. Le travail de Tanner a également été ignoré par les théoriciens pendant environ 14 ans jusqu'à la fin des années 1990, lorsque certains chercheurs en codage ont commencé à étudier les codes graphiques et le décodage itératif. Leurs recherches ont mené à la redécouverte des codes de Gallager. Ils ont montré qu'un long code LDPC avec un décodage itératif basé sur la propagation de Believe permet une erreur de performance représentant seulement une fraction de décibel de la limite de Shannon[6]. Cette découverte fait des codes LDPC de puissants concurrents par rapport aux codes turbo pour le contrôle des erreurs lorsqu'une haute fiabilité est requise. Les codes LDPC ont l'avantage des codes turbo, il ne nécessite pas un long entrelacement pour atteindre une bonne performance d'erreur. Ainsi, en 2004, un code LDPC a d'abord été standardisé dans une émission satellite DVB-S2 [1].

Les codes «Low-density parity-check (LDPC)» sont des codes correcteurs d'erreurs, Proposés par *Gallager* pour l'obtention de sa thèse de doctorat à MIT. à cet époque l'incroyable potentiel de ces codes demeurait inexploré des calculs fastidieux qu'il nécessite pour la simulation, dans une ère où les transistors à tubes venaient juste d'être remplacés par les premiers transistors. Il demeuraient cependant négligés plus de 35 ans. Entre temps le domaine des codes correcteurs d'erreurs étaient largement dominé par les algébrique en bloc et conventionnel. Malgé les nombreux succès de ces codes, leur performances etaient

loin de répondre aux exigences théoriques des limites établies par *Shannon* dans sa publication majeur en 1948. Malgré des décennies de tentatives, les chercheurs ont échoué semble-t-il à sur passer ces contraintes pratique-théoriques.