D0002/99B

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

# THESE

المدرسة الوطنية المتعددة التقنيات المكتبة المكتبة BIBLIOTNEQUE المكتبة Ecolo Mationale Polytechnique

Présentée à

# **Ecole Nationale Polytechnique**

Département d'Electronique

Pour l'obtention du Grade de

# Doctorat d'Etat en Electronique

par

**Djamel BENAZZOUZ** Magister en électronique

# Modélisation et évaluation des réseaux d'interconnexions dynamiques par les réseaux de Petri stochastiques

Date de la soutenance : le 27 Juin 1999.

### Composition du Jury:

| Mr. D. BERKANI  | Professeur à l'ENP                     | Président   |

|-----------------|----------------------------------------|-------------|

| Mr. A. FARAH    | Professeur à l'ENP                     | Rapporteur  |

| Mr. K. HARRICHE | Professeur à l'Université de Boumerdes | Examinateur |

| Mr. M. AIDENE   | M. C. à l'Université de Tizi Ouzou     | Examinateur |

| Mr. M. DJEDDI   | M. C. à l'Université de Boumerdes      | Examinateur |

| Mr. E. BERKOUK  | Docteur d'état à l'ENP                 | Invité      |

|                 |                                        |             |

المدرسة الوطنية المتعددة التقنيات المكستبسة — BIBLIOTNEQUE المكستبسة كالمحافظة Ecole Nationale Polytechnique

à la mémoire de mon père

à ma femme, et mes enfants: Karim, Lyna, et wacim à ma mère, mes frères et soeurs.

7

المدرسة الوطنية المتعددة التقنيات المحكستيسة — BIBLIOTHEQUE Ecole Nationale Polytechnique

#### Remerciements

J'exprime ma profonde gratitude et mes remerciements à Ahcène Farah, Professeur à l'ENP et sous la direction duquel ce travail a été réalisé.

Je tiens à remercier D. Berkani, Professeur à l'ENP pour m'avoir fait l'honneur de présider mon jury.

Kamel Harriche, Mohamed Aidène, Mohamed Djeddi, E. Berkouk ont accepté de participer à mon jury, je les en remercie vivement.

Je remercie ma femme sans qui je n'aurais jamais entrepris cette thèse et qui a supporté mes longues absences du foyer; je lui exprime ma profonde gratitude.

Je remercie ma mère pour ses encouragements constants.

Je remercie toute ma famille de m'avoir soutenu et encouragé.

Je remercie aussi Mme Farida Zerari pour son aide précieuse et son amitié. Qu'elle trouve ici ma profonde gratitude et reconnaissance.

Je remercie enfin Med. Lachemi Boudjemeline qui a l'amitié de revoir la forme de la présente thèse; qu'il trouve ici l'expression de ma profonde gratitude.

المدرسة الوطنية المتعددة التقنيات | BIBLIOTHEQUE | المحكمة المتعددة التقنيات | Ecole Nationale Polytechnique

#### Résumé

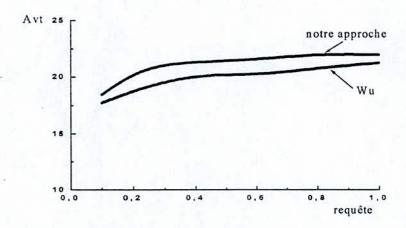

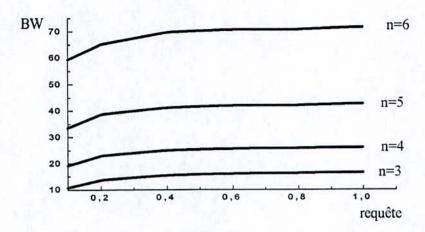

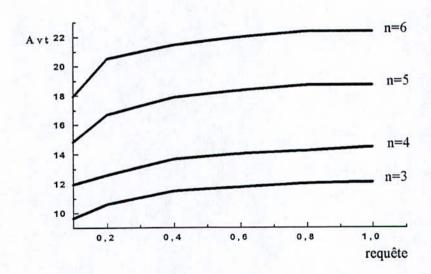

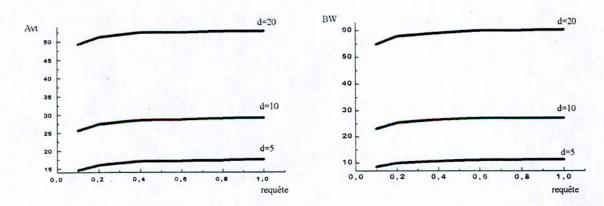

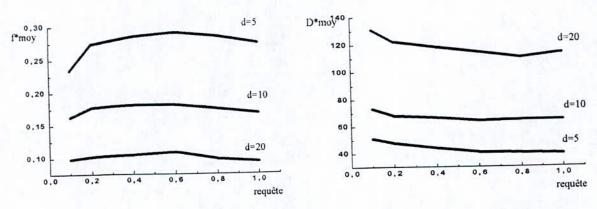

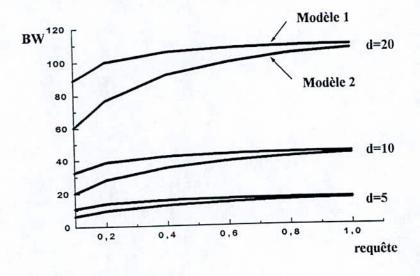

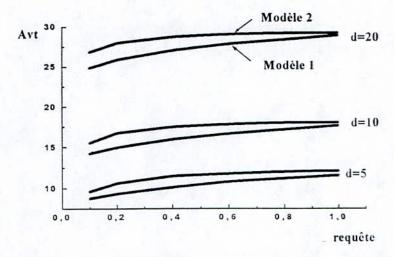

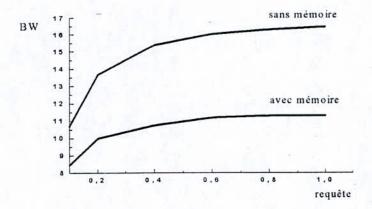

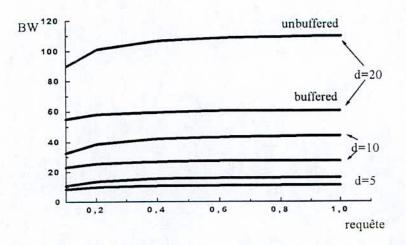

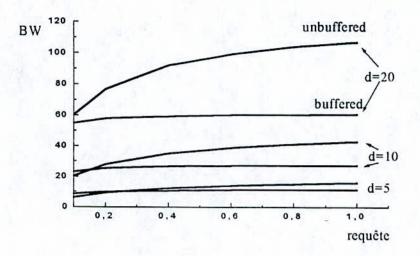

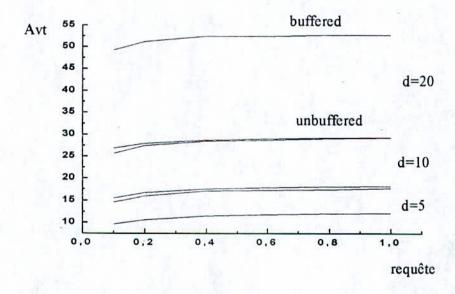

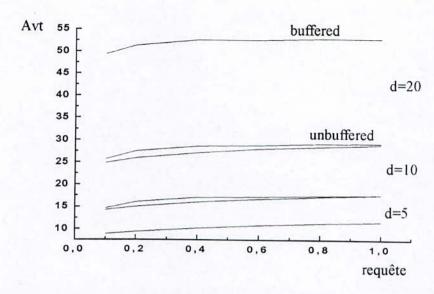

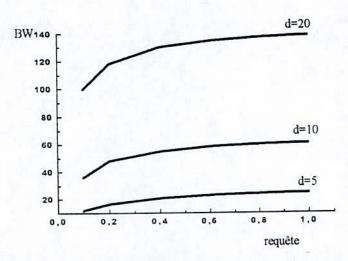

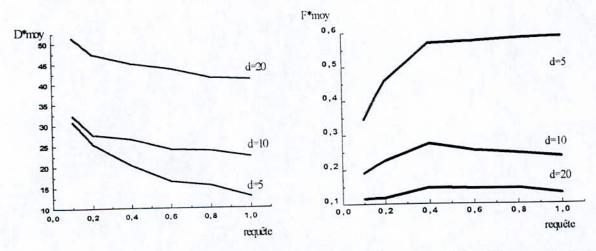

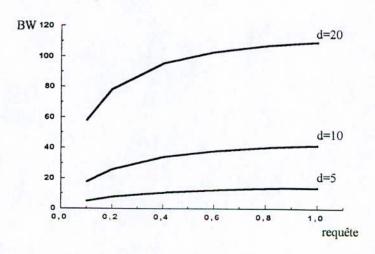

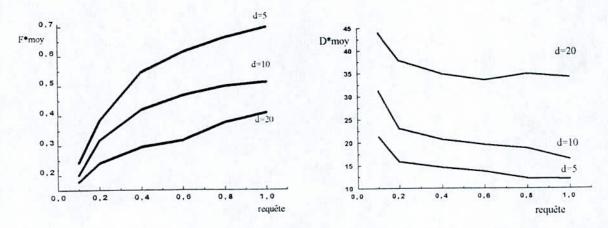

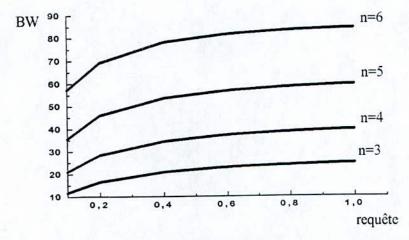

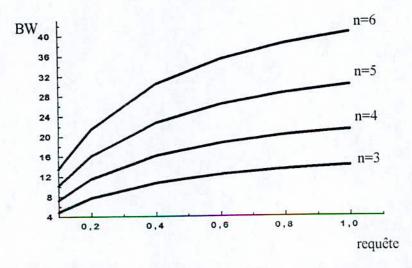

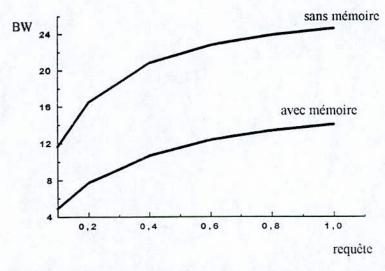

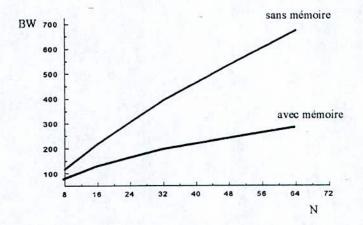

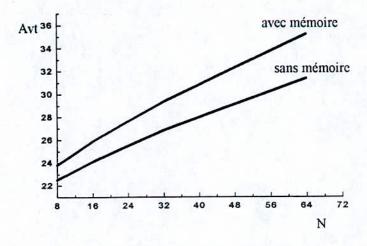

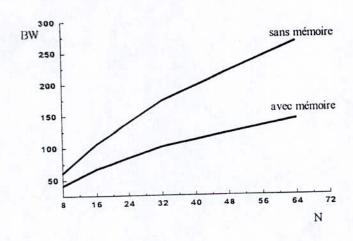

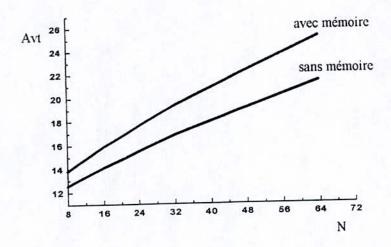

Cette thèse présente la modélisation des réseaux d'interconnexions dynamiques (RID) par les réseaux de Petri stochastiques (RdPS). Notre approche permet l'évaluation des performances des RID en présence de conflit. Ce conflit a été géré selon deux stratégies définies comme stratégie sans mémoire et stratégie avec mémoire. L'analyse des RdPS se ramène à celle d'un processus de Markov homogène à espace d'état discret à temps continu. Les modèles proposés sont des modèles simplifiés qui limitent considérablement le nombre d'état de la chaîne de Markov. La représentation d'un étage ou tour par une place réduit l'explosion des combinaisons des états de la chaîne de Markov. Les modèles s'adaptent facilement à l'extensibilité du réseau tout en gardant les propriétés de fonctionnement du réseau. Les résultats obtenus montrent qu'il n'y a pas de linéarité, d'une part, entre la bande passante (BW) ou le temps moyen de service (Avt) et la taille du réseau, et d'autre part, entre la BW ou le Avt et la longueur du message. Nous retenons que la stratégie sans mémoire est mieux adaptée aux RID, du fait qu'elle offre une meilleure fluidité de passage de messages à travers le réseau. Notre approche nous a permis de montrer que les RdPS constituent un puissant outil mathématique d'évaluation des performances des RID. Cette évaluation prend en considération, d'une part, la défaillance de la boîte de commutation, et d'autre part, la probabilité de passage ou de blocage des requêtes à travers le réseau.

Mots clés: Réseau de Petri stochastique - Processus de Markov - Réseau d'interconnexion dynamique - Système parallèle - Commutation de circuit.

المدرسة الوطنية المتعددة التقنيات المحكسسة — BIBLIOTHEQUE المحكسسة — Ecole Nationale Polytechnique

#### Abstract

This thesis presents an evaluation method of dynamic interconnection networks (DIN) using stochastic Petri nets (SPN). Our approach allows the performance evaluation of a DIN in presence of conflict. This conflict has been managed into two strategies; defined as unbuffered strategy and buffered strategy. The analysis of SPN is a homogeneous markovian process, and therefore to all SPN one could associate a homogeneous markovian chain (MC). Proposed models are simplified models that limit considerably the number of state of the MC. With the representation of a stage or a pass by a place reduce the state explosion combinations of the MC. Models are adapted easily to the scalability of the network. The obtained results show that there is no linearity, on one hand, between the bandwidth (BW) or the average service time (Avt) and the size of the network, and on the other hand, between the BW or the Avt and the length of the message. We retain that the unbuffered strategy is better adapted to DIN, because it offers a low blocking probabilities of the network. Our approach allows to show that SPN constitute a powerful mathematical performance evaluation tool of DIN. This evaluation takes in consideration, on one hand, the failure of the switching element, and on the other hand, the passing or blocking probability of requests through the network.

**Keywords:** Stochastic Petri net - Markov process - Dynamic interconnection network - Parallel processing - Circuit switching.

المدرسة الوطنية المتعددة التفنيات المكتبية — BIBLIOTNEQUE المكتبية كالمحكومة المتعاددة التفنيات

# Tables des matières

| Remerciements                                                   | i   |

|-----------------------------------------------------------------|-----|

| Résumé                                                          | ii  |

| Abstract                                                        | iii |

| Abréviations                                                    | vii |

|                                                                 |     |

| Introduction                                                    | 1   |

| Chapitre I Les machines parallèles                              | 5   |

| 1.1 Architecture d'une machine parallèle                        | 5   |

| 1.2 Les machines multiprocesseurs                               | 9   |

| 1.2.1 Les machines multiordinateurs                             | 9   |

| Chapitre II Les réseaux d'interconnexions                       | 12  |

| 2.1 Les caractéristiques d'un réseau d'interconnexion           | 12  |

| 2.2 Réseau d'interconnexion statique                            | 15  |

| 2.3 Réseau d'interconnexion dynamique                           | 16  |

| 2.3.1 Description de réseaux simples                            | 17  |

| 2.4 Les réseaux d'interconnexions à un seul étage               | 18  |

| 2.5 Les réseaux d'interconnexions à plusieurs étages            | 22  |

| 2.5.1 Réseau Clos                                               | 22  |

| 2.5.2 Réseau Butterfly                                          | 23  |

| 2.5.3 Réseau Benès                                              | 24  |

| 2.5.4 Réseau Oméga et Baseline                                  | 24  |

| 2.6. Comparaison des performances des réseaux d'interconnexions | 25  |

| Chapitre III Les réseaux de Petri                               | 27  |

| 3.1 Introduction                                                | 27  |

| 3.2 Réseaux de Petri : Définitions et Propriétés                | 28  |

| 3.2.1 Définitions de Base                                       | 28  |

| 3.2.1.1 Marquage                                                | 29  |

| 3.2.1.2 Règles de fonctionnement                                | 29  |

| 3.2.2 Analyse des RdP                                           | 30  |

| التقنيات | المدرسة الوطنية المتعددة |

|----------|--------------------------|

| BIBLISTM | المحتبة - EQUE           |

|          | ionale Polytechnique     |

| 3.2.2.1 Matrice d'incidence                                            | 30      |

|------------------------------------------------------------------------|---------|

| 3.2.2.2 Temporisation                                                  | 32      |

| 3.3 Les Réseaux de Petri Stochastiques                                 | 32      |

| 3.3.1 Pourquoi ?                                                       | 32      |

| 3.3.2 Comment définir les réseaux de Petri stochastiques               | 33      |

| Chapitre IV Modélisation des réseaux d'interconnexions à plusieurs éta | iges 35 |

| 4.1 Introduction                                                       | 35      |

| 4.2 Modélisation d'un réseau d'interconnexions à plusieurs étages      | 35      |

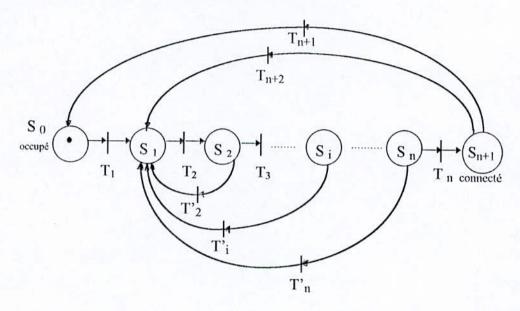

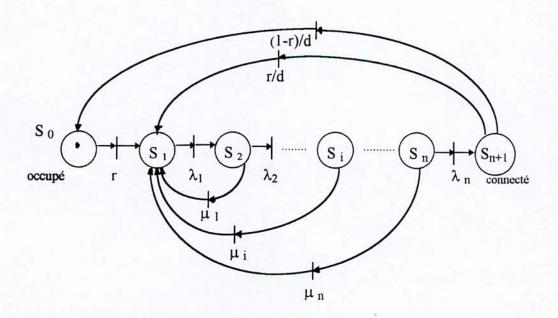

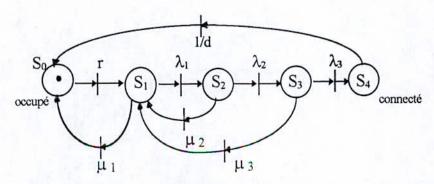

| 4.2.1 Modèle 1 sans mémoire                                            | 38      |

| 4.2.1.1 Description du modèle 1 sans mémoire                           | 39      |

| 4.2.2 Modèle 2 sans mémoire                                            | 40      |

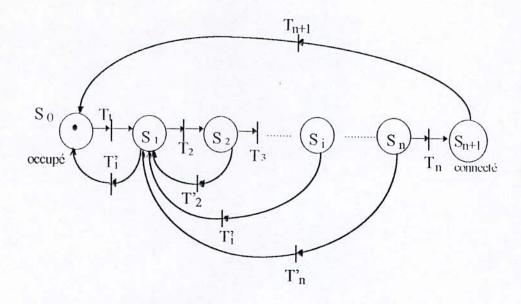

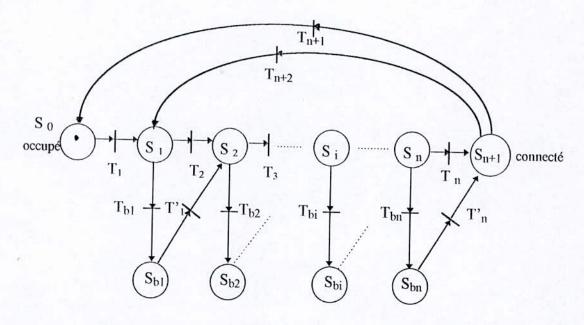

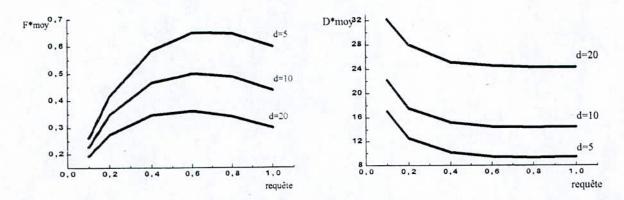

| 4.2.3 Modèle avec mémoire                                              | 40      |

| 4.2.3.1 Description du modèle avec mémoire                             | 41      |

| 4.3 Processus de Markov                                                | 43      |

| 4.3.1 Propriété de conservation                                        | 43      |

| 4.3.2 Conservation du flux en régime stationnaire                      | 43      |

| 4.3.3 Formule de Little pour les RdPS                                  | 44      |

| 4.3.4 Chaîne de Markov                                                 | 44      |

| Chapitre V Evaluation des performances des réseaux                     |         |

| d'interconnexions à plusieurs étages                                   | 48      |

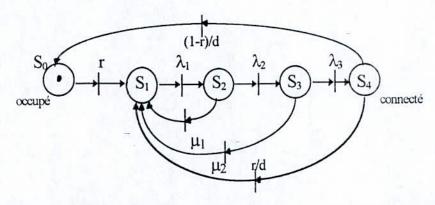

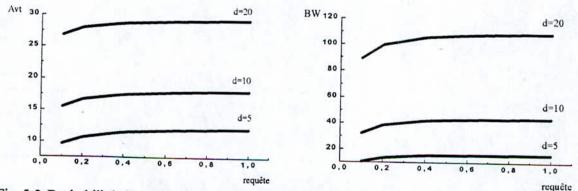

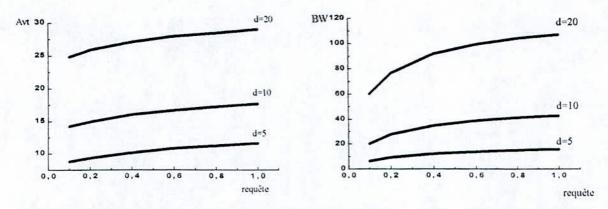

| 5.1 Evaluation du modèle 1 sans mémoire                                | 48      |

| 5.2 Evaluation du modèle 1 avec mémoire                                | 49      |

| 5.3 Algorithme de résolution                                           | 50      |

| 5.4 Applications                                                       | 51      |

| 5.4.1 Modèle 1 sans mémoire                                            | 51      |

| 5.4.2 Modèle 2 sans mémoire                                            | 57      |

| 5.4.3 Modèle avec mémoire                                              | 61      |

| 5.5 Discussion                                                         | 60      |

| Chapitre VI   | Modélisation des réseaux d'interconnexions à un seul étage | 72 |

|---------------|------------------------------------------------------------|----|

| 6.1 Intro     | oduction                                                   | 72 |

| 6.2 Mod       | lélisation du RIT selon la stratégie sans mémoire          | 74 |

| 6.2.1         | Description du modèle sans mémoire                         | 74 |

| 6.3 Mod       | lélisation du RIT selon la stratégie avec mémoire          | 78 |

| 6.3.1         | description du modèle avec mémoire                         | 79 |

| 6.4 Algo      | prithme de résolution                                      | 82 |

| 6.5 Eval      | uation du modèle sans mémoire                              | 84 |

| 6.6 Eval      | uation du modèle avec mémoire                              | 87 |

| 6.7 Disc      | ussion                                                     | 92 |

| Conclusion    |                                                            | 94 |

| Bibliographie |                                                            | 96 |

## Abréviations

المدرسة الوطنية المتعددة التقنيات المكتبة — BIBLIOTNEQUE المكتبة — Ecole Nationale Polytechnique

SISD Single instruction single data

SIMD Single instruction multi data

MISD Multiple instructions single data

MIMD Multiple instructions multiple data

M Mémoire

P Processeur

PE Processor element

RI Réseau d'interconnexion

RIP Réseau d'interconnexion à plusieurs étages

RIT Réseau d'interconnexion à un seul étage

n Nombre d'étage pour un RIP et tour pour un RIT

N Nombre d'entrée ou de sortie d'un RI

CIE Connexion interétage

BC Boîte de commutation

RdP Réseau de Petri

RdPS Réseau de Petri stochastique

W Matrice d'incidence

W Matrice d'incidence arrière

W<sup>+</sup> Matrice d'incidence avant

CM Chaîne de Markov

Q Matrice associée aux chaînes de Markov

Pi Place numéro i d'un RdP, ensemble des Places

T<sub>j</sub> Transition j d'un RdP, ensemble des transitions

M<sub>k</sub> Marquage d'un RdP

M<sub>0</sub> Marquage initial d'un RdP

M<sub>f</sub> Marquage final d'un RdP

M(P<sub>i</sub>) Marquage de la place P<sub>i</sub>

σ Séquence de franchissement

$\underline{\sigma}$  Vecteur caractéristique de la séquence de franchissement de  $\sigma$

| $T^0_{j}$                       | Ensemble de sortie T <sub>j</sub>                         | Ecole Nationale Polytechniqu |

|---------------------------------|-----------------------------------------------------------|------------------------------|

| $\mathbf{P}^{0}_{\ \mathbf{j}}$ | Ensemble de sortie P <sub>j</sub>                         |                              |

| $^{0}T_{j}$                     | Ensemble d'entrée T <sub>j</sub>                          |                              |

| $^{0}P_{j}$                     | Ensemble d'entrée P <sub>j</sub>                          |                              |

| $\mu_{i}$                       | Probabilité conditionnelle de franchissement, définie     | comme probabilité de blocage |

| $\lambda_{i}$                   | Probabilité conditionnelle de franchissement, définie o   | comme probabilité de passage |

| φ <sub>i</sub> 1                | Probabilité conditionnelle de franchissement, définie cor | nme probabilité de connexion |

| $\sigma_i$ I                    | Probabilité conditionnelle de franchissement, définie con | nme probabilité de déblocage |

| E(x)                            | Espérance mathématique                                    |                              |

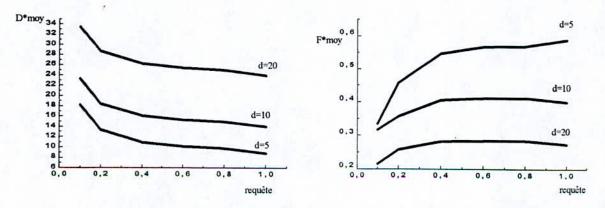

| F*moy                           | Fréquence moyenne de franchissement                       |                              |

| D*moy                           | Temps moyen de séjour dans les places                     |                              |

المدرسة الوطنية المتعددة التفنيات المحكستيسة — BIBLIOTHEQUE المحكستية المحكستية المحكودة المحكسة المحكودة المحكسة المحكودة المحكسة ال INTRODUCTION

7

المدرسة الوطنية المتعددة التقنيات المكتبة — BIBLIOTNEQUE الحكتبة — Ecole Nationale Polytechnique

# Introduction

Le développement de l'informatique et de ses applications a entraîné une demande sans cesse croissante en puissance de calcul. Pour répondre à ces besoins, les machines parallèles ont reçu un intérêt tout particulier. De ce fait, de nombreux domaines de recherche nouveaux ont émergé; par exemple, les langages parallèles, la parallélisation automatique, les architectures distribuées, les environnements de programmation, l'analyse de complexité parallèle et l'algorithme parallèle.

Actuellement, la plupart des machines existantes reposent sur des architectures à mémoire distribuée. Une des différences essentielles entre les machines traditionnelles, dites de "Von Neumann", et les réseaux de processeurs que sont les machines à mémoire distribuée, réside dans la gestion des communications. Si on cherche à distribuer le plus possible les traitements élémentaires, on obtient le parallélisme potentiellement le plus efficace, mais les communications induites à travers les réseaux peuvent être alors pénalisantes. Optimiser les communications est donc une des clefs de l'efficacité des algorithmes parallèles.

Si on peut souhaiter une modélisation complète des calculateurs parallèles qui prendrait en compte à la fois le réseau d'interconnexion, les calculs parallèles et les communications associées, la difficulté de sa réalisation apparaît bien vite; seuls quelques résultats particuliers concernant le recouvrement des communications et des calculs existent (dans ce cadre les seuls résultats existants sont en général associés à des instances particulières de machine) [ETU 95]. Notons au passage que le nombre de modèles ''globaux'' est d'un coup déraisonnablement élevé, puisqu'un modèle complet doit prendre en compte la vitesse relative des instructions de calcul et de communication, leur parallélisme ou non, etc...

Ainsi, à l'heure actuelle, il semble raisonnable d'étudier séparément les calculs et les communications, puis, dans le cas d'une application réelle, tenter de prendre en compte les spécificités de l'architecture utilisée en espérant qu'un bon algorithme, muni de bonnes routines de communications, fournisse un résultat efficace.

Les besoins actuels en matière de calcul qui se manifestent dans différents domaines nécessitent des systèmes informatiques de plus en plus puissants. Ainsi, des projets importants et ambitieux ont pu être mis en oeuvre, tel le programme HPCC (Highly Parallel Computing and Communication) aux Etats-Unis [TMC 91]. L'objectif de ce type de projets est d'élaborer des calculateurs suffisamment puissants pour faire en sorte que les performances actuellement visées soient atteintent. Ceci est une nécessité pour les applications qui demandent de plus en plus de performances, comme la modélisation du climat, la modélisation des semi-conducteurs, des supraconducteurs,...

Les besoins en calcul sont sans cesse croissants; cela a poussé les architectes de systèmes informatiques à s'intéresser aux systèmes parallèles. En effet, les chercheurs, profitant du parallélisme d'exécution de plusieurs processeurs, espèrent atteindre la machine idéale qui réalise les 1000 TeraFlops (soit 10<sup>15</sup> opérations par seconde en virgule flottante 64 bits) [REW 97].

La puissance de calcul d'une machine parallèle est potentiellement proportionnelle au nombre de processeurs qu'elle comporte. Cependant, le choix d'une machine pour une application donnée reste toujours posé. L'évaluation des performances des machines parallèles, particulièrement en ce qui concerne les réseaux d'interconnexions, discipline dans laquelle s'inscrit cette thèse, apporte un plus d'information qui permette de répondre à cette question.

L'évaluation des performances d'une machine parallèle consiste en la mesure des grandeurs caractéristiques de son comportement, telles que les vitesses de ses principaux composants (processeur, mémoire, périphérique, etc...), et les liens entre ces principaux composants (disponibilité, capacité de transport d'information, etc...). L'évaluation des performances d'un programme consiste en la mesure des durées caractéristiques de son exécution, comme par exemple la durée totale; ou pour un programme parallèle le temps qu'un processus de ce programme va passer en état bloqué (plus ce temps est long, plus le programme a des chances d'être inefficace).

C'est dans ce contexte que se situe la partie de notre travail dont le but est en effet d'étudier l'évaluation des performances, des réseaux d'interconnexions par les réseaux de Petri stochastiques. Le modèle que nous proposons est constitué de paramètres représentant les différents éléments de la machine tels que les processeurs, les mémoires, les liens de connexions, ainsi que les paramètres architecturaux tels que le nombre de processeurs, la taille mémoire disponible sur chacun des noeuds. Tous ces paramètres caractérisent le type de machine parallèle.

La contribution de notre travail de recherche consiste à la simplicité du modèle proposé. Les systèmes d'une machine parallèle sont tellement complexes que l'évaluation de leurs performances est très difficile. Le choix de ramener les réseaux de Petri stochastiques au processus de Markov à espace d'état discret, simplifie considérablement la modélisation d'un tel système. Notre approche permet aussi d'identifier les paramètres qui interviennent directement ou indirectement dans l'évaluation des performances des réseaux d'interconnexions dynamiques.

Ce travail comprend six chapitres.

Le premier chapitre concerne les différents aspects des machines parallèles. Nous décrirons particulièrement les diverses topologies qui caractérisent l'architecture d'une machine parallèle. Nous donnerons la classification, fondée par Flynn [FLY 72], de ces machines. Puis nous énumérerons quelques exemples de structure de machines parallèles.

Le deuxième chapitre présente les principales caractéristiques d'un réseau d'interconnexion (RI). Nous présenterons quelques topologies d'un RI dynamique particulièrement les RI à plusieurs étages (RIP) et les RI à un seul étage (RIT). C'est dans ce contexte que se situe la partie la plus importante de notre travail de recherche. On trouve beaucoup de travaux sur les RIP mais relativement peu de travaux concernent les RIT.

Le troisième chapitre concerne les réseaux de Petri (RdP) qui sont un outil mathématique très utilisé actuellement dans la modélisation des activités asynchrones ou synchrones, concurrentes et parallèles. Nous citerons les avantages principaux des RdP avec l'ensemble de bases et règles de fonctionnement. Enfin, nous présenterons l'extension des RdP aux réseaux de Petri stochastiques (RdPS). Les RdPS occupent une place privilégiée; d'une part, parcequ'ils permettent d'exprimer facilement les mécanismes premiers des systèmes distribués (le parallélisme et la synchronisation) d'autre part, parcequ'ils fournissent des méthodes d'analyses éprouvées très efficaces [FLO 90]. Par la suite nous utiliserons les RdPS à distributions exponentielles qui ont été suggérés par Molloy [MOL 81], Natkin [NAT 80], et Zuberek [ZUB 85]. L'analyse de ce type de modèle passe par l'étude de la chaîne de Markov continue associée au processus stochastique sous-jacent au modèle. Enfin nous donnerons les motivations quant au choix de cet outil.

Le quatrième chapitre décrira la boîte de commutation et une classe des RIP dont le réseau baseline qui est considéré dans le cadre notre approche. Nous présenterons la modélisation des RIP par les RdPS, ainsi que les hypothèses retenues. Dans la première partie de ce chapitre, une généralisation de la modélisation des RIP est développée selon

deux types de stratégies: sans mémoire puis avec mémoire. Dans la deuxième partie nous montrerons que l'analyse d'un RdPS se ramène à celle d'un processus de Markov homogène à espace d'état discret à temps continu.

Dans le cinquième chapitre nous donnerons l'application de notre approche pour des modèles à 3 étages des RIP.

Le sixième chapitre sera consacré à l'application d'une modélisation des RIT selon les deux stratégies retenues pour des modèles à 3 étages.

La dernière partie exposera les conclusions du présent travail.

# Les machines parallèles

Ce chapitre présente les différents aspects des machines parallèles. Partant du niveau bas, nous décrirons tout d'abord les principales caractéristiques matérielles, c'est à dire les différentes familles de machines parallèles et les différentes topologies (graphes de connexion entre les noeuds de calcul).

L'architecture des ordinateurs a connu d'importantes mutations. Depuis le modèle d'architecture de Von-Neumann proposé dans les années 50 et pendant une vingtaine d'années, les progrès ont essentiellement concerné l'exploitation des apports de l'électronique. Il a fallu attendre les années 80 pour connaître les premières machines RISC (Reduced-Instruction-Set Computing) qui ont permis de lancer des projets précurseurs sur le développement des architectures parallèles. Les évolutions technologiques, notamment les possibilités qu'offrait la micro-électronique avec l'arrivée des premiers circuits VLSI (Very Large Scale Integration), ont été le plus grand stimulant du développement de la nouvelle branche de l'architecture des machines parallèles.

En réalité, le développement des machines parallèles ne fait pas seulement appel au développement architectural mais également à la définition de nouveaux modèles de calcul non séquentiels, c'est à dire ne comportant pas forcément un compteur ordinal qui cadence l'exécution des instructions les unes après les autres. En effet, ces modèles se basent sur une nouvelle organisation des instructions (neuronale, concept 'demand-driven', ...) et s'appuient sur l'organisation intrinsèquement parallèle des applications. Il peut s'agir aussi bien d'un parallélisme de contrôle que de données.

#### 1.1 Architecture d'une machine parallèle

Une machine parallèle est composée de plusieurs processeurs pouvant réaliser des calculs simultanés. Une telle machine comprend donc des processeurs, de la mémoire et des gestionnaires d'entrée/sortie. Il existe actuellement de nombreuses machines parallèles. Elles peuvent être classées selon divers critères. Une classification générale devrait d'une part, tenir compte des éléments introduits par Flynn dans sa classification qui prend en

compte le flux d'instructions et de données [FLY 72] et d'autre part de proceder à l'évaluation de ces machines.

En effet, certaines machines élaborées ne peuvent pas être classées selon les critères introduits par Flynn: machine à base de processeurs vectoriels pipelinés, machines 'Data-Flow', ...[SAN 91], [DUN 90], [ETU 95]. La classification de Flynn est fondée sur le fait que la machine parallèle possède un ou plusieurs flux de données et d'instructions. La combinaison entre ces deux paramètres aboutit à quatre types d'architectures résumées dans le Tableau 1

|                |          | Flux de | données  |

|----------------|----------|---------|----------|

|                |          | Simple  | Multiple |

| Flux           | Simple   | SISD    | SIMD     |

| d'instructions | Multiple | MISD    | MIMD     |

Tableau 1. Taxinomie des architectures parallèles proposée par Flynn.

Nous pouvons considérer les machines parallèles comme étant divisées en deux grandes classes: les machines synchrones et les machines asynchrones.

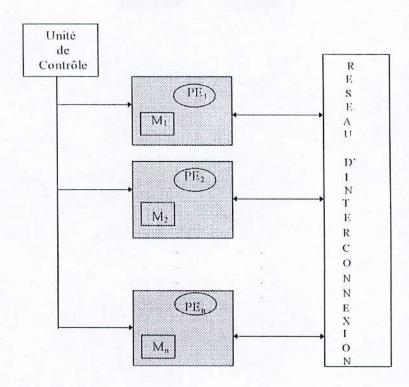

# a) Machines synchrones

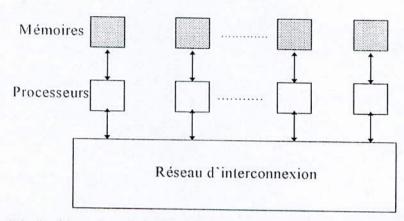

Ces machines comportent des unités de calcul (processeurs câblés) qui exécutent la même instruction par unité de contrôle centralisée commune (voir Figure 1.1). Un réseau d'interconnexion permet d'assurer la communication des processeurs entre eux ou des processeurs aux mémoires.

La classe SIMD (Single Instruction Multiple Data) est la machine pour laquelle tous les processeurs exécutent la même instruction sur des données différentes. Le comportement de ce type de machines est synchrone. Son fonctionnement est très intéressant pour le traitement des images bidimensionnelles, où la même opération est effectuée sur tous les pixels. Un exemple bien connu de machines SIMD correspond à la CM2 (Connection Machine 2 de Thinking Machine et la Maspar) [TMC 91].

Fig. 1.1 Organisation générale d'une machine SIMD. (PE: processor element, M: memory).

Les machines synchrones présentent l'avantage d'un modèle de programmation simple qui se rapproche du modèle de programmation séquentiel classique. Cela facilite leur exploitation. Néanmoins, en vue d'une utilisation massivement parallèle, les machines SIMD restent limitées surtout en ce qui concerne les contraintes technologiques relatives à la diffusion d'une instruction à des milliers de processeurs [ETU 95].

En effet, il est pratiquement très difficile d'assurer un contrôle centralisé des instructions quand le nombre de processeurs dépasse une certaine limite [UPL 94].

#### b) Machines asynchrones

La classe MIMD (Multiple Instruction Multiple Data) pour laquelle les processeurs sont plus indépendants, et peuvent exécuter des instructions différentes sur des données différentes. Le comportement de ces machines est asynchrone.

#### Remarque:

La plupart des machines fonctionnent aujourd'hui en mode MIMD; cependant elles sont souvent programmées en mode SPMD (Single Program Multiple Data). Ce mode

intermédiaire est dérivé des deux modes précédents; il est très répandu actuellement, et signifie que tous les processeurs exécutent le même code sur des données différentes. Il faut faire attention au fait que ce mode caractérise la programmation et non le fonctionnement matériel de la machine.

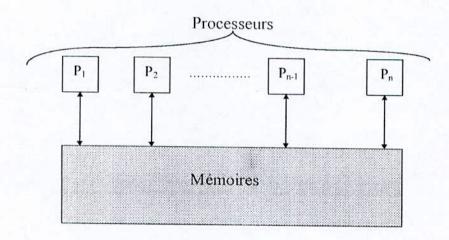

Un autre critère est utilisé pour classer les machines parallèles; il concerne l'architecture de leur mémoire et l'on distingue alors deux types de machines:

Soit que la mémoire correspondante est partagée et/où les processeurs partagent donc les données d'un programme; l'organisation d'une telle machine est schématisée par la figure

1.2 et se présente de telle façon que tous les processeurs accèdent à la même mémoire.

Fig. 1.2 Architecture schématique d'une machine parallèle à mémoire partagée.

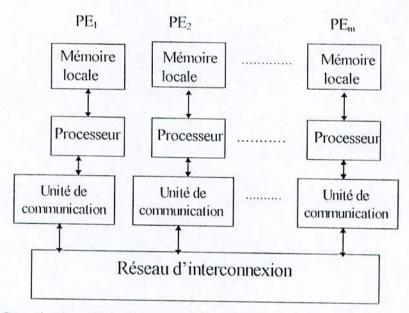

- Soit que la mémoire correspondante est distribuée et/où chacun des processeurs possède sa mémoire. La coopération (échange de données) et la synchronisation entre processeurs ne peut alors se faire que par l'intermédiaire de liens de communications; c'est à dire par l'échange de messages (ou par communication). L'ensemble de liens de communication d'une machine est appelé le **réseau de communication** ou **réseau d'interconnexion**. L'organisation d'une telle machine est schématisée par la figure 1.3.

L'architecture des machines parallèles à mémoire partagée, ou distribuée sont dites respectivement machines multiprocesseurs ou multiordinateurs.

Les multiordinateurs sont plus adaptées à une perspective de machines massivement parallèles, car dés que le nombre de processeurs atteint une certaine limite, le partage d'une mémoire devient pratiquement impossible. La structure physique de la mémoire peut ne pas directement correspondre au modèle de programmation et d'exécution.

Fig. 1.3 Architecture schématique d'une machine parallèle à mémoire distribuée.

## 1.2 Les machines multiprocesseurs

Bien que ces machines ne soient pas adaptées à une perspective de machines massivement parallèles, leur évolution présente un double intérêt. D'une part, leur modèle de programmation reste très souple et très utilisé dans les machines à multiordinateurs (en se basant sur un espace d'adressage unique). D'autre part, des performances intéressantes sont atteintes par ces machines, notamment celles formées à base de groupes ou "clusters" telle que la machine EXEMPLAR. Comme exemple de machines multiprocesseurs, on peut citer la KSR (Kendell Square Research), les machines vectorielles CRAY (XMP et YMP),...[RAM 93]

# 1.2.1 Les machines multiordinateurs: Machines MIMD à passage de messages

Ces machines dont l'organisation générale est présentée sur la figure 1.4, sont dites massivement parallèles. Parmi les machines MIMD développées et commercialisées, nous citons la CM-5 de TMC (Thinking Machine Corporation), et la Paragon d'INTEL. L'exemple de la CM-5 [TMC 92] représente bien ce type de machines. En effet, elle tire profit des modèles d'exécution d'autres architectures (SPMD susceptible de se substituer au SIMD sur des processeurs standards) et exploite également les performances de processeurs SPARC ainsi que des mémoires dynamiques (surmontant ainsi le coût des mémoires statiques).

Le but des constructeurs est de mettre de plus en plus de processeurs dans les machines puisqu'a priori cela multiplie d'autant la puissance de calcul. Les très grosses mémoires étant difficiles à construire et souvent plus lentes, les machines parallèles à mémoire partagée comportent peu de processeurs (moins de 64) et la majorité des machines présentées actuellement sur le marché sont à mémoire distribuée.

Fig. 1.4 Organisation générale des machines MIMD à passage de messages

L'augmentation de la puissance de calcul est, en fait, fonction de plusieurs paramètres; on citera les paramètres essentiels tel que le type de mémoire, les processeurs, l'architecture adoptée et le réseau d'interconnexion. On voit beaucoup de recherches orientées vers les performances des mémoires et des processeurs mais relativement peu de recherche portant particulièrement sur les réseaux d'interconnexions.

Dans cette thèse nous nous intéressons particulièrement aux RI. Ces réseaux sont généralement choisis pour respecter deux contraintes: facilement extensibles et assurer un lien de connexion entre chaque entrée et sortie. L'augmentation de la puissance de calcul des machines parallèles passe théoriquement par l'ajout de processeurs, il faut donc que cet ajout de noeuds soit facile et ne change pas fondamentalement les propriétés du réseau, c'est ce que nous appelons la contrainte d'extensibilité.

On sait donc construire des réseaux complètement connectés que l'on appelle commutateurs mais pour un petit nombre de processeurs (<64) [TMC 92]. Pour avoir un nombre de processeurs intéressant, les constructeurs se sont d'abord tournés vers d'autres

réseaux facilement extensibles, telles que les grilles ou tores 2D ou 3D (par exemple Computing Surface de Meiko, Transputers de Telmat), et les hypercubes (par exemple n Cube, CM2, iPSC) [RAM 93].

On distingue aussi une nouvelle génération de réseaux tels que le réseau de la dernière née de Thinking-Machine (fat-tree) [LEI 85], et les réseaux de la CS2 et de la SP1 qui sont des réseaux Omega. On reviendra avec plus de détail sur ces types de réseaux dans le chapitre II qui présentera les RI.

## Les réseaux d'interconnexions

#### 2.1 Les caractéristiques d'un réseau d'interconnexion

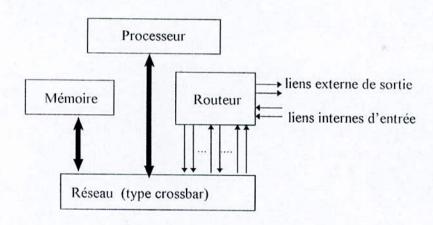

Les réseaux d'interconnexions d'une machine parallèle se présente comme un réseau d'interconnexion point-à-point. Chaque point ou noeud est généralement matérialisé par une entité complexe composée de différents modules: processeur (s), mémoire (s) externes et/ou composants de gestion et routage ou routeur des communications. La figure 2.1 schématise un modèle de noeud d'un réseau.

Fig. 2.1 Schématisation d'un noeud.

Dans une telle schématisation, nous considérons que le processeur (généralement de calculs) échange des messages avec le reste du réseau par l'intermédiaire d'un commutateur ou routeur. Dans ce cas, certains liens alimentent le routeur depuis le processeur, ou utilisent des messages en provenance du réseau. Ces liens sont des canaux internes du noeud. D'autres au contraire permettent le transit de messages par le routeur, ce sont les canaux externes. Le rôle d'un routeur est d'acheminer les messages entre noeuds non voisins. Les routeurs réalisent de façon distribuée un algorithme de routage qui spécifie le chemin à suivre dans le réseau pour se rendre de tout noeud x vers tout noeud y. Cet algorithme de routage est décrit par une fonction de routage [FRA 95].

Généralement on distingue 4 caractéristiques dans un RI [FEN 81], [BHU 87]:

#### a) Temps (Timing)

Le temps peut être synchrone où asynchrone. Les systèmes synchrones sont utilisés par exemple dans une configuration de noeuds en ligne (array). Une horloge centrale est utilisée pour que les processeurs dans les noeuds communiquent de façon synchrone. Les systèmes asynchrones ne disposent pas d'une horloge centrale qui contrôle les communications. Les requêtes de connexions sont issues des processeurs de façon asynchrone.

#### b) Mode de commutation (Switching)

Dans un RI point-à-point, la transmission d'un message entre processeurs non directement voisins, doit être routé via des noeuds intermédiaires. Comme schématisé sur la figure 2.1, nous considérons ici que le routeur de message se fait par l'intermédiaire de routeur implanté dans chaque noeud. La commutation d'un routeur est le phénomène consistant en la réception d'une adresse de destination, puis au décodage de cette adresse pour déterminer le canal de sortie convenable et à l'envoi de cette adresse sur ce canal. Mais il existe différents mécanismes physiques ou technologiques de commutation utilisés par les routeurs. Ces différences de mécanismes sont en partie dues au progrès et à la maîtrise technologiques acquises par les différents constructeurs au cours du temps.

Néanmoins, tous les types de commutations ont, dans certains cas, des avantages et dans d'autres, des inconvénients. On trouve une présentation des diverses techniques de commutation classiques dans le rapport Uplal [UPL 94] et du livre de J. de Rumeur [RUM 94].

Nous citons les différents modes classiques qui nous permettent de mieux comprendre l'échange d'information entre processeurs et mémoires à travers un RI. Ces modes de commutations sont présentés en partie dans le livre de J. de Rumeur [RUM 94].

#### \* Commutation de messages (Store-and -forward)

Il s'agit certainement du modèle le plus simple et le plus ancien (modélisant la quasitotalité des machines parallèles jusqu'au début des années 90).

Dans ce cas, les communications s'effectuent entre voisins [SAA 89]. Les messages avancent dans le réseau vers leur destination en transitant dans les noeuds intermédiaires. Un en-tête contenant un identificateur du destinataire est ajouté au message. Ainsi, le

message est stocké avant d'être réémis (d'où le terme anglais consacré dans le cadre des machines distribuées 'store-and-forward') par un noeud intermédiaire. A chaque étape, le canal emprunté est aussitôt libéré. Un défaut de cette technique est de nécessiter une taille de registre importante pour stocker le message sur les processeurs intermédiaires. En fait, ces messages sont généralement stockés en mémoire. Mais les temps d'accès à la mémoire, proportionnels à la taille des messages, ralentissent alors fortement les communications. Exemples, la Computing Surface de Meiko; le T-node et le Mega-node de Telmat, les Voltex d'Archipel, ainsi que les autres machines à base de transputers utilisent un routage par commutation de messages [UPL 94].

# \* Commutation par paquets (Packet Switching)

Ce mode dérive du précédent. En effet, cette fois les messages sont découpés en paquets de taille fixe; on bénéficie alors d'un effet pipeline. Cela signifie que les paquets sont envoyés les uns à la suite des autres: le second n'attend pas que le premier soit arrivé à destination. Les paquets sont routés indépendamment les uns et des autres, car chacun possède un en-tête l'adresse de destination, ils peuvent même emprunter des chemins différents. Notons que ceci implique, par rapport à la commutation de messages, un surplus de communications engendré par le supplément d'information ajouté à chaque paquet. De plus, la recomposition du message à partir des différents paquets demande également le transport d'un supplément d'information sur chaque paquet. Par contre, l'avantage de ce mode de commutation est de pouvoir utiliser des registres de petite taille, locaux au routeur. La capacité de stockage nécessaire sur un noeud pour un canal se limite à la taille d'un paquet.

# \* Commutation de circuit (Circuit Switching)

Dans ce mode, l'en-tête est envoyé en premier et s'il peut atteindre la destination, il réserve le chemin par lequel il est passé. Le message est alors envoyé directement de la source à la destination, sans être stocké sur les processeurs intermédiaires qui le laissent passer. Les messages qui voudraient emprunter tout ou partie de ce chemin restent bloqués jusqu'à ce qu'ils soient libérés. C'est le principe du téléphone. On établit d'abord la liaison (cela consiste en la matière à réserver une suite de canaux); la conversation commence ensuite.

Exemple: le direct-connect, qui est proposé par Intel sur les hypercubes de la série iPSC/2 et iPSC/860 est un routage par commutation de circuits.

#### c) Stratégie de contrôle

La stratégie de contrôle d'un RI peut être centralisée ou distribuée. Dans un contrôle centralisé, un contrôleur général reçoit toutes les requêtes de communications et assure la commutation nécessaire pour établir la connexion entre la source et la destination. Dans un contrôle distribué, un contrôleur local gère les requêtes de communications de façon distribuée.

#### d) Topologie

La topologie d'un réseau détermine l'interconnectibilité entre deux noeuds (entrée et sortie). Il existe deux classes de topologies; statique et dynamique. La topologie statique possède des liens dédiés entre les noeuds; ces liens sont figés et ne peuvent être reconfigurables. Par contre, la topologie dynamique possède des liens entre les noeuds qui peuvent être reconfigurés.

Nous nous intéressons dans cette thèse à la toplogie dynamique. Beaucoup de recherches ont investi la topologie statique; on trouve peu de recherches sur la topologie dynamique; en fait, il s'agit de la nouvelle génération de machines parallèles.

Plusieurs structures de RI existent [FEN 81]. Ces réseaux ont une topologie statique, adoptent un temps asynchrone, utilisent un mode de commutation par paquet, basé sur un contrôle distribué.

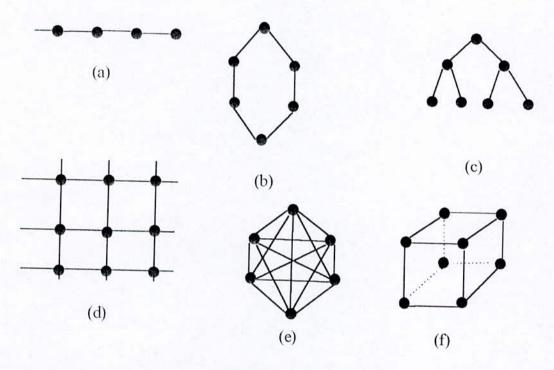

## 2.2 Réseau d'interconnexion statique

La figure 2.2 montre quelques RI à topologie statique. La figure 2.2 (a) montre une topologie unidimensionnelle définie comme topologie linéaire (linear array). C'est la plus simple des topologies et peut être utile dans les systèmes à pipeline. La figure 2.2 (b), (c) et (d) montre une topologie bi-dimensionnelle. Ceci est obtenu en fermant la topologie linéaire de la figure 2.2 (a) pour former un anneau (ring). L'anneau est un réseau très utilisé à cause de sa structure simple et de sa facilité d'extension (par exemple, le Token-ring d'IBM). De plus, de nombreux algorithmes ont été écrits pour l'anneau [RUM 94].

La topologie en arbre binaire (Tree) de la figure 2.2 (c) est une topologie régulière mais asymétrique. La figure 2.2 (e) et (f) montre une topologie tridimensionnelle. L'arbre binaire complet (Fully connected) est le plus complexe; chaque noeud est connecté à un autre noeud. Il s'agit là aussi d'un réseau très courant, en particulier pour interconnecter un petit nombre de processeurs. De nombreux algorithmes ont été écrits pour cette structure.

Fig. 2.2 Exemples de topologie statique. (a) arbre linéaire ou bus, (b) anneau ou cycle, (c) arbre binaire complet, (d) mesh, (e) anneau complet, (f) 3-cube.

Il existe aussi d'autre type de topologie statique tel que l'hypercube qui est un réseau utilisé dans plusieurs machines parallèles comme les ncube de nCUBE, les iPSC-1, 2 et 860 d'Intel ou les connection Mahines (CM-1 ou CM-2).

# 2.3 Réseau d'interconnexion dynamique

Nous venons de présenter la construction des réseaux de processeurs les plus usuels. Ces réseaux ont une configuration statique, dans le sens où la topologie est fixée une fois pour toutes. Il existe une seconde catégorie de réseaux dont la topologie est dynamique, c'est à dire pour lesquels le support physique est fixé, mais où des commutateurs (switches), généralement appelé boîte de commutation, permettent de modifier le schéma de connexion. On dit que ces réseaux sont reconfigurables par opposition aux réseaux statiques.

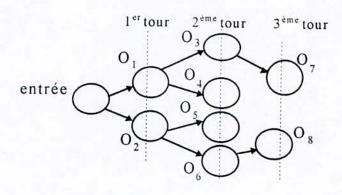

En effet, ces réseaux comprennent des boîtes de commutations qui peuvent être positionnées de manière différente dans le temps et qui, suivant leur position, permettent d'obțenir la connexion désirée. Dans ce type de réseau on distingue deux classes: réseau d'interconnexion à un seul étage (RIT) et réseau d'interconnexion à plusieurs étages ou multiétages (RIP). Le terme 'multiétage' signifie que les commutateurs, qui sont les briques de base du réseau, sont organisés en étages. Un étage est composé de commutateurs. Chaque commutateur possède un certain nombre de liens d'entrée et de sortie. Plusieurs étages sont juxtaposés. Si un réseau est constitué de n étages, numérotés en général de 0 à n-1, les sorties des commutateurs de l'étage  $\mathbf i$  (que l'on appelle plus brièvement sorties de l'étage  $\mathbf i$ ) ne peuvent être directement liées qu'aux entrées de l'étage  $\mathbf i+1$  (entrées de commutateurs de l'étage  $\mathbf i+1$ ), ceci pour tout  $\mathbf i$ ,  $0 \le \mathbf i \le \mathbf n-2$ . L'ensemble des liens d'entrée de l'étage  $\mathbf 0$  constitue des liens d'entrée du réseau.

Dans un réseau multiétages, il n'est possible d'établir une nouvelle liaison qu'entre une entrée libre du réseau (processeur source) et une sortie libre du réseau (un banc mémoire destination), c'est à dire une entrée et une sortie qui ne sont pas en cours de communication.

## 2.3.1 Description de réseaux simples

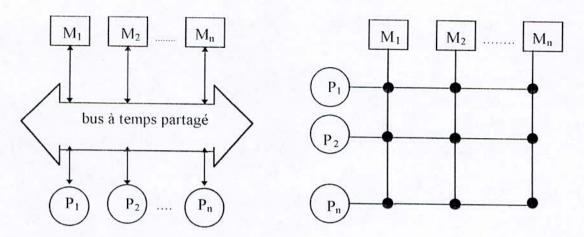

La complexité des réseaux multiétages se mesure en nombre de commutateurs élémentaires ou point de croisement mis en jeu dans le réseau. Le plus simple de ces réseaux est le *bus* utilisé en temps partagé, représenté dans la figure 2.3. Tout processeur (source) est relié à toute mémoire (destination) par l'intermédiaire du même bus, mais une seule requête peut être envisagée à la fois. En effet, dès que le bus est utilisé pour relier un processeur à une mémoire, il faut attendre qu'il se libère pour relier un autre processeur à une autre mémoire. La mise en oeuvre est en général facile.

Le réseau le plus complexe est le **crossbar**. Dans ce type de réseau, il existe toujours une liaison possible entre tout couple de noeuds libres (processeur vers banc mémoire), indépendamment des liaisons déjà existantes. On peut représenter un réseau crossbar par une grille (P, M), les P processeurs étant en tête des lignes, les M bancs mémoires en tête de colonnes, telque représenté dans la figure 2.4, avec un interrupteur à chaque point de croisement entre une ligne et une colonne. Chaque processeur P; est alors relié à la mémoire M; en fermant l'interrupteur se trouvant au point de croisement de la ligne i et la colonne j.

Fig. 2.3 Liaison par bus à temps partagé

Fig. 2.4 Topologie crossbar

Le réseau crossbar est malheureusement le réseau le plus coûteux qui permette de réaliser toute permutation en établissant des liaisons dans un ordre quelconque. Le nombre de points de croisement est égal au produit du nombre de processeurs par le nombre de bancs mémoires, c'est à dire de  $l'O(N^2)$  en supposant N-entrées / N-sorties.

Dans les réseaux dynamiques on cherche à construire des commutateurs dans lesquels chaque processeur soit potentiellement connecté à tous les bancs mémoire via le réseau multiétages [RUM 94] [HWA 93].

Le réseau crossbar est considéré comme un réseau à un seul étage du fait qu'il est construit avec un seul commutateur au point de croisement.

les réseaux crossbar (P, M) permettent de réaliser toutes les permutations des entrées. En d'autres termes, quelle que soit la permutation  $\pi$  de { 0, 1, 2, ....., p<sub>-1</sub>}, il existe un état du réseau qui permet simultanément d'associer à toute entrée  $E_i$ , la sortie  $S\pi(i)$ . Un état du réseau correspond à une position donnée de chaque interrupteur, et donc, dans ce cas, la permutation  $\pi$  est réalisée en fermant tout i, l'interrupteur situé à l'intersection de la ligne i et de la colonne  $\pi(i)$ .

Il est difficile aujourd'hui de construire des réseaux crossbar avec plus de 32 entrées à cause de la complexité des coûts et des délais de réalisation. Aussi les constructeurs proposent-ils d'autres alternatives que sont les RIT et les RIP.

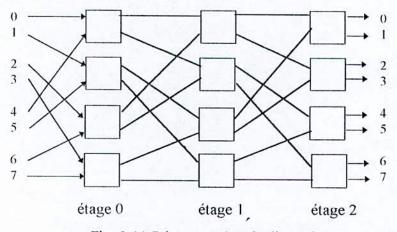

# 2.4 Les réseaux d'interconnexions à un seul étage

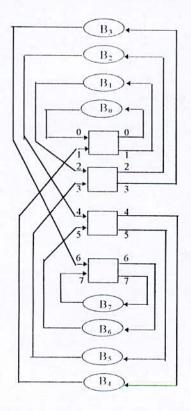

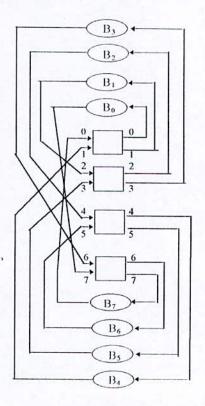

La figure 2.5 montre un RIT. Ce réseau à N=8 entrées et N=8 sorties. Le réseau consiste à un seul étage avec quatre commutateurs. La liaison entre ces commutateurs

détermine la topologie du réseau. Chaque commutateur a 2 entrées et 2 sorties (on dit que c'est un commutateur 2x2), qui peut être contrôlé pour établir une connexion interne en direct ou en croisé. L'entrée de ces commutateurs est désignée par  $S_0$  à  $S_{N-1}$ . La figure 2.5 montre un modèle du shuffle-exchange parfait pour n=3 (avec  $N=2^n$ , où n représente le nombre de tours ou de passes). Cette configuration est obtenue de la façon suivante: l'entrée  $E_x$  doit être connectée à l'entrée 2\*x modulo  $(2^n-1)$  du commutateur; c'est à dire l'entrée  $E_x$  est connectée à la sortie S[2\*x modulo  $(2^n-1)$ ]. Une méthode pratique est souvent utilisée pour déterminer l'interconnectabilité du shuffle-exchange parfait (perfect shuffle-exchange), première étape, on numérote la séquence normale selon n (fig. 2.5 (b), ligne 1).

Fig, 2.5 a) Réseau à un seul étage type Shuffle-exchange parfait.

Cette séquence est divisée en deux moitiés égales, après quoi, la première moitié reportée sur la ligne 2, entre chaque numéro, on laisse un espace. La deuxième moitié est reportée sur la ligne 3 et enfin la ligne 4 montre la configuration shuffle exchange parfait en fusionnant la ligne 2 et 3 [HWA 93].

Dans un réseau à un seul étage, les sorties doivent obligatoirement être connectées aux mêmes numéros d'entrée via des mémoires tampons (B<sub>i</sub>). Ceci est dû essentiellement au fait qu'une transmission de donnée à l'entrée du réseau peut ne pas être connectée à la sortie en un seul cycle, c'est à dire en un seul tour. Ces données peuvent recirculer à travers le réseau jusqu'à n tours (un tour dans un réseau à un seul étage est équivalent à un étage dans un

réseau à plusieurs étages). Par exemple, si l'entrée  $E_0$  veut transmettre des données à la sortie  $S_2$  (fig. 2.5.a), deux cycles sont nécessaires: dans le premier cycle, les données sont transmises de l'entrée  $E_0$  à la sortie  $S_1$  en positionnant le commutateur en **croisé**; dans le deuxième cycle, les données passent de l'entrée  $E_1$  vers la sortie  $S_2$  en mettant le commutateur dans la position **directe**. On trouve d'autres types de configuration donnés par Burke [BUR 91].

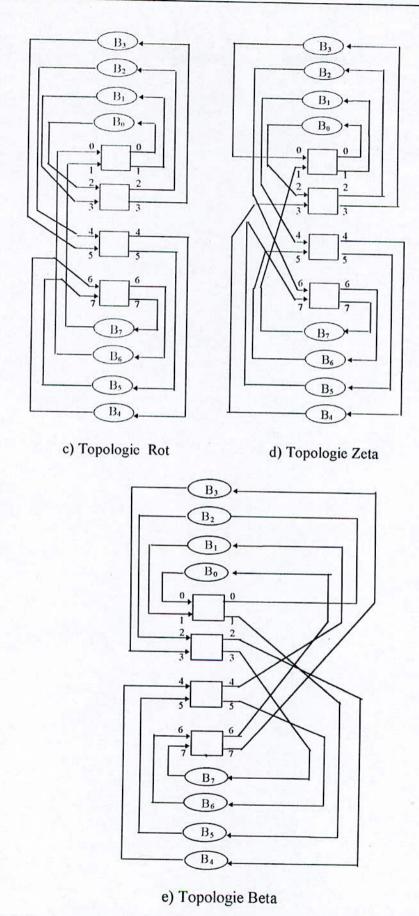

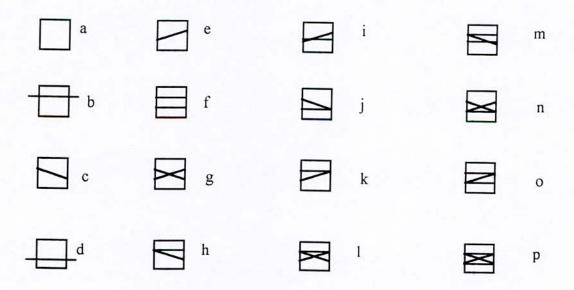

On distingue d'autre types de RIT; on énuméra quelques uns qui sont représentés dans la figure 2.6. Le principe de la structure du réseau reste la même; ce qui change c'est la liaison entre les entrées et les sorties qui définit généralement la topologie du réseau.

La complexité du RIT est de l'ordre de O(N); par contre celui d'un RIP est O(NLog<sub>2</sub>N) [HUA 87] ou N est le nombre d'entrée. On a observé que les RIT ont un chemin (path) moyen plus court. Ce chemin n'est au fait que le nombre de tours utilisé dans le réseau pour établir une connexion entre la source et la destination. Dans un RIP, chaque requête doit faire Log<sub>2</sub>N étages pour atteindre sa destination. Par contre dans un RIT, le nombre maximum de tour pour une quelconque connexion entre entrée et sortie est inférieur où égale à Log<sub>2</sub>N. Ceci est un avantage considérable pour ce type de réseau.

a) Réseau d'interconnexion à un seul étage topologie Shuffle-exchange

b) Topologie Shuffle-exchange modifié

Fig. 2.6 Quelque exemple des réseaux d'interconnexions à un seul étage

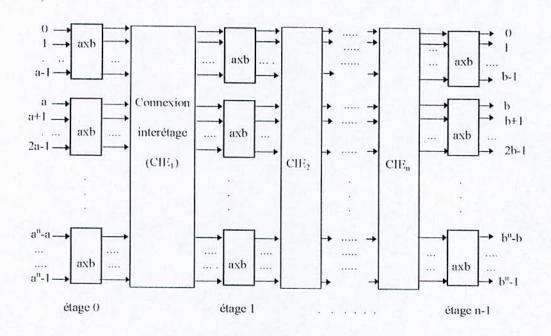

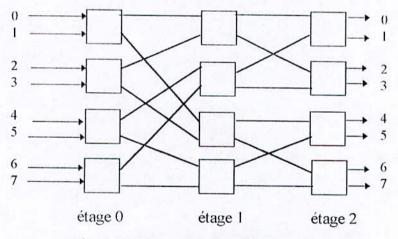

### 2.5 Les réseaux d'interconnexions à plusieurs étages

Les RIP ont été bien définis par J. de Rumeur [RUM 94]; c'est une nouvelle génération de machines qui ont pris de l'essor ces dernières années. Ces réseaux présentent une connexion complète entre l'entrée et la sortie; ils sont facilement extensibles. Un réseau multiétage généralisé est présenté dans la figure 2.7. Un nombre de commutateur axb est utilisé dans chaque étage. Une connexion fixe entre étage adjacent est établie. Cette connexion interétage définit la topologie du réseau. Les commutateurs disposent de commandes qui permettent d'établir la connexion entre la source et la destination désirée.

Fig. 2.7 Structure générale d'un réseau d'interconnexion multiétage avec un module de commutation axb et une connexion interétage CIE<sub>1</sub>, CIE<sub>2</sub>, .... CIE<sub>n</sub>.

Il existe plusieurs types de RIP, ils diffèrent dans le choix du module de commutation et le choix de la connexion interétage (CIE). Le plus simple du module de commutation est le commutateur 2x2, comme le montre la figure 2.5 (a). Nous allons présenter dans ce qui suit les CIEs avec quelques exemples les plus répandues.

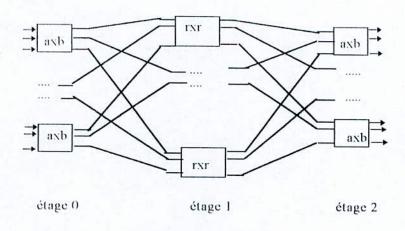

#### 2.5.1 Réseau Clos

Un réseau Clos, de paramètres a, b et r, noté CL(a, b, r) est constitué de trois étages: le premier étage (étage 0) est constitué de r commutateurs identiques, dits (a, b),

chacun reliant a entrées vers **b** sorties (nous avons donc r.a entrées et r.b sorties au premier étage); le deuxième étage (étage 1) comporte b commutateurs (r, r) identiques (nous avons donc ici b.r entrées et autant de sorties); et le troisième étage (étage 2) est le symétrique du premier et consiste en r commutateurs (b, a) identiques. La figure 2.8 illustre ce réseau. Nous allons présenter maintenant quelques exemples de RIP les plus communs et qui sont tous à base de commutateurs (2x2).

Fig. 2.8 Réseau Clos CL(a, b, r)

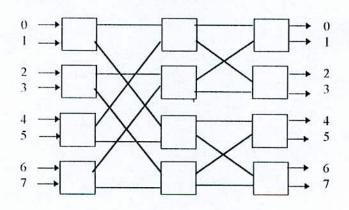

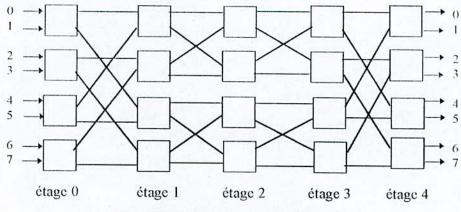

#### 2.5.2 Réseau Butterfly

Le réseau multiétages Butterfly de dimension n est un réseau formé de n+1 étages ayant chacun 2<sup>n</sup> commutateurs (2x2). Il existe donc 2<sup>n+1</sup> liens d'entrées et 2<sup>n+1</sup> liens de sorties. Les étages sont généralement étiquetés par les entrées de 0 à n. La figure 2.9 représente un réseau Butterfly de dimension 2.

Fig. 2. 9 Réseau Butterfly de dimension 2

#### 2.5.3 Réseau Benès

Un réseau Benès de dimension  $\mathbf{n}$ , noté  $B_n$ , est constitué d'un réseau Butterfly de dimension  $\mathbf{n}$ , suivi d'un réseau Butterfly de dimension  $\mathbf{n}$  inversé (c'est à dire obtenu par une opération miroir), de sorte que l'étage  $\mathbf{n}$  du premier soit confondu avec l'étage  $\mathbf{n}$  du second (figure 2.10). Il a donc 2n+1 étages de  $2^n$  commutateurs (2x2) chacun.

Fig. 2.10 Réseau Benès de dimension 2

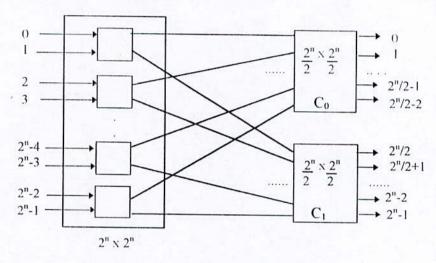

## 2.5.4 Réseau Oméga et Baseline

Le réseau oméga de dimension n est formé de n+1 étages de 2<sup>n</sup> commutateurs (2x2), les sorties de 2<sup>n-1</sup> premiers commutateurs d'un étage quelconque sont reliées aux entrées hautes des commutateurs de l'étage suivant, dans le même ordre. La figure 2.11 représente un réseau oméga de dimension 2.

Fig. 2.11 Réseau oméga de dimension 2

Le réseau oméga est équivalent au réseau butterfly [RUM 94]. Il n'est pas le seul réseau équivalent topologiquement au réseau butterfly; on peut trouver le réseau baseline. Pour

l'équivalence entre réseaux il y a lieu de se repporter à la Thèse de J. M. Fourneau [FOR 85]. Le réseau baseline de dimension n est également formé de n+1 étages de 2<sup>n</sup> commutateurs (2x2). Le premier étage est constitué d'un block de 2<sup>n</sup> x 2<sup>n</sup>, et le deuxième étage est constitué de deux sous-blocks de 2<sup>n-1</sup> x 2<sup>n-1</sup> identifié par C<sub>0</sub> et C<sub>1</sub>. La construction de ce processus peut être récursive jusqu'au dernier block de 2x2. La figure 2.13 montre un réseau baseline de dimension 2.

Fig. 2.12 Construction récursive

Fig. 2.13 Réseau baseline de dimension 2

# 2.6. Comparaison des performances des réseaux d'interconnexions

Par exemple, si on considère le réseau crossbar, on sait qu'il nécessite N<sup>2</sup> boîte de commutation (BC) pour pouvoir établir une connexion entre N-entrées/ N-sorties. Par contre, dans les RIP type baseline par exemple, cela nécessite N/2(Log<sub>2</sub>N) BC[REW 97]. L'avantage majeur du crossbar est la vitesse de connexion. Dans un cycle de temps, une

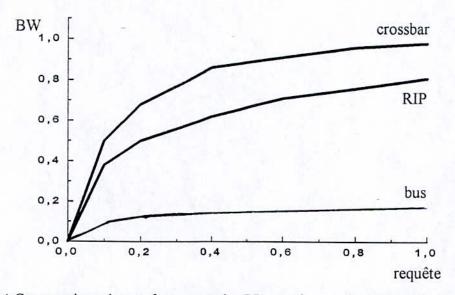

connexion peut s'établir entre le processeur source et la mémoire destination. Par contre les RIP nécessitent Log<sub>2</sub>N cycles pour établir une connexion. La figure 2.14 illustre les performances du réseau crossbar, RIP et la structure classique, liaison par bus. L'axe vertical représente la bande passante (BW) qui est un des paramètres qui permet de mesurer les performances d'un réseau. La BW représente le nombre d'accès de requête que le réseau satisfera par une unité de temps (qu'est le cycle dans notre cas). L'axe horizontal représente le taux d'arrivée des requêtes. La figure 2.14 montre que les performances des RIP sont très proches des performances du réseau crossbar pour une complexité materielle moindre (nombre de boîte de commutation). C'est l'une des raisons fondamentales qui a laissé bon nombre de chercheur de s'intéresser aux RIP.

Fig. 2.14 Comparaison des performances des RI entre le crossbar, RIP et le bus. [Hesham El-Rewini & Ted G. Lewis, 'Distributed and parallel computing', Ed. Manning, 1997, pp. 102].

## Les réseaux de Petri

Depuis longtemps déjà, l'homme a ressenti le besoin de comprendre le fonctionnement du monde qui l'entoure. C'est ainsi que très rapidement, il lui a fallu modéliser les phénomènes physiques afin d'en isoler les principaux ressorts. La modélisation lui a permis d'analyser des rapports de cause à effet, d'établir des lois de comportement aboutissant à une prédiction possible de ces phénomènes. Cependant, un dilemme subsiste entre l'élaboration d'un modèle trop simpliste autorisant une analyse facile de son comportement, mais un peu éloigné du comportement réel du système, et un modèle qui est très proche du système réel, mais dont l'étude est trop complexe, voire impossible.

C'est dans cet esprit que Carl Adam Petri a défini dans les années 60, un modèle consacré à l'étude des systèmes à événements discrets: les réseaux de Petri (RdP) [PET 62]. Ce modèle, initialement utilisé pour décrire le fonctionnement de systèmes informatiques, possède des propriétés structurelles que l'on peut facilement mettre en évidence et qui sont immédiatement transportables sur le système réel [BRA 83], [FLO 91], [MUR 89].

Très rapidement ce modèle a été doté d'extensions et a vu son domaine d'application s'étendre. En particulier, l'évaluation des performances des systèmes de production fait aujourd'hui largement appel aux RdP. Ces dernières années ont vu se réaliser des applications dans le domaine de l'informatique; c'est dans ce cadre que le présent travail a été effectué.

#### 3.1 Introduction

Les réseaux de Petri sont des outils de modélisation des activités asynchrones ou synchrones, concurrentes et parallèles.

Les avantages principaux des RdP sont les suivants:

- (i) ils autorisent une représentation graphique relativement proche des systèmes réels

- (ii) leur dynamique s'exprime sous forme d'équations d'état simples.

- (iii) certains types de RdP possèdent des propriétés fortes (conservation de marquages, temps de séjour, ...) qui sont des propriétés interprétables en termes de blocage d'informations dans les réseaux de communications informatiques.

De plus, les moyens dont on dispose pour l'étude des systèmes discrets sont très peu

nombreux et sont parfois soumis à des hypothèses fortes (c'est le cas des files d'attente, par exemple) [FLO 90].

Dans cette partie, nous donnerons les définitions et propriétés de bases des réseaux de Petri en insistant plus particulièrement sur les réseaux de Petri stochastiques (RdPS) qui sont une extension des RdP. C'est avec les RdPS que nous avons étudié l'évaluation d'architecture des systèmes parallèles. Nous présenterons par la suite les motivations du choix de cet outil mathématique.

# 3.2 Réseaux de Petri : Définitions et Propriétés

#### 3.2.1 Définitions de Base

Un réseau de Petri est un graphe biparti constitué de places, de transitions (correspondant aux sommets du graphe) et d'arcs qui relient les transitions aux places et les places aux transitions. Il est représenté par un quadruple [P, T, I, O] ou:

- P désigne l'ensemble (fini) de places  $P = \{P_1, P_2, \dots P_n\}$

- T est l'ensemble (fini) de transitions  $T = \{T_1, T_2, \dots, T_m\}$

- I est une application de P x T → IN (ensemble des entiers naturels) correspondant aux arcs directs des places vers les transitions.

I(p, t) > 0 signifie qu'il existe un arc orienté de p vers t et I(p, t) est la valuation de cet arc.

I(p, t) = 0 indique l'absence d'arc orienté reliant la place p à la transition t.

O est une application de Tx P → IN correspondant aux arcs directs reliant les transitions aux places.

O(t, p) > 0 signifie qu'il existe un arc orienté de t vers p et O(t, p) est la valuation de cet arc.

O(t, p) = 0 indique l'absence d'arc orienté reliant la transition t à la place p.

On notera t° (resp. °t) l'ensemble des places de sorties (resp. d'entrée) de la transition t.

$$t^{\circ} = \{ p \in P; I(p, t > 0) \}$$

$t^{\circ} = \{ p \in P; O(t, p > 0) \}$

De même p° (resp. °p) désignera l'ensemble de transitions de sortie (resp. d'entrée) de la place p.

$$^{\circ}p = \{ t \in T; O(t, p > 0) \}$$

$$p^{\circ} = \{ t \in T; I(p, t > 0) \}$$

#### 3.2.1.1 Marquage

Les places peuvent contenir zéro ou plusieurs marques (ou jetons). Le marquage d'un RdP est une application M de P dans IN (ensemble des entiers naturels).

$$M: P \rightarrow IN$$

M(p) désigne le nombre de marques (jetons) contenues dans la place p.

M peut être représenté par un vecteur colonne indicé par les numéros des places.

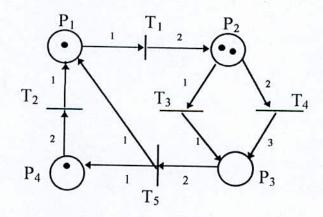

Un réseau de Petri marqué est un RdP noté R muni d'un marquage initial M<sub>0</sub>; la figure 3.1 est un exemple de réseau de Petri marqué.

Nous avons pour l'exemple de la figure 3.1:

- n = 4 (nombre de places) m = 5 (nombre de transitions)

- O  $(t_1, p_2) = 2$  O  $(t_4, p_3) = 3$  O  $(t_2, p_1) = O(t_3, p_3) = O(t_5, p_1) = O(t_5, p_4) = 1$

- $I(p_1, t_1) = I(p_2, t_3) = 1$   $I(p_2, t_4) = I(p_3, t_5) = I(p_4, t_2) = 2$

- et I(p, t) = O(t, p) = 0 pour tout autre  $p \in P$  et  $t \in T$

- $p_2^{\circ} = \{t_3, t_4\}$   ${}^{\circ}p_2 = \{t_1\}$   $t_5^{\circ} = \{p_1, p_4\}$   ${}^{\circ}t_5 = \{p_3\}$

- ${}^{t}M_{0} = (1, 2, 0, 1)$

Fig. 3.1 Un exemple de RdP marqué

# 3.2.1.2 Règles de fonctionnement

Le passage d'un marquage à un autre s'effectue de façon instantanée par franchissement d'une ou plusieurs transitions. Une transition est dite tirable (ou franchissable) si chacune de ses places d'entrée contient un nombre de jetons au moins égal à la valuation de l'arc joignant cette place à la transition.

La transition t est franchissable si :

$$\forall p \in {}^{\circ}t \qquad M(p) \geq I(p, t)$$

Revenons encore à la figure 3.1. La transition  $T_1$  est franchissable car sa place d'entrée  $P_1$  contient un nombre de jetons égal à la valuation de l'arc  $(p_1, t_1)$  (  $I(p_1, t_1) = 1$ ).

Par contre, la transition  $t_2$  n'est pas tirable puisque I  $(p_4, t_2) = 2 > M$   $(p_4) = 1$ Le tirage d'une transition t a pour conséquence:

- (i) de retirer I (p, t) jetons de chaque place d'entrée p de la transition t.

- (ii) d'ajouter O (t, p) jetons dans chaque place de sortie p de la transition t. " Le franchissement d'une transition t provoque alors le passage à un marquage M' tel que:

$$\forall p \in P$$

M'  $(p) = M(p) + O(t, p) - I(t, p)$

Le marquage M' du RdP de la figure 3.1, obtenu après franchissement de la transition t<sub>1</sub> est:

$$^{t}M' = (0, 4, 0, 1)$$

Une séquence de transitions  $\sigma = (t_{i1}, t_{i2}, .... t_{is})$  est franchissable pour le marquage  $M_0$  si  $t_{ik}(k=1, 2, ...., s)$  est franchissable par le marquage  $M^{(k-1)}$  obtenu par le franchissement de  $\sigma_{k-1} = (t_{i1}, t_{i2}, .... t_{i(k-1)})$ . L'ensemble des marquages qu'il est possible d'atteindre partant du marquage  $M_0$  en franchissant une séquence de transitions, sera noté  $\mathcal{M}(R, M_0)$ . Bien entendu, si  $M \in \mathcal{M}(R, M_0)$ , il existe au moins une séquence  $\sigma = (t_{i1}, t_{i2}, .... t_{is})$  franchissable qui permet de passer du marquage  $M_0$  au marquage M.

#### 3.2.2 Analyse des RdP

#### 3.2.2.1 Matrice d'incidence

La structure d'un RdP peut être définie par une matrice à éléments entiers, appelée matrice d'incidence. Pour un RdP avec n places et m transitions, la matrice d'incidence  $W = (c_{ij})$  est une matrice de (nxm), définie par:

$$W(i, j) = w_{ij} = O(t_j, p_i) - I(p_i, t_j)$$

La matrice d'incidence du RdP de la figure 3.1 est donnée par:

$$W = \begin{bmatrix} -1 & 1 & 0 & 0 & 1 \\ 2 & 0 & -1 & -2 & 0 \\ 0 & 0 & 1 & 3 & -2 \\ 0 & -2 & 0 & 0 & 1 \end{bmatrix}$$

Nous définirons de même la matrice d'incidence avant W<sup>+</sup> (resp. arrière W<sup>-</sup>) par:

$$W^{+}(i, j) = O(t_j, p_i)$$

$W^{-}(i, j) = I(p_i, t_j)$

D'où l'égalité matricielle suivante  $W(i, j) = W^{+}(i, j) - W^{-}(i, j)$ pour l'exemple de la figure 3.1 nous avons:

$$W^{+} = \begin{bmatrix} 0 & 1 & 0 & 0 & 1 \\ 2 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 3 & 0 \\ 0 & 0 & 0 & 0 & 1 \end{bmatrix} \qquad W^{-} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 2 & 0 \\ 0 & 0 & 0 & 0 & 2 \\ 0 & 2 & 0 & 0 & 0 \end{bmatrix}$$

Soit une séquence de transitions franchissables à partir d'un marquage initial  $M_0$ . Le vecteur caractéristique de la séquence  $\sigma$ , noté  $\underline{\sigma}$  est le vecteur colonne à coefficients entiers de dimension m, où  $\underline{\sigma}_{\underline{i}}$  (i=1, 2, ....m) est le nombre de fois que la transition  $t_i$  apparaît dans  $\sigma$ . Alors nous avons l'équation fondamentale suivante :

$$M_f = M_{0} + W_{.\underline{\sigma}}$$

(3.1)

où  $M_0$  est le marquage initial.  $M_f$  est le marquage obtenu à partir de  $M_0$  après que la séquence  $\sigma$  ait été franchie, W étant la matrice d'incidence du RdP.

Considérons le RdP de la figure 3.1 avec le marquage initial  $M_0 = (1, 2, 0.1)$ . La séquence  $\sigma = (t_1, t_4, t_5, t_2, t_1, t_3)$  est une séquence franchissable à partir de  $M_0$  et son vecteur caractéristique est donnée par  $\underline{\sigma} = (2, 1, 1, 1, 1)$ .

Appliquons l'équation fondamentale Eq.3.1 . Il vient:

$$M_{f} = M_{0} + W_{0} = \begin{bmatrix} 1 \\ 2 \\ 0 \\ 1 \end{bmatrix} + \begin{bmatrix} -1 & 1 & 0 & 0 & 1 \\ 2 & 0 & -1 & -2 & 0 \\ 0 & 0 & 1 & 3 & -2 \\ 0 & -2 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} 2 \\ 1 \\ 1 \\ 1 \end{bmatrix} = \begin{bmatrix} 1 \\ 3 \\ 2 \\ 0 \end{bmatrix}$$

## Remarque:

L'équation fondamentale Eq.3.1 donne le marquage final connaissant le marquage initial et la séquence des transitions franchies. Mais elle ne permet pas de vérifier si le franchissement d'une séquence donnée est possible.

#### 3.2.2.2 Temporisation

Aucune durée n'est liée au franchissement des transitions ni au séjour dans les places pour ce qui concerne les RdP que nous avons présentés précédemment. Il existe plusieurs extensions possibles des RdP. Parmi ces extensions nous pouvons citer les RdP temporisés et les RdP stochastiques. Cette classe appartient à la classe des RdP non autonomes (la classe des RdP permettant de lier l'évolution d'un réseau à celui d'un environnement).

Dans les RdP temporisés et les RdP stochastiques, on associe aux places ou aux transitions des durées de séjour ou de franchissement: déterministes dans le premier cas, aléatoires dans le second.

Dans notre approche, nous avons utilisé les RdP stochastiques comme outil mathématique. Nous allons, tout d'abord, préciser les motivations qui nous ont amené à retenir cet outil comme moyen d'évaluation des performances dans les systèmes (performances fonctionnelles et/ou de sûreté de fonctionnement). Nous rappellerons ensuite quelques définitions et propriétés relatives à une classe particulière de processus stochastiques à savoir les chaînes de Markov, qui sont le substrat fondamental des analyses faites avec les RdPS.

# 3.3 Les Réseaux de Petri Stochastiques

#### 3.3.1 Pourquoi les RdPS?

Les premières études d'évaluation de performances de systèmes informatiques ont été essentiellement basées sur des techniques qui font appel à des méthodes de simulation ou à des méthodes d'analyse basée sur la théorie des files d'attente.

Les méthodes de simulation permettent de présenter des systèmes à configurations réalistes. Cependant, d'une part, la convergence de ce type de méthodes est souvent assez coûteuse et assez aléatoire, et d'autre part, la validation du modèle est assez difficile.

Les réseaux de files d'attente permettent de modéliser uniquement des comportements de pur parallélisme. Un client arrive dans la queue, attend un service, reçoit le service et entre dans une autre queue ou quitte le réseau de files d'attente. Donc à un moment donné, plusieurs clients sont servis en parallèle dans plusieurs queues. Ce modèle est très bien adapté pour la modélisation du comportement asynchrone des clients; cependant le seul type d'interaction pouvant être décrit entre ces comportements

correspond au contentieux à l'accès au service [FLO 91].

Dans le domaine de la sûreté de fonctionnement, les processus stochastiques et particulièrement les chaînes de Markov sont les principaux outils de modélisation. Et comme tout graphe d'états peut être utilisé pour représenter le comportement du modèle, les chaînes de Markov permettent en théorie de décrire de très nombreuses architectures de systèmes, ceci étant dû à l'absence de restrictions sur les schémas de synchronisation mis en oeuvre. Malheureusement, le processus de modélisation implique l'énumération de tous les états possibles et de toutes les possibilités de transitions entre états; ceci est d'autant plus pénalisant, que même si cette fastidieuse étape combinatoire est rendue possible, il est très difficile d'éviter, en particulier les erreurs d'omission.

Il apparaît donc, qu'un outil d'un niveau d'abstraction acceptable est nécessaire. Un tel outil doit combiner, d'une part, un niveau d'expression qualitatif assez élevé du parallélisme, de la compétition et de la synchronisation et, d'autre part, doit être capable de représenter fidèlement le processus stochastique. Ces deux aspects permettent à la fois de faire une validation qualitative du modèle et une évaluation quantitative des performances et des critères de sûreté de fonctionnement (fiabilité, sécurité, disponibilité, ...).

#### 3.3.2 Comment définir les réseaux de Petri stochastiques

Une synthèse de la définition idéale des RdPS a été présentée par Florin [FLO 90]. Celle-ci doit tenir compte des principes suivants:

- Le point essentiel concerne la capacité du modèle à représenter n'importe quel ensemble d'activités parallèles à ressource partagées et, plus généralement, soumises à tout schéma de synchronisation possible.

- La durée d'une opération étant une variable aléatoire, sa distribution ne doit pas être restreinte à un type particulier, et doit pouvoir dépendre du contexte courant d'exécution.

Dans notre approche, nous avons choisi que la variable aléatoire suive une loi de distribution exponentielle. Ce choix s'explique par le fait de travailler dans l'intervalle de temps ou l'état 'future' dépend de l'état 'présent' du système (i.e. un système sans mémoire). L'analyse de ce type de modèle passe par l'étude d'une chaîne de Markov continue. En effet, il a été montré que le processus stochastique sous-jacent au RdPS est une chaîne de Markov continue [FLO 91].

# Chaîne de Markov [FLO 91]

Un processus de Markov est un processus stochastique X(t) tel que, étant donné trois instants t, u, s, où t > u > s, la valeur de X(t) lorsque X(u) est connue ne dépend que de X(u) et pas de X(s). Autrement dit, les états futurs d'un processus de Markov ne dépendent que de l'état présent et non de la trajectoire ayant permis d'atteindre cet état:

$$P[X(t) = E_i / X(u), X(s)] = P[X(t) = E_i / X(u)]$$

Nous reviendrons avec plus de détail sur l'ensemble des probabilités du processus stochastique quand nous développerons les modèles dans le chapitre suivant, particulièrement lorsque nous poserons les hypothèses qui seront évidemment fortes pour pouvoir appliquer le processus de Markov.

# Modélisation des réseaux d'interconnexions à plusieurs étages

#### 4.1 Introduction

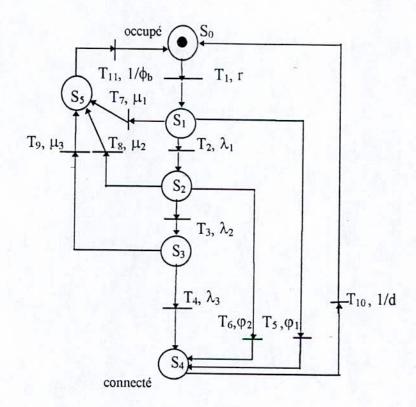

Dans le cadre des travaux de cette thèse, nous avons développé deux modèles de réseaux d'interconnexions dynamiques [BEN 94], [BEN 96]. Généralement dans les réseaux d'interconnexions dynamiques, on utilise des commutateurs ou boîte de commutation (BC) qui sont l'élément de base. Il existe plusieurs types de BC. Dans notre approche nous avons considéré la BC de 2x2, c'est à dire 2 entrées / 2 sorties, tel que le montre la figure 4.1. Ce type de BC est utilisé aussi bien dans les RIP que dans celui des RIT. Nous commencerons d'abord par donner un ensemble de définitions standard qui régissent les deux types de RI, ainsi que quelques hypothèses considérées dans notre approche. Ces hypothèses sont utilisées par la majeure partie des chercheurs; nous présenterons également la généralisation des modèles des RI dynamiques. Enfin, dans le chapitre V, nous exposerons l'application pour un réseau à 3 étages [BEN 95].

# 4.2 Modélisation d'un réseau d'interconnexions à plusieurs étages

Dans un RIP, on utilise des boîtes de commutation de 2x2 pour lier les entrées aux sorties. Nous supposons que les entrées sont des processeurs et que les sorties sont des mémoires. Un RI est un réseau capable de connecter n'importe quelle entrée à n'importe quelle sortie.

Un RIP est un réseau qui possède un chemin unique entre l'entrée et la sortie. Ceci nous amène à dire que le chemin entre les BC du réseau forme un arbre de lien. Un RI à nétages est un réseau dont les BC peuvent être arrangé en étage. Les processeurs sont liés à l'entrée de l'étage 1 du réseau, toutes les sorties de l'étage i sont connectées à l'entrée de l'étage i+1, et toutes les mémoires sont connectées à la sortie de l'étage n. Nous pouvons étendre cette définition, et dire que les processeurs sont à l'étage 0 et les mémoires sont à l'étage n+1. Un réseau uniforme est un réseau ou les BC du même étage ont le même nombre de liens d'entrée et le même nombre de liens de sortie. Un réseau carré de degré m est un réseau avec mxm BC. L'interconnectibilité entre étage détermine la topologie du réseau. Chaque étage est connecté à l'étage suivant par au moins N chemins avec ( N = m<sup>n</sup>).

Une classe de RI [Wu 92] est conçue pour connecter N=m<sup>n</sup> entrées à N sorties. Ce réseau contient n étages de N/m BC de dimension mxm. Les BC des étages adjacents sont connectées de façon à pouvoir lier les entrées et sorties du réseau. La figure 2.13 montre un RIP avec N=2<sup>3</sup>=8 entrées (m=2 et n=3), N=8 sorties, et trois étages de 8/2=4 BC de 2x2 chacun. Ce réseau est appelé réseau baseline de 8x8.

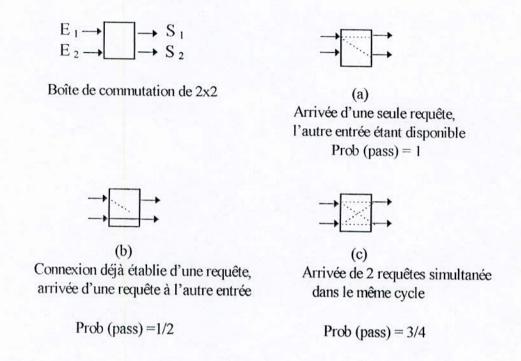

Dans le cas où nous considérons une BC de 2x2, une requête peut être connectée de trois manières différentes telles que le montre la figure 4.1.

Dans l'état de la figure 4.1 (a), l'entrée basse de la BC est disponible c'est-à-dire qu'il n'y a aucune requête qui occupe cette entrée. Pendant cette phase, s'il y a une arrivée de requête dans l'autre entrée, cette requête aura une probabilité de passage égale à 1.

Dans l'état de la figure 4.1 (b), nous supposons l'entrée basse de la BC occupée par une commutation, c'est-à-dire qu'il existe une connexion entre l'entrée et la sortie de la BC; pendant cette phase, s'il y a une arrivée d'une requête à l'autre entrée, elle aura une probabilité de passage égale à 1/2.

Dans l'état de la figure 4.1 (c), nous supposons que les deux entrées de la BC sont disponibles. Nous considérons l'arrivée de deux requêtes dans le même cycle aux deux entrées. Si les deux requêtes demandent la même sortie de la BC, alors une seule requête va accéder à cette sortie, l'autre sera bloquée. Le choix entre les deux requêtes en conflit sera aléatoire et dépendra de la priorité de passage donnée par la BC. La probabilité de passage d'une requête dans l'état (c) sera égale à 3/4. Dans la modélisation des RIP, nous avons déjà considéré cette forme d'hypothèse qui gère la BC de 2x2. Nous pouvons avoir d'autres formes d'hypothèses concernant la gestion de la BC. Une autre forme d'hypothèse est présentée et appliquée dans la modélisation des RIT dans le chapitre VI.

Grâce à cette première forme d'hypothèse qui gère la BC, nous pouvons dire quand un processeur à l'entrée du réseau génère une requête; cette requête établira un lien entre le processeur demandeur et l'entrée de la BC du premier étage. Cette requête se connectera à l'étage 1 du réseau avec une probabilité de passage égale à 1, 0.5 où 0.75; cela dépendra de l'état de la BC.

Les requêtes qui passeront l'étage 1, vont progresser vers l'étage 2 du réseau de la même manière et ainsi de suite. Quand une requête passera l'étage n (=Log<sub>2</sub> N; où N est le nombre d'entrées ou de sorties du réseau) nous dirons qu'un chemin est établi entre le processeur

(entrée du réseau) et la mémoire (sortie du réseau). Une requête peut passer un étage dans 1 cycle de temps, donc une connexion d'une requête au sein du réseau nécessite au moins n cycles (n étant le nombre d'étages du réseau).

Fig. 4.1 Boîte de commutation de 2x2 et les probabilités d'établir une connexion

Avant de présenter le modèle, nous donnerons les hypothèses considérées, qui sont généralement prisent par l'ensemble des chercheurs [DIN 91], [WU 92], [YOO 90]:

#### · Hypothèses du modèle

- a Le franchissement d'une transition suit une loi de distribution exponentielle.

- b L'état d'une transition prend un cycle de temps.

- c Quand un chemin est établi entre l'entrée et la sortie du réseau, ce chemin est maintenu pour transférer les données pendant un nombre de cycles fixe. Le temps de transfert de données est noté 'd'. Les requêtes arrivent au réseau avec une probabilité 'r'. Du moment qu'on utilise le cycle comme unité de temps, donc le taux et la probabilité d'arrivée de requête sont identiques.

- d Le nombre maximum d'étages dans le cas de RIP (ou tour dans le cas de RIT) dans le réseau est n.

- e Si deux requêtes arrivent simultanément aux entrées d'une même BC et demandent l'accès à une même sortie, la commutation se fera pour une requête, l'autre requête régénérera

une nouvelle demande d'accès au prochain cycle. Le choix de passage de la requête dépendra de la priorité donnée par la BC.

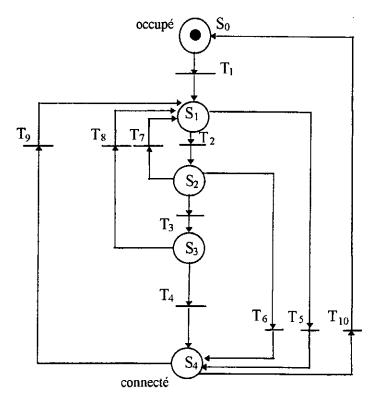

f - La probabilité de destination des requêtes est identique à travers les N sorties du réseau.