#### REPUPLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

## **ECOLE NATIONALE POLYTECHNIQUE Département d'Électronique**

# Projet de fin d'études en vue de l'obtention du Diplôme d'Ingénieur d'État en Électronique

#### Thème

# Évaluation de Mémoires Flash Haute Densité à Haute Température

Proposé et dirigé par :

Réalisé par

Pr. L.HAMAMI (ENP)

**BOUDOUR Sarah**

V.SHITIKOV (SRPC)

## **DEDICACES**

A ma très chère mère, qui m'a beaucoup soutenue et encouragée tout au long de mon parcours, pour ses sacrifices et son amour Que dieu me la garde

> A mon défunt père A mes deux frères : Amir et Samir

> A ma promotrice: Pr.L.HAMAMI

A tous ceux qui ont su croire en moi A tous ceux qui me sont chers

Je dédie ce modeste travail.

## Remerciements

Je tiens à exprimer ma gratitude aux deux responsables M.L.Garando et M.S.Baraket pour m'avoir accueilli au sein du Groupe TECHNO de RSPC et pour m'avoir permis d'intégrer une équipe aussi sympathique et pédagogue.

Je remercie également M.V.Shitikov pour m'avoir encadré lors de ce projet. Ses conseils avisés, pendant tout mon stage tant dans la partie pratique que théorique; ainsi que dans la vie en général m'ont été très précieux.

Je remercie le Professeur HAMAMI Latifa promotrice de ce projet, pour m'avoir permis d'effectuer ce stage, pour m'avoir encadrée et prodiguer ses précieux conseils tout au long de l'année. J'admire beaucoup sa passion pour son travail et l'attention qu'elle porte à ses étudiants.

Je tiens à remercier le Docteur Hicham Bousbia-Salah, Maitre de Conférences à l'École Nationale Polytechnique d'Alger, d'avoir accepté d'être le président du jury de mon projet de fin d'études. Je le remercie également de s'être si bien occupé des « électroniciens » tout au long de mes trois années.

Je remercie également le Docteur Ait\_cheikh Salah, Maître de Conférences à l'École Nationale Polytechnique d'Alger, d'avoir accepté d'être membre du jury de mon projet de fin d'études. Je le remercie aussi pour ce qu'il m'a apporté en tant qu'enseignant.

Je remercie l'ensemble de mes enseignants de l'École Nationale Polytechnique d'Alger, qui m'ont permis d'acquérir assez de connaissances pour en être là aujourd'hui.

Je tiens aussi à exprimer toute ma reconnaissance et mes sincère remerciements à tout ceux qui ont contribué de prés ou de loin à la réalisation de ce mémoire, et tout particulièrement : M.S.Chaumeny, M.A.Masyukov et M.D.Brakat.

Enfin, j'aimerais adresser mes plus fervents remerciements aux membres de ma famille, qui m'ont inculqué le goût du savoir et la valeur du travail bien fait.

## Table des matières

| Liste des Figures                                                              | x   |

|--------------------------------------------------------------------------------|-----|

| Liste des Tableaux                                                             | xii |

| Introduction Générale                                                          | xiv |

| Chapitre I : Présentation de l'Entreprise                                      |     |

| I.1.Introduction                                                               | 17  |

| I.2.Organisation et Segments                                                   | 2   |

| I.3.Recherche et Développement                                                 | 4   |

| I.4.Schlumberger Riboud Product Center (SRPC)                                  | 5   |

| I.4.1.L'organisation du centre technologique SRPC                              |     |

| I.4.2.La mission du centre                                                     | 6   |

| I.4.3.Le Groupe Technologie électrique                                         | 7   |

| Chapitre II :L'Électronique Haute-Température et les Mécanisme<br>Défaillances |     |

| II.1.Effets de la température sur les composants électroniques                 |     |

| II.2.Les effets à court terme (La performance):                                |     |

| II.2.1.La tension de seuil                                                     |     |

| II.2.2.La mobilité des porteurs de charge                                      |     |

| II.2.3.Le courant de fuite                                                     |     |

| II.2.4.Temps de retard                                                         | 11  |

| II.2.5.Le latch-up                                                             | 12  |

| II.3.Les effets à long terme (Loi d'Arrhenius)                                 | 13  |

| Chapitre III :Les Mémoires                                                     | 16  |

| III.1.Les spécifications du projet                                             | 16  |

| III.2.Introduction                                                             | 16  |

| III.3.Classement des mémoires                                                  | 17  |

| III.4.Différents types de mémoires non volatiles                               | 22  |

| III.4.1.Les PROM                                                               |     |

| III.4.2.Les EPROM                                                              |     |

| III.4.3.Les EEPROM                                                             | 23  |

| III.4.4.Les Flash EEPROM                                                       | 23  |

| III.5.Principes de mémorisation utilisés                                       | 24  |

| III.5.1.Mémoire EPROM                                                 | 24 |

|-----------------------------------------------------------------------|----|

| III.5.2.Mémoire EEPROM                                                | 26 |

| III.5.3.Mémoire FEEPROM (Flash EEPROM)                                | 26 |

| III.5.3.1.Familles de mémoires Flash                                  |    |

| III.5.3.1.1.La Flash NOR                                              |    |

| III.5.3.1.2.La Flash NAND                                             |    |

| III.5.3.2.SLC et MLC Flash                                            |    |

| III.5.3.2.2.Multi-Level Cell (MLC) Flash                              |    |

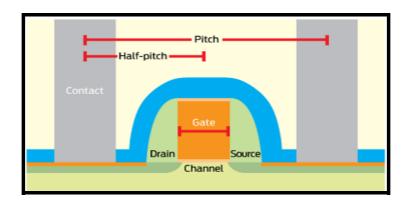

| III.6.Technologie et Finesse de gravure                               |    |

| III.7.Conclusion.                                                     |    |

| Chapitre IV :Plan de Travail et Choix des Composants                  | 34 |

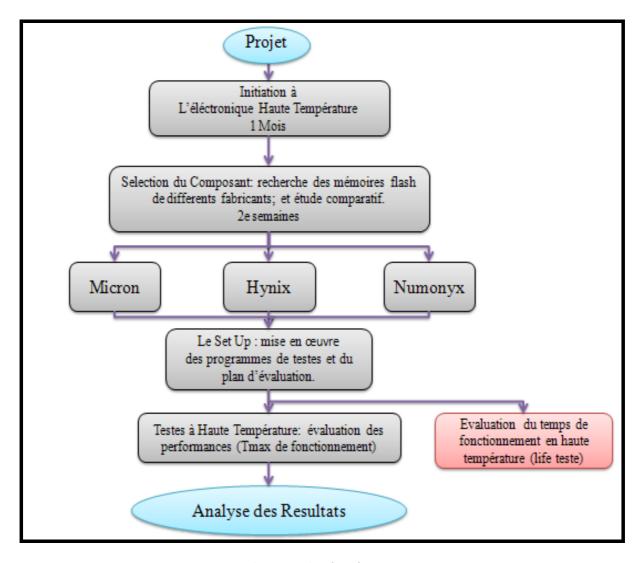

| IV.1.Plan de travail                                                  |    |

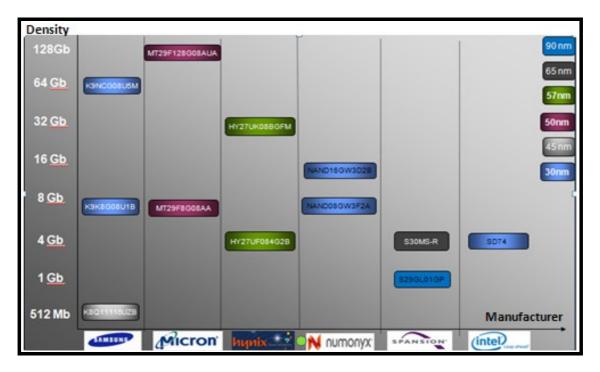

| IV.2.Sélection des mémoires flash                                     |    |

|                                                                       | 50 |

| Chapitre V :Étude de la Mémoire NAND FLASH HY27UF084G2B               |    |

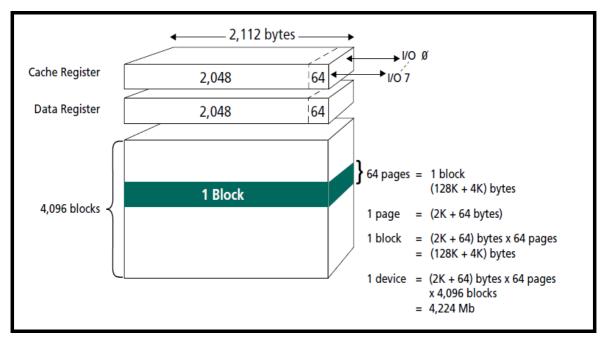

| V.1.Description Sommaire de la Mémoire                                | 41 |

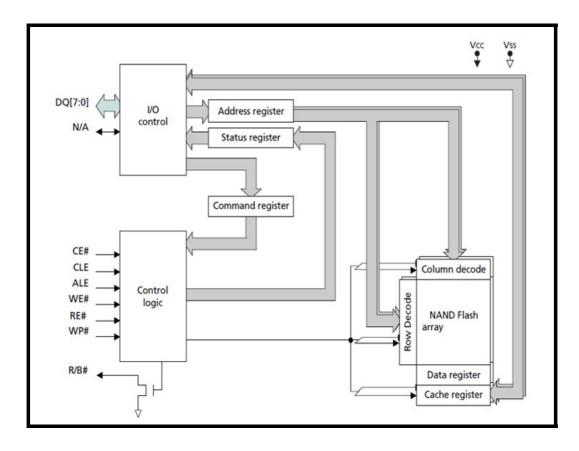

| V.2.Architecture                                                      | 43 |

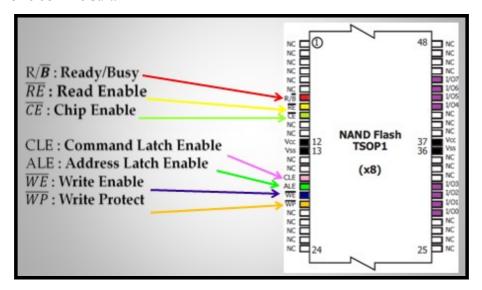

| V.3.Configuration                                                     | 44 |

| V.4.Le fonctionnement                                                 | 46 |

| V.4.1.L'adressage                                                     | 46 |

| V.4.2.Les Opérations du Bus                                           |    |

| V.4.2.1.Entrée de commande(command input)                             | 47 |

| V.4.2.2.Entrée d'adresses.(adresse input)                             |    |

| V.4.2.3.Entrée des données.(data input)                               |    |

| V.4.2.4.Sortie des données.(data output)                              |    |

| V.4.2.6.Le mode en veille (standby)                                   |    |

| V.4.3.Les Opérations Mémoire                                          |    |

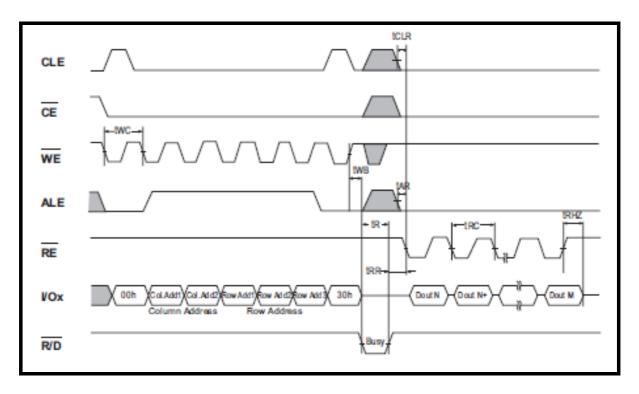

| V.4.3.1.Lecture d'une page                                            |    |

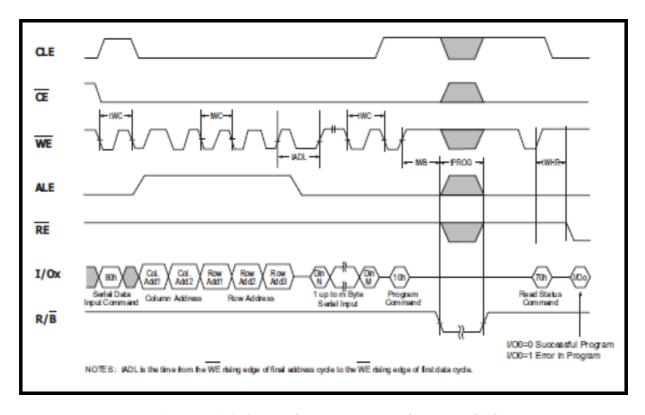

| V.4.3.2.L'écriture d'une page                                         |    |

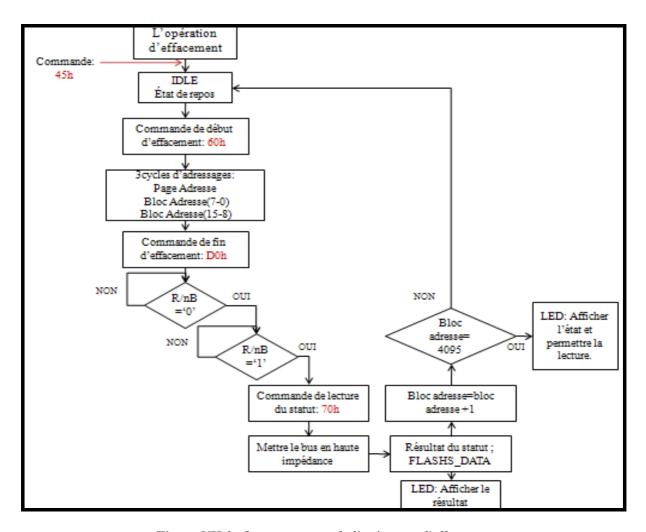

| V.4.3.3.L'effacement d'un bloc                                        |    |

| V.5.Conditions maximales tolérées                                     | 54 |

| V.6.Gestion des Bad blocs                                             | 54 |

| V.7.Résumé des caractéristiques                                       | 55 |

| Chapitre VI :Carte de Développement et Environnement de Programmation | 57 |

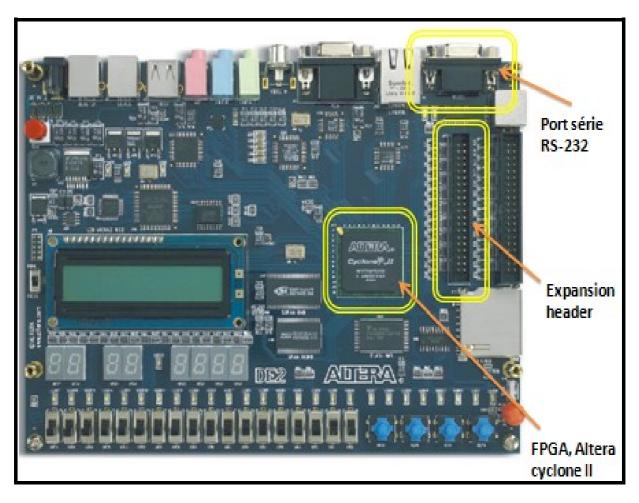

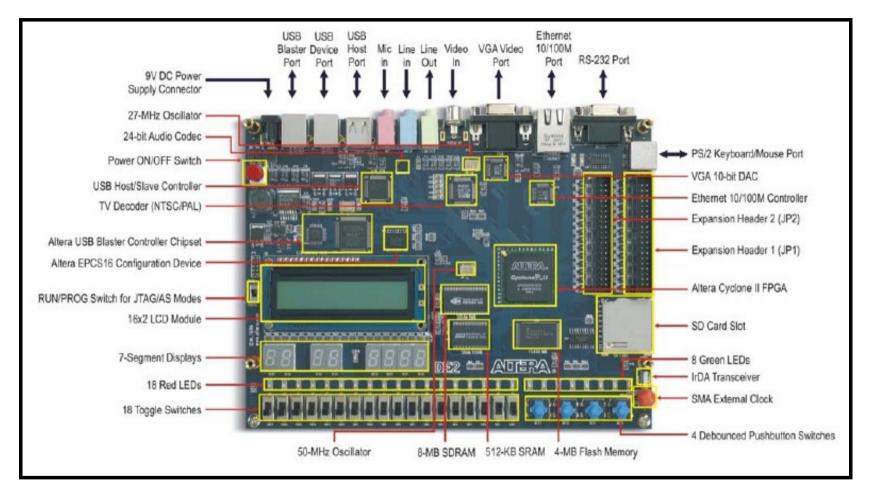

| VI.1.Présentation de l a carte de développement « Altera DE2 Board »  |    |

| VI.1.1.Description                                                    |    |

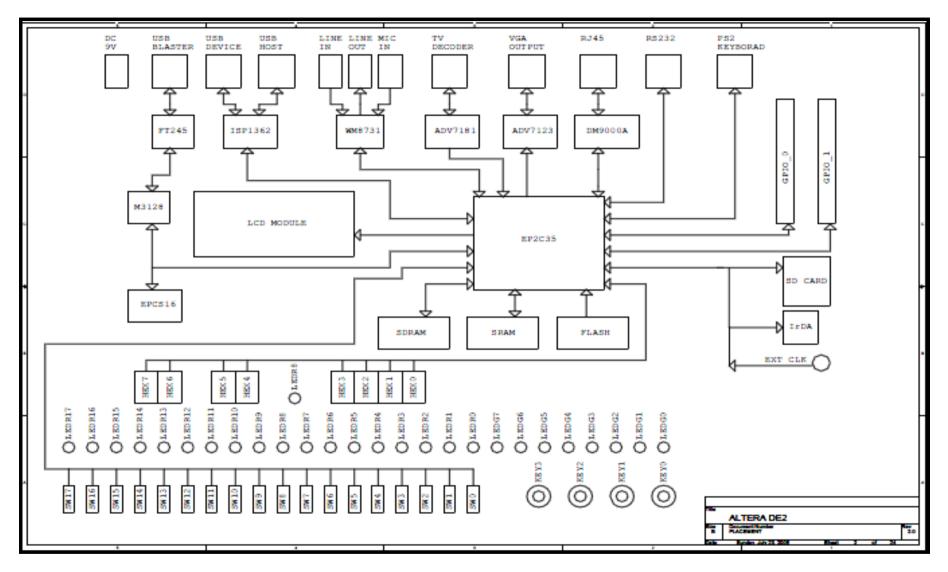

| VI.1.2 Schéma et principaux éléments de la carte                      |    |

| VI.1.2.1.Cœur                                                   |        |

|-----------------------------------------------------------------|--------|

| VI.1.2.2.Mémoires                                               |        |

| VI.1.2.3.Périphériques                                          |        |

| VI.1.2.5.Interfaces                                             |        |

| VI.1.2.6.Modules                                                |        |

| VI.2.Le logiciel « Quartus II »                                 |        |

| VI.2.1.Description                                              | 62     |

| VI.2.2.La programmation JTAG                                    |        |

| VI.3.Le protocole de communication entre l'ordinateur et l'FPGA | 65     |

| VI.4.Le dispositif du test                                      | 67     |

| Chapitre VII :La Programmation                                  | 72     |

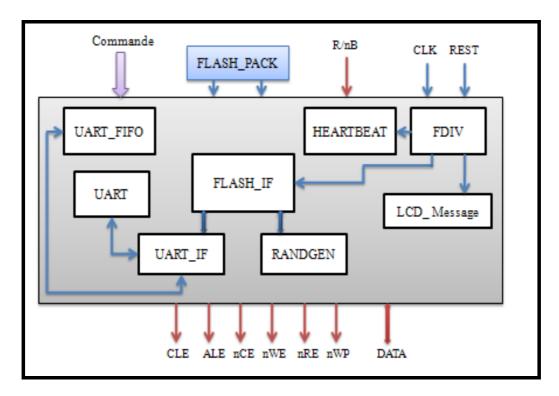

| VII.1.Introduction                                              |        |

| VII.2.Programmation des différentes entités                     |        |

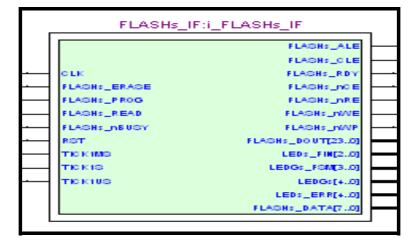

| VII.2.1 l'interface de la mémoire(FLASH_IF)                     |        |

| VII.2.1.L interface de la memorie (PLASII_II')                  |        |

| VII.2.3.Unité de transmission/réception série asynchrone        |        |

| VII.2.3.1.Interface                                             |        |

| VII.2.3.2.L'uart                                                |        |

| VII.3.Conclusion                                                | 79     |

|                                                                 |        |

| Chapitre VIII :Évaluation de la Mémoire à Haute Température     | 81     |

| VIII.1.Méthode d'évaluation                                     | 81     |

| VIII.1.1.Test de l'opération de lecture                         |        |

| VIII.1.2.Test de l'opération d'écriture                         |        |

| VIII.2.La procedure des tests                                   |        |

| VIII.3.Les tests                                                |        |

| VIII.3.1.Tests de fréquence                                     |        |

| VIII.3.2.Tests en température                                   |        |

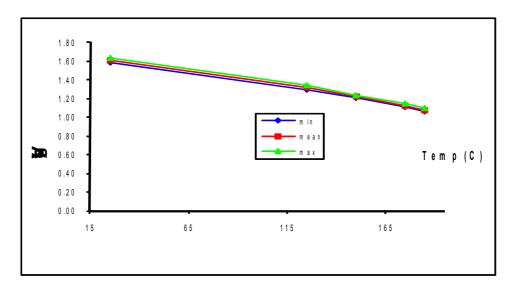

| VIII.3.2.1.Premier test                                         |        |

| VIII.3.2.1.1.Description et résultats                           |        |

| VIII.3.2.1.2.Interprétation                                     |        |

| VIII.3.2.2.Résultats du test de l'opération d'écriture          |        |

| VIII.3.2.3.Résultats du test de l'opération de lecture          |        |

| VIII.3.2.4.Interprétations                                      |        |

| V 111.4.COIICIUSIOII                                            | 90     |

| Conclusion et Perspectives                                      | xciv   |

| Références Bibliographiques                                     | xcviii |

| ANNEXE A: STATUT ACTUEL DES MEMOIRES A HAUTE DENSITE POUR LES APPLICATIONS LWD |     |

|--------------------------------------------------------------------------------|-----|

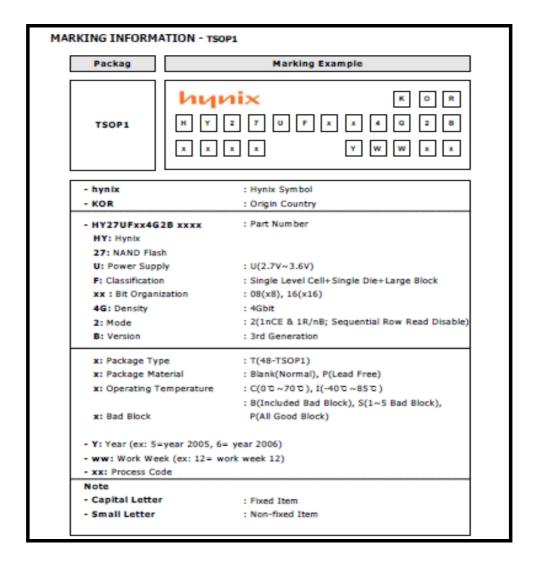

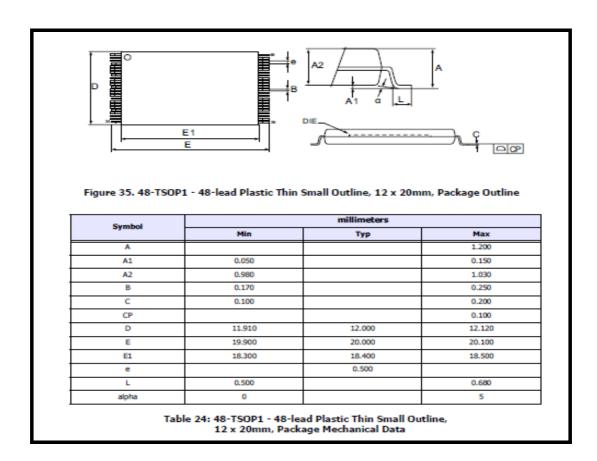

| ANNEXE B: DETAILS SUR LA MEMOIRE HYNIX HY27UF084G2B                            | civ |

| ANNEXE C: DETAILS SUR LA CARTE D'EVALUATION « ALTERA DE2 BOARD »               | cix |

| ANNEXE D: LES PROGRAMMES DE TEST EN VHDL                                       | cxi |

## **Liste des Figures**

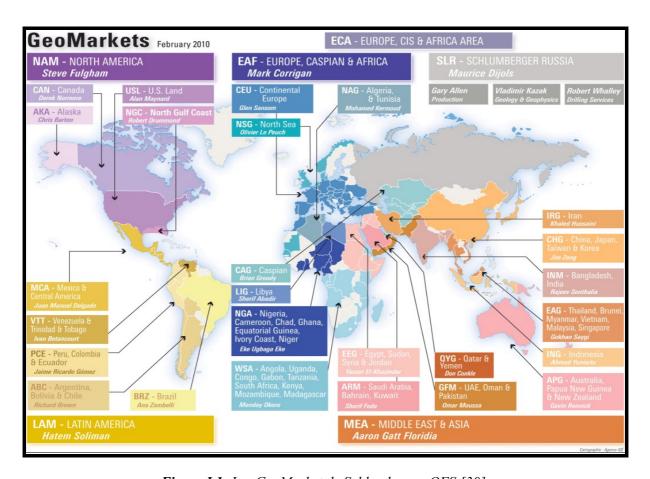

| Figure I.1: Les GeoMarket de Schlumberger OFS                                           | 2  |

|-----------------------------------------------------------------------------------------|----|

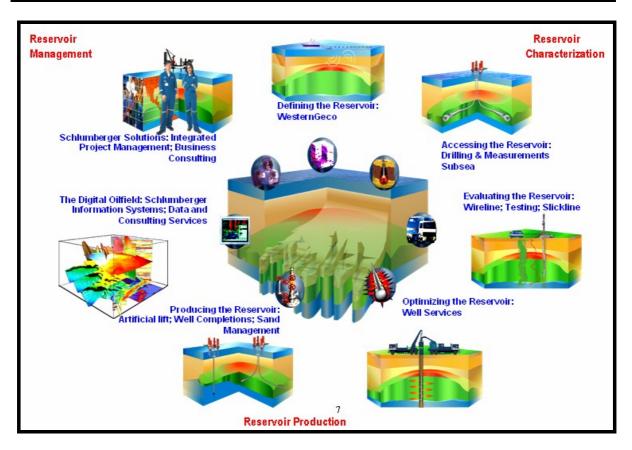

| Figure I.2: Les Segments Schlumberger OFS                                               |    |

| Figure I.3: Localisation des principaux centres de recherches et de développement       | 5  |

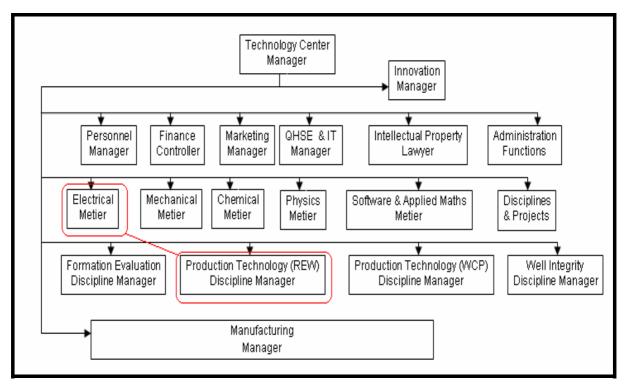

| Figure I.4: Organisation du centre technologique SRPC                                   |    |

| Figure I.5: Photographie du centre SRPC                                                 |    |

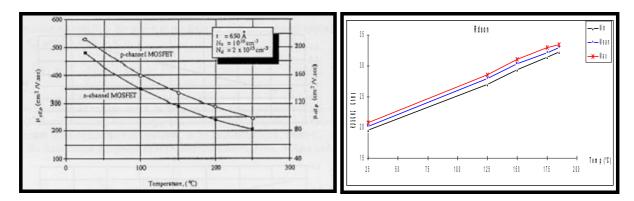

| Figure II.1: Variation de la tension de seuil avec la température                       | 10 |

| Figure II.2: Variation de la mobilité avec la température                               |    |

| Figure II.3: MOS Rdson en température                                                   |    |

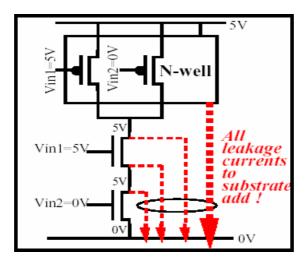

| Figure II.4: Les courants de fuite                                                      | 11 |

| Figure II.5: Variation du courant de fuite avec la température                          |    |

| Figure II.6: Évolution du temps de retard avec la température                           |    |

| Figure II.7: Structure parasite provoquant un latch-up                                  |    |

| Figure II.8: Évolution de la courbe d'âge d'un composant électronique en fonction de la |    |

| température                                                                             |    |

| Figure III.1: Organigramme de classement des mémoires                                   | 22 |

| Figure III.2: Cellule EPROM                                                             |    |

| Figure III.3: Cellule EEPROM                                                            | 26 |

| Figure III.4: Structure des cellules NAND et NOR                                        |    |

| Figure III.5: Référence de tension pour MLC                                             |    |

| Figure III.6: Le pitch                                                                  |    |

| Figure IV.1: Plan du projet                                                             | 35 |

| Figure V.1: Organisation d'une unité logique (LUN)                                      | 42 |

| Figure V.2: Schéma fonctionnel de la NAND Flash Die (LUN)                               |    |

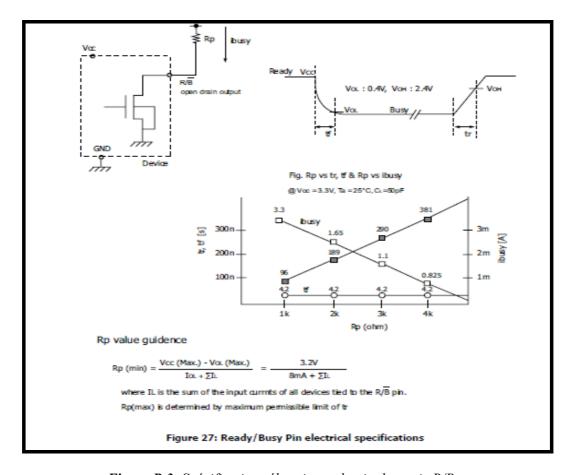

| Figure V.3: Position des signaux de commande et du signal R/B                           |    |

| Figure V.4: Opération de lecture d'une page                                             |    |

| Figure V.5: Programmation d'une page dans un bloc                                       |    |

| Figure V.6: Opération de programmation d'une page                                       |    |

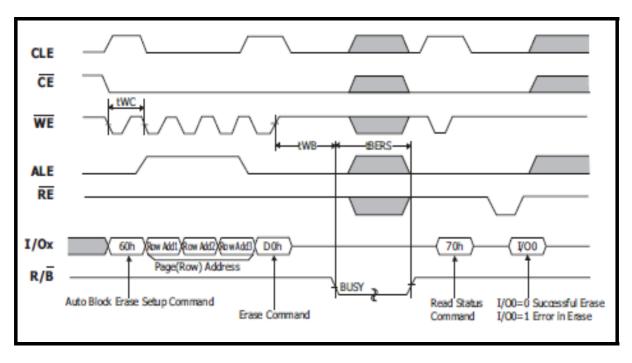

| Figure V.7: Opération d'effacement d'un bloc                                            | 53 |

| Figure V.8: Résumé des commandes des opérations de la mémoire                           | 53 |

| Figure V.9: Conditions maximales tolérées                                               |    |

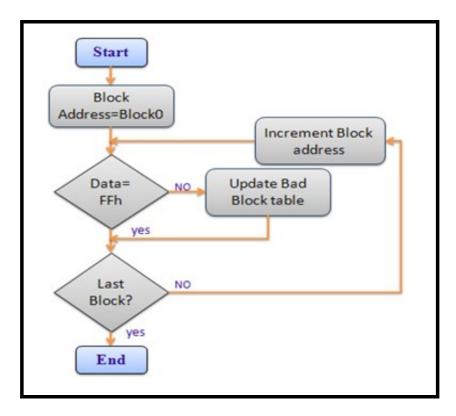

| Figure V.10: Organigramme de gestion des Bad blocs                                      | 55 |

| Figure VI.1: Carte de développement Altera DE2                                          | 58 |

| Figure VI.2: Schéma de placement de la carte d'évaluation Altera DE2                    |    |

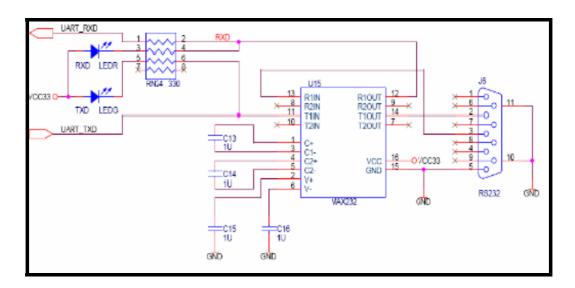

| Figure VI.3: Schématique de la puce MAX232 (RS-232)                                     | 61 |

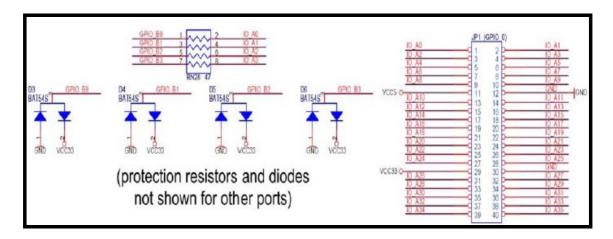

| Figure VI.4: Schéma d'une des têtes d'expansions                                        |    |

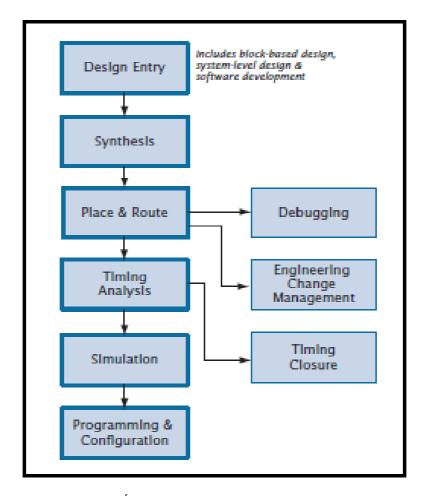

| Figure VI.5: Étapes du processus typique d'une CAD                                      |    |

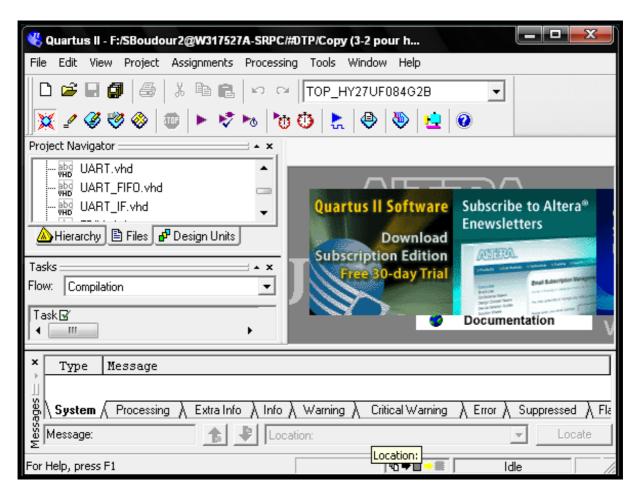

| Figure VI.6: Fenêtre de travail du Logiciel Quartus II                                  |    |

| Figure VI.7: Fenêtre de configuration du port                                           |    |

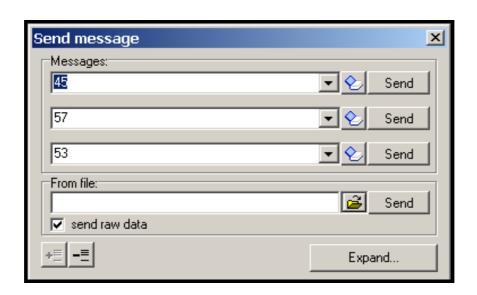

| Figure VI.8: Fenêtre de commande                                                        |    |

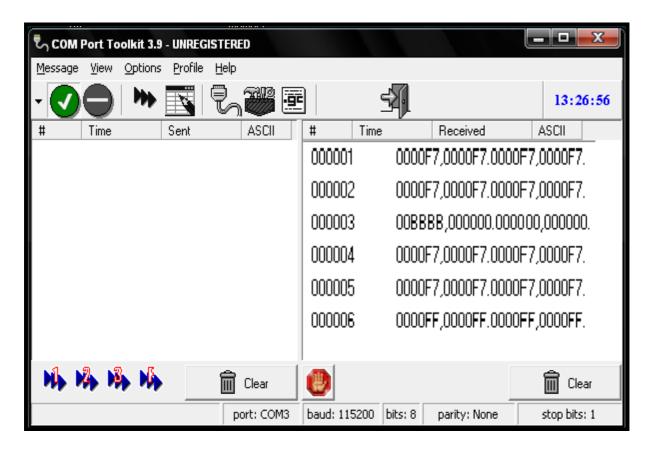

| Figure VI.9: Fenêtre de travail du COM Port Toolkit                                     |    |

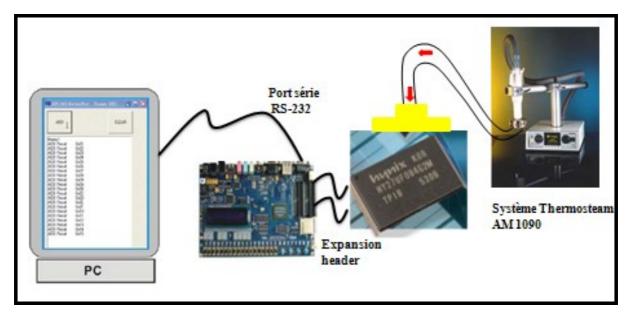

| Figure VI.10: Schéma de principe des mesures en haute température                       |    |

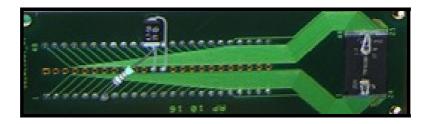

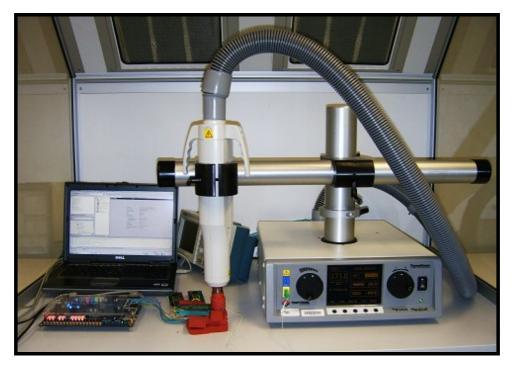

| Figure VI.11: Photographie de la mémoire soudée sur le PCB                           | 68  |

|--------------------------------------------------------------------------------------|-----|

| Figure VI.12: Photographie du dispositif complet lors d'un test                      |     |

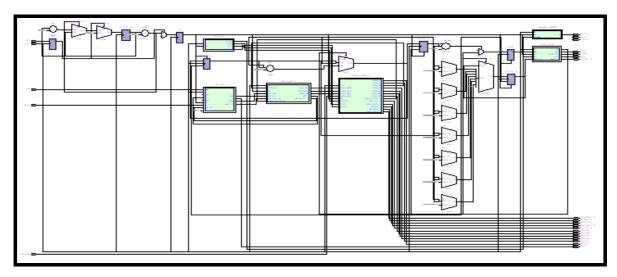

| Figure VII.1: Schéma RTL de l'entité globale : TOP_HY27UF084G2B                      | 72  |

| Figure VII.2: Schéma simplifié de l'entité globale                                   |     |

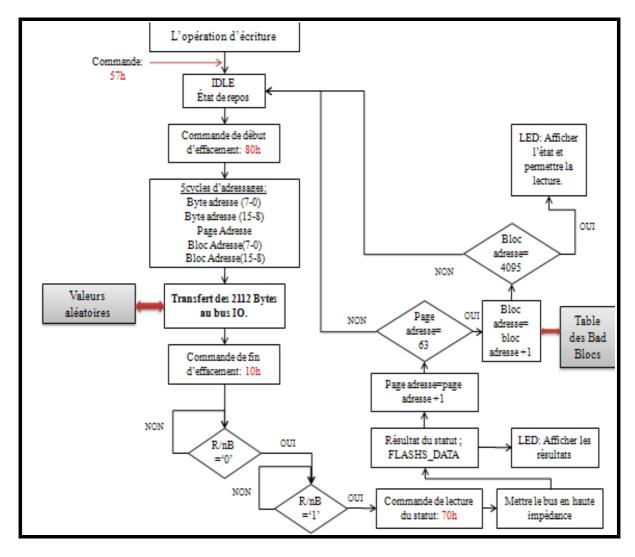

| Figure VII.3: Organigramme de l'opération d'effacement                               |     |

| Figure VII.4: Organigramme de l'opération d'écriture                                 |     |

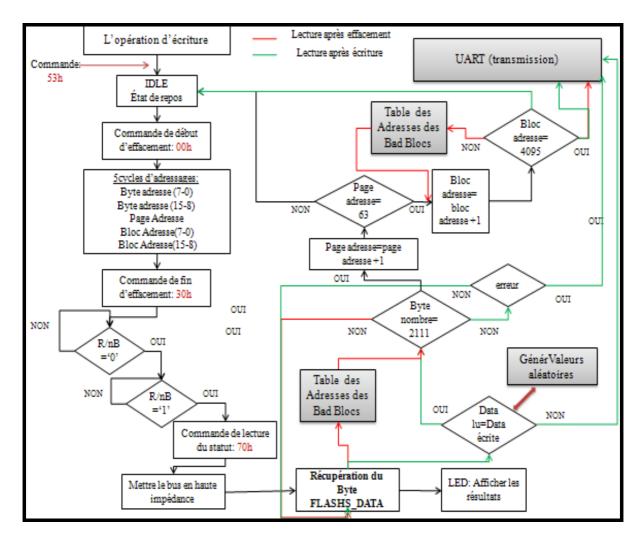

| Figure VII.5: Organigramme de l'opération de lecture                                 | 76  |

| Figure VII.6: Schéma RTL de l'entité FLASH IF                                        |     |

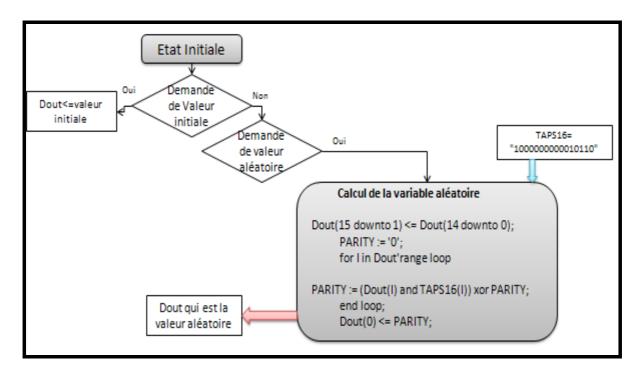

| Figure VII.7: Organigramme de l'algorithme du générateur de valeurs aléatoires       | 77  |

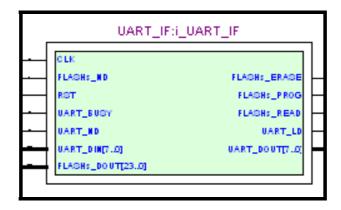

| Figure VII.8: Schéma RTL de l'entité UART IF                                         |     |

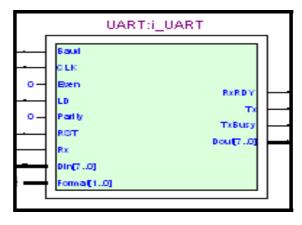

| Figure VII.9: Schéma RTL de l'entité UART                                            |     |

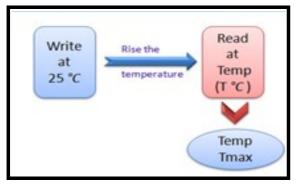

| Figure VIII.1: Schéma du principe du test de l'opération de lecture                  | 82  |

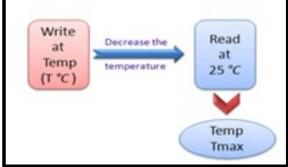

| Figure VIII.2: Schéma du principe du test de l'opération d'écriture                  |     |

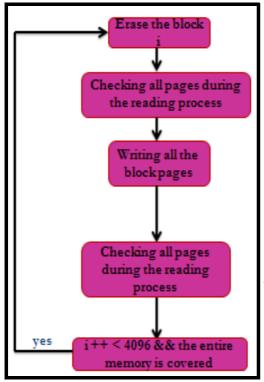

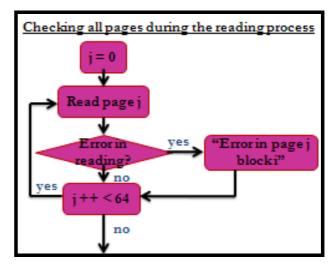

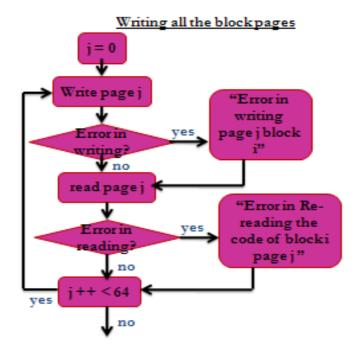

| Figure VIII.3: Procédure principale                                                  |     |

| Figure VIII.4: Procédure de vérification pour la lecture                             |     |

| Figure VIII.5: Procédure d'écriture                                                  |     |

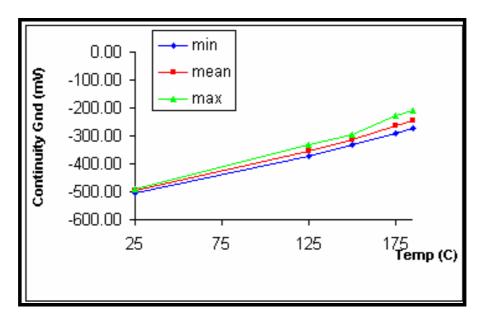

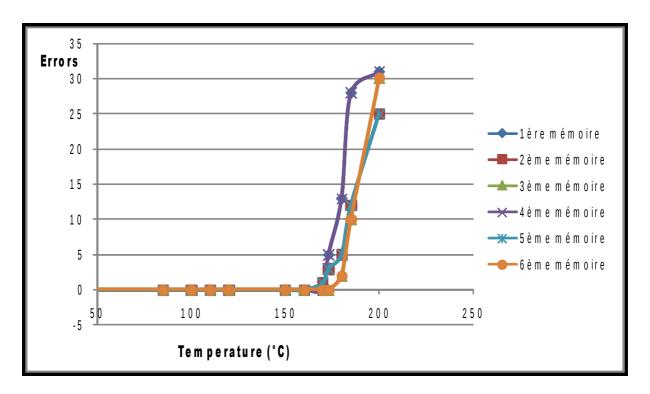

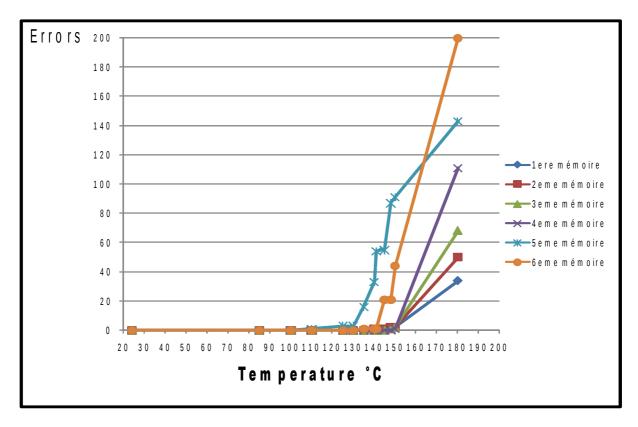

| Figure VIII.6: Courbes des résultats de l'écriture; des différentes mémoires         |     |

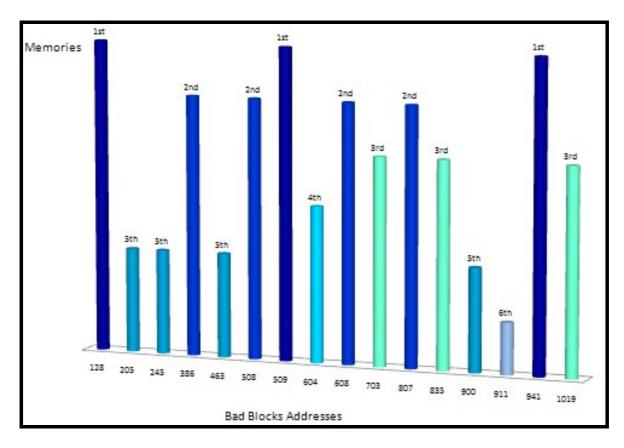

| Figure VIII.7: Nombre et distribution des Bad blocs des six mémoires                 |     |

| Figure VIII.8: Courbes des résultats de la lecture; des différentes mémoires         |     |

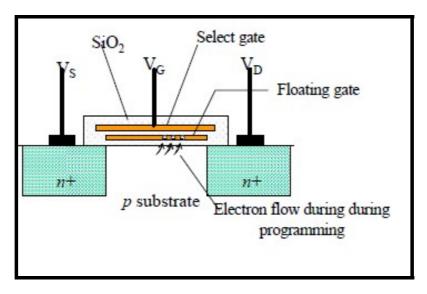

| Figure VIII.9: Schéma du transistor FGMOSFET                                         |     |

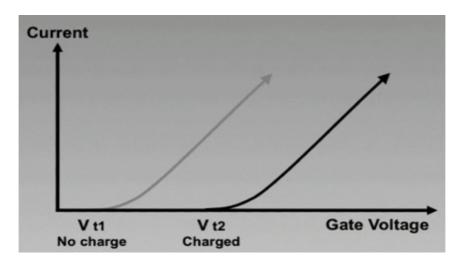

| Figure VIII.10: Tension seuil pour une grille flottante chargée                      |     |

| Figure VIII.11: Courbe représentative de la variation de la tension de seuil avec la |     |

| température                                                                          | 90  |

| Figure B.1: Marking informations                                                     | 105 |

| Figure B.2: Packaging informations                                                   |     |

| Figure B.2: Fackaging informations                                                   |     |

|                                                                                      |     |

| Figure C.1: La Carte Altera DE2                                                      | 110 |

### **Liste des Tableaux**

| Tableau III.1 : Classification des mémoires non-volatiles(1)                       | 18  |

|------------------------------------------------------------------------------------|-----|

| Tableau III.2 : Classification des mémoires non-volatiles(2)                       |     |

| Tableau III.3 : Classification des mémoires non-volatiles(3)                       |     |

| Tableau III.4 : Classification des mémoires volatiles.                             |     |

| Tableau III.5: Niveaux de la SLC [25]                                              |     |

| Tableau III.6: Référence de tension pour SLC [25]                                  |     |

| Tableau III.7: Niveaux de la MLC [25]                                              |     |

| Tableau IV.1: État de l'art des mémoires Flash SLC et MLC(1)                       | 36  |

| Tableau IV.2: État de l'art des mémoires Flash SLC et MLC(2)                       |     |

| Tableau IV.3: État de l'art des Flash SLC.                                         |     |

| Tableau V.1: Nom des signaux et pins correspondants [22]                           | 44  |

| Tableau V.2: Description des signaux de la HY27UF084G2B [22]                       | 45  |

| Tableau V.3: Les cinq cycles d'adressage[22]                                       | 46  |

| Tableau VI.1: Affectation des broches du port RS-232[13]                           | 62  |

| Tableau VIII.1: Comparaison entre nombre de Bad Blocs de deux mémoires et valeurs  |     |

| approximatives des temps d'effacement, d'écriture et de lecture                    |     |

| Tableau VIII.2: Échantillon d'erreurs lors de la lecture                           |     |

| Tableau VIII.3: Paramètres intervenant dans l'équation de la tension de seuil [46] | 89  |

| Tableau B.1: Timing caractéristiques                                               | 108 |

#### **Introduction Générale**

De nos jours le marché de l'électronique haute température est petit et est principalement dominé par l'industrie du "petroleum well-logging", étant une compagnie de services pétroliers, Schlumberger y déploie de gros moyens et spécialement dans le choix des technologies et des composants électroniques adéquats aux applications en ses milieux, aux conditions extrêmes.

Parmi les nombreux services fournis par Schlumberger, on cite le Logging-while-dilling (LWD service) où les outils élaborés sont chargés des mesures des conditions des puits et des caractéristiques de la formation rocheuse (résistivité,porosité,densité...).Les données recueillies sont alors transmises à la surface en temps réel et utilisées pour positionner l'outil dans le modèle géologique, mettre à jour ce modèle et avec précision, bien l'orienter vers les objectifs du réservoir.

Face à ce défi de télémétrie en temps réel dont la vitesse ne dépasse pas 12bit/s et le besoin continuel de meilleures résolutions, la solution était alors de stocker une grande partie des informations dans les mémoires des outils au fond des puits et de récupérer ces données une fois l'outil à la surface.

La nécessité des mémoires flash à grandes densités trouve alors sa place,ce qui conduit vers l'objectif de ce projet, réalisé dans le plus grand centre de développement technologique de Schlumberger, qui consiste à évaluer et qualifier différentes technologies de ces mémoires susceptibles de fonctionner à haute température.

Avant d'exposer l'étape de l'évaluation de la mémoire sélectionnée après notre étude, à haute température et les résultats obtenus, ce rapport commencera dans le premier chapitre par une brève présentation de la compagnie, pour arriver plus précisément au groupe au sein

duquel j'ai effectué mon travail et aux domaines qu'il exerce.

Le second chapitre traitera des effets de la haute température sur les composants électroniques en général, ce qui permettra de mieux préciser l'axe de nos recherches et la procédure de nos tests.

Le troisième chapitre commencera par une mise au point des spécifications des mémoires requises par ce projet et déploiera par la suite l'étude des différentes mémoires existantes sur le marché, en abordant leurs types et en les classant selon certaines de leurs caractéristiques; pour aboutir au noyau de notre recherche qui est la mémoire non volatile flash, où une brève explication de son principe de mémorisation et de ses principaux types sera présentée ainsi qu'une comparaison de ses différentes technologies qui donnera les raisons du choix effectué.

Après avoir sélectionné le type de mémoire flash à étudier; restait le choix entre les différents fabricants et les caractéristiques qu'ils offraient et cela fera l'objet du quatrième chapitre. On y exposera aussi le plan de travail établi.

Le cinquième chapitre sera entièrement consacré à la mémoire Hynix, sa datasheet y sera totalement examinée afin d'établir un résumé de ses caractéristiques et d'utiliser toutes les fonctionnalités et méthodes de programmation qu'elle offre.

Le sixième et le septième chapitre regrouperont la partie de l'élaboration du dispositif des tests à effectuer de part l'étude du matériel utilisé; principalement la carte de développement mais aussi le programme de contrôle et de manipulation de la mémoire en VHDL

Le dernier chapitre présentera la partie pratique de l'évaluation à haute température de la mémoire, on y introduira les types de tests et la procédure à pratiquer. Ce même chapitre contiendra aussi les résultats et les interprétations du comportement de la mémoire lors de ces tests.

#### Chapitre I : Présentation de l'Entreprise

Ce premier chapitre est consacré à la présentation de l'entreprise au sein de laquelle j'ai effectué mon stage; une vue générale de la compagnie de part son organisation et ses différents segments sera présentée, un accent sera porté sur ses installations de recherche et de développement dont fait partie SRPC (Schlumberger Riboud Product Center) qui sera à son tour présenté afin d'aboutir à la fin de ce chapitre, au groupe TECHNO et sa mission. [29, 30, 35].

#### I.1. Introduction:

Schlumberger est la plus grande compagnie de prestation de services pétroliers dans le monde. Elle fournit l'information, la technologie et les solutions à ses clients, travaillant dans le pétrole et le gaz naturel, pour en optimiser les performances.

La compagnie a été fondée en 1926 en Alsace par deux frères Conrad et Marcel Schlumberger qui ont découvert un nouveau système de mesures permettant la description des sous-sols, basées sur les mesures de résistance électrique effectuées en surface ;un an après ils prouvent la possibilité de la mise en œuvre de ces mêmes principes au fond d'un puits. Ainsi, en utilisant des instruments de mesure à l'extrémité d'un câble conducteur « wire-line », ils ont pu identifier les couches géologiques contenant du pétrole. La technique du « logging » était alors née et pendant près de trente ans, la société s'est exclusivement consacrée à cette activité. Elle s'est ensuite vite diversifiée, pour être présente dans des secteurs comme l'électronique, la gestion des systèmes d'eau, d'air et d'électricité, ainsi que dans les télécommunications et les systèmes d'information ou encore la recherche d'eau et séquestration de CO2.

Aujourd'hui, Les principaux sites administratifs du groupe Schlumberger sont situés à Houston, Paris et la Haye. elle emploie plus de 77.000 personnes de plus de 140

nationalités travaillant dans environ 80 pays.

#### I.2. Organisation et Segments :

Schlumberger gère ses activités à travers 33 régions (GeoMarket), qui sont regroupées en quatre zones géographiques et cela en Amérique du Nord, Amérique latine, Europe, CEI (Communauté des États Indépendants), Afrique au Moyen-Orient et en Asie comme le montre la Figure I.1.

Figure I.1: Les GeoMarket de Schlumberger OFS [30].

Cette structure offre aux clients un point de contact unique au niveau local pour les opérations sur le terrain et rassemble des équipes géographiquement ciblées pour répondre aux besoins locaux et offrir des solutions personnalisées. Collaborant avec les différents segments technologiques de l'entreprise, les marchés géographiques fournissent un

puissant conduit par lequel transite l'information et le savoir-faire aux clients, et à travers lequel des ingénieurs et des géoscientifiques de Schlumberger maximisent les synergies technologiques sur toute la durée du champ.

Le groupe Schlumberger s'organise autour de sept segments technologiques qui assument totalement tous les services pétroliers depuis l'inspection (recherche de pétrole) jusqu'à la production et la maintenance. Les services qu'offre chaque segment de Schlumberger Oilfield Services sont listés ci-dessous :

- WesternGeco : service d'acquisition et de traitement de données sismiques.

- Wire-line : service fournissant l'information nécessaire à la caractérisation du réservoir, à la planification et au contrôle de la construction des puits ainsi qu'à l'évaluation de la production

- drilling and measurement :service de forages dirigés de mesures et de logging : en cours de forage.

- Well services : optimisation de la production, services de cimentation et de stimulation de puits.

- Well completion and productivity : services d'essais de complétion et de production et d'activation des puits.

- integrated project management : conseil, gestion des projets et études d'ingénierie mobilisant l'expertise des autres segments technologiques.

- Schlumberger information solution : solutions stratégiques intégrées comprenant des services de gestion de l'information, des technologies de l'information et une gamme complète de services d'experts.

La Figure I.2 qui suit résume l'ensemble de ces segments

Figure 1.2: Les Segments Schlumberger OFS [30].

#### I.3. Recherche et Développement :

Avec 25 installations de recherche et d'ingénierie dans le monde entier, Schlumberger met fortement l'accent sur le développement de technologies novatrices qui ajoute de la valeur pour ses clients. En 2008, elle a investi environ 818 millions de dollars dans la Recherche & Développement (plus que toutes les compagnies du même secteur, réunies).

On peut voir dans la Figure I.3 les principaux centres de recherche et de développement technologique de part le monde.

Figure I.3: Localisation des principaux centres de recherches et de développement [35].

#### I.4. Schlumberger Riboud Product Center (SRPC):

SRPC est le plus grand centre de technologie Schlumberger et de développement en Europe il se situe comme le montre la Figure précédente en plein Paris ,il compte plus de 500 scientifiques, ingénieurs et techniciens .

Le centre est réputé mondialement pour ses compétences en électronique hautetempérature, en systèmes mécaniques pour conditions extrêmes (pression, chocs, vibrations), en physique des capteurs et de la mesure, en chimie et sciences des matériaux, en développement des logiciels, en mathématiques appliquées, en géophysique et géologie et en génie pétrolier.

#### I.4.1. L'organisation du centre technologique SRPC :

Comme le montre l'organigramme de la Figure I.4; le SRPC est constitué d'une partie Études et une partie Production.

Dans chaque partie des équipes multidisciplinaires sont formées en fonction des projets en cours : les membres de ces équipes appartiennent à différents métiers : **Mécanique, électrique physique/chimie** et **software**, ils seront réaffectés à d'autres projets, une fois le travail accompli sur le projet en question. Le chef de métier a un rôle de responsable fonctionnel et de suivi de carrière des personnes appartenant à son métier. En plus de ces départements, il existe des groupes technologiques pour chaque métier.

La partie production travaille sans distinction de segments. Elle se charge de fabriquer, monter, tester et évaluer les produits qui ont été conçus par la partie Études. Elle va également piloter la sous-traitance pour tous les segments.

*Figure I.4:* Organisation du centre technologique SRPC [30].

#### I.4.2. La mission du centre :

SRPC a pour mission de concevoir, développer et fabriquer des produits destines aux activités de services pétroliers suivants :

- Réservoir Évaluation,

- Réservoir Développement,

Ces produits sont essentiellement fournis à Schlumberger Oilfield Services.

Cependant, certains produits spécifiques sont conçus pour être vendus ou loués directement aux clients tels que des vannes de sécurité, des manomètres permanents et des équipements de mise en production temporaire. De plus, des produits sélectionnés (équipement d'essai de puits et de travail de câble) sont vendus de préférence sous leur forme standard mais peuvent incorporer des modifications limitées pour répondre aux besoins du client.

#### I.4.3. <u>Le Groupe Technologie électrique :</u>

Le service, Electrical Technology, au sein duquel j'ai effectué mon stage fait partie de la branche Engineering, comme l'illustre l'organigramme de la Figure I.4. Sa mission est d'identifier, valider et maintenir les technologies qui améliorent le coût, la fiabilité et la performance technique des outils. Il permet de faire le lien entre les produits et fabrications standards et les conditions extrêmes que requièrent les applications Schlumberger, avec une production sécurisée et à coût raisonnable. Ce service intervient depuis les composants électroniques jusqu'au procédé d'assemblage, en passant par le packaging. Il intervient sur les projets en développement, sur la qualification de nouvelles technologies électroniques et sur les outils fabriqués, sur l'analyse des erreurs et l'obsolescence.

Figure I.5: Photographie du centre SRPC [30].

La présentation de la compagnie et tout particulièrement du groupe TECHNO nous donne une idée sur le domaine du travail que nous aurons à effectuer lors du stage et de l'objectif final de ce dernier.

# Chapitre II : L'Électronique Haute-Température et les Mécanismes de Défaillances

Ce chapitre traitera des effets de la température, qui constitue un paramètre à surveiller de près, sur les performances et sur la fiabilité des circuits électroniques en général, cela nous éclairera quant aux tests et procédures de tests à venir. [1, 2, 3 et 29].

# II.1. <u>Effets de la température sur les composants</u> <u>électroniques:</u>

Un système électronique qui fonctionne en haute température est confronté à des phénomènes divers qui peuvent le mettre hors service. Le plus important est le vieillissement accéléré des composants électroniques qui représente un problème majeur, car il ne s'agit pas seulement de mettre en service ce système à telle ou telle température mais de certifier aussi un temps minimum de fonctionnement à la température en question.

Le vieillissement est dû à d'autres phénomènes présents, en haute température, appelés mécanismes de défaillances. Les déformations thermomécaniques et la dissipation thermique en sont des exemples et peuvent sérieusement dégrader le package du composant alors que le latch-up et l'électromigration peuvent porter atteinte au silicium.

#### II.2. Les effets à court terme (La performance) :

#### II.2.1. La tension de seuil :

La tension de seuil est la tension minimale de grille à laquelle le canal commence à conduire. En règle générale, la tension de seuil des deux transistors NMOS et PMOS à enrichissement, diminue (Magnitude par 1,5 à 2 mV / °C) avec l'augmentation de la température, comme le montre la Figure II.1.

Figure II.1: Variation de la tension de seuil avec la température[1].

#### II.2.2. <u>La mobilité des porteurs de charge :</u>

Elle est le rapport de la vitesse des porteurs par le champ électrique. Ainsi l'augmentation de la température et donc de l'agitation thermique conduit à la diminution de la mobilité dans les conducteurs, en augmentant le nombre de collisions entre porteurs.

Figure II.2: Variation de la mobilité avec la température[1].

Figure II.3: MOS Rdson en température [3].

Les variations de la tension de seuil et de la mobilité affectent le courant de drain « *iD* », la transconductance et la résistance drain-source.

#### II.2.3. Le courant de fuite :

C'est un paramètre limitant du bon fonctionnement des composants MOSFET en haute

température.

Figure II.4: Les courants de fuite [1].

Il dépend de la géométrie du transistor (la largeur du canal) et augmente avec la température (Figure II.5).

Figure II.5: Variation du courant de fuite avec la température [1].

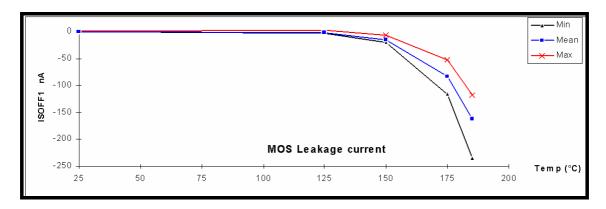

#### II.2.4. Temps de retard :

Il est dû à la charge et à la décharge des condensateurs au cours des mises à 1 et à 0. Il augmente avec un rapport de 1,67 entre 25°C et 200°C. Ce rapport représente donc la diminution de la fréquence d'horloge des applications utilisées à cette température, et donc l'augmentation du temps nécessaire à l'exécution d'opérations telles que la lecture et l'écriture.

Figure II.6: Évolution du temps de retard avec la température [3].

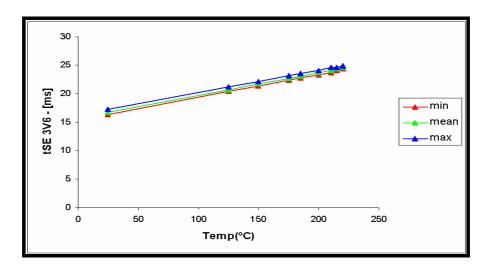

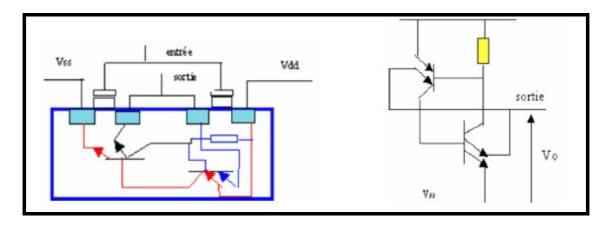

#### II.2.5. Le latch-up:

Le latch-up a pour origine une structure parasite apparaissant à la construction d'un circuit intégré.

Figure II.7: Structure parasite provoquant un latch-up [1],

Cette structure parasite composée des jonctions N et P des transistors MOS forme un thyristor entre Vdd et Vss. Si le thyristor se déclenche, il court-circuite l'alimentation et cause des dégâts irréversibles sur le circuit intégré. Ce cas se présente si la tension d'entrée dépasse Vdd.

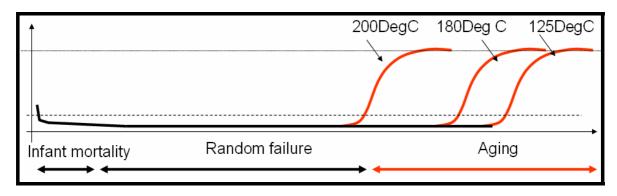

#### II.3. Les effets à long terme (Loi d'Arrhenius) :

Exposés à la haute température, les composants subissent une usure très importante qui réduit leur durée de vie. Il s'agit d'un vieillissement accéléré qui s'accentue exponentiellement en fonction de la température selon la loi d'Arrhenius :

$$r = A \exp(-E_a/kT)$$

Où r : le facteur d'accélération de vieillissement.

T : la température absolue en °K

Ea : l'énergie d'activation (eV) qui dépend du matériau et du mécanisme de défaillance

${f k}$  : constante de Boltzmann (8,62 . 10-5 eV/ $^{\circ}$ K)

**A**: Une constante.

On remarque que si la température augmente de quelques degrés, le facteur d'accélération augmente très vite ; donc un composant vieillit beaucoup plus vite quand il est à une température élevée. La Figure II.8 permet d'observer l'évolution de la courbe d'âge d'un composant électronique en fonction de la température.

#### Mortality

Figure II.8: Évolution de la courbe d'âge d'un composant électronique en fonction de la température [3].

Ce chapitre montre que la température influe fortement sur le fonctionnement des composants électroniques et c'est exactement ce qui a poussé Schlumberger à développer le procédé de qualification des composants à haute température dont le sens des tests est orienté selon les fonctionnalités du composant en question.

Dans notre application le composant est une mémoire et cette mémoire doit satisfaire certaines spécifications ordonnées par le projet pour lequel elle servira. Ces spécifications seront introduites dans le chapitre qui suit.

#### Chapitre III : Les Mémoires

Afin de nous familiariser avec les mémoires que nous aurons à traiter tout au long de ce mémoire, nous passerons en revue dans ce chapitre les différents types de mémoire à semi-conducteur rencontrées de nos jours, leurs principes de mémorisation et leurs technologies, on comprendra mieux ainsi les possibilités offertes par telle ou telle catégorie de mémoire, et permettra une sélection plus judicieuse du composant, vérifiant les spécifications précisées. Nous verrons aussi à la fin de ce chapitre quelques exemples de mémoires illustrant les possibilités de différentes technologies au niveau produit. [3, 5, 6, 7, 8, 9, 22, 23, 24, 25, 34, 35, 36, 37].

#### III.1. Les spécifications du projet :

En vue de l'application future de la mémoire qualifiée, cette dernière devra contenir une grande quantité d'informations et ne devra pas les perdre en l'absence d'alimentation; des fois pendant de longues périodes et cela 24/7 sans l'intervention de l'homme. La seule mémoire regroupant tous ces critères est la EEPROM Flash; la densité voulue est de 8Gbit et de préférence en un seul bloc à cause des contraintes de refroidissement (à la rigueur deux de 4Gbit); quant au procédé de fabrication, la finesse de gravure devra être entre 90nm et 50nm car celles avec une finesse supérieure à 90nm sont déjà testées<sup>(1)</sup> et avec celle de moins de 50nm on ne doit pas s'attendre à de bons résultats.

#### III.2. Introduction:

Les mémoires sont des dispositifs électroniques destinés à enregistrer, à conserver et à restituer à la demande des informations numériques de toutes sortes, et notamment celles produites ou utilisées par les programmes d'un ordinateur ou d'un microcontrôleur.

<sup>(1) :</sup>Ces tests de mémoires effectués antérieurement, sont présentés dans l'annexe A.

Les mémoires sont la catégorie de circuits intégrés représentant le plus grand volume en termes de production et de chiffre d'affaires. De plus, les circuits VLSI actuels contiennent souvent une ou plusieurs parties de mémoires intégrées (mémoire cache) ce qui augmente d'autant l'importance de ce type de circuits.

La mémoire est organisée sous forme de lignes et de colonnes. À chaque intersection correspond un bit de mémoire.

La capacité de stockage des mémoires suit une progression géométrique (loi de Moore) prenant exemple sur des mémoires issues de la technologie 180 nm elles présentent une capacité de stockage de 1 Gbit; cela correspond approximativement au contenu de 62 000 pages écrites. La surface de la puce de silicium contenant cette énorme quantité d'information dépasse à peine 4 cm2.

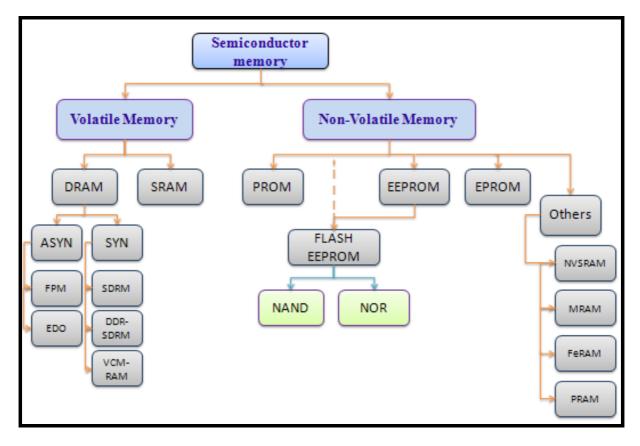

#### III.3. Classement des mémoires:

Il existe sur le marché une très grande variété de produits « mémoires », de fonctionnements différents et d'applications diverses. La classification des mémoires n'est pas simple, mais peut se baser sur différents critères<sup>(1)</sup>.

Un premier critère est la possibilité de lecture/écriture dans un temps de cycle :

**Mémoires mortes ou ROM (Read Only Memory) :** elles permettent seulement la lecture de l'information pré-enregistrée soit en cours de fabrication (on parle de Rom programmable par masque)., soit par l'utilisateur lui-même, mais l'enregistrement de l'information ne peut être fait qu'une seule fois.

Mémoires vives ou RAM (Random Access Memory) : mémoires à accès aléatoire dans lesquelles chaque cellule mémoire peut-être identifiée par une adresse et pour laquelle l'accès à n'importe quelle cellule (associée à une adresse) se fait approximativement à la même vitesse, elles permettent la lecture ainsi que l'écriture de l'information.

<sup>(1) :</sup>Un classement important à été réalisé pour les mémoires volatiles et non volatiles résumant leur état actuel et cela selon leur types, les fabricants les fournissant, leur durée de rétention, leur endurance, leur densité et surtout selon les gammes de températures proposées pour ces mémoire. (les quatre pages suivantes).

| Memory type       | Add. Function |                         | Manufacturer              | State   | Technology                             | Retention          | Endurance | Temperature (°C) | Density (bit)         |

|-------------------|---------------|-------------------------|---------------------------|---------|----------------------------------------|--------------------|-----------|------------------|-----------------------|

|                   |               |                         | Honeywell                 |         | RICMOS SOI 0.75μm                      |                    | 2.00E+05  | 125              | 256k                  |

| ROM               |               |                         | NEC                       |         |                                        |                    |           | 85               |                       |

|                   |               |                         | Maxim                     |         | ?                                      |                    |           | 85               |                       |

| 00044             |               |                         | BAE System                |         | CMOS                                   | 10 ans             | 2.00E+05  | 125              | 256k                  |

| PROM              |               |                         | Intersil                  |         | CMOS                                   |                    |           | 125              | 4k - 16k              |

|                   |               |                         | STMicroelectronics        |         |                                        |                    |           | 125              | 1M                    |

| EPROM             |               |                         | Atmel                     |         |                                        |                    |           | 125              | 256k - 2M             |

|                   |               |                         | Maxim                     |         | ?                                      |                    |           | 85               |                       |

|                   |               | 1                       | Toshiba                   |         |                                        | 10 ans             | 1.00E+05  | 85               |                       |

|                   |               |                         | STMicroelectronics        |         | CMOS?                                  | 40 ans             | 1.00E+06  | 125              | 1M                    |

|                   |               | I <sup>2</sup> C serial | Holtek                    |         |                                        | 40 ans             | 1.00E+07  | 85               |                       |

|                   |               | 1 Cacina                | Microchip                 |         | low power CMOS                         | 200 ans            | 1.00E+06  | 150              | 1M                    |

|                   |               |                         | STMicroelectronics        |         | CMOS?                                  | 40 ans             | 1.00E+06  | 125              | 512k                  |

|                   |               |                         |                           |         |                                        | 200 ans            | 1.00E+06  | 150              | 1M                    |

|                   |               | SPI serial              | Microchip<br>ISSI         |         | low power CMOS<br>low power CMOS       | 200 ans<br>100 ans | 1.00E+06  | 125              | 1k - 256k             |

|                   |               | SPI Serial              |                           |         | low power Circos                       | 50 ans à 125°C     | 5.00E+06  | 125              | 32k                   |

|                   |               |                         | Seiko Instrument          |         |                                        | 50 ans a 125°C     | 5.001+06  |                  |                       |

|                   |               |                         | Rohm                      |         |                                        |                    |           | 125              | 32k                   |

|                   |               | microwire serial        | STMicroelectronics        |         | CMOS?                                  | 40 ans             | 1.00E+06  | 125              | 16k                   |

|                   | série         |                         | Microchip                 |         | CMOS                                   | 200 ans            | 1.00E+06  | 150              | 16k                   |

|                   |               |                         | Rohm                      |         |                                        |                    |           | 125              | 16k                   |

|                   |               |                         | Catalyst semiconductor    |         | low power CMOS 0.8µm                   | 100 ans            | 1.00E+06  | 125              | 256k - 128k - 64k -32 |

|                   |               |                         | ISSI                      |         | low power, low voltage CMOS            | 40 ans             | 1.00E+06  | 85               |                       |

| EEPROM            |               | 3 wire                  | Holtek                    |         |                                        | 10 ans             | 1.00E+05  | 85               |                       |

| EEPHUM            |               | 5 WIFE                  | Seiko Instrument          |         |                                        | 15 ans à 125°C     | 1.50E+06  | 125              | 16k                   |

|                   |               |                         | Holtek                    |         |                                        | 40 ans             | 1.00E+06  | 85               |                       |

|                   |               |                         | ISSI                      |         | low power 0.11 - 0.15 - 0.18 - 0.35µm? | 100 ans            | 1.00E+06  | 125              | 1k - 256k             |

|                   |               | 2 wire                  | Seiko Instrument          |         |                                        | 10 ans             | 1.00E+06  | 85               |                       |

|                   |               |                         | Atmel                     |         |                                        |                    |           | 125              | 256k                  |

|                   |               | 1wire                   | Maxim                     |         | ?                                      |                    | 2.00E+05  | 85               |                       |

|                   |               |                         | Microchip                 |         | low power CMOS                         | 200 ans            | 1.00E+06  | 150              | 16k                   |

|                   |               |                         |                           |         | CMOS?                                  | 40 ans             | 1.00E+06  | 85               | 64k                   |

|                   |               |                         | STMicroelectronics        |         | CMOS?                                  | 40 ans             | 1.00E+06  | 90               | 2k                    |

|                   |               |                         | Honeywell                 | article | CHICAL                                 | 40 8112            | 2.002.700 | 250              | **                    |

|                   |               |                         | Renesas                   | article |                                        | 10 ans             | 1.00E+07  | 85               |                       |

|                   |               | 7                       | Catalyst semiconductor    |         | CMOS floating gate 0.8µm               | 100 ans            | 1.00E+07  | 125              | 256k                  |

|                   | parallèle     |                         | Catalyst sellificonductor |         | floating gate CMOS                     | 100 ans            | 1.00E+05  | 175              | 256x<br>1M            |

|                   |               |                         | Intersil                  |         |                                        |                    |           |                  |                       |

|                   |               | I .                     | About                     |         | floating gate CMOS                     | 100 ans            | 1.00E+05  | 125              | 512k                  |

|                   |               |                         | Atmel                     |         | CMOS                                   | 10 ans             | 1.00E+04  | 125              | 4M                    |

|                   |               |                         |                           |         |                                        |                    |           |                  |                       |

| gende température |               | < 95°C                  |                           |         |                                        |                    |           |                  |                       |

| ļ                 |               | 95 à 110°C              |                           |         |                                        |                    |           |                  |                       |

| Į.                |               | 125 à 135°C             |                           |         |                                        |                    |           |                  |                       |

| L                 |               | 150 à 175°C             |                           |         |                                        |                    |           |                  |                       |

|                   |               | 250°C                   |                           |         |                                        |                    |           |                  |                       |

Tableau III.1 : Classification des mémoires non-volatiles(1).

| Memory type         | Add. Function |                                                             | Manufacturer           | State | Technology         | Retention      | Endurance                                        | Temperature (°C) | Density (bit)             |

|---------------------|---------------|-------------------------------------------------------------|------------------------|-------|--------------------|----------------|--------------------------------------------------|------------------|---------------------------|

|                     |               |                                                             | Spansion               |       | 200 - 110 - 90 nm  | 20 ans         | 1.00E+05                                         | 85               | 16M - 1G                  |

|                     | NOR           |                                                             | Samsung                |       | 90 nm?CMOS         | 10 ans         | 1.00E+05                                         | 85               |                           |

|                     |               |                                                             | Toshiba                |       |                    |                |                                                  | 85               | 16M - 128M                |

|                     |               |                                                             |                        |       | 0.13um             |                | 1.00E+05                                         | 85               | 32 - 256M                 |

|                     |               |                                                             |                        |       | 0.13um             | 20 ans         | 1.00E+05                                         | 85               | 16 - 32 -64M              |

|                     |               |                                                             |                        |       |                    | 20 ans         | 1.00E+05                                         | 150              | 8M                        |

|                     |               |                                                             | Numonyx                |       |                    | 20 ans         | 1.00E+05                                         | 125              | 8 - 64M                   |

|                     |               |                                                             |                        |       | 0.11um             | 7 ans          | 1.00E+05                                         | 125              | 16M -32 M                 |

|                     |               | serial                                                      |                        |       | T7Y, T9HX          | 20 ans à 55°C  | 1.00E+04                                         | 125              | 512k - 64M                |

|                     |               | serial                                                      |                        |       |                    | 20 ans         | 1.00E+05                                         | 125              | 8M - 64M                  |

|                     |               |                                                             | Samsung                |       | 90nm               |                |                                                  | 85               |                           |

|                     |               | SLC small block                                             | Hynix                  |       |                    | 10 ans         | 1.00E+05                                         | 85               |                           |

|                     |               |                                                             | Numonyx                |       |                    | 10 ans         | 1.00E+05                                         | 85               | 128M - 1G                 |

|                     |               |                                                             | Samsung                |       | 90 - 73nm?         |                |                                                  | 85               |                           |

|                     |               | SLC large block                                             | Hynix                  |       |                    | 10 ans         | 1.00E+05                                         | 85               |                           |

|                     |               |                                                             | Numonyx                |       |                    | 10 ans         | 1.00E+05                                         | 85               | 1G - 16G                  |

|                     | NAND          |                                                             | Samsung                |       | 90 - 60nm?         |                |                                                  | 85               |                           |

|                     |               | MLC large block                                             | Numonyx                |       |                    | 10 ans         | 1.00E+04                                         | 85               | 8G - 16G                  |

|                     |               |                                                             |                        |       |                    |                |                                                  | 85               | 16M - 1G                  |

|                     |               |                                                             | Toshiba                |       |                    |                | <del>                                     </del> | 70               | 32G                       |

| FLASH               |               |                                                             |                        |       |                    |                |                                                  | 70               | 320                       |

|                     |               |                                                             | Micron                 |       |                    |                |                                                  | 85               |                           |

|                     | ORNAND        | 1                                                           | THICK GIT              |       | 90 - 65nm          | 10 ans         | 1.00E+05                                         | 85               | 128M - 512M               |

|                     | District      | 1                                                           | Spansion               |       | 200nm              | 20 ans         | 1.00E+06                                         | 125              | 4M - 8M - 16M             |

|                     |               |                                                             |                        |       | 170nm              | 20 ans         | 1.00E+06                                         | 125              | 16M - 32M                 |

|                     |               |                                                             |                        |       | 320nm              | 20 ans         | 1.00E+05                                         | 125              | 16M                       |

|                     |               |                                                             |                        |       | 320nm              | 20 ans à 125°C | 1.00E+06                                         | 125              | 32M - 16 - 8 - 4 - 2 - 1M |

|                     |               |                                                             |                        |       | 230nm / 320nm      | 10 ans à 1500  | 1,000,000                                        | 125              | 64M -8M                   |

|                     |               |                                                             | Samsung                |       | ?                  | 10 arts a 150c | _                                                | 85               | D4M -GM                   |

|                     |               |                                                             |                        | ?     |                    |                |                                                  | 85               |                           |

|                     |               |                                                             | Numonyx                | r     |                    |                |                                                  |                  | 10.330                    |

|                     |               |                                                             | Toshiba                |       |                    |                |                                                  | 85               | 1G - 32G                  |

|                     |               |                                                             | Numonyx                |       |                    |                |                                                  | 85               |                           |

|                     |               |                                                             | Sharp                  |       |                    | 10 ans         |                                                  | 85               | 512M                      |

|                     |               |                                                             | Amic                   |       | CLICA Bestler and  | 20 ans         | 1.00E+05                                         | 85               | ***                       |

|                     |               |                                                             | Catalyst semiconductor |       | CMOS floating gate | 10 ans         | 1.00E+05                                         | 105              | 1M - 2M                   |

|                     |               |                                                             | Elite Semiconductor    |       |                    | 20 ans         | 1.00E+05                                         | 85               |                           |

|                     |               |                                                             | Atmel                  |       |                    | 20 ans         | 1.00E+05                                         | 85               |                           |

|                     |               |                                                             | Intel                  | ?     |                    |                |                                                  |                  |                           |

|                     | parallèle     |                                                             | SST                    |       |                    | 100 ans        | 1.00E+05                                         | 85               | 64M                       |

|                     | série         | l I                                                         |                        |       |                    | 100 ans        | 1.00E+05                                         | 85               | 64M                       |

| légende température |               | < 95°C<br>95 à 110°C<br>125 à 135°C<br>150 à 175°C<br>250°C |                        |       |                    |                |                                                  |                  |                           |

Tableau III.2 : Classification des mémoires non-volatiles(2).

| Memory type         | Add. Function |             | Manufacturer                 | State       | Technology                         | Retention                   | Endurance | Temperature (°C) | Density (bit) |

|---------------------|---------------|-------------|------------------------------|-------------|------------------------------------|-----------------------------|-----------|------------------|---------------|

| RRAM (ReRAM)        |               |             | STMicroelectronics           | étude       |                                    |                             |           |                  |               |

| model (nerodel)     |               |             | Fujitsu                      | étude       |                                    |                             |           |                  |               |

|                     |               | ]           |                              |             | CMOS et ferroelectric process PZT  | 10 ans à 55°C               |           | 85               | 256k          |

|                     |               |             | Fujitsu                      |             |                                    | 10 ans à 55°C               |           | 85               | 256k          |

|                     | parallèle     |             |                              |             |                                    | 10 ans à 55°C               |           | 85               | 1M - 2M       |

|                     |               |             |                              |             |                                    | 45 ans                      | 1.00E+13  | 85               |               |

|                     |               |             |                              |             | 0.13um                             | 10 ans                      | 1.00E+15  | 85               | 4M            |

| FRAM (FeRAM)        |               | PC          | Ramtron                      |             | advanced feroelectric process      | 45 ans                      | 1.00E+13  | 85               | 256k          |

| FRAM (FERAM)        |               |             | Kameron                      |             | use PZT as feroeoectrical material |                             |           |                  |               |

|                     | série         | SPI         |                              |             | 0.13µm                             | 10 ans                      | 1.00E+15  | 85               | 1M            |

|                     | serie         |             |                              |             | 0.13µm                             | 10 ans                      | 1.00E+15  | 85               | 2M            |

|                     |               |             | Eudeu                        |             |                                    | 10 ans à 55°C               |           | 85               | 256k          |

|                     |               | J           | Fujitsu                      |             |                                    | 10 ans à 55°C               |           | 85               | 1M - 2M       |

|                     |               |             | Hynix                        | article     |                                    |                             |           |                  |               |

|                     |               |             | STMicroelectronics           |             | CMOS SRAM                          | 10 ans                      | infini    | 70               | 16k - 32M     |

|                     |               |             | Cypress                      |             | 0.8 - 0.25µm CMOS + quantum trap   | 20 ans à 55°C               | 2.00E+05  | 85               |               |

| NV SRAM             |               |             | Texas Instrument             |             | CMOS                               | 10 ou 5 ans                 | infini    | 85               | 64k - 16M     |

| NV SKAM             |               |             | Greenwich Instrument         |             | CMOS                               |                             |           | 70               |               |

|                     |               |             | Catalyst semiconductor       |             | CMOS floating gate 0.6um           | 10 ans                      | 1.00E+05  | 125              | 256           |

|                     | parallel      |             | Maxim                        |             | ?                                  | 5 ans with internal battery | infini    | 85               |               |

|                     | 1             |             | Honeywell                    |             | SOI 150 nm                         | 10 ans                      | 1.00E+16  | 125              | 1M            |

| MRAM                |               |             | Funnala                      | échantillon | 1T/1MTJ (magnetic tunnel jonction) | 20 ans                      | infini    | 125              | 1M - 4M       |

| MINAM               |               |             | Everspin                     |             | ?                                  | 20 ans                      | infini    | 105              | 1M - 4M       |

|                     |               |             | NVE                          | recherche?  |                                    |                             |           |                  |               |

| PCRAM (OUM)         | 1             |             | Qimonda                      | presse      | ?                                  |                             |           |                  |               |

|                     |               |             | BAE System                   |             | 0.25µm CMOS                        | 0.5 ans à 90°C              | 1.00E+06  | 110              | 2M - 4M       |

| CRAM                |               |             | Numonyx                      | recherche   |                                    |                             | 1.00E+08  |                  |               |

|                     | 1             |             | Honeywell                    |             | RICMOS SOI 0.8µm                   |                             |           | 125              | 36k           |

| FIFO                |               |             | Cypress                      |             | 0.5µm                              |                             |           | 125              | 256k          |

|                     |               |             | BAE System                   | ?           | •                                  |                             |           |                  |               |

|                     |               |             | Amic                         |             |                                    |                             |           | 85               |               |

|                     |               |             | Integrated Device Technology | ?           |                                    |                             |           |                  |               |

|                     | ]             |             | Numonyx                      |             |                                    |                             |           |                  |               |

|                     |               |             | Spansion                     |             |                                    |                             |           |                  |               |

|                     |               |             | Samsung                      |             |                                    |                             |           |                  |               |

| MCP                 |               |             | Micron                       |             |                                    |                             |           |                  |               |

|                     |               |             | SST                          |             |                                    | 100 ans                     | 100000    | 85               |               |

|                     |               |             | Toshiba                      |             |                                    |                             |           |                  |               |

|                     | •             |             |                              |             |                                    |                             |           |                  |               |

| légende température |               | < 95°C      | 1                            |             |                                    |                             |           |                  |               |

|                     |               | 95 à 110°C  | 1                            |             |                                    |                             |           |                  |               |

|                     |               | 125 à 135°C | 1                            |             |                                    |                             |           |                  |               |

|                     |               | 150 à 175°C | 1                            |             |                                    |                             |           |                  |               |

|                     |               | 250°C       | 1                            |             |                                    |                             |           |                  |               |

Tableau III.3 : Classification des mémoires non-volatiles(3).

| Memory type        | Add. Function | Manufacturer                     | state    | Technology          | Temperature (°C) | Density (bit)  |

|--------------------|---------------|----------------------------------|----------|---------------------|------------------|----------------|

|                    |               | Samsung                          |          |                     |                  |                |

|                    |               | Qimonda                          |          |                     | 95               |                |

|                    |               | Intel                            |          |                     |                  |                |

| DRAM               |               | NEC                              |          |                     | 85               |                |

|                    |               | Artic                            |          |                     |                  |                |

|                    |               | Elite semiconductor              |          |                     | 85               |                |

|                    |               | Samsung                          |          |                     | 85               |                |

|                    | synchrone     | 659                              |          |                     | 105              |                |

| PSRAM              |               | Micron                           |          |                     | 85               | 4M - 8M        |

|                    |               | Elite semiconductor              | ,        |                     |                  |                |

| REDRAM             |               | Micron                           | _        |                     | 95               | 288M - 576M    |

|                    | DOR DOR2 DOR3 | Hynix                            |          |                     | 95               |                |

| SDRAM              | DDR           | Micron                           |          |                     | 105              | 256M           |

|                    | DOR DORS DORS | Elpida                           |          |                     | 85               |                |

|                    |               | Sharp                            |          |                     |                  |                |

|                    |               |                                  | $\vdash$ | RICMOS IV SOI 0.7µm | 125              | 1M             |

|                    |               | Honeywell                        | $\vdash$ | RICMOS IV SOI 0.7µm | 125              | 1M             |

|                    |               |                                  |          | RICMOS V SOI 0.35µm | 125              | 4M             |

|                    |               |                                  |          | 150nm               | 125              | 16M            |

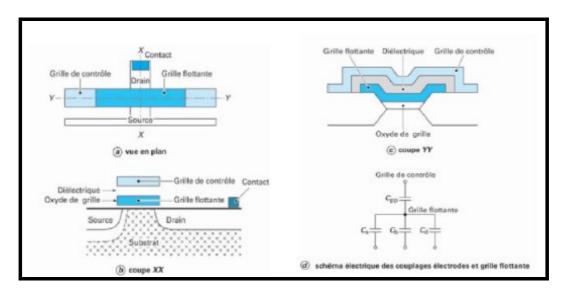

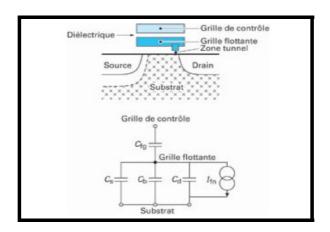

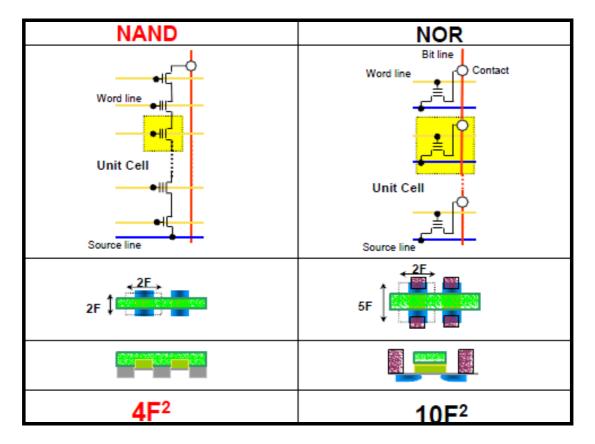

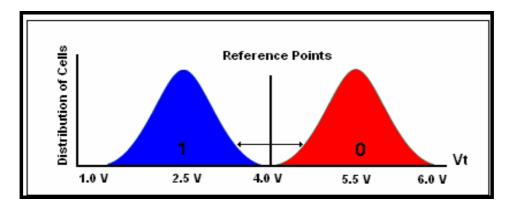

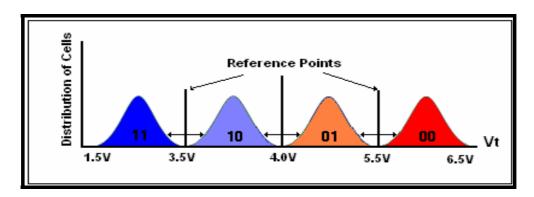

|                    |               | Cypress                          |          | 7                   | 85               |                |