## <u>République Algérienne Démocratique et Populaire</u> <u>Ministère de l'Enseignement Supérieur et de la Recherche Scientifique</u>

# Département d'Electronique

# Projet de Fin d'Etudes pour l'obtention du diplôme d'Ingénieur d'Etat en Electronique

Présenté par : BOUDJEMA Mohammed BELHAOUAS Nasreddine

#### Thème:

# Commande d'une poursuite du point de puissance maximum (MPPT) par les Réseaux de Neurones et implémentation sur FPGA et DSP

# Membres du jury:

M HADDADI Mourad Professeur Président

M AIT CHEIKH Mohamed Salah Chargé de Cours Rapporteur

M LARBES Chérif Maître de Conférence Examinateur

M<sup>me</sup> HAMMAMI Latifa Maître de Conférence Examinatrice

Juin 2007

ملخص:

يهدف هذا العمل إلى دراسة المبدأ الأساسي لطريقة تعقب نقطة الاستطاعة القصوى باستعمال الشبكات العصبية (MPPT-neuronale) الخاصة بالألواح الكهروضوئية حيث تم تحديد العوامل المؤثرة على هذه النقطة.

قامت برامج " MATLAB " و "SIMULINK" بتقنيد حسن أداء جهاز السيطرة و الذي سنقوم ببرمجته على الدارات المبرمجة FPGA باستعمال بطاقة التطوير "ميماك ديزاين " (Memec Design)

و على المعالج الرقمي للإشارة دي إس بي C6211 من فئة C6000.

كلمات مُفتاحيه : نقطة الاستطاعة القصوى, الدارات المبرمجة FPGA , لغة البرمجة VHDL , برنامج المعالج الرقمي للإشارة DSP , برنامج Composer Studio ، الكهرؤضوئي, الشبكات العصبية .

#### Résumé:

Ce travail s'intéresse à l'étude de la méthode de poursuite du point de puissance maximale par les réseaux de neurones (MPPT-neuronale) des générateurs photovoltaïques, qui a permis de déterminer les différents paramètres influençant le point de puissance maximale.

Des simulations effectuées sous MATLAB et "SIMULINK" confirment la bonne performance du contrôleur MPPT, qui sera implémenté sur le circuit FPGA en utilisant la carte de développement « Memec Design » et DSP TMS 320C6211de la famille C6000.

*Mots clés*: MPPT, Circuit FPGA, langage VHDL, DSP, Code Composer Studio, Photovoltaïque, réseaux de neurones.

#### Abstract:

This work is interested in the method of Power Point Maximum Tracking of neural network (neural MPPT) for photovoltaic generators, who allowed to determine the various parameters influencing on the maximum power point.

The simulations carried out under MATLAB and "SIMULINK" confirm the best performance of controller MPPT, and which will be implement on circuit FPGA by using the chart of development "Memec Design" and DSP TMS 320C6211 the C6000 family.

*Keywords*: MPPT, FPGA Circuit, VHDL Languge, DSP, Code Composer Studio, photovoltaic, neural network.

# Dédicace

I dedicate this work to

My mother and father

My brothers (Mohammed, Abdelhamid, Abdelkarim)

And to my family

Also, to

All my friends.

$\mathcal{N} \! E \! S \! R \! E \! D \! D \! I \! N \! E$

Je dédie ce travail à : Ma très chère mère, mon très cher père, Mes frères, Ainsi qu'à toute ma famille et mes amis.

$\mathcal{H}\mathcal{A}\mathcal{M}I\mathcal{D}O$

# Remerciements

Au terme de ce travail, nous tenons à présenter nos remerciements

- aux membres du jury, qui m'ont fait l'insigne honneur d'examiner ce travail.

- à mon encadreur, qui a sacrifié son temps pour m'accompagner dans l'aboutissement de ce sujet.

- Nous tenons à remercier également Monsieur LARBES Chérif, Madame HAMMAMI pour leur précieuse aide et leurs encouragements.

- A nos parents pour leur compréhension et pour ce qu'ils ont enduré pour nous offrir le bonheur et la confiance, nous disons notre gratitude.

- Nous ne saurons oublier de remercier toute les personnes qui, d'une manière ou d'une autre, nous ont aidés dans l'élaboration de ce travail.

# Table des matières

| In | ntroduction |                                                                         |    |  |  |

|----|-------------|-------------------------------------------------------------------------|----|--|--|

| 1  | Syst        | tème photovoltaïque                                                     | 5  |  |  |

|    | 1.1         | Introduction                                                            | 5  |  |  |

|    | 1.2         | L'effet photovoltaïque                                                  | 5  |  |  |

|    | 1.3         | La photopile                                                            | 6  |  |  |

|    | 1.4         | Caractéristiques de la cellule photovoltaïque                           | 6  |  |  |

|    | 1.5         | Influence de l'ensoleillement et de la température                      | 7  |  |  |

|    | 1.6         | Le module photovoltaïque                                                | 8  |  |  |

|    | 1.7         | Modèle mathématique d'un panneau photovoltaïque                         | Ö  |  |  |

|    | 1.8         | Contexte de l'étude sur les systèmes de conversion photovoltaïques (PV) | S  |  |  |

|    | 1.9         | Les systèmes photovoltaïques avec batterie                              | 10 |  |  |

|    | 1.10        | Le convertisseur DC-DC (les hacheurs)                                   | 11 |  |  |

|    |             | 1.10.1 Principe de fonctionnement du convertisseur Buck-Boost           | 12 |  |  |

|    |             | 1.10.2 Modèle mathématique équivalent                                   | 12 |  |  |

|    |             | 1.10.3 Les ondulations des courants et des tensions                     | 13 |  |  |

|    | 1.11        | Les batteries                                                           | 13 |  |  |

|    | 1.12        | Méthode de poursuite MPPT                                               | 15 |  |  |

|    |             | 1.12.1 Fonctionnement d'un générateur PV à sa puissance maximale        | 15 |  |  |

|    |             | 1.12.2 La réalisation                                                   | 16 |  |  |

| 2  | Rés         | eaux de neurones                                                        | 18 |  |  |

| _  | 2.1         | Introduction                                                            | 18 |  |  |

|    | 2.2         | Le modèle neurophysiologique                                            | 18 |  |  |

|    | 2.3         | Le modèle mathématique                                                  | 18 |  |  |

|    | 2.4         | Structure                                                               | 19 |  |  |

|    | 2.5         | Comportement                                                            | 19 |  |  |

|    |             | 2.5.1 fonction sigmoïde                                                 | 20 |  |  |

|    |             | 2.5.2 fonction binaire sigmoïde                                         | 20 |  |  |

|    |             | 2.5.3 fonction bipolaire sigmoïde                                       | 21 |  |  |

|    |             | 2.5.4 fonction arctangent                                               | 21 |  |  |

|    |             | 2.5.5 fonction gaussien                                                 | 22 |  |  |

|    | 2.6         | Structure d'interconnexion                                              | 22 |  |  |

|    | 2.7         |                                                                         |    |  |  |

|    |             | 2.7.1 Réseau multicouche (MLP)                                          | 23 |  |  |

|    | 2.8         | Apprentissage d'un réseau multicouche                                   | 23 |  |  |

|    |             | 2.8.1 Apprentissage supervisé                                           | 24 |  |  |

|    |             | 2.8.2 Apprentissage non supervisé                                       | 24 |  |  |

|   | 2.9  | Caracté   | ristique de l'algorithme d'apprentissage supervisé          | 24 |

|---|------|-----------|-------------------------------------------------------------|----|

|   |      | 2.9.1     | La méthode du gradient                                      | 24 |

|   |      |           |                                                             | 25 |

|   |      |           | Propagation                                                 | 25 |

|   |      |           | Rétropropagation                                            | 25 |

|   |      |           | Calcul du gradient                                          | 25 |

|   | 2.10 |           |                                                             | 26 |

|   |      |           |                                                             | 27 |

|   |      |           | ation du vecteur du paramètre de poids W                    | 27 |

|   |      |           | ${f tion \ et \ simulation}$                                | 27 |

|   |      |           |                                                             | 27 |

|   |      |           |                                                             | 29 |

|   |      |           |                                                             | 29 |

|   |      |           | Choix de la structure des réseaux de neurones pour les pro- |    |

|   |      |           | <u> </u>                                                    | 31 |

|   | 2 14 |           |                                                             | 32 |

|   | 2.11 | Concrus   |                                                             | 02 |

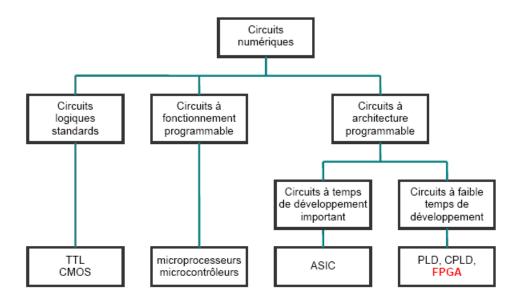

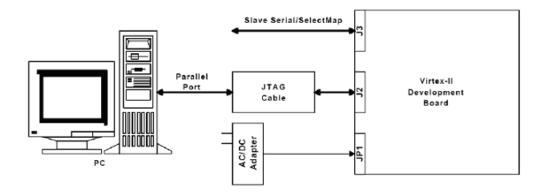

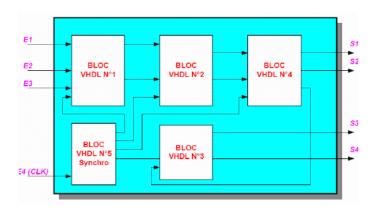

| 3 | Dév  | eloppem   | nent d'un projet sur FPGA                                   | 33 |

|   | 3.1  |           |                                                             | 33 |

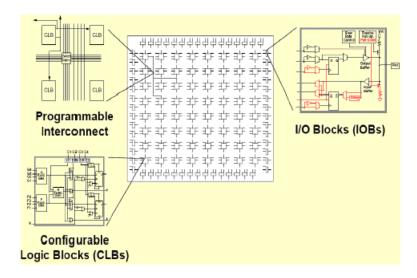

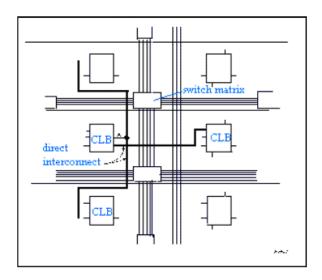

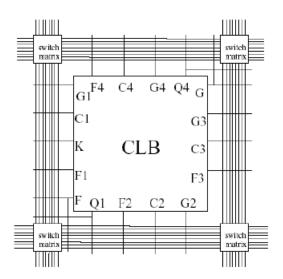

|   | 3.2  |           | FPGA                                                        | 33 |

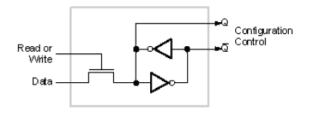

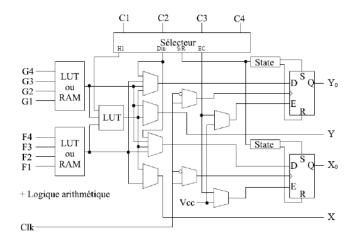

|   |      |           |                                                             | 34 |

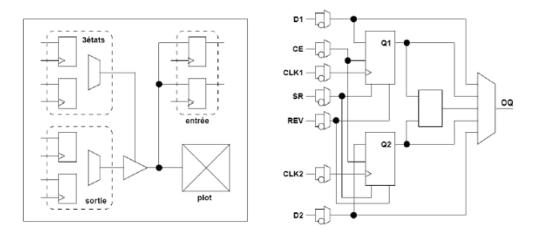

|   |      |           |                                                             | 36 |

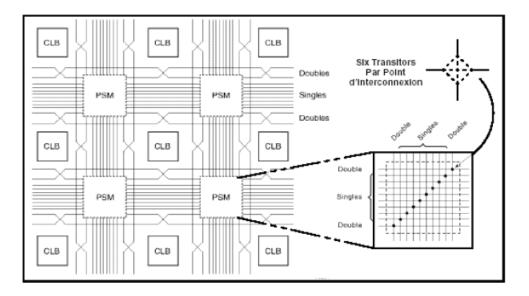

|   |      |           |                                                             | 37 |

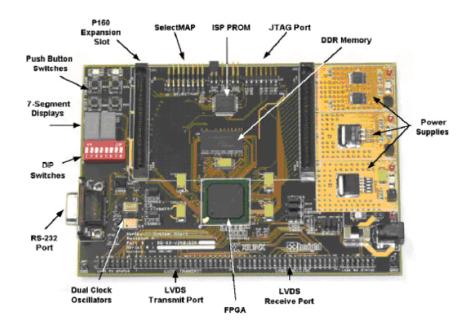

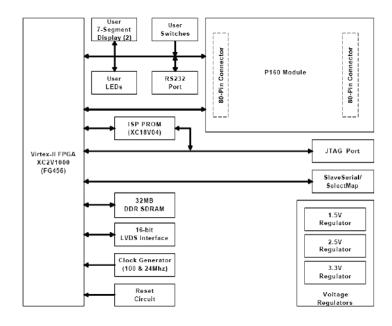

|   | 3.3  |           |                                                             | 39 |

|   | 0.0  |           | Description de la carte de développement                    | 39 |

|   |      |           |                                                             | 41 |

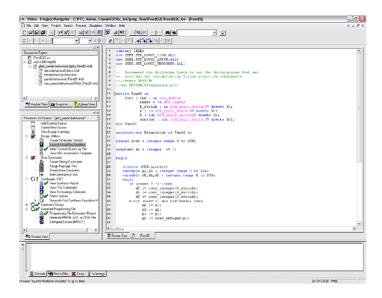

|   | 3.4  |           |                                                             | 42 |

|   | 3.5  |           | •                                                           | 43 |

|   | 0.0  |           | ·                                                           | 43 |

|   |      |           |                                                             | 43 |

|   |      |           |                                                             | 44 |

|   |      |           | Optimisantion ,placement et routage                         | 44 |

|   |      |           |                                                             | 44 |

|   |      | 0.0.0 I   | programation du composant et test                           |    |

| 4 | Dév  | eloppem   | nent d'un projet sur DSP                                    | 45 |

|   | 4.1  | Introduc  | e <mark>tion</mark>                                         | 45 |

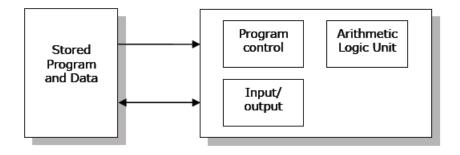

|   | 4.2  | Spécifici | tés architecturales                                         | 45 |

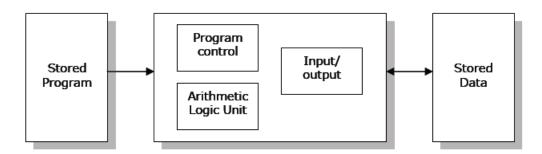

|   |      | 4.2.1     | Architecture de Von Neumann                                 | 45 |

|   |      | 4.2.2     | Architecture de Harvard                                     | 46 |

|   |      | 4.2.3     | Architecture d'un DSP                                       | 46 |

|   | 4.3  |           | tés de programmation                                        | 47 |

|   |      | -         | Spécificités de programmation                               | 47 |

|   |      |           | Pipeline                                                    | 47 |

|   | 4.4  |           | etique des DSP                                              | 48 |

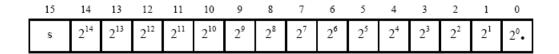

|   | _    |           | Arithmétique en virgule fixe (fixed point)                  | 49 |

|   |      |           | Arithmétique en virgule flottante (floating point)          | 49 |

|   | 4.5  |           | lle de DSP de Texas Instruments TMS320                      | 49 |

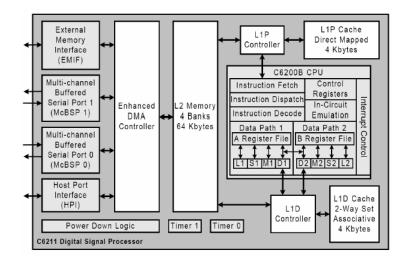

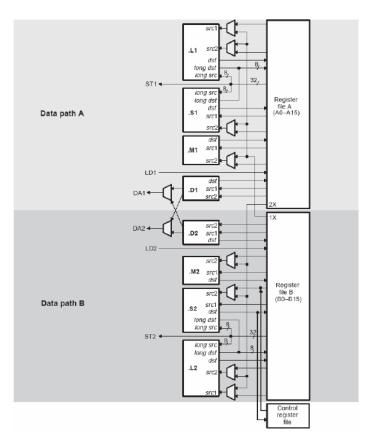

|   | 4.6  |           | eture du TMS320C6x                                          | 50 |

|   |      |           | onctionnelles                                               | 52 |

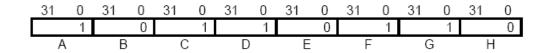

|   | 4.8  | Fetch  | et excute packets                                            | 5 |

|---|------|--------|--------------------------------------------------------------|---|

|   | 4.9  | Consid | leration mémoire                                             | 5 |

|   |      | 4.9.1  | Allocation de données                                        | 5 |

|   |      | 4.9.2  | Alignement de données                                        | 5 |

|   |      | 4.9.3  | Type de données                                              | 5 |

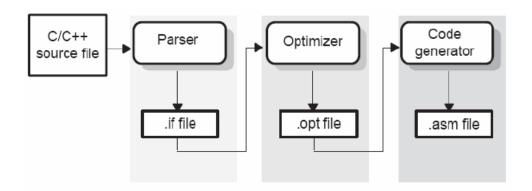

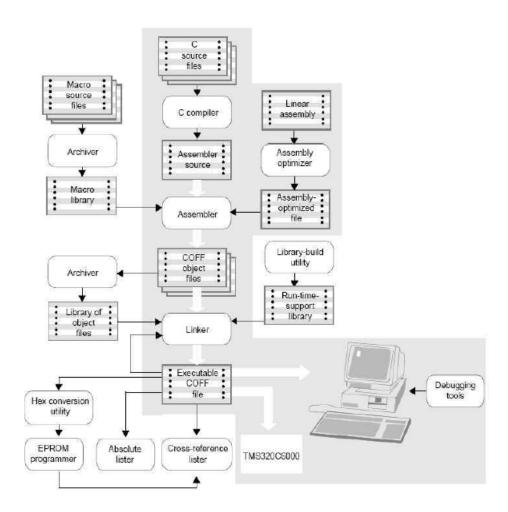

|   | 4.10 | Outils | de génération du code et de développement                    | 5 |

|   |      | 4.10.1 | Outils de développement logiciel                             | 5 |

|   |      | 4.10.2 | outils de déboggage software                                 | 5 |

|   | 4.11 |        | isaton du code                                               | 5 |

|   |      | 4.11.1 | Options du compilateur                                       | 5 |

|   |      | 4.11.2 | Fonction C « intrinsics »                                    | 5 |

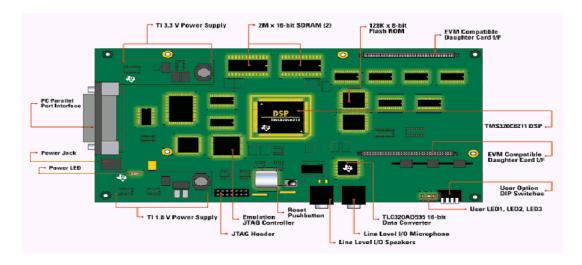

|   | 4.12 |        | d'évaluation DSK (DSP Starter Kit)                           | 5 |

|   | 4.13 | La car | te d'évaluation                                              | 5 |

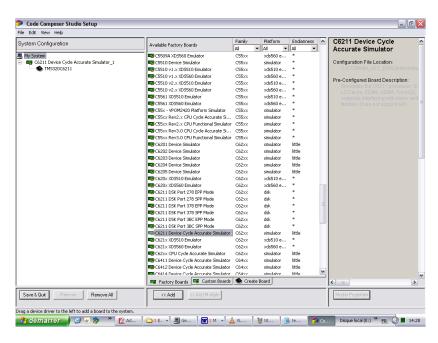

|   | 4.14 | Outils | d'émulation                                                  | 5 |

|   | 4.15 | Conclu | i <mark>sion</mark>                                          | 5 |

|   | ~.   |        |                                                              | _ |

| 5 |      |        | et évaluation des résultats                                  | 6 |

|   | 5.1  |        | uction                                                       |   |

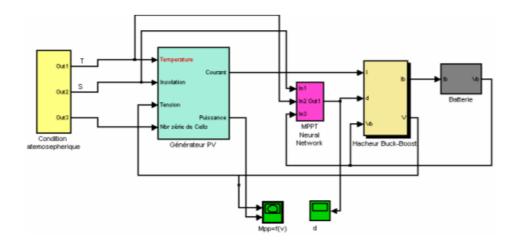

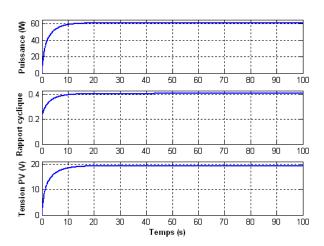

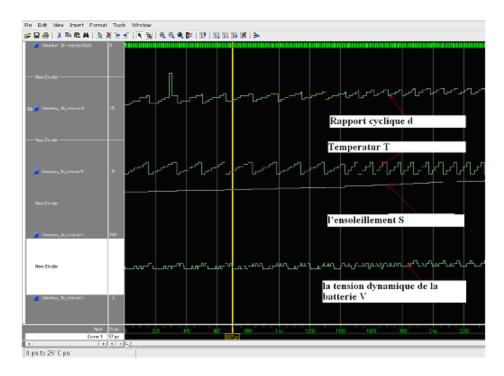

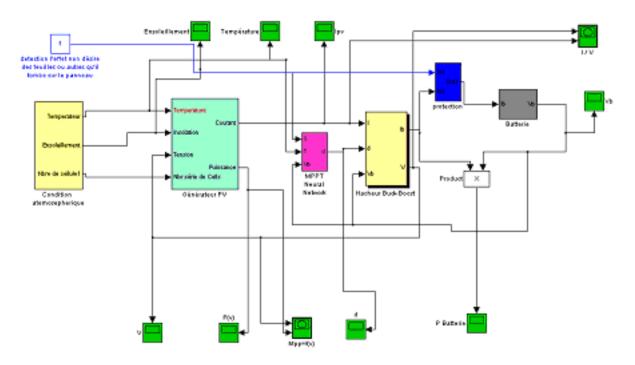

|   | 5.2  |        | tion sur SIMULINK                                            |   |

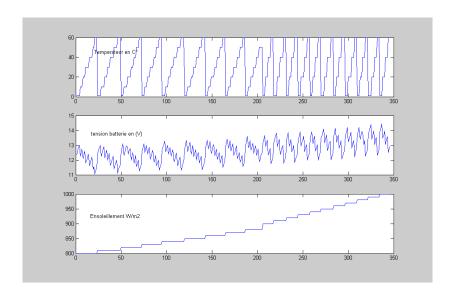

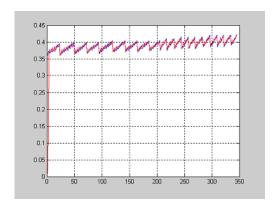

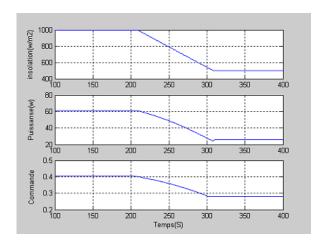

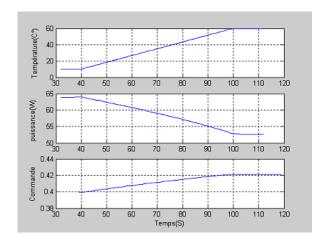

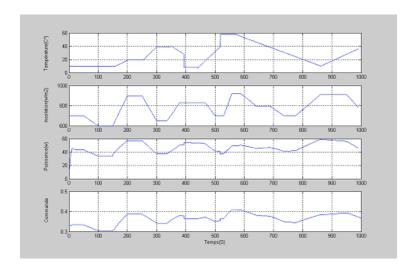

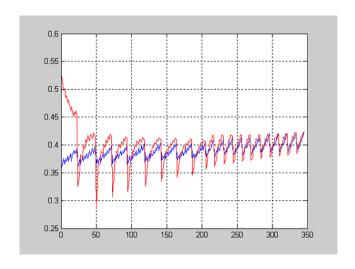

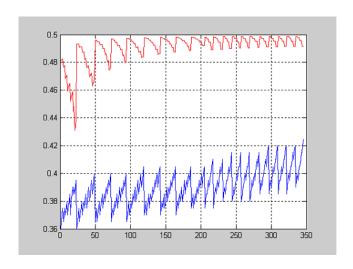

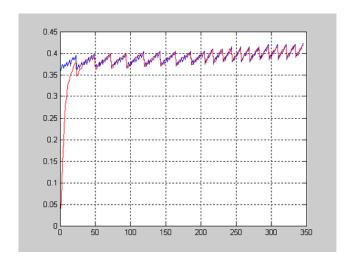

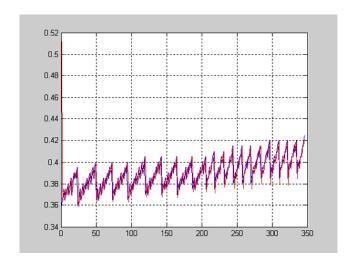

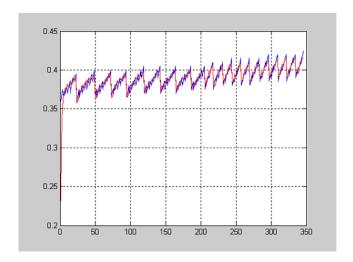

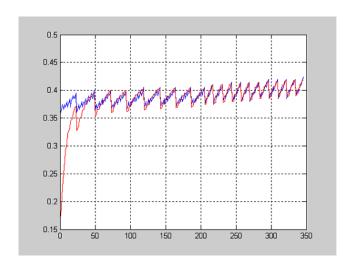

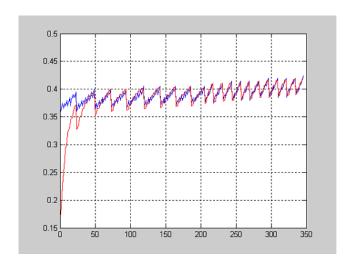

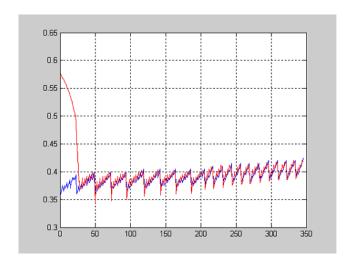

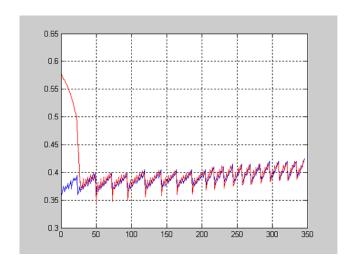

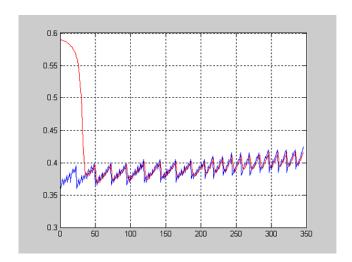

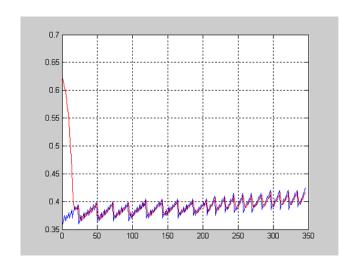

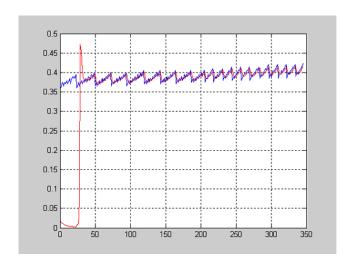

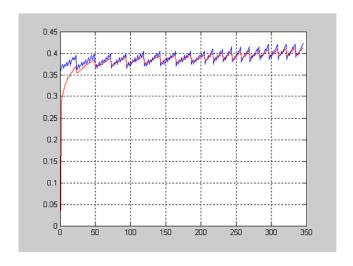

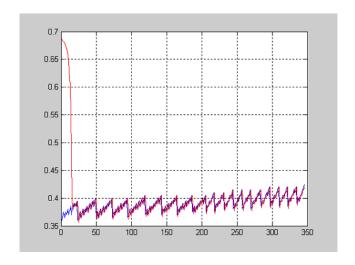

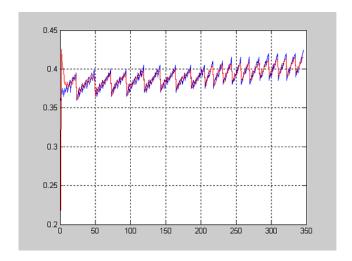

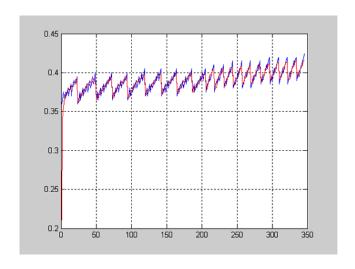

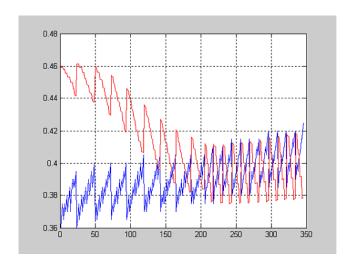

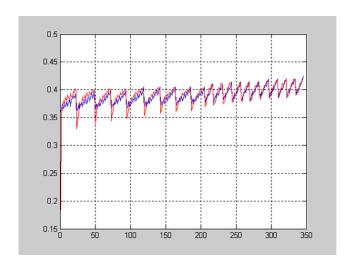

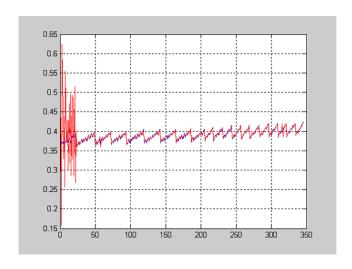

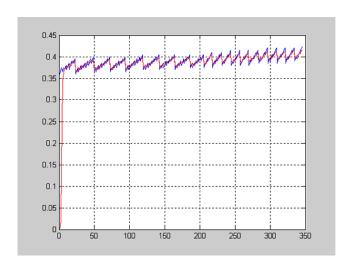

|   |      | 5.2.1  | Performances des commandes sous des conditions différentes . |   |

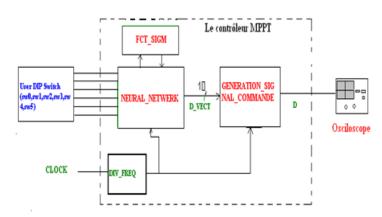

|   | 5.3  |        | ppement sur FPGA                                             | 6 |

|   |      | 5.3.1  | Introduction                                                 | 6 |

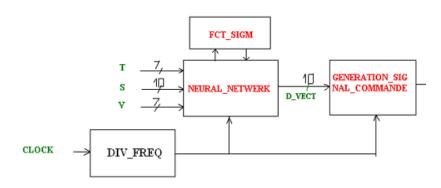

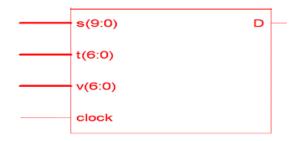

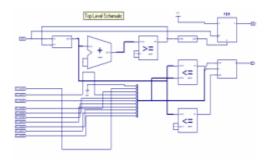

|   |      | 5.3.2  | Description des programmes écrits en VHDL                    | 6 |

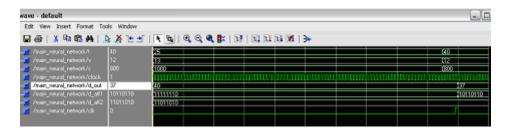

|   |      | 5.3.3  | Synthèse                                                     | 6 |

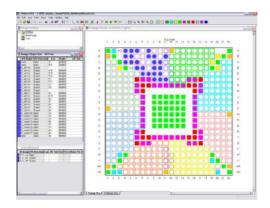

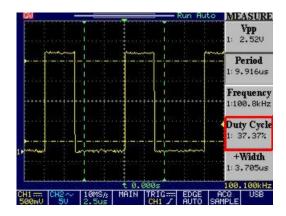

|   |      | 5.3.4  | Simulation                                                   | 6 |

|   |      | 5.3.5  | Environnement de test                                        | 6 |

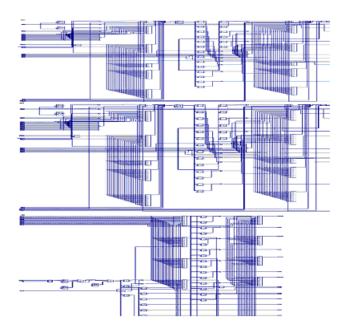

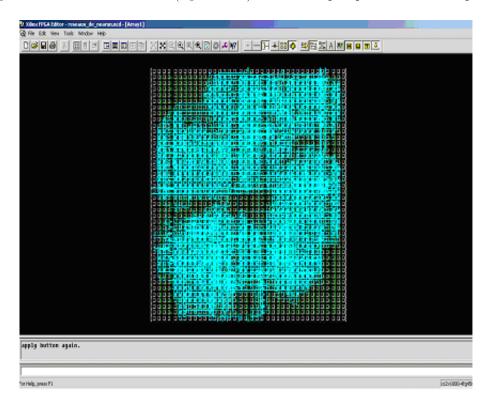

|   |      | 5.3.6  | Placement et routage du programme sur le circuit FPGA        | 6 |

|   |      | 5.3.7  | Conclusion                                                   | 7 |

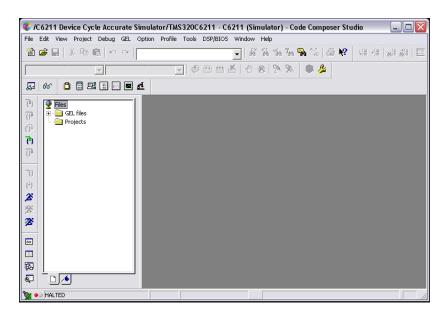

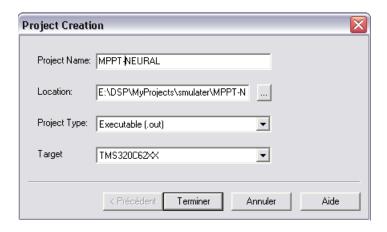

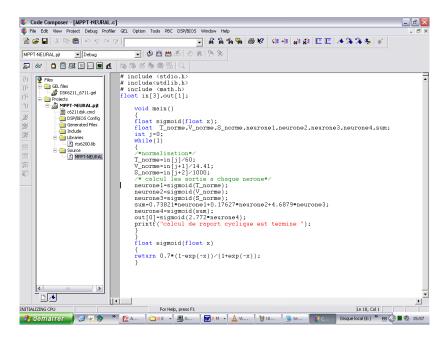

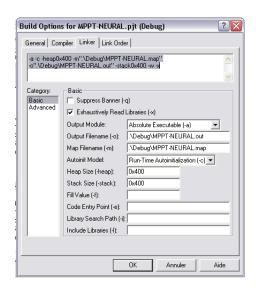

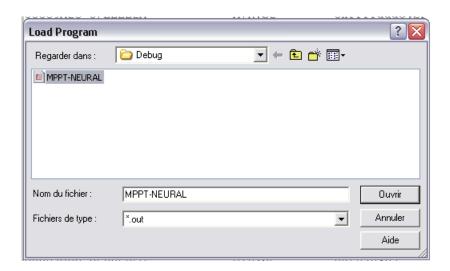

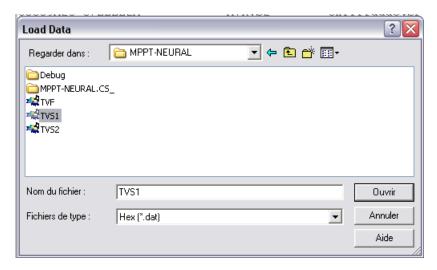

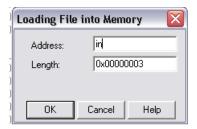

|   | 5.4  |        | ppement sur DSP                                              | 7 |

|   |      | 5.4.1  | Introduction                                                 | 7 |

|   |      | 5.4.2  | Outils de développement                                      | 7 |

|   |      | 5.4.3  | Données                                                      | 7 |

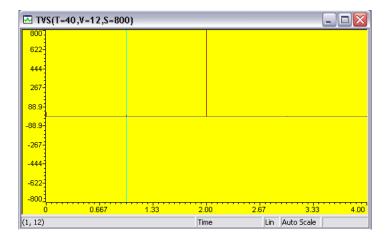

|   |      | 5.4.4  | La simulation                                                | 7 |

|   |      | 5.4.5  | Création de projet                                           | 7 |

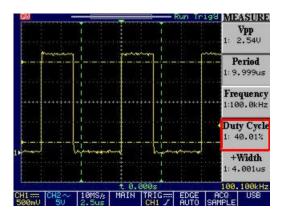

|   |      | 5.4.6  | Résultats obtenus                                            | 7 |

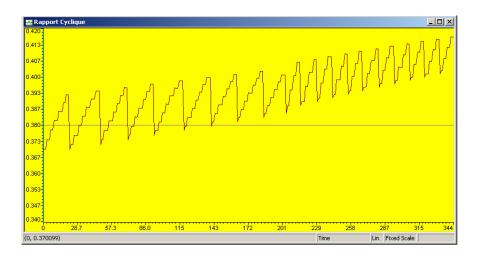

|   |      | 5.4.7  | Poursuite du point de puissance maximale                     | 7 |

|   |      | 5.4.8  | Conculsion                                                   | 8 |

| ~ |      |        | inórala                                                      | Q |

# Table des figures

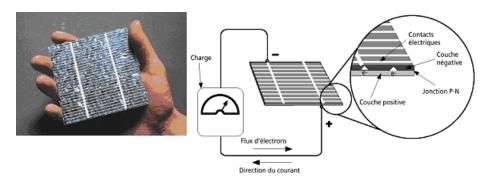

| 1.1  | Description d'une photopile ou cellule photovoltaique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

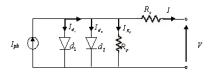

| 1.2  | Schéma du modèle équivalent à deux diodes d'une cellule photovoltaïque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6  |

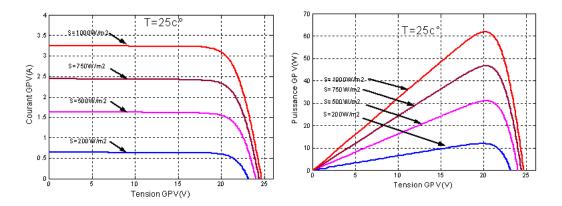

| 1.3  | Influence de l'ensoleillement sur les courbes I-V et PV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8  |

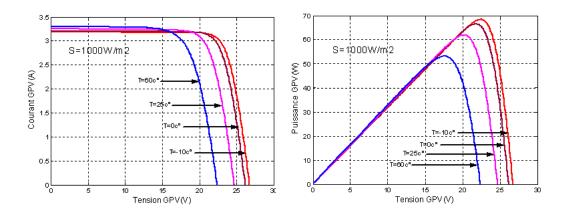

| 1.4  | Influence de la température sur les courbes I-V et PV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8  |

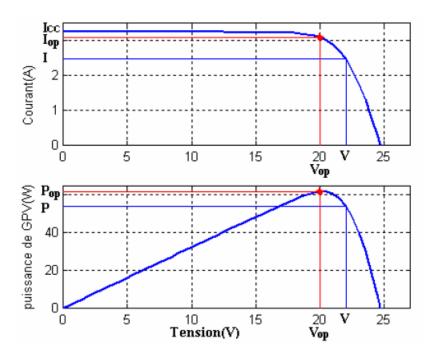

| 1.5  | Point de puissance maximale (PPM), puissance et courant correspon-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | dant à $V_{OP}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 |

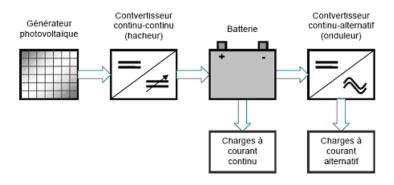

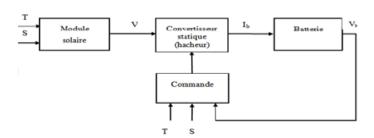

| 1.6  | Composantes de base d'un système PV autonome avec batterie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11 |

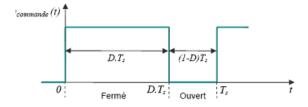

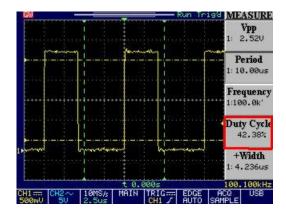

| 1.7  | Tension de commande (PWM) du commutateur durant une période                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | de commutation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11 |

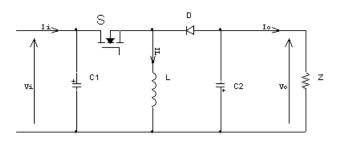

| 1.8  | Circuit électrique d'un convertisseur Buck-Boost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12 |

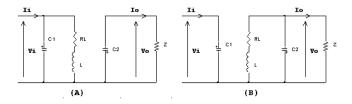

| 1.9  | Circuits équivalents de Buck-Boost, (A) :S fermer, (B) :S ouvert                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12 |

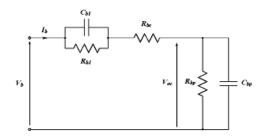

| 1.10 | Modèle équivalent de batterie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14 |

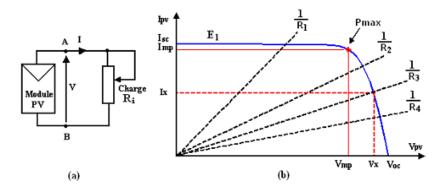

| 1.11 | (a) Connexion électrique directe entre un générateur PV et une charge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | (b) Points de fonctionnement résultant de l'association des généra-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|      | teurs PV sous un niveau d'éclairement E1 avec une charge résistive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | variable (R1, R2, R3, R4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16 |

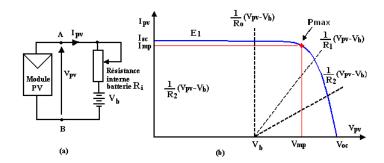

| 1.12 | (a) Connexion électrique directe entre un générateur PV et une batte-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | rie. (b) Points de fonctionnement résultant de l'association des géné-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | rateurs PV sous un niveau d'éclairement E1 avec une batterie comme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | charge ayant ou pas une résistance interne Ri Variable (R1, R2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

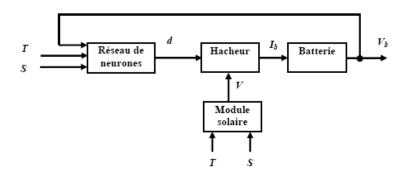

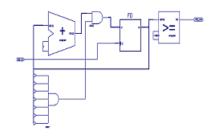

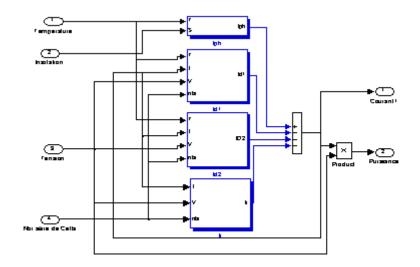

| 1.13 | Structure du système de commande                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17 |

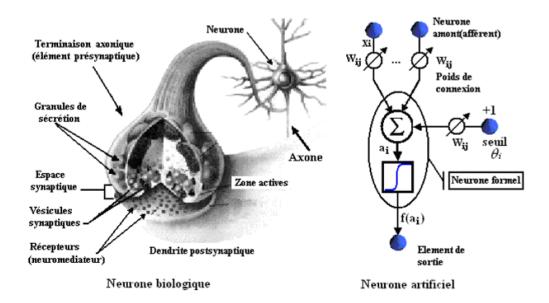

| 2.1  | mise en correspondance neurone biologique/neurone artificiel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19 |

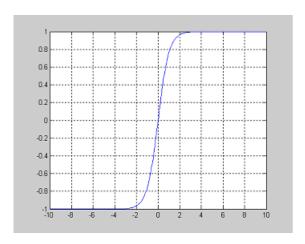

| 2.2  | sigmoïde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20 |

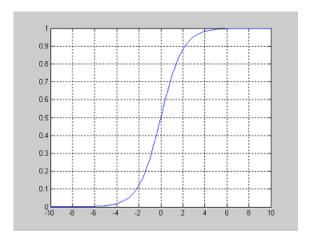

| 2.3  | binaire sigmoïde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21 |

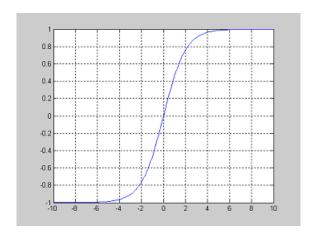

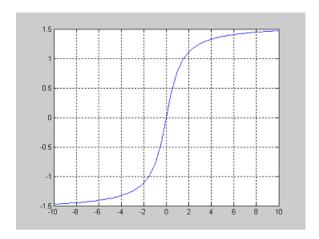

| 2.4  | bipolaire sigmoïde                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21 |

| 2.5  | arctangent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22 |

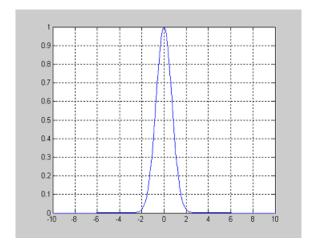

| 2.6  | gaussien                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22 |

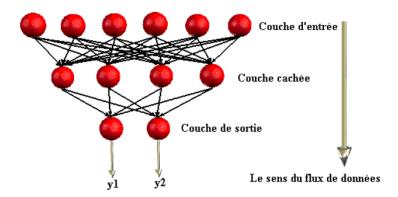

| 2.7  | Topologie d'un réseau multicouche (MLP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23 |

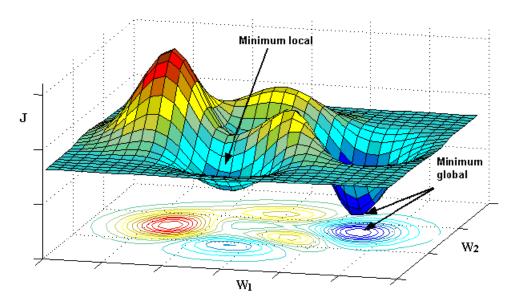

| 2.8  | Représentation de la fonction de coût J d'un neurone à deux entrées                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |