وزارة التعليم والسبحث العلمسي

MINISTERE DE L'ENSEIGNEMENT ET DE LA RECHERCHE SCIENTIFIQUE

2005

# ECOLE NATIONALE POLYTECHNIQUE

DEPARTEMENT ELECTRONIQUE

المدرسة الوطنية المتعددة التفنيات المكتبة - BIBLIOTHEQUE المكتبة - Essis Kationale Polytechnique

# PROJET DE FIN D'ETUDES

SUJET

Etude d'un lecteur rapide de mémoires dynamiques à MOS

Proposé par : Karakhanian

Etudié par : Teffahi.Hocine Mameri.Essaïd Dirigé par : Karakhanian

PROMOTION : JANVIER 86

المدرسة الوطنية المتددة التقنيات BIBLIOTHEQUE - المكتب Ecole Nationale Polytechnique

#### REMERCIEMENTS

Nos plus vifs remerciements vont particulierement à notre promoteur Monsieur : KARAKHANIAN pour ses précieux conseils qui nous ont été très bénifiques.

Que Monsieur : SAIDJ Ali, trouve ici le témoignage de nos reconnaissances, pour son amicale collaboration .

Que Monsieur : TEFFAHI Mohamed, trouve ici l'expression de nos remerciements pour avoir assuré le tirage de cette thèse .

Nous sommes reconnaissant à tous les professeurs du département d'électronique pour leur contribution à notre formation .

#### PLAN DE TRAVAIL

Introduction

المدرسة الوطنية المتعددة التقنيبات المحتبة — BIBLIOTHEQUE

Ecole Nationale Polytechnique

Chapitre I : Analyse d'un amplificateur de lecture élémentaire

- I- Généralités

- 2- Présentation de l'amplificateur de lecture

- 3- Control par une impulsion rectangulaire

- 4- Control par blocage d'un transistor

- 5- Control par un courant constant Conclusion

Chapitre II: Amélioration des caractéristiques de l'amplificateur de lecture

- I- Introduction

- 2- Recherche d'une fonction de commande

- 3- Attaque par deux niveaux de courants constants

- 4- Augmentation de la vitesse de fonctionnement

- 5- Application Conclusion

Chapitre III : Application de l'amplificateur de lecture dans les mémoires dynamiques à MOS

- I- Introduction

- 2- Différents types de RAM à MOS

- 3- Organisation d'une RAM dynamique à MOS

- 4- Structure interne de quelques éléments Conclusion

Chapitre IV : Vérification expérimentale

- I- Présentation du circuit intégré

- 2- Montage expérimental

- 3- Commande de l'amplificateur par mise à la masse de la source

- 4- Commande par un courant constant Conclusion

CONCLUSION

#### INTRODUCTION

leurs applications .

Les mémoires à semiconducteurs utilisent, comme les technologies des circuits intégrés, le silicium en tant que matériau de départ.

Elles constituent un domaine privilégié où les progrés de l'intégration poussée se font sentir immédiatement. Elles ont représenté les premières applications des circuits intégrés complexes (L.S.I: large scale integration, niveau de 1000 portes par circuit intégré), et constitueront encore des véhicules de choix pour la démonstration de la faisabilité des circuits intégrés très complexes (V.L.S.I: very large scale integration, niveau de 10000 portes par circuit intégré) et

De très nombreuses recherches menées sur les semiconducteurs, en général, ont permis de découvrir de nouveaux effets physiques permettant d'améliorer les caractéristiques des mémoires à semiconducteurs et l'obtention de performances elevées en vitesse par rapport aux solutions magnétiques, d'autant plus que ces performances (Temps d'accés lecture par exemple) s'améliorent en général lorsque le niveau d'intégration augmente (diminution des capacités parasites en diminuant les dimensions des composants).

C'est le cas des mémoires dynamiques à technologie MOS (métal, oxyde, semiconducteur) qui offrent de très grandes possibilités quant à l'augmentation du niveau d'intégration.

Dans les mémoires dynamiques, les informations sont stockées dans les capacités de structure des transistors MOS constituants les points mémoires.

A cause des inévitables courants de fuites, les charges de ces capacités diminuent avec le temps, ce qui nécessite l'opération de rafraîchissement, qui consiste en une lecture puis une réécriture de l'information.

Bien que les mémoires dynamiques à MOS offrent une solution élégante au problème d'augmentation de la capacité des mémoires, elles exigent des organes supplémentaires très délicats dont les caractéristiques sont les garants de la fiabilité du systeme entier.

Dans ce mémoire, on se propose d'étudier l'élément le plus déterminant qui n'est autre que l'amplificateur de lecture. L'information se présente à son entrée comme une légere chute (ou surplus) de tension, le rôle de cet élément est de l'amplifier et de la presenter en sortie pour pouvoir piloter un périphérique.

Des caractéristiques de cet amplificateur, tels que: Temps de lecture au niveau de l'amplificateur, pouvoir de conserver l'information (amplification), dependent esse-ntiellement toutes les performances de la mémoire.

Le but de ce travail est l'étude de l'amplificateur de lecture et la recherche d'un moyen permettant d'améliorer ses caractéristiques.

#### Chapitre I

# Analyse d'un amplificateur de lecture élèmentaire .

## I- Généralités

Un transistor MOS est constitué par un substrat ( N ou P ) dans le quel sont diffusées deux regions (P ou N ), appelées respectivement la source et le drain notées S et D.

Au dessus de l'espace drain-Source est deposée une mince couche d'oxyde de 0,I à 0,2 µm d'épaisseur environ, metalisée en surface avec de l'aluminium pour constituer le gate noté G, les autres régions non actives, sont couvertes d'une couche épaisse d'oxyde.

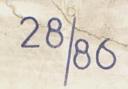

Le transistor MOS polarisé, présente 3 etats de fonctionnement : - si  $V_{65} < V_T$  ,on a  $I_0$  = 0 , d'où pas de canal, le transistor est bloqué .

- 51  $V_{GS} > V_T$  et  $V_{DS} < V_{GS} - V_T$ , on est dans la région triode, et le transistor fonctionne en régime non saturé .

- Si VGS > VT et VDS > VGS - VT ) le transistor fonctionne en régime saturé

Le courant s'exprime pour chaque cas comme suit :

transistor bloqué  $I_n = 0$

Transistor non saturé  $I_D = K (V_{GS} - V_T - \frac{V_{DS}}{2}) \cdot V_{DS}$ Transistor saturé  $I_D = K/2 (V_{GS} - V_T)^2$

La tension V<sub>T</sub>est appelée tension de seuil.

K est typique et constant pour un procedé techn $\phi$ logique donné il s'expr $\phi$ me en ( $A/V^2$ ) et est dit conductivité spécifique.

## Avantages du MOS

- I. Le MOS a une structure simple, de ce fait il occupe une surface moindre de silicuim .

- 2. Le MOS posséde des qualités inconnues des bipolaires qui lui permettent par exemple de fonctionner en dynamique.

- 3. Il consomme beaucoup moins que le bipolaire .

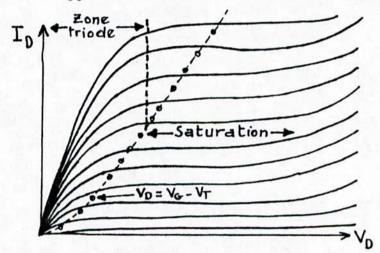

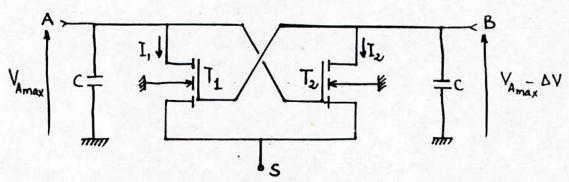

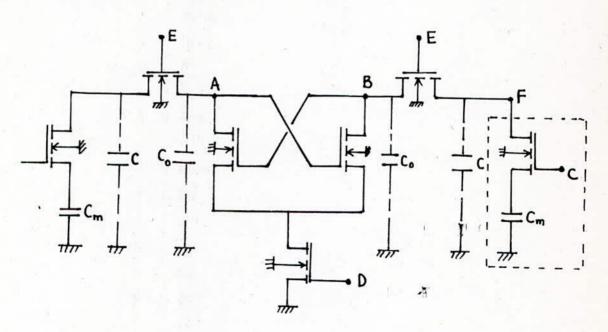

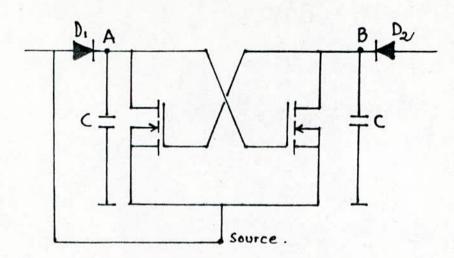

## 2- Présentation de l'amplificateur de lecture

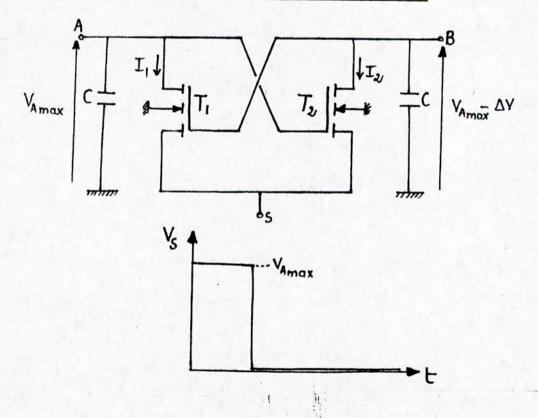

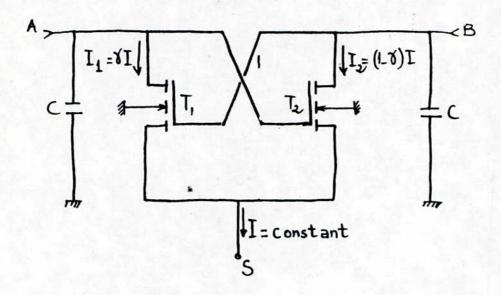

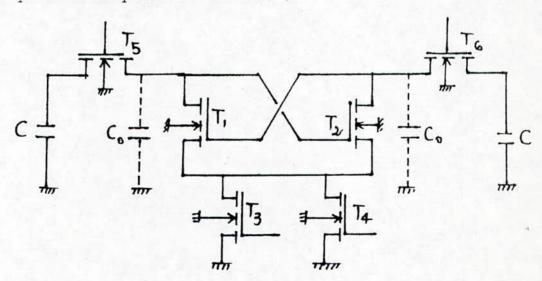

Le plus simple amplificateur de lecture qui existe est constitué par deux transistors MOS indentiques, montés en trigger, avec une contre réaction entre l'entrée et la sortie, comme l'indique la figure ci-dessous.

Les deux transistors T<sub>1</sub> et T<sub>2</sub> sont à canal N ( un transistor MOS à canal N occupe une surface d'intégration deux fois plus petite que celle d'un MOS à canal P ) , de tensions de seuil  $V_{\mathsf{T}}$  et de conductivité spécifique K .

Départ et d'autre des points A et B sont connectées deux reseaux indentiques de cellules mémoires ( constituées par un seul transistor MOS à canal N par cellule ).

Les deux capacités C, sont la somme de trois capacités:

- Capacité d'entrée de l'Amplificateur .

- Capacité parasite de la ligne de lecture .

- Capacité de la cellule mémoire selectionnée.

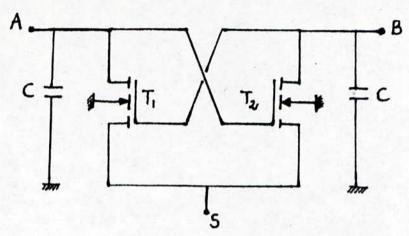

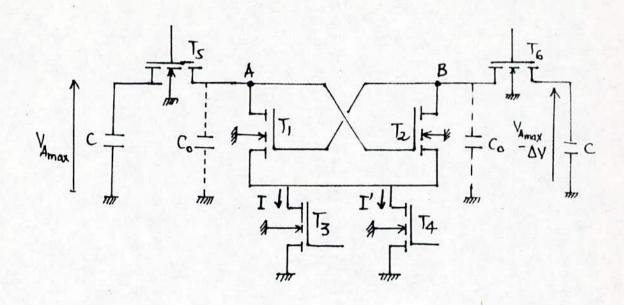

à l'instant initial, les deux points A et B sont à une tension de réference V<sub>Amax</sub> (grâce au signal de précharge).

V<sub>Amax</sub> est située à mi-chemin des deux niveaux logiques "I" ou "O" que peut contenir la cellule mémoire.

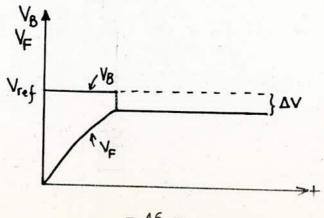

L'information à détecter apparait comme une légère chute (ou surplus) de tension  $\Delta V$ , en A ou en B, le rôle de ce montage est de détecter cette tension  $\Delta V$  et de l'amplifier pour y être lue.

dans le cas idéal, c'est à dire que toutes les mémoires à lire sont à transistors MOS rigoureusement identiques, on aura une vitesse de lecture infinie et une amplification maximum, mais en réalité, les mémoires à lire ne sont jamais identiques et l'information  $\Delta V$  à détecter peut varier d'une cellule à une autre.

Pour cela on analyse le comportement de l'amplificateur Vis à vis de cette variation et son effet sur le temps de lecture et l'Ampli-fication .

- On définit le temps de lecture comme le temps nécessaire pour que la différence des tensions en A et B atteigné la tension de seuil VŢ, c'est à dire la tension nécessaire pour déclencher un périphe--rique.

- On définit l'amplification, comme la tension maximum que peut atteindre la différence de tensions entre A et B

# 3- Control par une impulsion rectangulaire

On suppose qu'initialement, les tensions en A et B sont respecti-vement à  $V_{Amax}$  et  $V_{Amax}$  -  $\Delta$  V ( l'information à détecter est en B ).

à t = 0, le signal de control  $V_S$  est à  $V_{Amax}$ , ce qui bloque les

deux transistors  $T_1$  et  $T_2$ ; dés que  $V_S$  passe à zéro les deux

capacités C se déchargent à travers  $T_1$  et  $T_2$  en trois régimes de

fonctionnement suivant les tensions de polarisation des transistors :  $T_1$  et  $T_2$  saturés;  $T_1$  saturé et  $T_2$  non saturé et  $T_1$  Bloqué,  $T_2$  non

saturé .

En d'autre terme, dés que les deux décharges s'amorcent, on constate que le transistor T<sub>1</sub> a son gate porté à V<sub>Amax</sub>- ΔV alors que T<sub>2</sub> a son gate porté à V<sub>Amax</sub> et par conséquent est un tout petit peu plus conducteur que T<sub>1</sub> et dons a son courant de drain plus important, ce qui fait chuter encore plus vite la tension V<sub>B</sub>; cette dernière réduit encore plus la courant de T<sub>1</sub>, qui voit sa tension de drain diminuer certe, mais moins que sa symétrique V<sub>B</sub>; le processus cumulatif conduit fatalement au blocage de T<sub>1</sub>, alors que T<sub>2</sub> continue à conduire jusqu'à la compléte décharge de la capacité lui corres-pondant

## 3.I Formulation mathématique

Pour obtenir des resultats généralisés, on a normalisé les tensions par rapport à la tension de seuil  $V_T$ , et le temps par rapport à la constante  $\mathcal{T} = \mathbb{C}/\mathbb{K} \times V_T$  On note  $\overline{V} = \mathbb{V}/V_T$  et  $\overline{\mathsf{L}} = \mathsf{L}/\mathcal{T}$

Ier Régime : T<sub>1</sub> et T<sub>2</sub>, Saturés

En exprimant le courant dans une capacité, en fonction de la tension à ses bornes, on obtient le système d'equations differentielles suivant :

$$\frac{d\overline{V_A}}{d\overline{t}} = -\frac{1}{2} (V_B - 1)^2 (1)$$

$$\frac{d\overline{V_B}}{d\overline{t}} = -\frac{1}{2} (V_A - 1)^2 (2)$$

Ce qui donne :  $(V_A-I)^3 = (V_B-I)^3 + 3\overline{\Delta V}(\overline{V_{Amax}}-I)^2$

de plus cet état cesse lorsque  $\overline{V}_A - \overline{V}_B = I$  (instant  $\overline{t}_1$ ) avec ces deux hypothéses, on a pu tracer  $\overline{V}_A = f(\overline{V}_B)$  pour ce régime et cela nous a amené à poser l'approximation suivante :

$$\overline{V}_{A} = \propto \overline{V}_{8} + \beta$$

avec :

$$\alpha = \frac{\overline{V_{A_{max}}} - \overline{V_{B}}(\overline{t_{1}}) - 1}{\overline{V_{A_{max}}} - \overline{\Delta V} - \overline{V_{B}}(\overline{t_{1}})} \quad \text{et} \quad \beta = (1 - \alpha)\overline{V_{A_{max}}} + \alpha \overline{\Delta V}$$

$$\overline{V}_{B}(\overline{t}_{1}) = \frac{3 + \sqrt{36 \, \Delta V (\overline{V}_{Amax}^{2})^{2} - 3}}{6}$$

d'où Les expressions de VA(t) et VB(t):

$$\overline{V}_{B}(\bar{t}) = \frac{1}{\alpha} \left( \frac{1}{\frac{\alpha}{2} \bar{t} + \frac{1}{\alpha \bar{V}_{B max} + \beta - 1}} - \beta + 1 \right) ; \bar{V}_{A}(\bar{t}) = \alpha \bar{V}_{B}(\bar{t}) + \beta$$

L'état cesse à t=t, ou VA(t,)-VB(t,)=1

on trouve:

$$\overline{t}_1 = \frac{2}{\alpha} \left[ \frac{\alpha - 1}{\alpha (1 - \beta)} - \frac{1}{\alpha \overline{V_{B_{max}}} + \beta - 1} \right]$$

-2éme régime :  $T_1$  Saturé et  $T_2$  non saturé Pour ce régime, on a supposé, que la caractéristique  $I_{DS}$ =f ( $V_{DS}$ ) est linéaire, d'òù les équations différentielles suivantes :

$$\left\| \frac{d\overline{V_A}}{d\overline{t}} = -\frac{1}{2} \left( V_B - 1 \right)^2 \quad \text{conditions initiales} \\ \overline{V_B}(0) = \overline{V_B}(\overline{t_1}) \\ \frac{d\overline{V_B}}{d\overline{t}} = -\frac{1}{2} \overline{V_B}(\overline{t_1}) \overline{V_B} \quad \overline{V_A}(0) = \frac{1}{4} V_B(\overline{t_1})$$

Les solutions du systéme sont :

$$\overline{V}_{B}(\overline{t}) = \overline{V}_{B}(\overline{t}_{1}) \exp \left\{-\frac{\overline{V}_{B}(\overline{t}_{1})}{2}(\overline{t}_{1}-\overline{t}_{1})\right\}$$

$$\overline{V}_{A}(\overline{t}) = \frac{\overline{V}_{B}(\overline{t}_{1})}{2} \left[ \exp\left\{-\overline{V}_{B}(\overline{t}_{1})(\overline{t}_{-}\overline{t}_{1})\right\} - \frac{1}{2} - 2\left[\exp\left\{-\frac{\overline{V}_{B}(\overline{t}_{1})}{2}(\overline{t}_{-}\overline{t}_{1})\right\} - \frac{1}{2}\right] - \frac{1}{2}\left(\overline{t}_{-}\overline{t}_{1}\right) + \overline{V}_{A}(\overline{t}_{1})$$

Le second état cesse à  $\bar{t} = \bar{t}_2$  où  $\bar{v}_8$  ( $\bar{t}_2$ ) = 1 On trouve  $\bar{t}_2 = \bar{t}_1 + \frac{2}{\bar{V}_8(\bar{t}_1)} \text{Log}[\bar{V}_8(\bar{t}_1)]$

-3éme régime : T<sub>1</sub> Bloqué et T<sub>2</sub>, non saturé Les équations qui régissent cet etat sont :

$$\begin{vmatrix} \overline{V}_{A} &= \overline{V}_{0} &= \text{constante} \\ \frac{d\overline{V}_{B}}{d\overline{t}} &= -\frac{1}{2} \overline{V}_{B}(\overline{t}_{1}) \overline{V}_{B} & \text{d'ou } \overline{V}_{B} &= \exp\left\{-\frac{\overline{V}_{B}(\overline{t}_{2})}{2} (\overline{t} - \overline{t}_{2})\right\} \end{vmatrix}$$

Remarque: Pour  $\overline{\Delta V} = 0$ ; on a un seul régime (Saturé, Saturé)

On trouve

$$\overline{V}_{A} = \overline{V}_{B} = \frac{\overline{V}_{A \max} - 1}{\left(\overline{V}_{A \max}^{-1}\right)\overline{t} + 1}$$

## 3.2 Application:

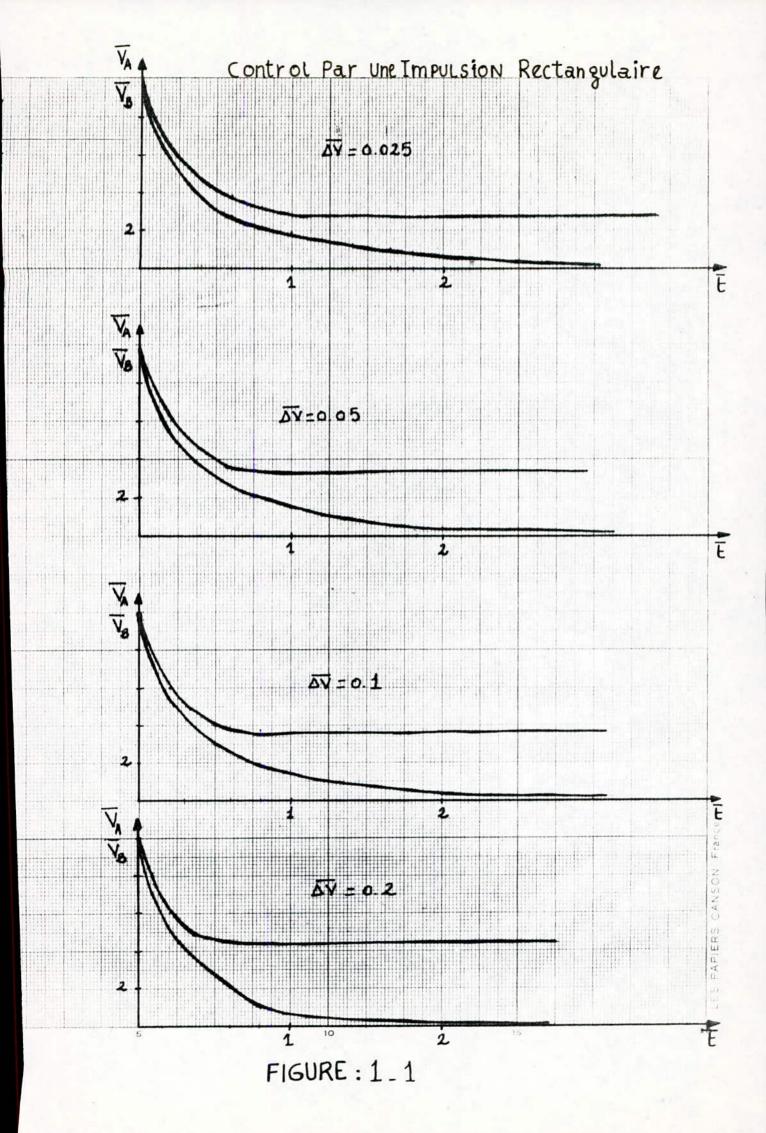

Pour illustrer ces resultats, on a tracé les courbes donnant  $\overline{V}_A$  et  $\overline{V}_B$  en fonction de  $\overline{t}$  ( Voir figure I - I )

de plus pour mieux comprendre les redultats obtenus, on a tracé  $\overline{V}_A = f(\overline{V}_B)$  et  $\overline{t}_{Lecture} = f(\overline{\Delta V})$  ainsi que  $\overline{\Delta V}_A = f(\overline{\Delta V})$  (Voir figure I-2)

$\overline{\Delta V_A}$  est la chute de tension au point A . On a pris  $\overline{V_{A_{max}}}$  = IO et  $\overline{\Delta V}$  = 0,025; 0,05; 0,1 et 0,2 .

## 3.3 Commentaires des resultats

d'Aprés la courbe  $\overline{\Delta V_A}$  = f ( $\overline{\Delta V}$ ), la tension au point A diminue d'une manière considérable, ce qui donne une amplification insuffisante, donc on peut conclure que ce type de fonction de commande ne convient pas pour ce montage.

Le tableau ci-dessous donne quelques valeurs de  $\overline{\Delta V_A}$  pour des tensions  $\overline{\Delta V}$  variables.

| VΔ  | 0,025 | 0,05 | 0,1 | 0,2 |

|-----|-------|------|-----|-----|

| ΔVA | 7,2   | 6,6  | : 6 | 5,6 |

- d'Aprés la courbe  $\overline{t}$  (lecture) =  $f(\overline{\Delta V})$ Le temps de lecture diminue, quand  $\Delta V$  augmente et d'une façon linéaire, mais cette diminution n'est pas assez importante et on

| ΔV         | 0,025 | 0,05 | ! 0,1  | 0,2  |

|------------|-------|------|--------|------|

| t(lecture) | 0,875 | 0,75 | 10,625 | 0,45 |

peut supposer que ce temps est constant

FIGURE: 1\_2

On voit que  $si \overline{\Delta V}$  augmente huit fois, le temps de lecture diminue seulement de deux fois, ce qui laisse `supposer que ce temps est constant.

Mais pour la raison sus-indiquée, on conclut que ce type de fonction de commande n'est pas convenable pour l'Amlificateur de lecture.

## 4- Contret par blocage d'un transistor

On a vu dans ce qui a précedé, que la tension au point A chute d'une manière considérable lorsque la tension à détecter augmente et cela constitue un inconvenient pour l'amplificateur de lecture, pour palier à cet inconvenient, on propose une solution qui consiste à trouver une fonction de commande qui garde le transistor  $T_1$  toujours bloqué ( ce qui assure une chute de tension au point A nulle ) et qui permet de débloquer le transistor  $T_2$ .

# 4-1 Formulation mathématique

Pour bloquer un transistor MOS, il suffit de garder 3a tension gate-source toujours infèrieure ou egale à sa tension de seuil  $V_T$ ; ce qui revient à imposer au transistor  $T_1$  de l'amplificateur de lecture une tension  $V_8$  -  $V_5$  =  $V_T$

<u>ler régime</u> : régime saturé

$$\frac{\overline{d\overline{V}_B}}{\overline{d\overline{t}}} = -\frac{1}{2} \left( \overline{V}_{Amey} - \overline{V}_S - 1 \right)^2 = \frac{\overline{dV}_S}{\overline{d\overline{t}}}$$

et  $\overline{V}_B = \overline{V}_S + 1$  (1)

On trouve:

$$\overline{V}_{S} = \overline{V}_{A \, max} 1 - \frac{\Delta \overline{V}}{-\frac{1}{2} \, \Delta \overline{V} \, \overline{L} + 1}$$

$$\overline{V}_{B} = \overline{V}_{A \, max} - \frac{\Delta \overline{V}}{-\frac{1}{2} \, \Delta \overline{V} \, \overline{L} + 1} \qquad \text{et} \qquad \overline{V}_{A} = \overline{V}_{A \, max} = \text{cste}$$

Cet état cesse à  $\overline{t} = \overline{t_1}$  où  $\overline{v_A} - \overline{v_B} = 1$ On trouve:

$$\bar{\xi}_1 = 2 \frac{1 - \overline{\Delta V}}{\overline{\Delta V}}$$

2 éme régime : régime non saturé

de l'expression donnant le courant de drain en fonction des tensions drain-Source et gate-Source et avec la condition (I)

On trouve:

$$\frac{d\overline{V_S}}{d\overline{t}} = -\left(\overline{V}_{A_{max}} - \overline{V}_S - \frac{3}{2}\right)$$

On trouve:

$$\overline{V}_{S} = (\overline{V}_{Amax} - \frac{3}{2}) - \frac{1}{2} e^{(\overline{t} - \overline{t}_{1})}$$

$$\overline{V}_{B} = (\overline{V}_{Amax} - \frac{1}{2}) - \frac{1}{2} e^{(\overline{t} - \overline{t}_{1})}$$

et  $\overline{V}_{A} = \overline{V}_{Amax} = cste$

Cet état césse à  $\overline{t} = \overline{t_2}$  où  $\overline{V_g}(\overline{t_2}) = I$  c'est à dire  $\overline{V_S} = 0$  On trouve:

3 'eme r'egime: non saturé avec  $\overline{V_5} = 0$

on a

$$\frac{d\overline{V}_B}{d\overline{t}} = -(\overline{V}_{Amox}^{-1} - \frac{\overline{V}_B}{2})\overline{V}_B \quad \text{avec} \quad \overline{V}_B(\overline{t}_2) = 1$$

On trouve

$$\overline{V}_{B}(\overline{t}) = \frac{\overline{V}_{A max} - 1}{(\overline{V}_{A max} - 3/2) e \times p \left[ (\overline{V}_{A max} - 1) (\overline{t} - \overline{t}_{2}) \right] + 1/2}$$

$$\overline{V}_{S} = 0$$

$$e t \qquad \overline{V}_{A} = \overline{V}_{A max} = cste$$

#### 4.2 Application.

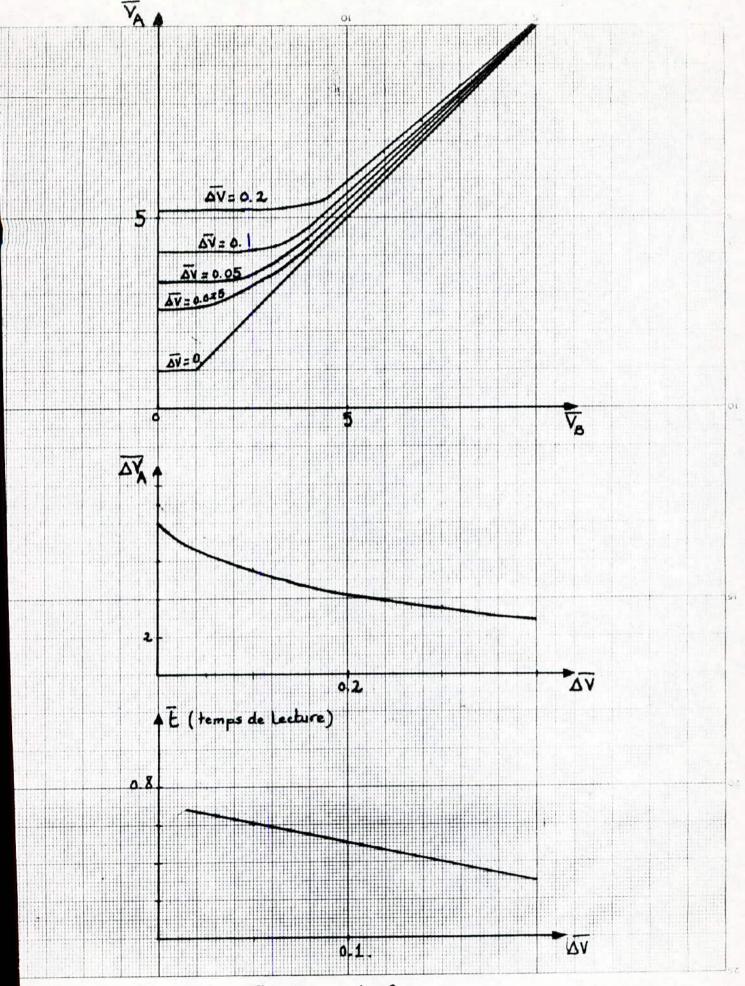

Pour illustrer les expressions théoriques obtenues, on à tracé les tensions  $\overline{V}_A$  et  $\overline{V}_B$  en fonction de  $\overline{t}$  (voir figure 2-I) Pour conclure, on a tracé la courbe donnant l'évolution du temps de lecture en fonction de  $\overline{A}\overline{V}$  (voir figure 2-2) on a pris  $\overline{V}_A$  max =IO et  $\overline{A}\overline{V}$  = 0,0I; 0,I; 0,2

Figure: 2-1 Control Par Blocage D'un transistor

#### 4-3 Commentaires:

La foction de commande trouvée permet bien d'avoir une amplification idéale, mais malheureusement, un un inconvenient important apparait: le temps de lecture n'est plus constant, mais il est inversement proportionnel à la tension ΔV presente initialement à l'entrée de l'amplificateur

| ΔV          | 0,025 | 0,05 | 0,1 | 0,2 |

|-------------|-------|------|-----|-----|

| t ( lecture | 78    | 38 ! | 18  | 8   |

$$\bar{t} = 2 \left( \frac{1 - \overline{\Delta V}}{\overline{\Delta V}} \right)$$

Les deux transistors ne peuvent jamais être exactement identiques cela est dûe à la dispertion des paramétres électriques et la variation des paramétres intrinséques de chaque transistors, conc les tensions à détecter peuvent être différentes pour un groupe d'amplificateurs exsitants dans le circuit intégré, ce qui fait que si on commande l'amplificateur de lecture par un signal de ce type, toutes les informations ne peuvent pas être lues convenablement

- Ce résultat pouvait être déduit physiquement, car si on élimine la contre- réaction par blocage d'un transistor on obtient un temps de lecture variable pour des tensions à detecter variables.

# 5 - Control par un courant constant

Dans ce qui a précédé, on a vu qu'il existe un compromis entre le temps de lecture et l'amplification et que l'élimination de la contre-réaction entraine des variations du temps de lecture dans de trop larges proportions.

Pour assurer une contre-réaction positive, on propose de commander le montage par un courant constant, car la diminution du courant du transistor T<sub>1</sub>, induit automatiquement l'augmentation du courant dans le transistor T<sub>2</sub> afin de garder un courant total constant, ce qui permet de précipiter la décharge de la capacité reliée au noeud B et de freiner la décharge de la capacité reliée au noeud A.

#### 5.I Formulation mathématique

Les régimes de fonctionnement sont identiques aux deux cas préce--dents, mais pour ce cas on a une condition supplémentaire :

Pour obtenir des resultats genéralisés, on a normalisé les tensions, le courant et le temps.

en note

$$\overline{V} = \frac{V}{V_T}$$

;  $\overline{t} = \frac{t}{C/KV_T}$  et  $\overline{I} = \frac{I}{KV_T^2}$

<u>Ier régime</u>: T<sub>1</sub> et T<sub>2</sub> Saturés Les équations différentielles régissent le fonctionnement du système sont les suivantes :-

$$\begin{vmatrix} \frac{d\overline{V_A}}{d\overline{t}} = -\frac{1}{2} \left( \overline{V_{BS}} - 1 \right)^2 & \text{conditions initiales} \\ \frac{d\overline{V_B}}{d\overline{t}} = -\frac{1}{2} \left( \overline{V_{AS}} - 1 \right)^2 & \text{(2)} \\ \frac{d\overline{V_B}}{d\overline{t}} = -\frac{1}{2} \left( \overline{V_{AS}} - 1 \right)^2 & \text{(2)} \\ \frac{d\overline{V_A}}{d\overline{t}} + \frac{d\overline{V_B}}{d\overline{t}} = -\overline{I} & \text{(3)} \end{vmatrix}$$

Pour résoudre ce système, on pose  $\overline{V_A} - \overline{V_B} = f(\overline{t})$  avec  $f(0) = \overline{\Delta V}$  avec cette condition, (I) et (2) on trouve

$$\bar{V}_{BS} = \frac{1}{f} \frac{df}{dt} - \frac{f}{2} + 1$$

;  $\bar{V}_{AS} = \frac{1}{f} \frac{df}{dt} + \frac{f}{2} + 1$

On substitue ces deux expressions dans (3); on obtient l'équation différentielle suivante :

$$\left(\frac{1}{f} \frac{df}{dt}\right)^2 + \left(\frac{f}{2}\right)^2 = \bar{I}$$

La solution de cette équation est .

$$f(\bar{t}) = \frac{4\alpha\sqrt{\bar{t}}}{\alpha^2} e^{-2\sqrt{\bar{t}}} \bar{t}$$

avec  $\alpha = \frac{2\sqrt{\bar{t}}}{\Delta \bar{V}} + \sqrt{\frac{4\bar{t}}{\Delta \bar{V}^2}} - 1$

$$\overline{V}_{A}(\overline{t}) = -\frac{1}{2}\overline{I}\overline{t} + \frac{1}{2}f(\overline{t}) - \frac{1}{2}\overline{\Delta V} + \overline{V}_{Amax}$$

$$\overline{V}_{B}(\overline{t}) = -\frac{1}{2}\overline{I}(\overline{t}) - \frac{1}{2}f(\overline{t}) - \frac{1}{2}\overline{\Delta V} + \overline{V}_{Amax}$$

Le premier état césse à  $\overline{t} = \overline{t_1}$ , où  $\overline{V_A}(\overline{t_2}) - \overline{V_B}(\overline{t_2}) = 1$ On trouve:

$$\bar{t}_1 = -\frac{1}{\sqrt{\bar{t}}} \log \left[ \frac{2\sqrt{\bar{t}} + \sqrt{4\bar{t} - 1}}{\alpha} \right]$$

2 éme etat :  $T_1$  Saturé et  $T_2$  non saturé Pour ce cas, on suppose que la caractéristique  $I_{DS} = f(V_{DS})$  est linéaire pour le régime non saturé . d'Ou les équations différentielles suivantes

$$\begin{vmatrix} \frac{d\overline{V_A}}{d\overline{t}} = -\frac{1}{2} (\overline{V_{RS}} - 1)^2 & \text{(4)} \\ \frac{d\overline{V_B}}{d\overline{t}} = -\frac{1}{2} \overline{V_{BS}}(\overline{t},) & \overline{V_{BS}}(5) & \overline{V_{A}}(0) = \overline{V_{A}}(\overline{t},) = 1 + \overline{V_{B}}(\overline{t},) \\ \frac{d\overline{V_{A}}}{d\overline{t}} = -\frac{1}{2} \overline{V_{BS}}(\overline{t},) & \overline{V_{BS}}(5) & \overline{V_{BS}}(0) = \overline{V_{B}}(\overline{t},) \\ \frac{d\overline{V_{A}}}{d\overline{t}} + \frac{d\overline{V_{B}}}{d\overline{t}} = -\overline{I} & \text{(6)} & \overline{V_{AS}}(\overline{t},) = \text{cste} \end{vmatrix}$$

On substitue (4) et (5) dans (6) on obtient

$$\overline{V}_{BS} = \frac{2 + \overline{V}_{BS}(\overline{t}_1) + \sqrt{(2 - \overline{V}_{BS}(\overline{t}_1))^2 + 8\overline{1} - 4}}{2} = 7 = cste$$

d'où

$$\overline{V}_{A}(\overline{t}) = -\frac{1}{2} (\nabla_{-1})^{2} (\overline{t} - \overline{t}_{1}) + \overline{V}_{A}(\overline{t}_{1})$$

$$\overline{V}_{B}(\overline{t}) = -\frac{1}{2} \overline{V}_{BS}(\overline{t}_{1}) \cdot \nabla_{\cdot} (\overline{t} - \overline{t}_{1}) + \overline{V}_{B}(\overline{t}_{1})$$

Cet état césse à  $\overline{t} = \overline{t_2}$  où  $\overline{V_R}(\overline{t_2}) = 1$ ; on trouve

$$\overline{t}_2 = \overline{t}_1 + \frac{2(\overline{V}_B(\overline{t}_1) - 1)}{\sqrt{\overline{V}_{BS}(\overline{t}_1)}}$$

; on note  $\overline{V}_A(\overline{t}_2) = \overline{V}_0$ .

$$\frac{3\text{\'eme \'etat}}{\text{Pour ce cas on a } \overline{V}_{A}} = \overline{V}_{O} \quad \text{et } \frac{d\overline{V}_{B}}{d\overline{t}} = -\overline{I}$$

## 5.2 Application

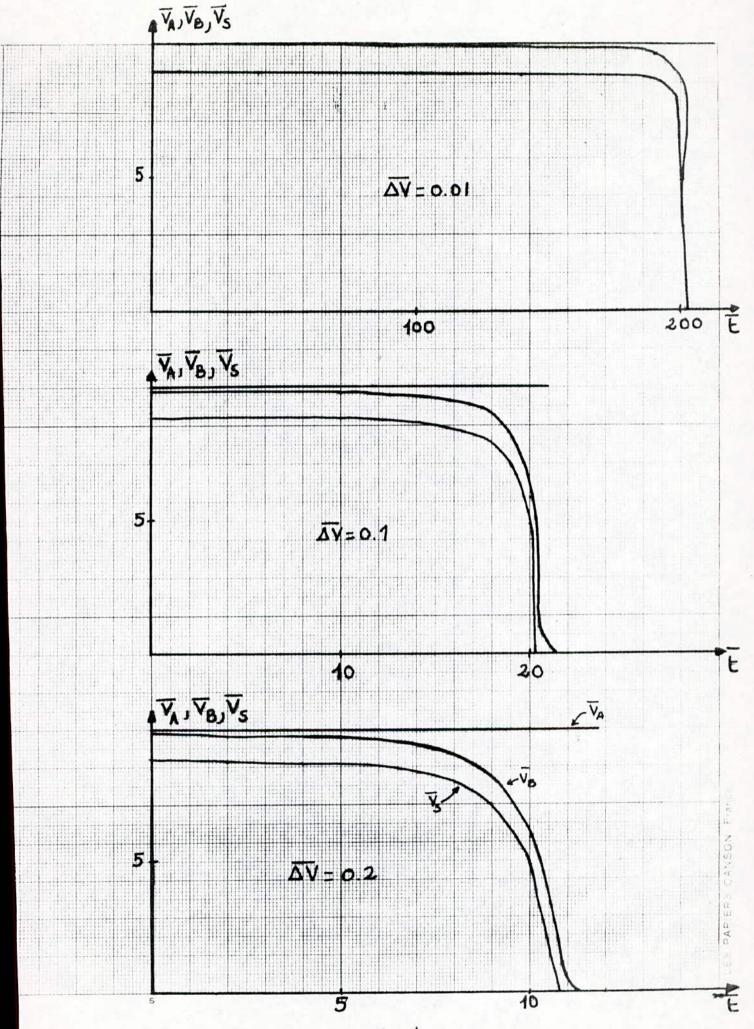

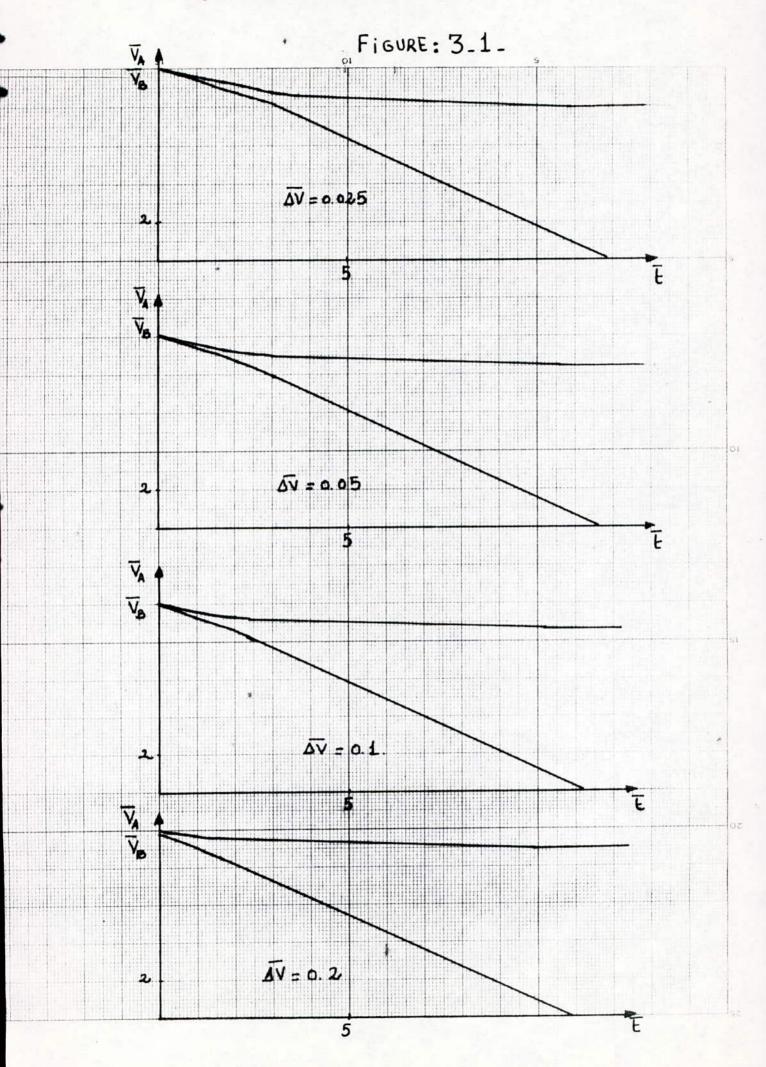

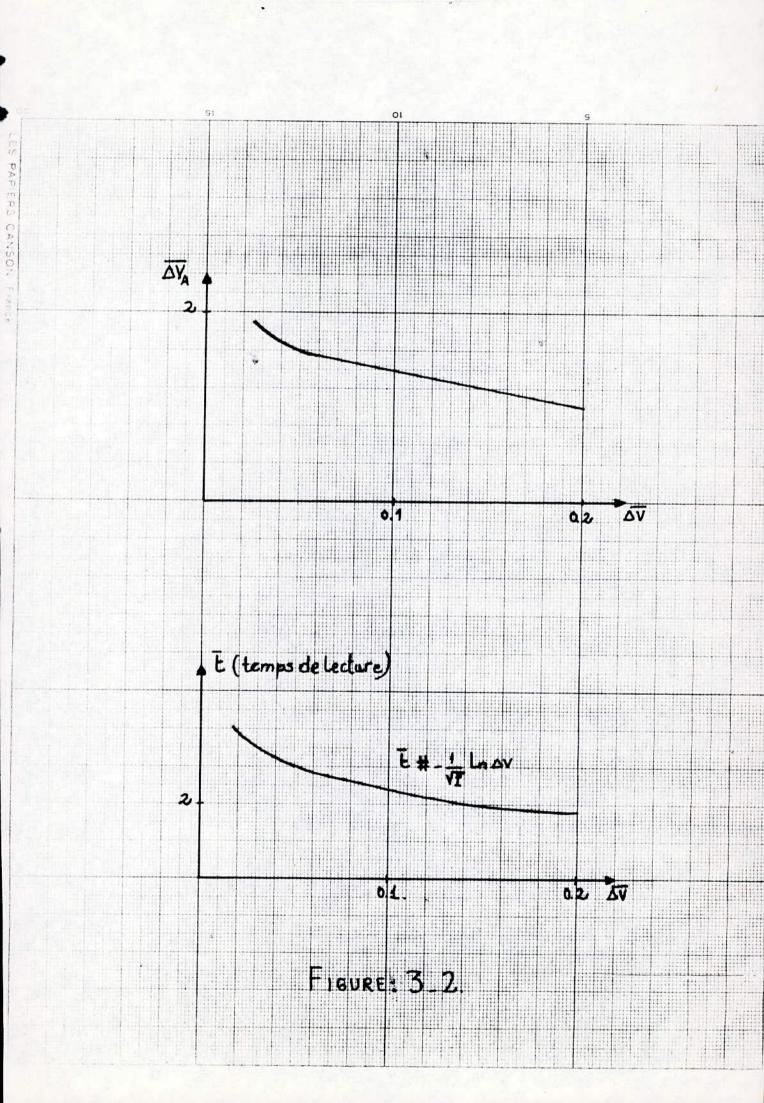

Pour illustrer les expressions mathématiques, on a tracé  $\overline{V}_A$  et  $\overline{V}_B$  en fonction de  $\overline{t}$ , pour différentes valeurs de  $\overline{A}\overline{V}$  On a pris  $\overline{I}$  = 1 et  $\overline{V}_{A_{max}}$  =IO ( voir figure 3-I ) Et pour conclure on a tracé  $\overline{A}\overline{V}_A$  = f  $(\overline{A}\overline{V})$  et  $\overline{t}$  (lecture) = f  $(\overline{A}\overline{V})$  ( voir figure 3-2 )

## 5-3 Commentaires des resultats

D'aprés les courbes donnantl'évolution de la chute de tension au point A , et du temps de lecture, en fonction de la tension  $\Delta$ V à détecter on conclut:

- La commande du montage par un courant constant offre deux avantages tres importants .

- d'Abord une amplification constante .

- un temps de lecture à peu aprés constant.

En effet, pour un tourant  $\overline{I} = 1$ ;

| ΔV          | 0,025 | !<br>! 0,05 | 0,1 | 0,2 |

|-------------|-------|-------------|-----|-----|

| t (Lecture) | 3,7   | . 3         | 2,4 | 1,7 |

On remarque que si la tension à détecter augmente huit fois le temps de lecture diminue de deux fois, ce qui laisse supposer que ce temps est constant.

Control Par Un Courant: I = 1

| 74              | 0,025 | 0,05 | 0,1 | 0,2 |  |

|-----------------|-------|------|-----|-----|--|

| ĀΨ <sub>A</sub> | I     | 0,8  | 0,7 | 0,5 |  |

On remarque que la chute de tension au point est constante et de plus pas assez importante

En conclusion, on peut dire que ce type de commande est bien convenable pour L'amplificateur de lecture, car si on fixe par exemple le temps de lecture à 4 °C, quelques soit la variation de &V, toutes lez tensions à lire, sont lues convenablement et de plus l'amplification est constante.

- Les résultats trouvés, peuvent être expliqués physiquement : dans le montage, on Remarque que chaque transistor constitue pour l'autre une contre-réaction, qui tend dans un transistor à augmenter la courant et dans l'autre à le diminuer, du fait qu'au début de la lecture, il existe une différence de courant dûe à la tension △V qui crée le dèséquilibre

#### 5-4 Remarques

Des expressions des tensions  $\overline{V}_A$  (t),  $\overline{V}_B$  (t) et du temps de lecture deux choses importantes apparaissent :

- si I  $\angle$  0, 25 K  $V_T^2$  ; la différence  $V_A$   $V_B$  n'atteint pas la tension de seuil dans l**g** régime saturé .

- de Plus, pour pouvoir faire conduire les deux transistors il faut que l'intensité du courant de commande soit supérieure à la différence des courants initia  $\mathbf{U}\mathbf{X}$  existants entre les deux transistors après calcul, on trouve que I > K  $\cdot \Delta \mathbf{V}^2$

C'est à dire que pour un courant I  $\leq$  K  $\Delta$  V  $^{\upsilon}$  , le transistor T  $_{1}$  restera bloqué .

#### Exemple:

Pour mieux comprendre ce phénomène, on a fait l'analyse du montage pour un courant I=0.0I K  $V_T$  C'est à dire I=0.0I d'Aprés la relation sus-indiquée, on constate que pour  $\overline{\Delta V} \gtrsim 0.1$  Le transistor  $T_1$  est bloqué, et pour  $\overline{\Delta V} < 0.1$  les deux transistors sont conducteurs .

$$\frac{d\overline{V_A}}{d\overline{t}} = -\frac{1}{2}(\overline{V_{BS}} - 1)^2$$

$$\frac{d\overline{V_B}}{d\overline{t}} = -\frac{1}{2}(\overline{V_{AS}} - 1)^2$$

$$\frac{d\overline{V_A}}{d\overline{t}} + \frac{d\overline{V_B}}{d\overline{t}} = -\overline{I}$$

On trouve

$$\overline{V}_{A} = -\frac{1}{2} \overline{1} \overline{t} + \frac{1}{2} f(\overline{t}) - \frac{1}{2} \overline{N} + \overline{V}_{A_{max}} ; f(\overline{t}) = \frac{4 \alpha \sqrt{1} e^{-\sqrt{1} \overline{t}}}{\alpha^{2} e^{-2\sqrt{1} \overline{t}}} + 1$$

$$\overline{V}_{B} = -\frac{1}{2} \overline{1} \overline{t} - \frac{1}{2} f(\overline{t}) - \frac{1}{2} \overline{N} + \overline{V}_{A_{max}}$$

avec  $\alpha = \frac{2\sqrt{1}}{\overline{N}} + \sqrt{\frac{4\overline{1}}{\overline{N}^{2}} - 1}$

Cet état cesse à

$$\overline{t} = \overline{t_1}$$

où  $\overline{V_{BS}} = 1$

On trouve

$$\overline{E} = -\frac{1}{\sqrt{\overline{L}}} \log \left[ \frac{2 + \sqrt{4 + \alpha^2}}{\alpha^2} \right]; \text{ on note } \overline{V_A}(\overline{t_1}) = \overline{V_A}$$

2éme Régime : T1 Bloqué et T2 Conducteur

$$\overline{V_A} = \overline{V_O}$$

on theore  $\overline{V_B}(\overline{t}) = -\overline{I}(\overline{t} - \overline{t_1}) + \overline{V_B}(\overline{t_1})$

$\overline{d}\overline{V_B} = -\overline{I}$

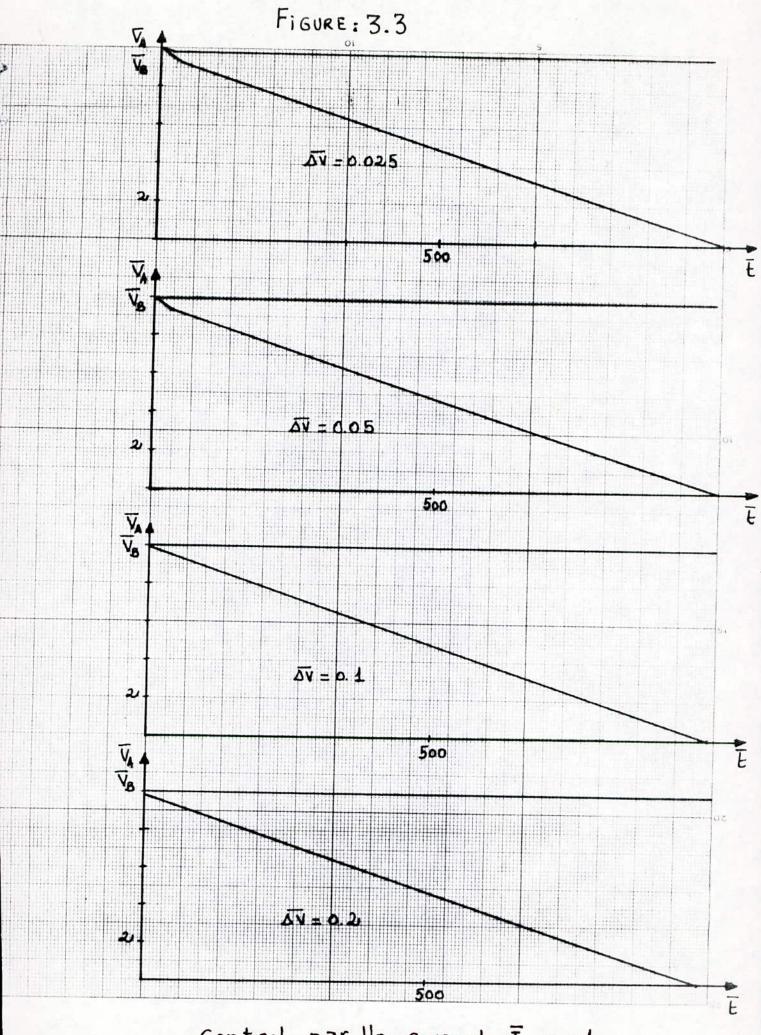

Pour illustrer ces resultats, on a tracé  $\overline{V_A(t)}$  et  $\overline{V_B(t)}$ Four  $\overline{I} = 0.01$ ; on a pris  $\overline{V_{Amax}} = 10$  et  $\overline{N} = 0.025, ..., 0.2$  (Voir fig 3-3)

Control par Un courant: I = 0.01

#### Commentaires :

On remarque d'aprés cette petite étude que l'intensité du courant de commande joue un rôle important, et deux choses apparaissent.

- Si l'intensité du courant de commande est grande, le temps de lecture est petit, mais la chute de tension au point A est grande

- Si l'intensité du courant de commande est faible, le temps de lecture devient grand, mais la chute de tensionn au point A est petite.

d'Où existance d'un lien entre l'intensité du courant de commande est les contraintes de notre problème.

Néanmoins, l'analyse du montage avec des courants de commande d'intensités moyennes montre que la commande du montage par un courant constant donne des resultats trés satisfaisants.

Ainsi pour un courant  $I = K V_T^2$ , le temps de lecture est  $t = 4 C/_{KV_T}$  et la diminution de la tension en A est inferieure à 10 % de la tension d'alimentation .

Donc on peut adopter ce type de commande, mais in est nécessaire d'agir sur les constantes technologiques des transistors pour diminuer le temps de lecture et 'avoir ainsi un lecteur rapide.

#### CONCLUSION

D'aprés cette analyse, on peut noter deux choses importantes : Ier:la variation de la tension AV à détecter influe beaucoup sur le fonctionnement de l'amplificateur de lecture, c'est à dire sur le temps de lecture et l'amplification.

2 eme : existance d'un lien solide entre l'amplification obtenue et le temps de lecture et par conséquent, an lieu d'éssayer d'obtenir par exemple une amplification maximum comme dans le cas de la fonction de commande qui permet la blocage net d'un des deux transistors, et qui a conduit à des temps de lecture instables à l'exptrême, on devrait plutôt chercher un compromis entre les deux, c'est à dire la plus grande amplification possible tout en ayant un temps de lecture stable et assez court.

- des trois fonctions de commandes utilisées, la meilleure, c'est à dire celle qui présente le meilleur compromis amplification tiré temps de lecture est l'attaque par un courant constant, qui peut être adoptée mais necessité encore une amélioration du temps de lecture, le prochain chapitre sera consacré à l'étude d'un moyen perméttant d'augmenter la vitesse de fontionnement de l'amplificateur de lecture, tout en ayant une amplification stable et maximum.

Nous tenons à faire remarquer que la résolution directe de certains des systemes d'equations différentielles auxquels nous avons eu à faire était impossible, ce qui nous a obligé à contournerle problème en usant des approximations et par conséquentl'exactitude des resultats depand énormément de l'exactitude des approximations faites.

La vérification expérimentale nous permettra de conclurequant à la véracité des resultats.

## CHAPITREII

# AMELIORATION DES CARACTERISTIQUES DE L'AMPLIFICATEUR DE LECTURE

# I-Introduction

Jusqu'à présent, les resultats obtenus ne repondent toujours pas aux objectifs que l' on s'est proposés d'atteindre, c'est à dire un lecteur rapige de mémoires dynamiques.

En effet d'aprés l'analyse faite au chapitre I, il est impossible d'obtenir un temps de lecture satisfaisant sans pour cela perdre en amplification.

La chute de tension doit être au maximum entre 10et 20 % de la tension d'alimentation car si on l'a minimise, letemps de lecture devient énorme.

Le but de ce chapitre est la recherche d'un meilleur compromis entre le temps de lecture et l'amplification, en agissant et sur les fonctions de commande et, s'il le faut, sur la compléxité du montage (ce qui se traduit par une augmentation de la surface occupée par l'amplificateur de lecture).

# 2- Recherche d'une fonction de commande

On suppose toujours que l'information à détecter AV, se trouve au point B.

Avoir un temps de lecture faible et une décharge de V<sub>A</sub> la moindre possible, revient à faire décharger la capacité reliée au noeud B Le plus rapidement possible.

A cet égard, nous avons établis deux hypothéses: Ier hypothése:

Le courant de drain I<sub>1</sub> est constant et trés faible, ce qui assure une contre réaction positive et une faible diminution de V<sub>A</sub> au cours du temps et par conséquent une bonne amplification.

En faisant intervenir les équations différentielles qui régissent le fonctionnement du système, on arrive à trouver la tension V<sub>S</sub> QUI satisfait l'hypothèse énoncée plus haut.

## 2éme hypothése:

Les variations de V<sub>A</sub> et de V<sub>B</sub> sont dans un rapport constant et très grand àtout instant c'est à dire que

AVB-a avec a > 1.

Ce qui assure une diminution rapide de la tension  $V_{\bf 8}$ et surtout une bonne amplif ica t ion.

## COMMENTAIRES

L'analyse faite au niveau de ce paragraphe nous a permis de nous approcher de la solution, mais hélas, d'une par t les tensions de commandes nécessaires sont prégners très difficiles à génerer (nécessité d'élaborer des génerateurs complexes), d'autre part on obtient des temps de lecture assez courts (dans certains cas) mais qui varient beaucoup lorsque la tension &V varie.

# 3- Attaque par deux niveaux de courants constants

Dans l'étude faite au premier chapitre pour le cas d'une attaque par un courant constant, on avait conclu que l'intensité du courant de commande joue un role important dans la détermination des caractéristiques de l'amplificateur et que:

-Si l'intensité du courant de commande est grande, on avait un temps de lecture trés court mais l'amplification est médiocre et vice-versa.

En exploitant ce résultat, on peut optimiser les caractéristiques de l'amplificateur, c'est à dire qu'on va éssayer de trouver l'in-tensité du courant de commande qui donnerait le meilleur compromis temps de lecture-amplification.

On se fixe deux hypothéses au départ:

-On dira que l'amplification est bonne, si la chute de tension au point A(symétrique deB où se trouve la tension à detecter) ne depasse pas I5% de la tension d'alimentation VAMANA

-On dira qu'on a un temps de lecture assez court, si celui-ci est infèrieur ou égal à 4  $\text{C/KV}_{\mathsf{T}}$

# 361 Détermination de l'intensité du courant de commande

Pour généraliser les résultats, on a normalisé les tensions, le temps et le courant par rapport aux paramétres des transistors et la capacité C

On note:  $\overline{V} = \frac{V}{V_T}$ ;  $\overline{t} = \frac{t}{C/KV_T}$  et  $\overline{I} = \frac{I}{KV_T^2}$ .

On suppose qu'à l'instant initial(début de la lecture) que la distribution du courant dans les deux branches de l'amplificateur de

lecture est  $\overline{I} = \sqrt[4]{I}$  et  $\overline{I} = \sqrt[4]{I}$ .

A l'aide des équations différentielles qui régissent le fonctionne--ment du montage, on détermine l'intensité du courant qui donnerait une telle distribution.

#### CALCUL DE I

Au départ les deux transistors Tiet Tisont saturés, d'où:

$$\overline{I}_{1}(0) = \frac{1}{2} \left( \overline{V}_{8s_{max}} \right)^{2} = \sqrt[3]{I}$$

On trouve:

$$\overline{I} = \frac{\overline{\Delta V_{min}}^{2}}{2(1-8)} \left( \frac{1}{1-\sqrt{\frac{8}{3-1}}} \right)^{2}$$

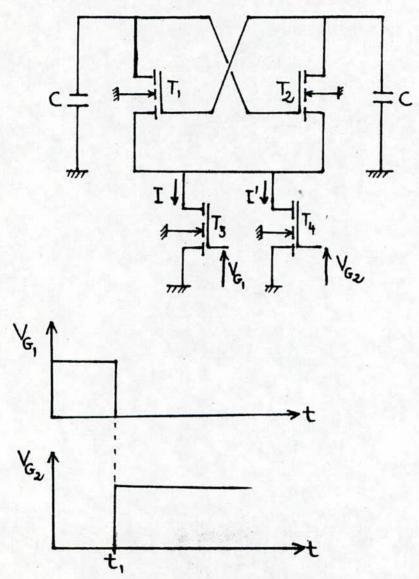

Pour illustrer cette expression, on a tracé la caractéristique I=f(%); on a pris Δ V=0,05(plus basse tension pouvant se présenter à l'entrée de l'amplificateur). (voir figure 4-I).

Pour réaliser l'hypothese fixée au depart, c'est à dire meilleur compromis temps de lecture- amplification, on a tracé les deux carac-téristiques: temps de lecture en fonction de l'intensité de commande et chute de tension au point  $A(\overline{\Lambda V_A})$  en fonction de  $\overline{I}$ .

(voir figure 4-2)

Pour pouvoir tracer ces deux caractéristiques, on utilise les resulats trguvés au chapitre I pour le cas de l'attaque par un courant constant

D'après la figure 4-2 on conclu que:

-Pour réaliser les deux hypothéses de départ, l'intensité du courant de commande doit être comprise dans la fourchette suivante:

0,4 ≤ Ī ≤ I,6 c'est à dire 0,46 ≤ % ≤ 0,48

De plus pour activer la décharge de la capacité liée au point B on prévoit une attaque par un deuxième courant dont l'intensité est supérieure à l'intensité du courant initial, c'est à dire:

Au début de la lecture on attaque le montage par un courant dont l'intensité est comprise dans la fourchette sus -indiquée, aussitôt les deux capacités commencent à se décharger à travers les deux transistors T₁et T₂avec des courants différents(cela est dû à la différence MV EXISTANTE entre Va et Va au début de la lecture), ainsi la différence de tension entre A et B augmente, et dés que cette dif-

-férence atteint un certain seuil (par exemple 500 mV) le deuxième courant intervient, ce qui provoque une décharge rapide de la tension VB, et par effet cumulatif cette derniere tend à bloquer rapidement le transistor T1, ce qui assure en même temps un temps de lecture as-sez court ét une amplification meilleure.

Pour réaliser une telle commande, on utilise deux transistots MOS fonctionnants en régime saturé(en sources de courants) et qui s'ouv-rent et se ferment grâce à une commande externe.

Le temps  $t_1$  est le temps nécessaire pour que la différence entre les tensions  $V_A$  et  $V_B$  atteigne un certain seuil(par exemple  $\overline{\Delta V}$ =0,5).

#### 3-2 APPLICATION

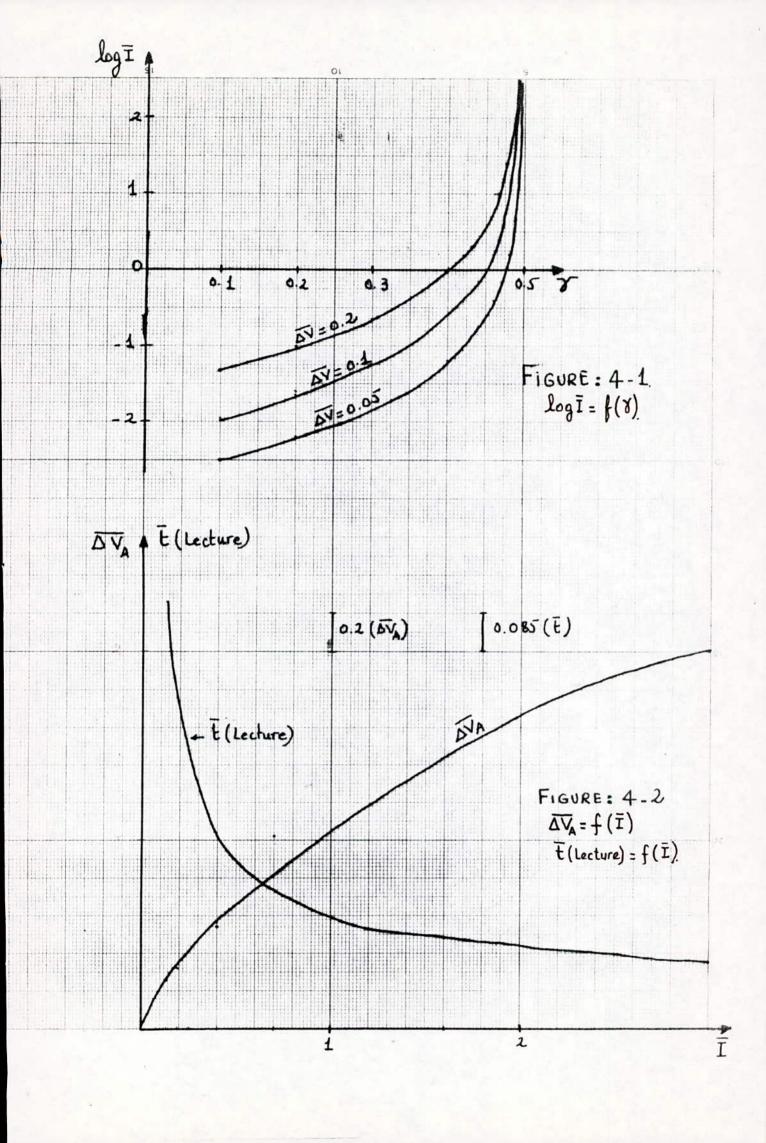

Pour illustrer ces résultats, ona tracè  $\overline{V}_A$  et  $\overline{V}_B$  en fonction de  $\overline{t}$  pour diffèrentes tensions  $\overline{\Delta V}$  à dètecter.

On a pris  $\overline{1}=0.7$  et  $\overline{1}'=1$ ;  $\overline{V}_{\text{amax}}=10$  (voir figure 4-3).

#### 3-3 COMMENTAIRES

D'après les résultats trouvès, on peut dire qu'on est arrive à réaliser les deux hypothèses fixèes au départ.

-Le temps de lecture est assez court et de plus ne varie pas beau-coup quand la tension  $\Delta V$  à détecter varie .

| ΔV          | 0.05 | 0. L | 0.2 |  |

|-------------|------|------|-----|--|

| E (Lecture) | 3,5  | 2,9  | 2   |  |

-La chute de tension au point A est infèrieur à 15% de la tension d'alimentation  $V_{A_{max}}$ , et de plus varie peu quand la tension  $\Delta V$  à détecter varie.

| $\overline{\Delta V}$   | 0.05 | 0.1 | 0.2 |

|-------------------------|------|-----|-----|

| $\overline{\Delta V_A}$ | 1.1  | 1   | 0.9 |

Pour montrer l'avantage de l'attaque par deux niveaux de courants par rapport à l'attaque par un seul courant, on a fait l'ètude comparative des résultats obtenus pour les deux cas, le tableau ci-dessous donne les résultats trouvès.

|            | E(Lecture) |      |      | ΔVA  |     |     |

|------------|------------|------|------|------|-----|-----|

| ΔV         | 0.05       | 0.1  | 0.2  | 0.05 | 0.1 | 0.2 |

| 2 Courants | 3,5        | 2,9  | 2    | 1,1  | 1   | 0,9 |

| 1 courant  | 4,2        | 3,25 | 2,27 | 0,7  | 0,5 | 0,4 |

On remarque que l'amèlioration apportée par l'attaque par deux ni-veaux de courants est à peu près de 20% pour le temps de lecture

et d'autre part la chute de tension en A augmente à peu près de 10%

mais reste toujourd infèrieure à 15% de la tension d'alimentation.

#### 4- AUGMENTATION DE LA VITESSE DE FONCTIONNEMENT

On peut remarquer que le temps de lecture est êtroitement liè à la constante de temps  $\mathcal{T} = \mathbb{C}/KV_{\mathcal{T}}$ , c'est à dire liè aux valeurs de C et K (conductivité spécifique du transistor).

Pour diminuer le temps de lecture, on agit sur ces deux paramètres ce qui revient à dire que si on arrive à diminuer la capacité C ou à augmenter K, on arrive à augmenter la vitesse de fonctionnement du lecteur.

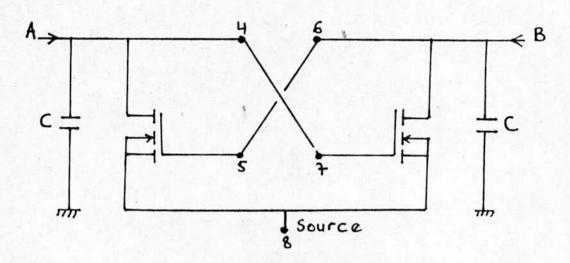

#### 4-I DIMINUTION DE LA CAPACITE C

Comme il a été signalè dans le chapitre I , la capacité C represente la somme de plusieurs capacités parasites, dont l'une est la capacité d'entrée de l'amplificateur et les autres sont les capacités qu'off-rent tout le réseau de cellules mémoires qui se trouvent de part et d'autre de l'amplificateur et la capacité de la ligne de lecture .

Pour diminuer cette capacité, on isole l'amplificateur pendant la phase de lecture des mémoires qui se trouvent connectées à son entrée grâce à deux transistors MOS qui s'ouvrent juste pour décharger l'in-formation AV à lire dans la capacité d'entrée de l'amplificateur , puis sont fermés et ainsi isolent le lecteur du réseau de points mémoires pendant la phase de lecture .

Grâce à ces deux transistors ( $T_5$  et  $T_6$ ) la constante de temps devient  $\mathcal{T}=C_0/KV_{\mathcal{T}}$  au lieu de  $\mathcal{T}=C/KV_{\mathcal{T}}$  avec  $C_0$  au moins dix fois plus petite -te que  $C_0$ , ce qui implique une diminution du temps de lecture d'au moins de IO fois.

#### APPLICATION

Pour mieux voir l'avantage qu'offre les deux transistors MOS d'iso--lement, on a dressè le tableau suivant donnant le temps de lecture en fonction de la tension à dètecter  $\Delta V$ , pour des courants de commande  $\overline{I}=0,7$  et  $\overline{I}^**=\overline{I}$ .

| ΔV         | 0.05 | 0.1  | 0.2 |

|------------|------|------|-----|

| E(Lecture) | 935  | 0.29 | 0.2 |

On remarque que le temps de lecture diminue dix fois, et l'amplific--ation est inchangée.

#### 4-2 AUGMENTATION DE K

La deuxième solution qui offre un temps de lecture très court consis-te à augmenter la valeur de K(conductivité spécifique du transistor)

ce qui revient à agir les paramètres technologiques des transistors

constituants l'amplificateur de lecture.

Or K s'exprime comme suit /

$$K = \mu \frac{\mathcal{E}_{ox} \mathcal{E}_{o}}{\mathsf{t}_{ox}} \cdot \frac{\mathsf{W}}{\mathsf{L}} = K_{o} \frac{\mathsf{W}}{\mathsf{L}}$$

Où

ν: mobilité des porteurs de charges.

€ constante diélectrique de l'oxyde isolant la gate.

E: constante dielectrique du vide.

W : largeur de la zone de gate ou du canal.

L : longueur de cette même zone. (voir figure 4-4)

Remarquons que pour une même surface de la région de gate S=W.L si on divise L par A>I et on multiplie W par la même valeur

Alors

$$K' = K_0 \frac{W \cdot A}{L/A} = K_0 W/L \cdot A^2 = A^2. K$$

Donc sans changer la surface de gate, on peut multiplier la constante K par 3 ou 4 , ce qui donne un temps de lecture plus faible , car K à augment \*\*

Métallisation de gate (a) (aluminium suroxyde mince) W: Largeur du Canal × contact de drain contact de source. fenêtres contact Gate exyde épais P N ·N Diffusion de drain Substrat (B) P Diffusion de - oxyde mince de gate. Longueur du canal Source

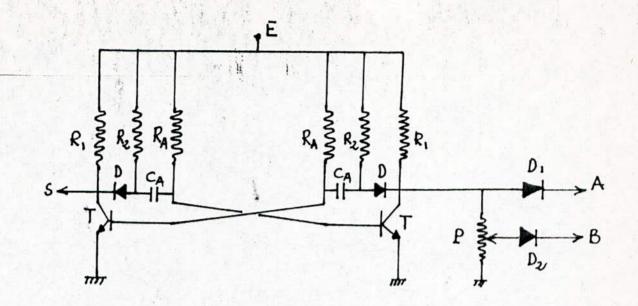

## 5- APPLICATION

Le schema final de l'amplificateur de lecture serait donc :

On prend:

Paramètres des transistors T1et T2

K=80

$$\mu$$

A/V<sup>2</sup> ; V=I volt ; C<sub>o</sub>=0,I pF

Intensités des courants de commandes

Tension de référence:

Resultats obtenus

| ΔV (mV)                          | 50  | 100 | 200 |

|----------------------------------|-----|-----|-----|

| temps de Lecture (nS)            | 4.3 | 3.6 | 2.5 |

| Chute de tension en A<br>(Volts) | 1,1 | 1   | 0,9 |

## CONCLUSION

Nous pouvons conclure ce deuxième chapitre en disant que l'attaque par deux niveaux de courants constants, offre les meilleurs possi-bilitès quant à la vitesse de fonctionnement de l'amplificateur et l'amplification obtenue.

A cela s'ajoute le fait que générer un courant constant est plus facile que de générer les tensions  $V_S$  qui étaient nécéssaire pour mettre en application nos précédentes hypothèses.

D'autre part on a vu qu'il était (sinon impossible) très difficile d'obtenir d'encouragents résultats avec la première configuration de l'amplificateur de lecture, c'est à dire avec deux transistors MOS uniquement, mais par contre en ajoutant deux transistors "d'isolement" on parvenait dèja à des temps de lecture dix fois moindre. L'amélioration technologique accomplissait le reste, c'est à dire fatsait diminuer encore ce temps de lecture de 4à 5 fois et on obtient enfin un temps de 3 à 4 nS.

#### CHAPITREIII

# APPLICATION DE L'AMPLIFICATEUR DE LECTURE DANS LES MEMOIRES DYNAMIQUES A MOS

### I- Introduction

Les memoires à semi-conducteur utilisent, comme les technologies des circuits intègrès, le silicium en tant que matérieau de depart. Elles constituent un domaine privilégé où les progrès de l'intègra-tion poussèe se font sentir immèdiatement. Elles represente les premières applications des circuits intégrès complexes, et constitu-eront encore des véhicules de choix pour la démonstration de faisabilité des circuits intègrés très complexes (V. L. S. I). Le chapitre des memoires est extrêmement vaste et complexe, pour èssayer d'en synthètiser l'éssentiel, on peut ranger les memoires dans six grandes catégories:

a- Les RAM:-comparables dans leurs fonctions aux tores de ferrites donc à lecture, écriture et éffacement. Elles sont adréssables, c'est à dire qu'on peut agir exclusivement

b-Les ROM:-memoire "morte" enregistrée une fois pour toute part le fabriquant, et qui ne peut plus être que lue. Elle est egalement adressable (accés aléatoire).

sur n'importe quelle cellule élémentaire.

c-Les PROM:-autre memoire morte, mais cette fois inscriptible par l'utilisateur à l'unite; après quoi, elle ne peut plus être que lue Egalement adressable.

d-Les reprom ou RMM:-PROM, pouvant cependant être éffacée (selon un processus long ou difficile) puis rè-inscrite par l'utilisateur, à l'unitè, pour servir uniquement en lecture ensuite.

e-Les CAM:-mèmoire non adressable, où le message est retrouve en fonction de son contenu, c'est une memoire très complexe, bien moins utilisée que les précedentes.

f-Registres à decalage:-registres dans les quels l'information se dèplace pas à pas, l'accès n'est pas alèatoire, mais sequentiel (comme lorsqu'on lit une piste de disque magnètique).

Notre ètude s'interesse aux mèmoires RAM à technologie MOS, on ditingue deux types de RAM:-

RAM statique:l'information est memorisée dans un flip-flop aussi longtemps qu'on le désire(tant que l'alimentation subsiste!)

RAM dynamique:n'existe qu'en technologie MOS,l'information est stockée dans une capacité de structure gate-substrat ou drain-substrat, et doit être rafraîchie periodiquement pour compenserles pertes dûes aux inévitables courants de fuite.

2-DIFFERENTS TYPES DE RAM A MOS

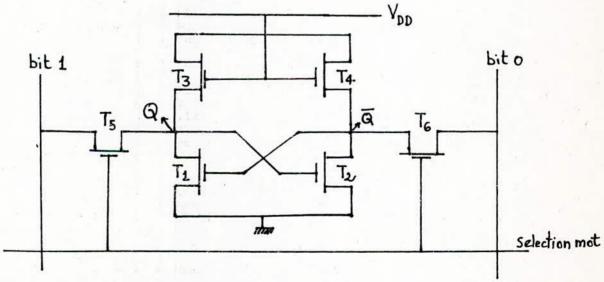

2-IMemoires statiques à MOS

Elles ont comme circuit de maintien de l'information un bistable constitué par les transistors  $T_1$  et  $T_2$  (transistors de commande)  $T_3$  et  $T_4$  (transistors de charge à enrichissement ou à dépletion qui peuvent être remplacés par des résustances en silicium polycristall-in).

La communication avec les lignes de bits(bit I et bit o) est assurée par les transistors  $T_5$  et  $T_6$  qui jouent le rôle d'intérrupteurs. Lors de l'ériture, les niveaux appliqués sur bit I et bit 0 sont transfèrés à Q et  $\overline{Q}$  à travers les transistors  $T_5$  et  $T_6$  rendus conducteurs par la commande selection mot, imposant ainsi au point mèmoire un " I " logique(le potentiel du point Q est ègal à  $V_{DD}$   $\overline{A}$  -  $V_{\overline{D}}$ ) ou un "0" logique(le potentiel du point  $\overline{Q}$  est  $V_{DD}$  -  $V_{\overline{D}}$ )

Avec  $V_{\overline{DD}}$ : tension d'alimentation et  $V_{\overline{T}}$ : tension de seuil des MOS. A la lecture, les valeurs des tensions en Q et  $\overline{Q}$  sont lues sur les lignes bit I et bit O à l'aide d'amplificateur de lecture après adressage de la ligne selection mot(transistors  $T_5$  et  $T_6$  rendus conducteurs).

## 2-2 Memoires dynamiques à transistors MOS

Les caractèristiques des memoires évoquées au paragraphe précédent sont leur operation en mode statique nécéssitant un nombre élevé d'èlements actifs et nécéssitant, par-là même, une surface de silicium occupé par point mémoire relativement importante.

Afin d'augmenter le nombre de points mémoires sur une surface donnée de silicium, c'est à dire pour un rendement technologique donnée on a cherchér à diminuer le nombre d'éléments actus nécessaires par bit d'information stockée.

on a ainsi simplifiè les points statiques pour arriver au concept de points mémoires dynamiques, utilisant trois transistors, puis un seul transistor MOS par bit.

## 2-2-I Principe de la mémorisation dynamique

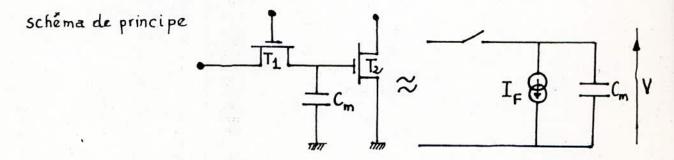

La memorisation dynamique est basée sur la propriété du transistor MOS d'avoir une impédance d'entrée très élevée, le courant de fuite à travers la grille d'un transistor MOS, est en effet, très infèrieur à 10<sup>615</sup> A. Nous disposons donc d'une capacité de bonne qualité qu'il faut adresser avec un commutateur de faibles fuites. Il On utilise pour cela un transistor MOS de faibles dimensions, et d'est c'estlui qui est responsable du courant de fuite mesuré, ona donc le schèma de principe représenté ci-dessus.

- Trjoue le rôle de commutateur.

- T<sub>2</sub>joue le rôle d'élément de stockage par sa grille, et d'élément de lecture par son drain .

Du point de vue mémorisation on a l'équivalent d'une capacité mémorise cm associé à un courant de fuite  $I_F$  du commutateur  $T_I$  (fuites associés à sa diode de drain). On conserve donc la tension V en mémoire plus ou moins longtemps suivant la valeur de  $I_F$ . Si on tolere une perte  $\Delta V$ , on conservera l'information pendant un temps  $\Delta t = \Delta V$  Cm/ $I_F$

### EXEMPLE:

Pour Cm=0.2 pF , AV= I volt et IF= I pA (à 25°C)

On aura  $\Delta t = 200 \text{ mS}$

Cela signifie que pendant 200 ms on peut conserver une information sans avoir à la rafraîchir.

En realitè si la température augmente, le courant  $I_F$  augmente (de deux fois tous les IO degrés) ce qui fait diminuer le temps de conservation .

Generalement on se limite à un temps de mémorisation entre deux rafraîchissement de 2ms, c'est à dire qu'on doit lire la mémoire toute les 2 ms et réecrire l'information.

Pour que ce principe soit utilisable pratiquement, il faut que le temps nécessaire au rafraîchissement soit inferieur à 5% du temps de disponibilité de l'information au niveau du systeme et sur toute la gamme de température d'utilisation.

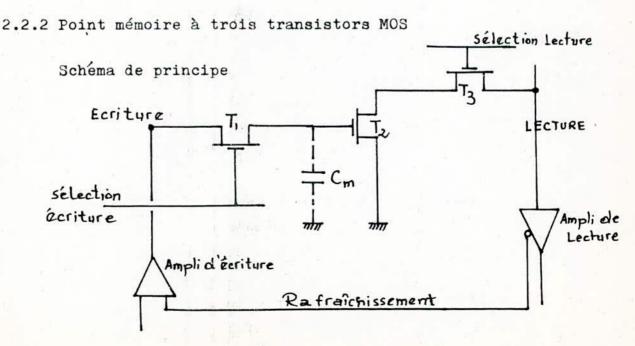

Comme il a été indique, ce point utilise la memorisation dynamique de l'information dans une capacité de grille d'un transistor MOS et sa structure est donnée par la figure ci-dessus.

Cm est la capacité mémoire qui conserve l'information en dynamique, ceèle-ci est inscrite à travers T<sub>I</sub> depuis la ligne d'écriture. Le transistor T<sub>2</sub> est le transistor de lecture et selection lecture s'effectue par T<sub>3</sub> (lecture par mot).

Périodiquement il est nècessaire de rafraîchir l'information dans Cm, cela s'éffectue par une lecture à travers  $T_3$  et  $T_2$ , ensuite l'information est rèinscrite àtravers  $T_1$ .

Ils existent d'autres configurations de point memoire à trois tran--sistors MOS, utilisants moins de lignes de commandes, l'explication de leur fonctionnement ne serait guere utile ici.

## 2-2-3 Point memoire aun transistor MOS par bit

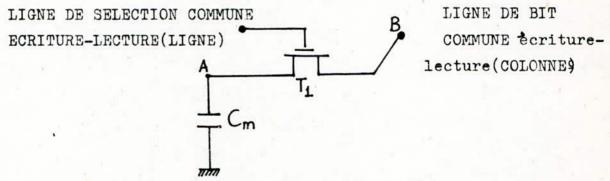

Ce point memoire utilise directement la cellule donnée au paragrap--he 2.2.I ,et la structure du point memoire est celle représente ci-dessous:

On y trouve la capacité memoire Cm qui stocke l'information sous forme d'un niveau élevé(I logique) ou d'un niveau faible(O logique) de tension en A .Le transistor  $T_{\rm I}$  est un transistor de sélection ligne aussi bien pour la lecture que pour l'écriture .

C'est cette structure qu'on adoptera pour la suite de notre êtude.

### 3- ORGANISATION D'UNE RAM DYNAMIQUE

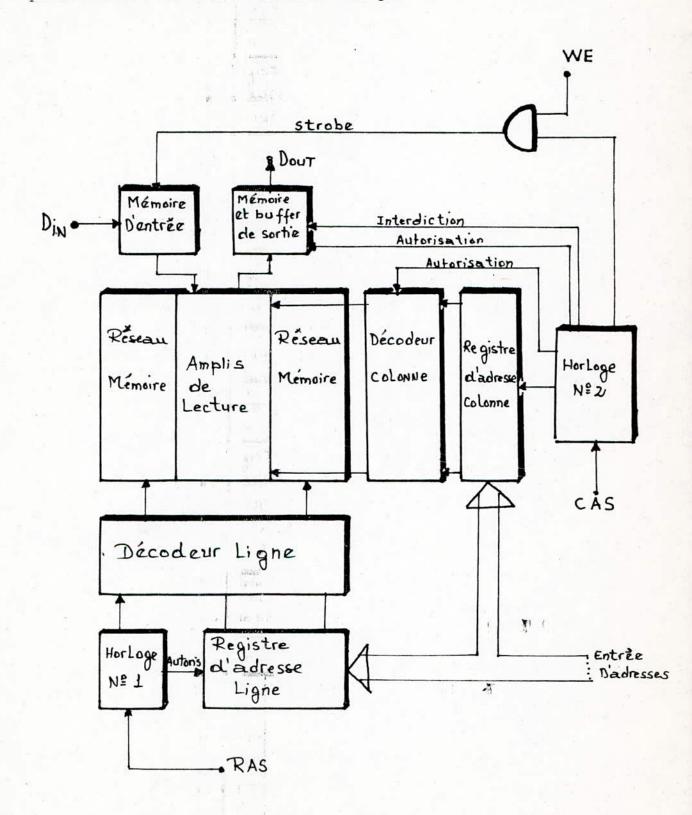

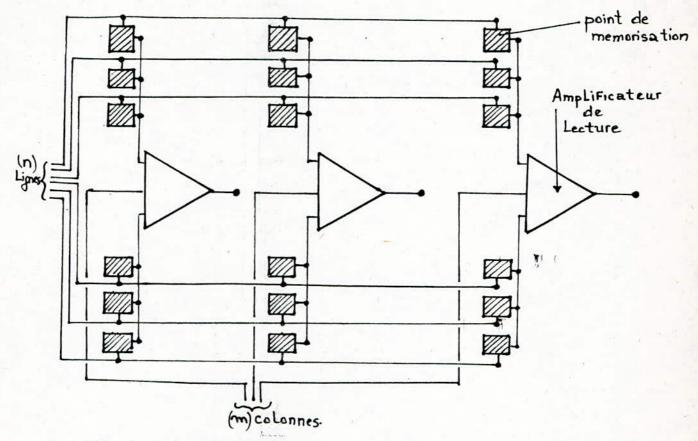

Pour éssayer d'en synthétiser l'essentiel, on donne le synoptique de base d'une RAM dynamique de  $(n \times m)$  bits utilisants comme point mémoire un seul transistor MOS par bit.

On y trouve:

-Rèseau memoire: c'est l'ensemble de points memoires, disposés en n lignes et m colonnes de part et d'autre des amplificateurs de lecture. On a ainsi une structure de (n x m ) cellules.

-Amplificateurs de lecture: leurs rôles est d'amplifier l'informatie -on memorisée pour être lue.

De plus on note qu'il y a autant d'amplificateurs de lecture que de colonnes.

6-Entrèe d'adresses: pour réduire le nombre de broches du circuit intègré, on utilise les mêmes entrées pour l'adressage colonne et ligne, les k bits d'adresse requis pour adresser une cellule parmi (n x m ) sont èmis en deux fois par multiplexage, sur les lignes d'adresses et mèmorisées dans les registres d'adresses ligne et colonne

-Registres d'adresses: sont des registres capables de memoriser l'adresse jusqu'à une décision donnéeq.

-DIN et Dout: designent respectivement entrèe de données et sortie de données.

Décodeurs ligne et colonne:

Grâce aux adresses fournies par les deux registres d'adresses ligne et colonne, les dècodeurs permettent de selectionner une seule cell--ule parmi (n x m ) autres, et de la préparer ainsi pour un cycle de lecture ou d'écritime.

### -Horloge NºI:

L'horloge NºI est commandée par le signal RAS (strobe adresse ligne) et permet la validation du décodeur ligne.

### Horloge Nº2:

L'horloge Nº2 est commandée par le signal CAS (strobe adresse colonne elle proet de :

-autoriser le transfert de données en sortie en cas de lecture notons que la sortie est à logique trois états.

-autoriser le transfert de données vers la mémoire sélectionnée en cas d'écriture.

### L'entrée WE:

cette entrèe permet de choisir entre un cycle de lecture ou d'écriture

ON peut donc imaginer le schema de brochage du circuit intégré:

### 3-2 FONCTIONNEMENT

La RAM dynamiques à cellules de un transistor MOS? peut être soumise à trois cycles: lecture, écriture et rafraîchissement.

Le déroulement de ces cycles est conditionne par :

-La précharge

-L'autorisation d'écriture ou de lecture.

Le décodage des bits d'adresse ligne permet de selectionner une ligne de m cellules, dont le contenu est lu par m amplificateurs de lecture; le décodage des bits d'adresse colonne permet d'aiguiller sur une sortie unique l'information choisie sur les m lues initia--lement.

Pour mieux comprendre la lecture, on suppose qu'ona seléctionné une cellule, et voyons comment s'éffectue le basculement de l'amplific-ateur de lecture?

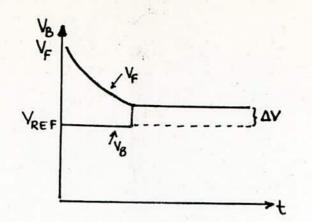

D'abord le signal de prècharge charge les capacités de structure de la ligne de lecture et la capacité d'entrèe de l'amplificateur à une tension de référence située à mi-chemin entre le niveau haut(I logique et le niveau bas (O logique) que peut contenir la cellule.

Dès l'ouverture du transistor d'isolement de l'amplificateur de lect-re , la capacité de la cellule se dècharge (ou se charge) à travers

la capacité d'entrée de l'amplificateur, et ce phénomène conduit à un

déséquilibre de l'amplificateur et qui par la suite bascule selon le

procèssus décrit aux chapitres I et II.

# -Cas de la lecture d'un "I"

Dès l'ouverture des transistors d'isolement, la capacité de la cellule mémoire se décharge à travers la capacité d'entrée de l'amplificateur Co et de plus on a Co«C (Cètant la capacité de la ligne) ce qui conduit à un surplus (ΔV) de tension en B et celà conduit au bascul-ement de l'amplificateur de lecture (voir figure).

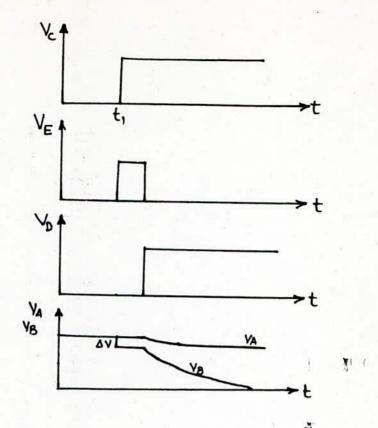

# Allure des tensions aux différents points

On suppose que la lecture commence à

# Cas de la lecture d'un "O"

Dans le cas où la celluteseléctionnée contient un "zèro" (basse ten--sion) la capacité Co de l'amplificateur se décharge à travers la capacitè memoire Cm et la capacite C Et de plus Co C, ce qui conduit au basculement de l'amplificateur.

## Allure des tensions aux diffèrents points

### REMARQUE:

On remarque que pour les deux cas envisagés, la tension au point B EST à l'état haut si on lit un "#" ET & l'état bas si on lit un "O" d'où conservation de l'information au niveau de l'amplificateur.

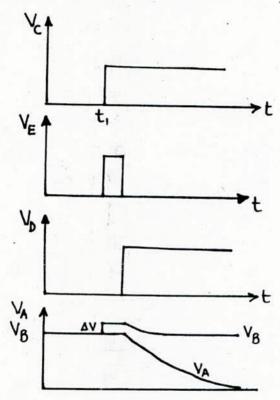

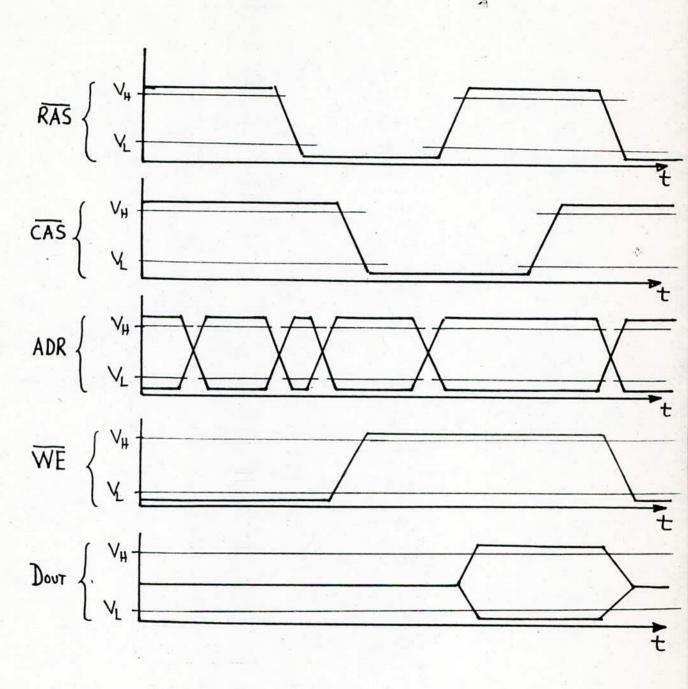

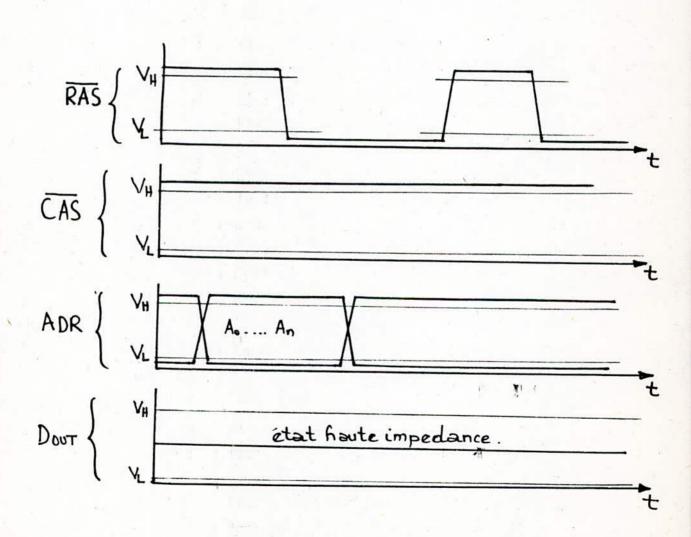

#### CHRONOGRAMMES DU CYCLE DE LECTURE

Trois signeaux sont nécéssaire pour permettre la lecture de la donnée contenue dans la cellule seléctionnée.

- Le signal (RAS) actif à l'état haut, autorise le décodeur ligne à fournir l'adresse contenue dans le registre d'adresse ligne au réseau de cellules mémoires, ce qui permet de seléctionner une ligne de cellules -Le signal (CAS) actif lui aussi à l'état haut, autorise le décodeur colonne à fournir l'adresse contenue dans le registre d'adresse colonne au rèseau de mémoires, ce qui permet d'activer une colonne. Donc après application des signeaux RAS et CAS Une seule cellule est selèctionnée.

-Le signal WE(write enable) est mis à l'état bas, ce qui interdit toute écriture et prépare ainsi le dispositif à accomplir la lecture de la donnée extraite.

Ayant realise les trois conditions c'est à dire RAS, CAS et WE la donnée est transmise vers le registre de sortie pour être lue.

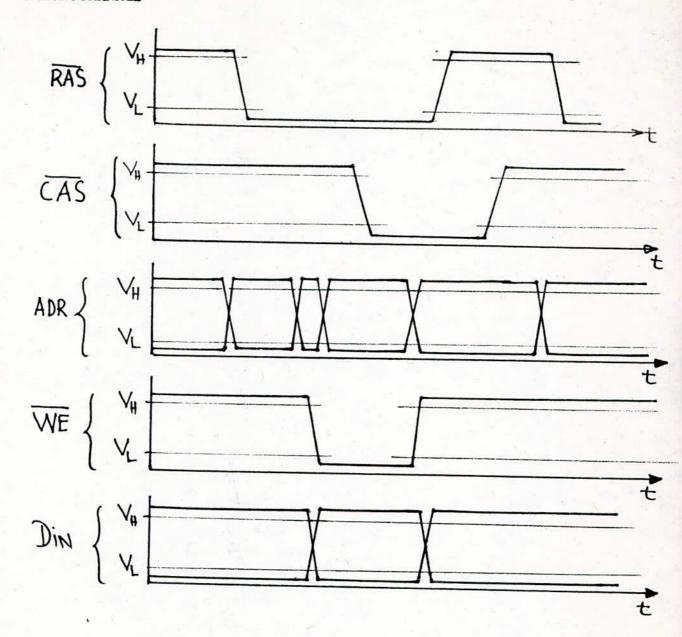

### 3.2.2 CYCLE D'ECRITURE

### CHRONOGRAMMES

Comme dans le cas de la lecture, les signeaux RAS et CAS valident les décodeurs ligne et colonne, et selèctionnent ainsi une seule cellule.

Pour ce cas le signal WE autorise le transfert de données vers la mémoire, mais interdit le transfert de données vers la sortie. Les diffèrentes phades nécéssaires au cycle d'écriture sont décrites ci-haut.

# 3.2.3 CYCLE DE RAFRAICHISSEMENT

Dans la mesure où un cycle de lecture entraine le rafraîchissement automatique des informations contenues dans les n cellules d'une ligne, un rafraîchissement complet de la memoire est effectué en m cycles de lecture, permettant de selectionner successivement toute les lignes, et cela toutes les 2mS.

Il est à noter que ces cycles de lecture nécéssaires au rafraîchis-sement de la totalité de la mémoire correspondent aux K combinan-sons binaires possibles des bits d'adresse ligne; l'état des bits

d'adresse colonne étant indifférent durant le rafraîchissement.

Notons que la durée du cycle de rafraîchissement ne dépasse pas

gènéralement 5% du temps utile pour les différentes RAM dynamiques

existantes.

Les chronogrammes du cycle de rafraîchissement sont donnés ci-dessous.

## 4- Structure interne de quelques éléments

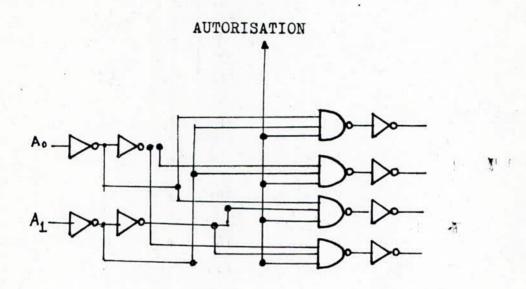

## 4-I Décodeurs:

Comme il a été dit dans les paragraphes précèdents, les décodeurs ligne et colonne ont pour rôle de sélectionner une seule cellule mémoire parmi n autres cellules, et de la préparer ainsi pour un cycle de lecture ou d'écriture.

Vu ce rôle important, on donne un exemple de décodeur I parmi 4 .

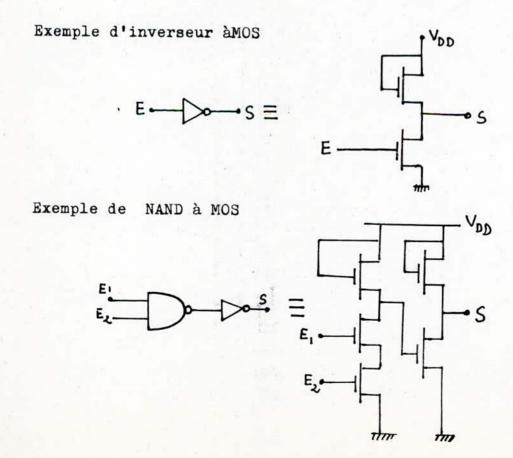

Un décodeur classique est constitué de portes NAND et d'inverseurs facilement concevables à l'aide de la technologie MOS.

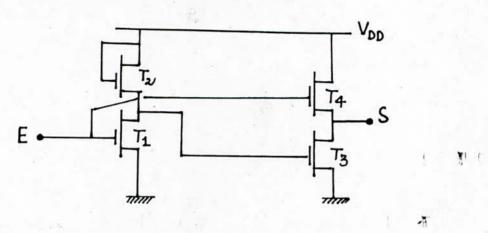

#### 4.2 Buffers

Là où de la puissance est exigèe, pour assurer la com--mande de lignes ou de charges capacitives, par exemple, on utilise une porte de sortie de puissance du type push-pull.

Grâce à l'inverseur, l'attaque de la porte de sortie est assurée en symétrique et lorsque T<sub>3</sub> est conducteur, T<sub>4</sub> EST BEL et bien bloqué, souvent la porte de puissance est appellée "buffer" ce qui désigne aussi bien d'ailleurs une porte-tampon.

## 4.3 Technologie canal N, grille silicium

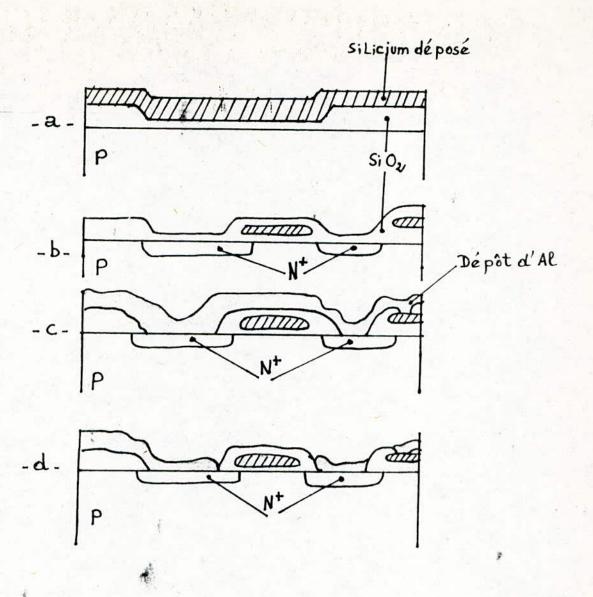

Les principales étapes de réalisation d'un circuit intègré à grille silicium sont données sur la figure ci-dessous et montrent certains des avantages de cette technologie qui l'on faite choisir comme technologie de base des mémoires.

- -La grille en silicium polycristallin est deposée dès le début de la fabrication ce qui protège la zone active des contaminations possibles -La grille autopositionnée par rapport aux diffusions permet de réaliser des dispositifs plus petits et de performances plus elevès (capcitès parasites plus faibles ).

- La couche de silicium polycristallin peut être utilisée comme un noveau supplémentaire d'interconnexion ce qui permet de réaliser des points mémoires très denses;

Actuellement cette couche est aussi utilisée pour faire des résista--nces de charges pour les points memoires statiques (très forte résistivité) et les capacités memoires dans les cellules dynamiques

a/ Croissance de l'oxyde èpais, ouverture des régions de source-grilledrain, croissance de l'oxyde fin de grille, dépôt de silicium polycristallin.

b/ Attaque du silicium des connexions et de grille, diffusion des sour--ces et drain (N<sup>+</sup>), dépêt de l'oxyde de protection.

c/ Ouverture des prises de contact, dépôt d'aluminium .

d/ Gravure de l'aluminium .

# 4.4 Exemple de RAM dynamique

Comme nous l'avons signale au paragraphe 4.3, la technologie la mieux adoptée est la grille silicium canal N à deux niveaux de silicium polycristallin.

Comme exemple de RAM dynamique on cite ici la 16 Kbits, dont les caracteristiques sont données dans le tableau ci-dessous.

| Capacite                             | I6384 éléments binaires    |

|--------------------------------------|----------------------------|

| Technologie                          | Canal N                    |

| Point memoire                        | I seul transistor par bit  |

| Taille de la cellule                 | I4,5 μm x 30 μm            |

| Taille de mémoire                    | 3,10 mm x 5,8 mm           |

| Temps d'accès à la lecture           | I50 nS                     |

| Temps de cycle écriture-<br>-lecture | 250 nS                     |

| Rafraichissement                     | I28 cycles toutes les 2 mS |

| Organisation                         | I6 K x I bit               |

### CONCLUSION

Cette brêve description des RAM utilisant la technologie MOS, montre l'avantage des RAM dynamiques, en effet, bien plus difficiles à utiliser que les RAM statiques, en raison des circuits de rafraîchissement et de l'obligation d'utiliser une horloge, toutes sérvitudes qui implique un strict respect des temps et des signeaux d'enchaînement, les RAM dynamiques offrent cependant:

-Une grande densité d'intégration, il faut noter ici que de nos jours on atteint 512 Kbits de points mémoires par puce et cela va encore continuer la baisse des prix pour ces produits, et à cette grande densité d'intégration s'associe une amélioration des performances des mémoires (en temps d'accés en particulier), par le fait de la diminution des dimensions des composants, entraînant une diminution des capacités parasites.

De plus cette déscription montre que l'amplificateur de lecture et de rafraîchissement est l'élément le plus important à réaliser dans l'élaboration d'une RAM dynamique, car de ses caractéristiques dependent éssentiellement: le temps de lecture, le temps d'écriture, et le rafraîchissement.

### CHAPITRE IV

## VERIFICATION EXPERIMENTALE

### Préliminaire

Pour pouvoir réaliser et tester l'amplificateur de lect--ure de mêmoires dynamiques, deux transistors MOS à canal N sont au moins nécessaires.

Etant donné que nous n'avons pas pu nous procurer les composants discrets en raison de leurs indisponibilité sur le marché, nous avons contournés la difficulté en utilisant un circuit intégré de la serie 4000.

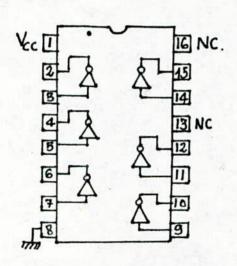

## I/Présentation du circuit intègré

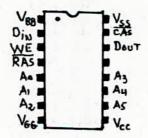

Le circuit intégré que nous avons utilisé est le CD 4049, qui comporte six portes inverseuses conçues en technologie CMOS(c'est à dire à transistors MOS complèmentaires) il possède en outre I6 broches DIL(dual in line).

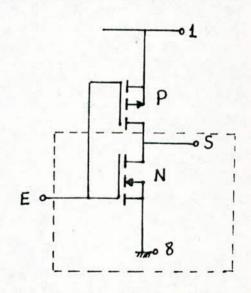

Le schema de brochage du CD4049 est représenté sur la figure ci-deses -sous, ainsi que le schema interne d'une porte inverseuse CMOS

Il est inutile d'expliquer le fonctionnement de cette porte, car comme nous l'avons indique plus haut, nous nous intéressons uniquement aux transistors à canal N que comporte chaque porte.

Notons que le circuit intégré est protègé(grâce à des diodes ) contre les charges éléctrostatiques qui pouraient le détruire, et cela nous procure une certaine liberté de mouvement.

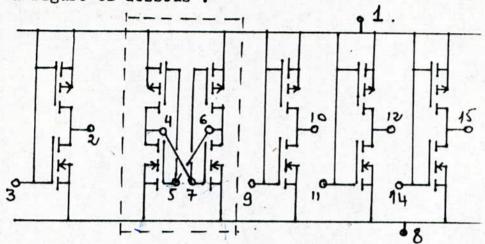

Pour réaliser le montage de l'amplificateur de lecture, on peut utiliser deux portes consécutives, et pour éviter le passage du coura--ant à travers le transistor (P) il suffit de relier toutes les entrèes des portes non utilisées à la broche (I), comme l'indique la figure ci-dessous.

Pour la source de courant commandée, un deuxième circuit intégré est nècessaire car on ne peut pas utiliser une porte du même circuit intègré étant donné que la connexion de masse est commune aux six portes contenues dans ce circuit.

Evaluation des constantes technologique du transistor

Pour comparer les resultats que nous trouverons lors des tests qui vont suivre, avec les resultats théoriques trouvés, ilest nécessaire de caractériser les transistors MOS que nous utiliserons, c'est à dire qu'il faut connaître la tension de seuil  $V_{\rm T}$  ET LA CONDUCTI--VITE spécifique K .

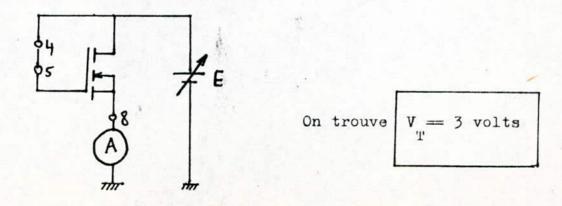

# Mesure de la tension de seuil $V_{\mathrm{T}}$

Pôur mesurer  $\mathbf{V}_{T}$ , il suffit d'alimenter le transistor et de détecter la tension d'alimenta $\mathbf{j}$ ion pour laquelle le transistor devient passant

Mesure de la conductivité spécifique K du transistor

Le montage de mesure est le suivant:

E= 8 volts , I=5,6 mA

R= I K

$$\Lambda$$

,  $V_T$ = 3 volts

$V_{GS}$ = E ;  $V_{DS}$ = E-RI

Grâce à l'expression du courant en régime non saturé, on calcule K CONNAISSANT  $V_{GS}$ ,  $V_{DS}$ ,  $V_{T}$  et I

On a I=K(

$$V_{GS}-V_{T}-V_{DS}/2$$

) x  $V_{DS}$

On trouve K=600  $\mu$ A/ $V^2$

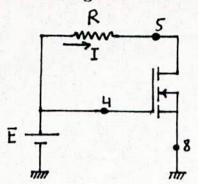

#### 2- MONTAGE EXPERIMENTAL

Pour générer les différentes tensions nécessaires pour éffectuer des mesures sur l'amplificateur de lecture, on a utilisé un montage astable à transistors bipolaires car il est de conception très simple, avec des composants robustes, d'un coût dérisoire et disponibles partout. Pour alimenter les deux noeuds A et B de l'amplificateur de lecture on utilise une sortie de l'astable, et pour faire varier la tension que doit détecter l'amplificateur, on utilise un potentiometre, qui fait varier la différence de tension entre A et B.

L'une des voies A ou B est utilisée pour déclencher l'amplificateur en agissant sur les sources des deux transistors MOS constituants l'amplificateur (cas de la commande par un signal carré).

La deuxième sortie de l'astable (notons que les deux signaux de part et d'autre de l'astable sont en opposition de phases) est utilisée pour commander un autre transistor MOS (canal N), qui sera utilisé comme source de courant lors du test de la commande du montage par un courant constant.

Le schéma final est le suivant :

1 ...

### NOMENCLATURE DES COMPOSANTS

Résistances:  $R_I = I K \Omega$ ;  $R_2 = 5.6 K \Omega$  et  $R_A = 27 K \Omega$

Potentiometre:  $P = 47 \text{ K}\Omega$

Capacités: CA=C= I nF

Transistors: de type 2N1613

Diodes: de type IN4I48

Circuit intégré: CD4049

Tension d'alimentation: E=15 volts

### Remarques :

- Les deux diodes notées(D) sur le schéma, servent à reduire le temps de montée du signal carré.

-Alors que (D<sub>I et</sub> D 2), servent à empécher les capacités C de se décharger à travers T lors de son état de saturation .

3- Commande de l'amplificateur par mise à la masse de la source:

On réalise cette commande en reliant la source à l'anode de la diode  $D_{\overline{1}}$ , les autres connexions etant comme il est indiqué sur le schéma, c'est à dire , le noeud A à la cathode de  $D_{\overline{1}}$  et le noeud B à la cathode de  $D_{\overline{1}}$ .

Grâce au potentiometre P on peut facilement régler l'amplitude de la tension au point B.

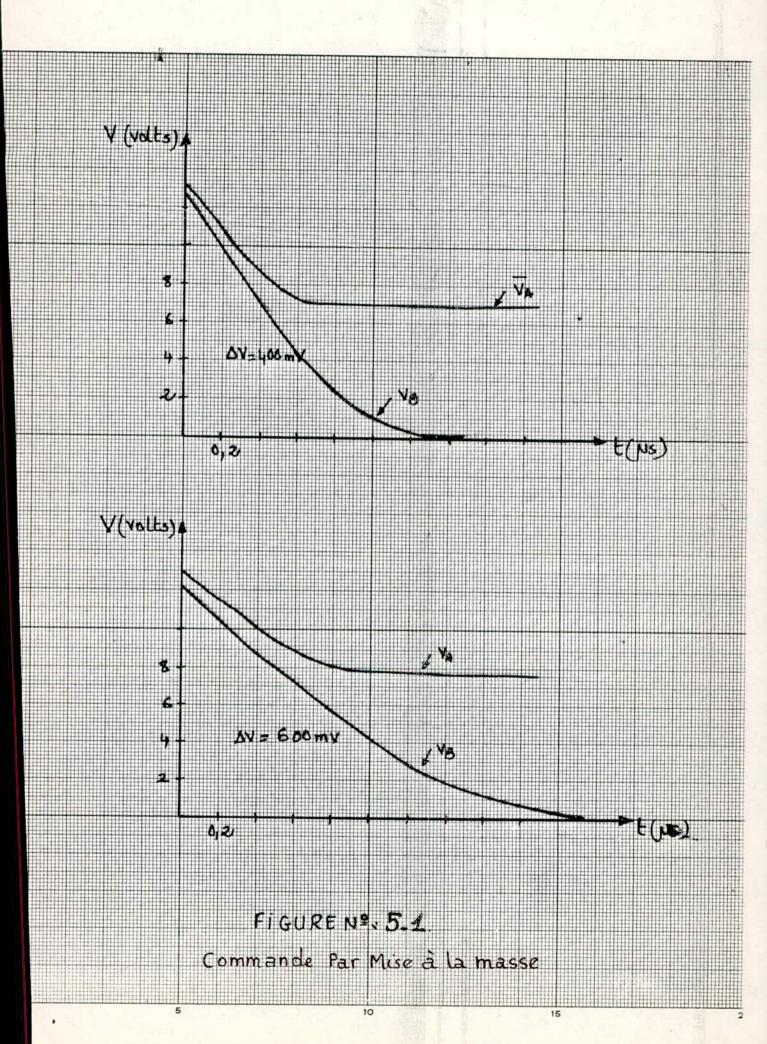

Ayant réalisé ce montage, on a relevé quelques resultats pour des différentes tensions  $\Delta V$  (voir figure 5-I).

Comparaison et interprétation des resultats

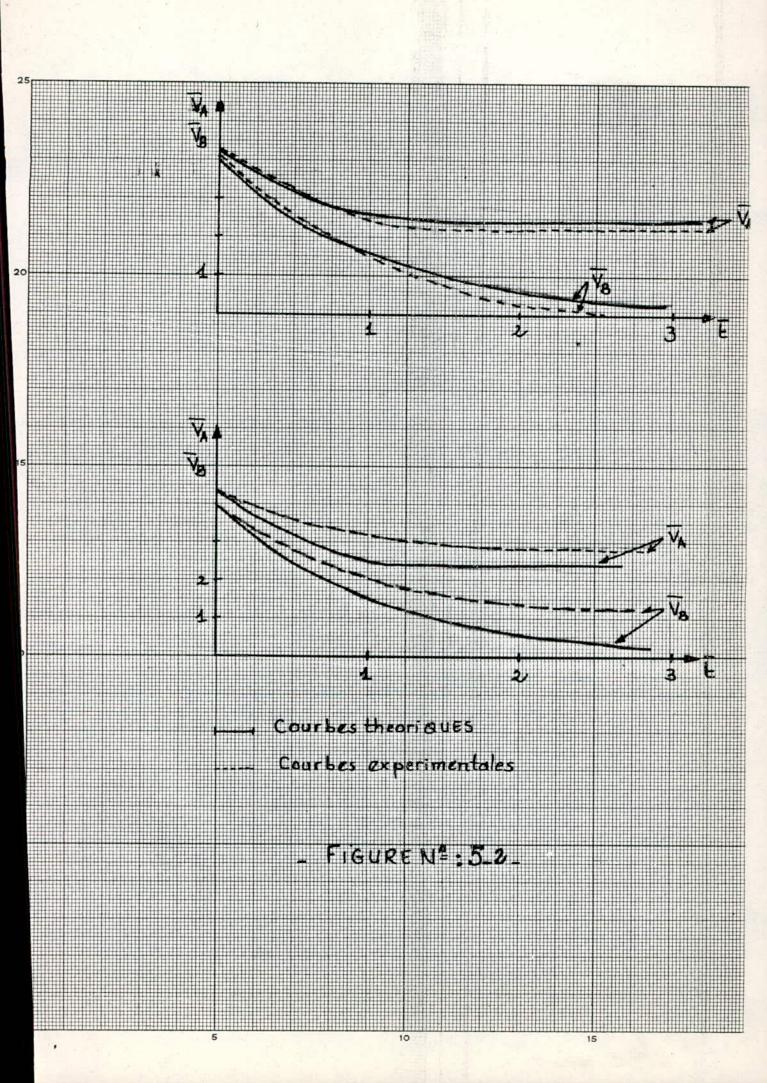

Afin de pouvoir comparer les resultats trouvés experimentalement avec ceux trouvés théoriquement, on doit normaliser les premiers, c'est à dire , les tensions à  $V_T$  et les temps mesurés à la constante  $T=C/KV_T$ , sachant que  $V_T$  vaut 3 volts, C=I nF et K=600 pA/ $V^2$ 8n trouve T=560 ns .

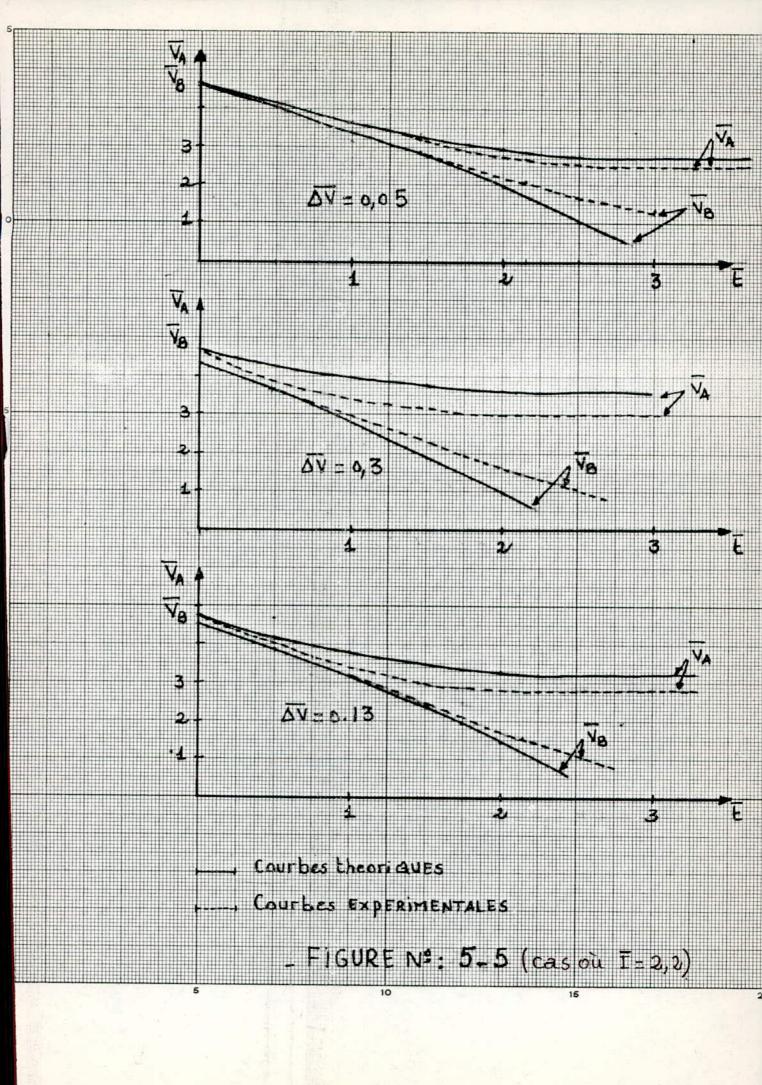

La figure (5-2) donne les courbes tracées à partir des valeurs obtenue s expérimentalement auquel experimentalement auque

### TABLEAUX DE COMPARAISON

-  $\overline{\Delta V}$ =0.13 Approche  $\overline{t}(\text{lecture})$   $\overline{\Delta V}_{A}(\text{chute de tension})$  Théorique 0.92 I.8

1.5

2

expérimentale

| Approche      | t(lecture) | $\overline{\Delta V_A}$ (chute de tension) |

|---------------|------------|--------------------------------------------|

| Théorique     | 0.9        | 1.6                                        |

| Expérimentale | 1.07       | 1.4                                        |

### Commentaires:

Aux érreurs de mesures prés, les resultats expérimentaux concordent assez bien avec les resultats théoriques, ce qui confirme nos conclusions quant à l'attaque de l'amplificateur de lecture par une impulsion rectangulaire, car il apparait bien que le temps de lecture est àpeu prés constant, mais l'amplification resultante varie quand la tension à détécter varie et de plus la chute de tension au point A depasse les I5% de la tension d'alimentation.

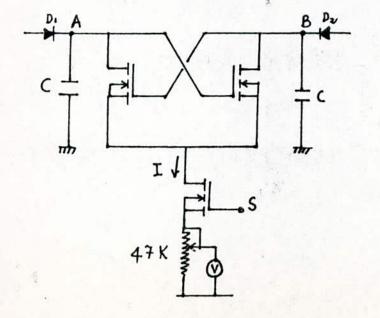

## 4- Commande par un courant constant

La commande est réalisée grâce au deuxième circuit intégré et la seconde sortie de l'astable, de telle maniere QUE lorsque les deux capacités sont en train de se charger , le gate du transistor de commande est à zéro, ce qui permet son blocage (courant nul entre drain et source) et en même temps le blocage des deux transiste -ors constituants l'amplificateur de lecture.

Le potentiometre inséré entre la source du transistor et la masse sert à ajuster l'intensité du courant et la connaissance de sa valeur en même temps (ceci en mesurant la resistance offerte par le potentiometre et la chute de tension à ces bornes) :

Le schéma du montage d'essais est le suivant:

Ayant mis le montage sous tensions, nous avons relevés les courbes pour différentes valeurs de AV et cela pour deux intensités du cou-rant de commande.

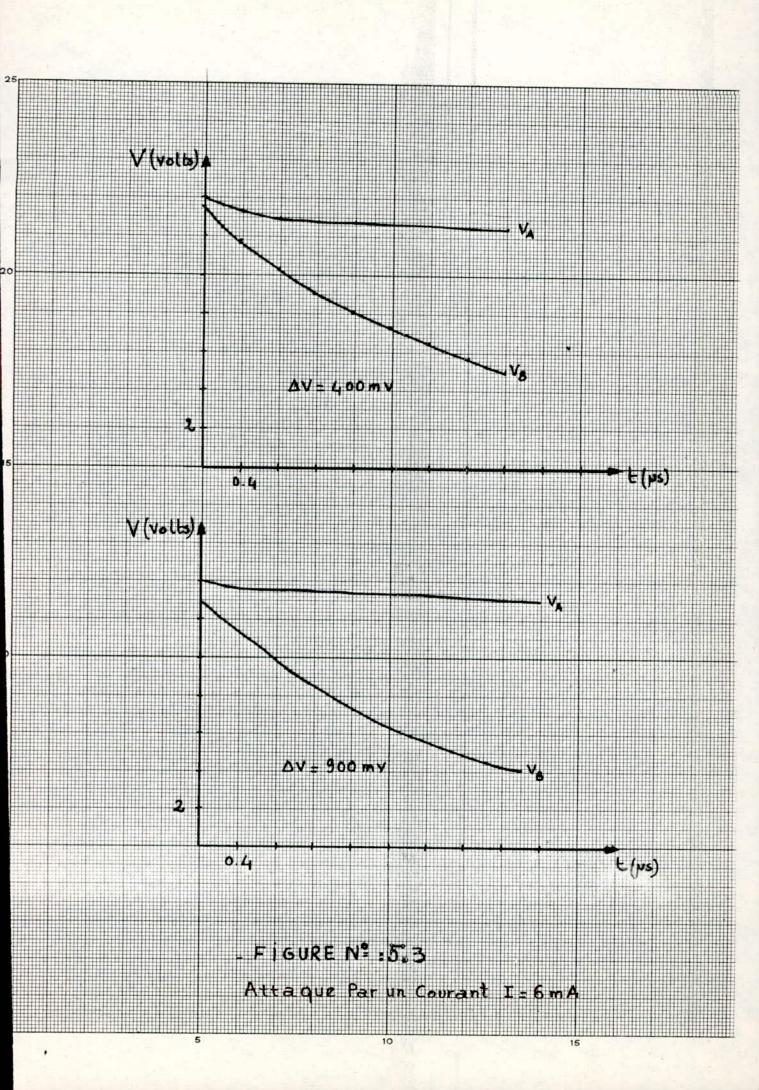

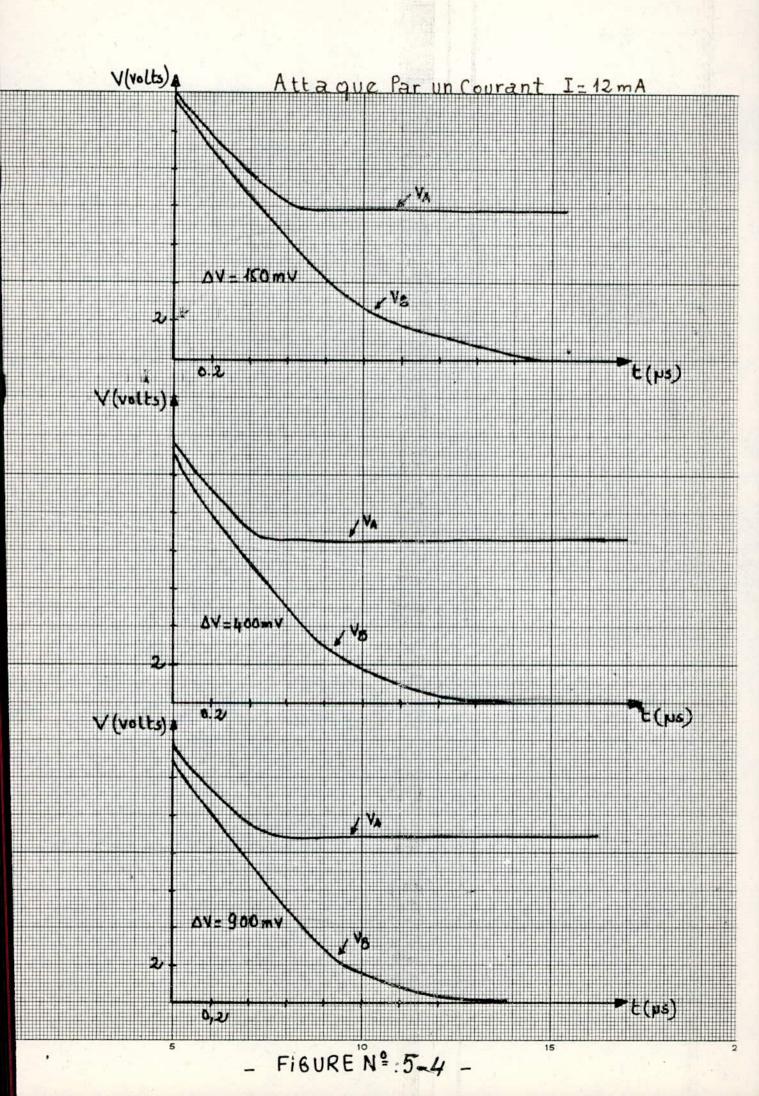

Les figures 5-3 et 5-4 donnent l'allure des courbes pour respectivement I=6 mA et I=I2 mA

Comparaison et interprétation des resultats:

Pour pouvoir comparer les resultats trouvés à ceux \*\* trouvés théoriquement, on a normalisé les tensions à  $V_T$ , l'intensité du courant de commande à  $KV_T^2$  et le temps à  $\mathcal{T}=C/KV_T$ ;

Iercas: intensité du courant de commande I=I2 mA, I=2.2

| - <b>Δ</b> Ψ=0.05 | Approche      | t(lecture) | $\overline{\Delta V}_{A}$ (chute de tension |

|-------------------|---------------|------------|---------------------------------------------|

|                   | Théorique     | 2          | 2                                           |

|                   | Expérimentale | 2.5        | 2.2                                         |

- ΔV=0.13 Appro

| Approche      | T(lecture) | ΔV <sub>A</sub> |

|---------------|------------|-----------------|

| Théorique     | 1.25       | 1.6             |

| Expérimentale | 1.9        | 2               |

-  $\overline{\Delta V}=0.3$

| Approche      | t(Meture) | ΔVA |

|---------------|-----------|-----|

| Théorique     | I         | 1.2 |

| Expérimentale | 1.75      | 1.8 |

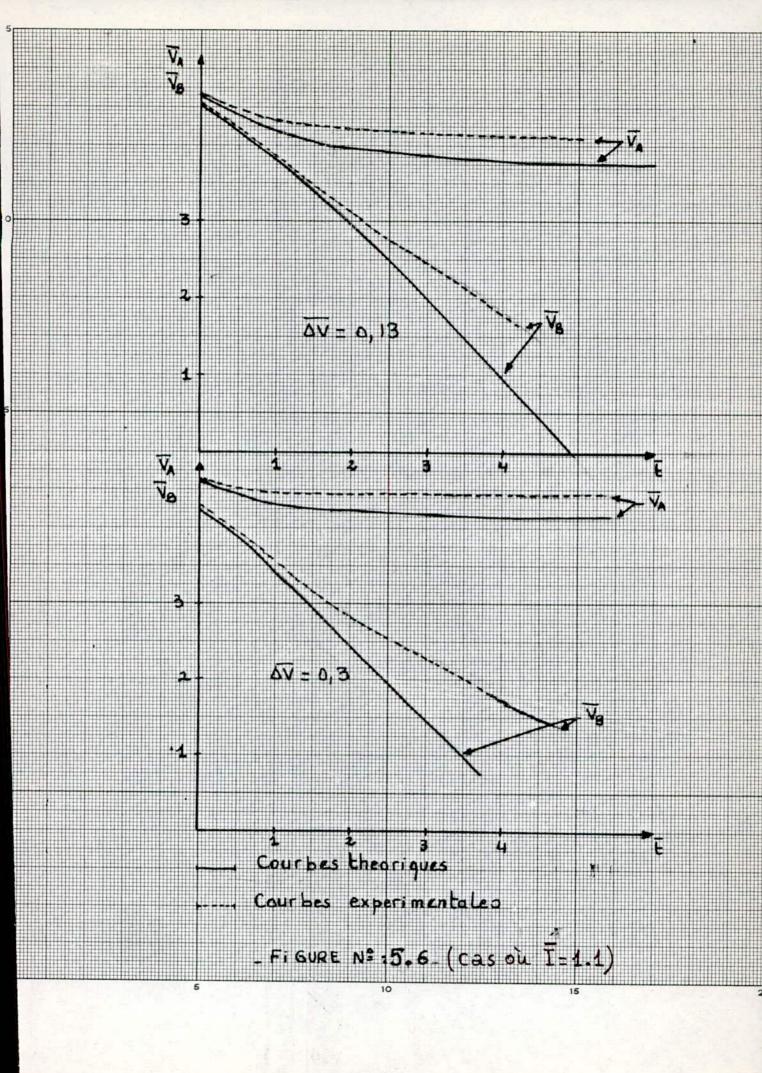

2<sup>éme</sup> cas: intensité du courant de commande I=6 mA , I=I.I

$-\overline{\Delta V}=0.13$

| Approche      | t(lecture) | ΔV <sub>A</sub> |

|---------------|------------|-----------------|

| Théorique     | 2          | 0.9             |

| Expérimentale | 1.8        | 0.5             |

$\Delta V=0.3$

| Approche      | t(lecture) | ΔVA  |

|---------------|------------|------|

| Théorique     | I.45       | 0.45 |

| Expérimentale | 1.2        | 0715 |

Les figures 5-5 et 5-6 donnent les courbes tracées à partir des valeneurs obtenues expérimentalement auquelles on a superposé celles trouvées théoriquement pour respectivement I=2.2 et I=I.I

### COMMENTAIRES

Là aussi l'expérience confirme les resultats théoriques ainsi que les concludions tirées de l'analyse de l'amplificateur, en l'attaquant par un courant constant, entre autre, on peut verificerque le tempé de lecture diminue quand l'intensité de courant de commande augmente et vice-versa; d'autre part, on voit bien que le temps de lecture reste sensiblement constant quand la tension à détecter varie (pour un courant de commande donné).

Notons que pour I=2.2 la chute de tension au point A dépasse lar-gement les 15% de la tension d'alimentation, alors que pour I=I.I cette chute atteint à peine les 4.5%, ce qui limite la valeur de l'intensité de courant pouvant être choisie pour commander l'ampl-ificateur de lecture.

## CONCLUSION

En analysant les resultats obtenus expérimentalement, et on les comparant aux resultats théoriques, on peut à juste titre éstimer que

l'expérience justifie amplement les approximations que l'on a du

faire au cours de la résolution des systèmes d'êquations d'équat-ions différentielles qui régissent le fonctionnement de l'ampli .

Par conséquent les resultats et les enseignements que nous avons

tirés des chapitres précédents sont crédibles. Notons que certains

décalages existent entre les valeurs théoriques et expérimentales.

ces différences proviennent/\_Des érreurs de mesures (inévitables)

dans la détermination des AV, de l'intensité du courant et des par-amétres du transistor, et du fait que le modéle mathématique du

transistor MOS utilisé ne rend pas compte du comportement réel du

transistor (sapproximation du premier ordre ))

Ajoutons à tout cela l'influence des portes non utilisées dans le circuit intégre car celles-ci communiquent au moins par deux point s (broche d'alimentation et broche de masse) et par conséquent faussent (quoique faiblement) les mesures effectuées sur l'amplificateur.

La caractérisation de l'amplificateur de lecture est à présent compléte le schéma tel qu'on l'a vu comporte six transistors :

- Deux transistors isolent l'amplificateur du réseau de cellules mémoires, pendant la phase de lecture.

- Deux autres constituent les sources de courants qui commandent l'amplificateur .

- Les deux restants forment l'amplificateur lui même .

Nous sommes ainsi parvenus à des temps de lectures ( au niveau de l'amplificateur ) de 4 nS, avec des décharges ne dépassant pas les 10% de la tension d'alimentation. Ces performances répondent bien à la dénomination de lecteur rapide de mémoires dynamiques à MOS.

Cependant l'utilisation d'un seul transistor MOS par point mémoire apporte une contribution importante à l'augmentation du niveau d'intégration, mais exige de l'amplificateur d'être très sensible.

La sensibilité de l'amplificateur dépend éssentiellement de la symétrie du montage ( plus celui-ci est symétrique, meilleure est la sensibilité ) et se traduit par une valeur limite de la différence de tension ΔV entre les deux noeuds de l'amplifica-teur, en déça de laquelle la lecture est erronée. Nous avons limité cette valeur à 50 mV dans notre étude, mais il n'est pas exclu qu'une meilleure sensibilité soit éxigée. Cependant les progrés techniques et l'amélioration des procédés d'intégra-tion peuvent apporter des solutions pour rendre le montage plus symétrique.

Hormis le sujet principal, cette thése, nous a permis de nous familiariser avec la technologie MOS, qui constitue à bien des égards la solution actuelle la plus élé-gante (aux yeux de tous les spécialistes) aux problèmes de la mémorisation de

l'information, tant ses avantages offrent de grandes possibilités que ne peuvent

offrir les bipolaires, qui d'ailleurs perdent du terrain dans de nombreuses appli-cations de la microélectronique tels que les microprocesseurs, les mémoires de

grandes capacités, ainsi que là où l'energie doit être économisée (car le MOS

consomme moins) et là où la place disponible est limitée (car le MOS occupe moins

de place que le bipolaire).

Notre étude touche à son terme, et nous ésperons avoir été à la hauteur de la tâche qui nous a été confiée.