وزارة التعليم والبعث العلمي Ministère de l'Enseignement et de la Recherche Scientifique

المدرسية الوطنيية المتعمدة التقنيات ECOLE NATIONALE POLYTECHNIQUE D'ALGER 24

DEPARTEMENT D'ELECTRONIQUE

PROJET DE FIN D'ETUDES

ETUDIE AU CDTA - LABO : SERELEC

DIPLOME D'INGENIEUR

#### THEME

# Etude et Réalisation d'une Centrale de Sécurité

Sujet proposé par : Mr A. BOURKEB

Etudié par :

Melle GUENDOUZ Hassina

Mr BENAKKI Abdelkrim

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

وزارة التعليم والبحيث العلمي Ministère de l'Enseignement et de la Recherche Scientifique

المادرسية الوطنيية المتعمدة التقنيمات ECOLE NATIONALE POLYTECHNIQUE D'ALGER

DEPARTEMENT D'ELECTRONIQUE

PROJET DE FIN D'ETUDES

ETUDIE AU CDTA - LABO : SERELEC

DIPLOME D'INGENIEUR

Sujet proposé par : Mr A. BOURKEB

Etudié par :

Melle GUENDOUZ Hassina

Mr BENAKKI Abdelkrim

#### DEDICACES

- A LA MEMOIRE DE MON PERE TOMBE AU CHAMP D'HONNEUR.

- A MA MERE

- A MA SOEUR ET MON FRERE

- A TOUS MES ONCLES

- A TOUS MES AMIS (ES).

Hakip

A MA FAMILLE ET TOUS MES AMIS (ES).

#### R EMERCIEMENTS

Nous tenons d'abord à exprimer notre entière gratitude à nos parents pour leur sacrifice et leurs encouragements.

Nous exprimons notre reconnaissance à tous les **Pro** fesseurs ayant contribué à notre formation.

Nous remerçions M. A. BOURKEB pour nous avoir accepté au sein de son laboratoire ou règne une ambiance **sy**mpatique, et pour l'aide qu'il nous a fourni.

Nos sincères remerciements vont aussi à M. SAIDJ pour sa gentillesse et les conseils utiles qu'il nous a donnés.

Que tout le personnel du laboratoire d'électronique du CEN trouvent ici l'expression de notre pleine reconnaissance pour leur aide aussi petite soit-elle.

- INTRODUCTION : 1) Nécessité des systèmes de sécurité

- 2) Généralités sur les systèmes de sécurité

- 3) Organisation du système de sécurité proposé

### CHAPITRE I/ - Structure de la Centrale de Sécurité.

- I Etude et réalisation de la Carte Unité Centrale.

- I 1 Constitution et rôle de la carte Unité Centrale

- I 2 Etude des composants du module MPU

- I 21 Microprocesseur MC 6800

- I 22 Horloge MC 6871 A

- I 23 Circuits d'extension.

- I 3 Logique de commande et de contrôle

- I 31 Circuit de lecture et d'écriture

- I 32 Circuit de reinitialisation automatique

- I 33 Circuit de raffraichissement dynamique

- II Etude du Système de Visualisation .

- II 1 Composants de ce système

- II 2 Etude de la carte de visualisation

- II 3 Mode de visualisation d'un texte

- II 4 Traitement de l'information avant visualisation.

#### III Unité de Stockage.

- III 1 Nécessité d'une unité de stockage

- III 3 Constitution de l'unité de stockage.

## CHAPITRE II / Mode d'Echange d'information entre la Centrale et les Zones.

- I 1 Rôle de la Carte Interface ACIA

- I 2 Rappels sur l'ACIA et la Norme RS 232

- I 3 Mode d'Echange d'informations

- I 4 Détails sur le mode d'échange.

II Simulation

#### CONCLUSION:

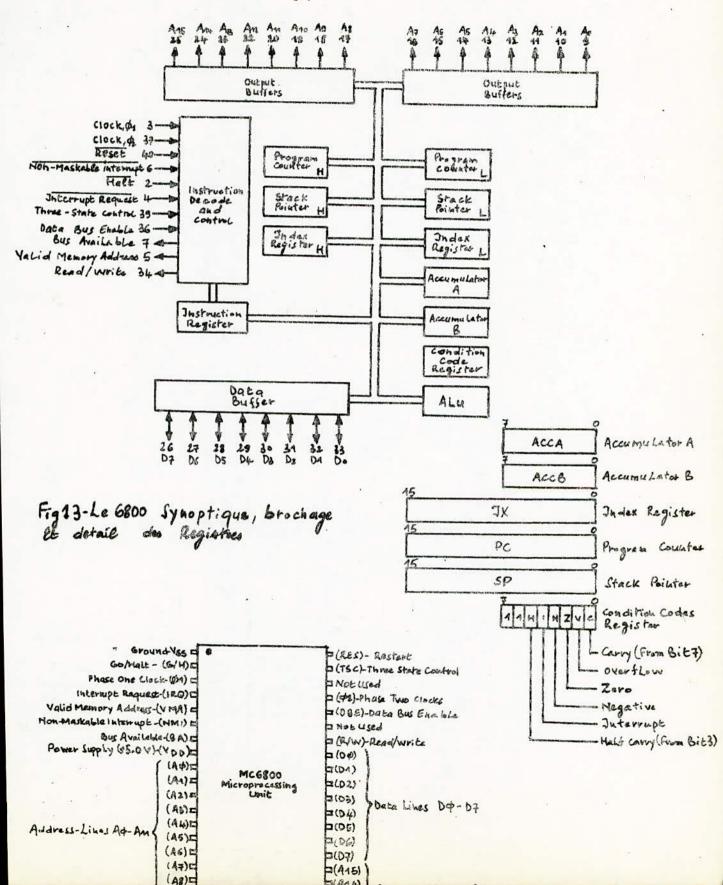

ANNEXE: - MC 6800 (Brochage, Synoptique)

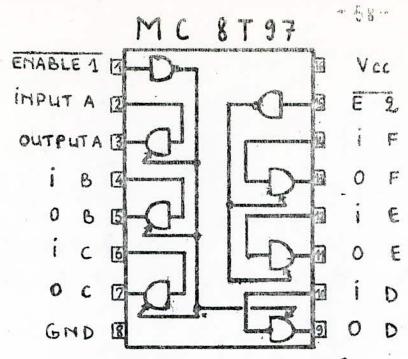

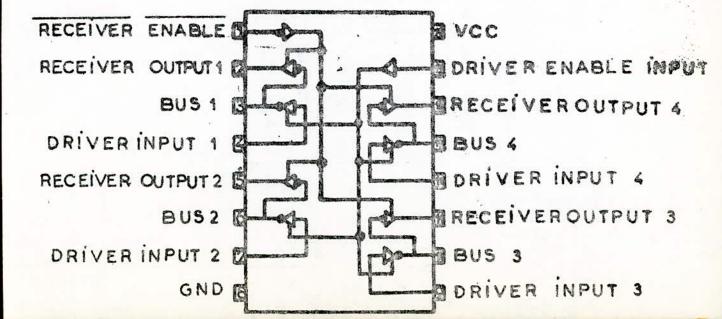

- MC 8 T 97, MC 3 T 26 (brochage, table de vérité)

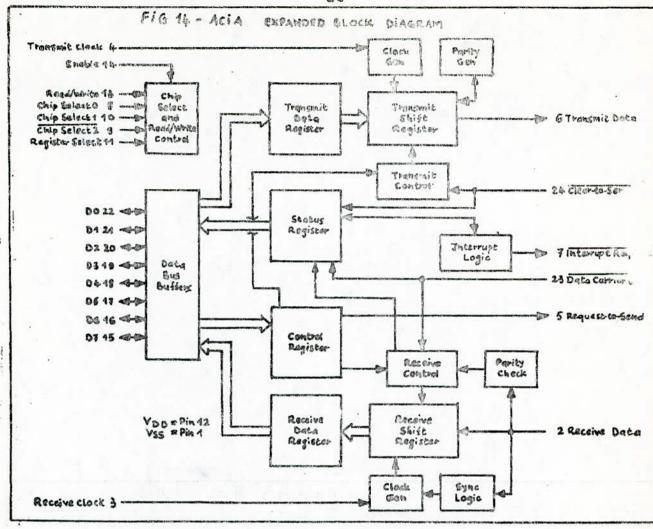

- 1'ACIA (MC 6850)

- Principe de fonctionnement du Monostable MC 1455 (RESTART AUTOMATIQUE)

- Programme de simulation

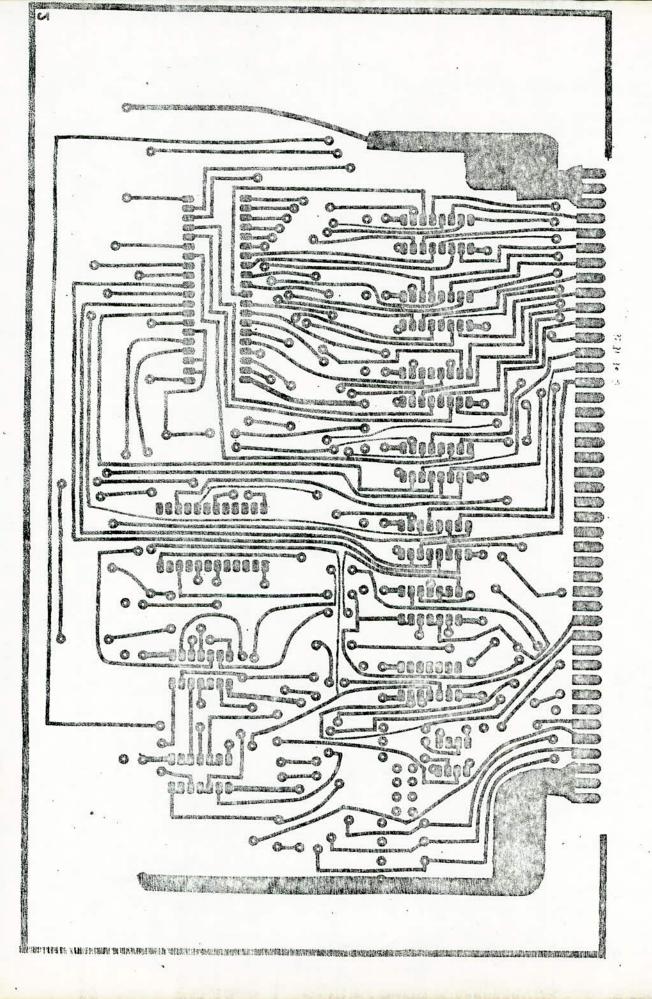

- Les 2 Faces du circuit imprimé (MPU).

## I NTRODUCTION

#### 1) = NECESSITE DES SYSTEMES DE SECURITE /

L'utilisation d'installations et équipements de plus en plus onéreux par les techniques modernes, ainsi que la protection du personnel opérant dans un milieu dangereux, imposent des dispositifs de sécurité efficaces et souvent d'une grande complexité.

Ainsi au Commissariat aux Energies Nouvelles (CEN), ou se déroulent des expériences mettant en jeu des réactions nucléaires (radio activite &, B, rayons gamma, neutrons), un intérêt particulier est accordé à ce genre de dispositif.

Dans ce sens, le laboratoire d'électronique du CEN nous a confié l'étude et la réalisation d'un système de sécurité centralisé basé sur une technique de micro processing.

#### 2) = GENERALITES SUR LES SYSTEMES DE SECURITE :

Un système de sécurité doit répondre aux critères suivants:

- Fiabilité

- Rapidité

- Efficacité

- Faible consommation

- Souple d'utilisation.

Il existe différents types de systèmes de sécurité, certains font appel à des méthodes très simples et rudimentaires (par exemple : un fusible, une alarme antivol necessitant juste une logique, un système à contact, à relais etc...).

D'autres par contre, plus évolués, nécessitent une saisie de données suivie d'un traitement et d'une décision (commande) d'ou opportunité de l'utilisation du microprocesseur.

De partsa souplesse d'utilisation et sa fiabilité, le microprocesseur représente le moyen le plus rapide et le plus sûr pour les applications en temps réel.

Un système centralisé mermet de converger les différents types de détection vers un dispositif unique de réception, de traitement et de réaction.

L'orientation vers le microprocesseur pour la réalisation de ce système nous paraît évidente.

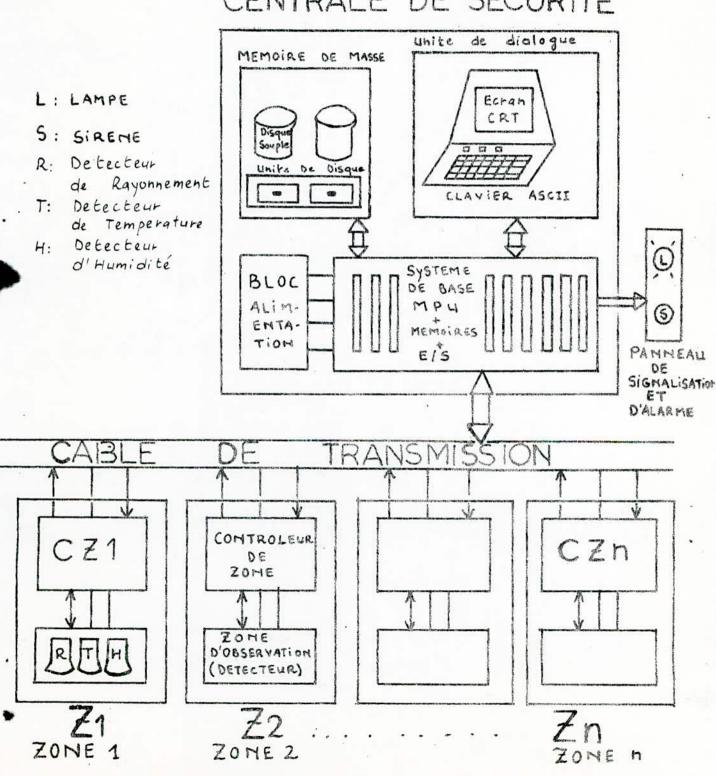

#### 3) = ORGANISATION DU SYSTEME DE SECURITE PROPOSE :

#### \* (A) Problème posé:

Ce système de sécurité centralisé a été conçu pour répondre aux objectifs suivants :

- celui du contrôle de l'acheminement des informations des zones vers la centrale de sécurité.

- d'informer sur le niveau de sécurité de chaque zone.

Pour cela, la centrale de sécurité doit donner à chaque instant l'état de plusieurs zones et actionner les commandes adéquates.

Différents détecteurs sont placés au niveau de chaque zone.

Toute détection d'anomalie sera recensée par un "Contrôleur de zone" et envoyé à la centrale qui décidera de la situation. (Un ACIA permettra le dialogue entre la Centrale et chaque zone).

Pour s'affranchir des problèmes d'adaptation de niveau dû à l'éloignement, on applique aux niveaux électriques des signaux échangés la norme "RS 232" (ou V 24) adapté à cette liaison série asynchrone.

Notre travail se limite à l'étude et la réalisation d'une centrale de sécurité.

Le plan d'étude comporte deux parties :

- une partie Hardware qui consiste en une mise au point de la centrale.

- la partie software qui se résume en une simulation.

#### \* (B) Intérêt d'une centralisation :

Une centralisation permet :

- D'avoir d'un seul coup d'oeil une vue d'ensemble sur le niveau de sécurité général du centre.

- De décider, de déclencher et de coordonner les réactions dans un minimum de temps.

1 . . .

- De gagner de la place en regroupant les alarmes et de mieux les protéger.

- D'accélérer les dépannages et la maintenance car tous les matériels sont regroupés au même endroit.

Cependant, une centralisation peut parfois entrainer des coûts d'équipements élevés.

Pour éclaireir tout ce qui a été enuméré, un schéma sur l'organisation du système de sécurité est donné par la fig. 1.

## ORGANISATION DU SYSTEME DE SECURITÉ (FIG 1)

## CENTRALE DE SECURITÉ

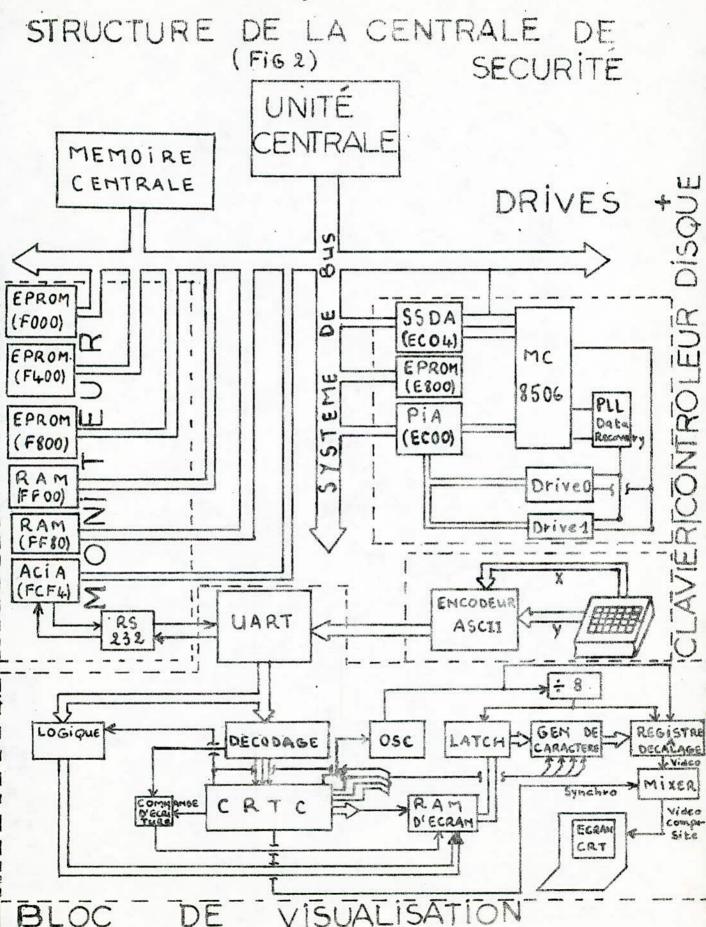

#### CHAPITRE I : STRUCTURE DE LA CENTRALE DE SECURITE :

#### La centrale de sécurité comprend :

- Une carte unité centrale permettant le traitement des informations associée à une carte contenant un moniteur de base résidant en mémoire morte (EPROM), ainsi qu'un ACIA réalisant la liaison avec l'unité de dialogue (clavier + Ecran CRT + Module de visualisation).

- Une carte permettant la visualisation d'un texte sur écran associée à une consôle de visualisation et un clavier ASCII.

- Une carte contrôleur disque en liaison avec deux lecteurs de disques souples (ou Drives).

- Deux cartes mémoires Dynamiques ayant chacune une capacité de 16 K bytes, représentant la mémoire de travail du microprocesseur.

Elle a essentiellement pour rôle de stocker des programmes en cours d'exécution, et des données en cours de traitement

- Une carte interface entre la centrale et les différentes zones comprenant autant d'ACIA que de zones à surveiller.

- Une alimentation + 5 Volts et + 12 Volts pour les différentes cartes.

Toutes ces cartes s'enfichent sur des connecteurs standards reliés à une "carte mère" ou "carte Bus Fond de Panier".

Sur ces connecteurs sont présents tous les signaux composants le bus d'adresse, de données et de commande, ainsi que, des signaux supplémentaires nécessaires au fonctionnement de certains modules comme le module mémoire Dynamique.

Parmi ces signaux, ceux qui réalisent les raffraichissements tels que (RR, RG) et d'autres pour la synchronisation avec les mémoires lentes tels que (MR, MC) etc...

- Une alimentation + 24 Volts, pour les unités de disques souples.

Et enfin un pupitre support de tous les modules qui ont été cités.

Un schéma synoptique de la centrale est donné par la fig;2.

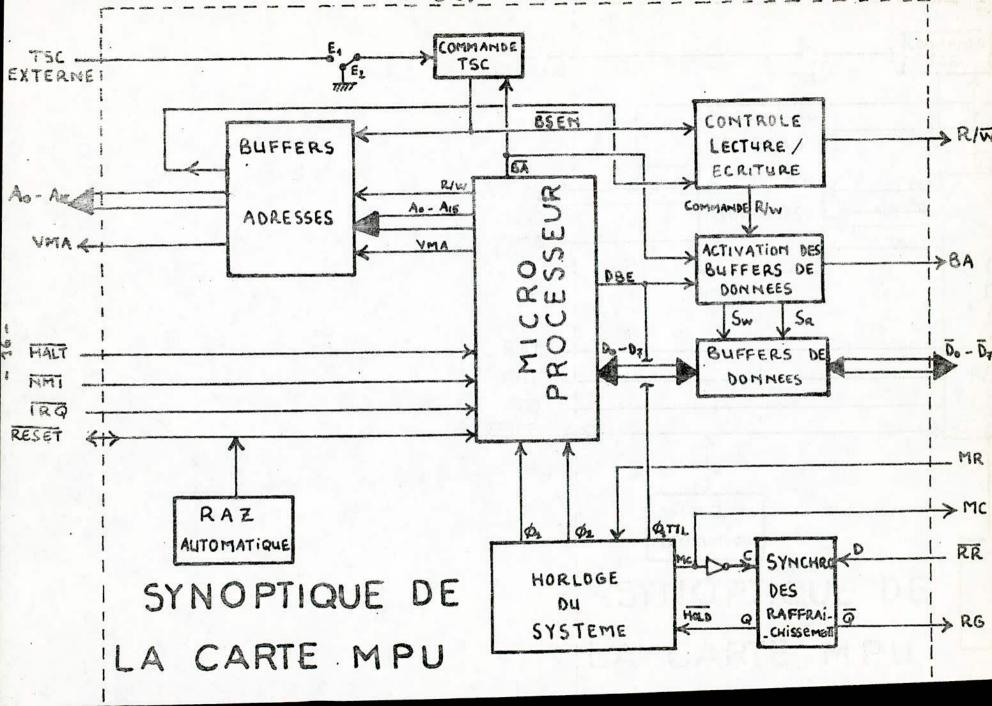

## I - ETUDE ET REALISATION DE LA CARTE UNITE CENTRALE

#### I - 1 Constitution et rôle de la carte unité centrale :

Le module MPU comprend une unité centrale (MC 6800).

Une horloge associée (MC 6871 A) ainsi que des circuits d'extension(amplificateurs de Bus MC 8 T 26, MC 8 T 97) assurant le raccordement sur le bus système ou pourront être connectés d'autres cartes.

Une logique de contrôle et de commande de ces amplificateurs de bus.

Un circuit (Monostable MC 1455) permet un Restart automatique (Demarrage du systèmé) après mise sous tension.

Et enfin un circuit de raffraichissement de mémoire dynamique. Ce module permet sous contrôle de programmes stockés en mémoires, et au rythme des impulsions d'horloge, de réaliser un certain nombre d'opérations (traitement, gestion de mémoires et des organes d'entrées/sorties).

Un schéma synoptique de ce module est fourni par la fig. 3.

#### I - 2 Etude des Composants du module MPU :

#### I 21 Le microprocesseur MC 6800 :

Le MC 6800 est un produit de la deuxième (2ème) génération (74 - 75) dont les caractéristiques sont connues, nous citerons briévement les points essentiels.

En annexe est fourni le brochage et l'organisation interne de ce microprocesseur.

Le MC 6800 réalisé en technologie N MOS necessite une tension d'alimentation (+ 5 Volts) et sa consommation varie autour de 0,25 W.

Les caractéristiques électriques externes sont compatibles TTL.

Il travaille à une fréquence de 1 MHZ et dispose pour son logiciel de 72 instructions différentes dont chacune peut être définie selon un ou plusieurs modes d'adressage.

Les échanges avec l'extérieur se font par l'intermédiaire de bus, on distingue :

- -- Un bus données : bidirectionnel permettant une capacité de traitement de 8 Bits.

- Un bus adresse: Unidirectionnel disposant de 16 Bits capables d'adresser 64 K octets (1 K OCTET = 1024 Octets).

- Un bus de contrôle : qui englobe les signaux suivants :

#### a) les signaux sortants :

- \* VMA (Valid Memory Adress) = A l'état haut, indiqué aux circuits périphériques qu'il y ' a une adresse valide sur le bus adresse (généralement utilisé pour la sélection de circuit).

- \* BA (Bus Available): Cénéralement, il est à l'état bas, à l'état haut, il indique que le microprocesseur est à l'arrêt et le bus adresse est disponible. Ceci, arrive quand la ligne HALT passe à 0 ou quand le microprocesseur est dans l'état WAIT (attente d'interruption).

- \* DBE (Data Bus Enable) : A l'état haut, indique que les sorties du Bus données sont disponibles.

#### b) Signaux entrants:

- \* RESET : Sert à mettre à l'état initial et demarrer le système.

- \* IRQ : A l'état bas, indique une demande d'interruption au microprocesseur.

- \* NMI : Demande d'interruption non masquable donc prioritaire par rapport à IRQ.

\* HALT: A l'état bas arrête le microprocesseur (sans agir sur son horloge) en le deconnectant du bus système, le signal BA sera mis à 1 et le signal VMA à 0. Il est utilisé pour des applications necessitant une DMA (Direct Mémory Access.).

#### I 22 Horloge MC 6871 A :

Le MC 6800 ne dispose pas de génerateur d'horloge interne, aussi il doit être piloté par un oscillateur externe qui délivre deux signaux de fréquence identique mais déphasés et sans recouvrement (Ø1, Ø2).

Le MC 6871 A renferme un quartz et un oscillateur donnant une fréquence de 1 MHZ les signaux générés par cette horloge sont :

- Ø1 et Ø2 (N MOS) : nécessaire au MC 6800

- $\emptyset$ 2 (TTL) : nécessaire aux éléments de support et à la logique de commande inhérente.

- MR (Memory Ready) cette commande prolonge l'état haut de Ø2 (ou bas de Ø1), c'est un signal de synchro dans le cas d'utilisation de mémoires lentes.

Lorsque le MPU adresse une mémoire lente (temps d'accés supérteur à celui autorisé), le circuit d'horloge reçoit un niveau haut (1) sur l'entrée MR. L'horloge maitient alors Ø1 (N MOS) et Ø2 (N MOS) dans l'état respectif O et 1. Après reconnaissance d'adresse, la mémoire agit en conséquence sur MR (le met à O) pour que le microprocesseur puisse se synchroniser sur son propre rythme.

Le prolongement de Ø2 à 1 ne doit pas dépasser 9 s pour assurer le raffraichissement des registres internes du microprocesseur.

- MC (Memory Clock): Signal de sélection de mémoire

- 2 Fc : 2 fois la fréquence d'horloge

- Hold: Permet de prolonger l'état haut de Ø1 (N MOS). Il sert pour le raffraichissement des mémoires dynamiques et la DMA par vol de cycle.

/ . . .

I 23 Circuits d'extensions : (Amplis de bus ou Buffers) :

La sortance des circuits N MOS étant limitée

à 10 entrées de la même famille; il est nécessaire de placer

des circuits d'extensions de bus (ou Ampli de Bus). Ces circuits sont à trois (3) états permettant ainsi une deconnection du microprocesseur pour les applications DMA.

En fonctionnement normal, les amplificateurs du Bus adresse et commande sont actifs en permanence. Par contre les amplificateurs du bus de données nécessitent une logique de commande en lecture ou écriture afin de déterminer le sens de transfert des informations. Le rôle essentiel de ces circuits est d'amplifier en courant les signaux issus du microprocesseur.

I 231 : Interface Adresse (MC 8 T 97) (Voir brochage et table de vérité en annexe).

Les lignes d'adresse étant au nombre de seize (16) et unidirectionnelles on a besoin de trois buffers 8 T 97 (chacun ayant une capacité de 6 Lignes). Ces circuits sont munis de la possibilité d'être mis en haute impedance soit directement par TSC (Three state control), soit indirectement par Halt qui met la sortie BA à l'état Haut (1)

#### (a) - Circuit de contrôle trois états (TSC):

Le microprocesseur est muni d'une entrée TSC (brôche 39) qui est mise à la masse pour assurer son fonctionnement.

Un circuit de contrôle 3 états (TSC) est commandé par le microprocesseur (BA) en agissant sur Halt et par un signal externe TSC.

Lorsque le TSC est à 1, le bus adresse et la ligne  $R/\bar{W}$  sont à l'état haute impedance. Toute opération est donc interdite.

Pour permettre le fonctionnement du MPU, il faut que le TSC externe soit à la masse (Ceci est réalisé par un strap).

#### (b) - Signal d'activation de l'interface adresse : (BSEN) :

| TABLE | DE | VERITE | • | BA | : | TSC (extern | e) : | BSEN |

|-------|----|--------|---|----|---|-------------|------|------|

|       |    |        |   | 0  |   | 0           | :    | 1    |

|       |    |        |   | 0  | : | 1           | :    | 0    |

|       |    |        |   | 1  |   | 0           |      | 0    |

|       |    |        |   | 1  |   | 1           |      | 0    |

: BSEN = TSC BA :

REMARQUES: Par action conjointe sur TSC il faut agir sur le générateur d'horloge (sur Ø1 et Ø2 pour les maintenir à 1 et 0) si l'on veut faire de la DMA.

Seulement, cette DMA est limitée par le raffraichissement nécessaire aux registres internes du micro, cependant, elle réalise des transferts avec un bon temps de réponse.

I 232 Interface Données (MC 8 T 26) (voir brochage o

## I 232 Interface données (MC 8726) (Voir brochage table de verité en annexe):

Dans un ordre de lecture les données sont entrantes et dans un ordre d'écriture, les données sont sortantes.

Les interfaces de données doivent être bidirectionnels, le nombre de lignes de données disponibles par boitier est de huit (8) donc deux 8 T 26 suffisent.

#### I 3 - Logique de Commande et de contrôle :

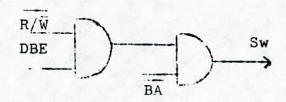

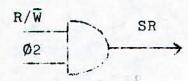

#### I 3.1 Circuit de lecture écriture :

Ce circuit reçoit un ordre de lecture ou d'écriture et autorise une entrée ou une sortie de données en agissant sur les interfaces de données.

a) Opération d'écriture : (sortie de données).

Signaux à validés :

$$(R/W = 0)$$

$(DBE (OU Ø2) = 1)$

$(BA = 0)$

$SW = R/\overline{W}$  DBE BA

Vers la commande d'activation du sens sortant des Buffers de données.

#### b) Opération de lecture : (entrée de données)

Signaux à validés

$$(R/\overline{W} = 1)$$

$(\emptyset 2 = 1)$

Vers la commande d'activation du sens entrant des Buffers de données.

$$SR = R/W.Ø2$$

Dans le cas des 8 T 26, le signal d'activation de l'entrée des données doit être au niveau bas. Le signal SR doit être inversé et le buffer sera attaqué par  $\overline{SR}$ .

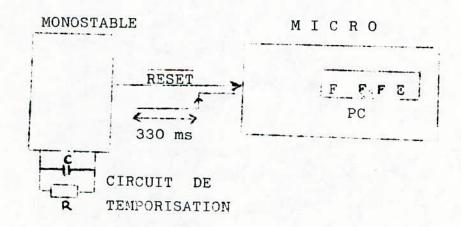

#### I 32 Circuit de Reinitialisation automatique :

Après chaque mise sous tension de l'appareil

1 . . . .

et quand le niveau minimum de tension requis  $(4,75\ V)$  est atteint, le microprocesseur en recevant un signal  $\overline{\text{RESET}}$  de niveau logique O execute une routine d'initialisation.

Un circuit conçu autour d'un monostable (MC 1455) permet de réaliser un RESTAFT automatique, la durée de l'impulsion RESET dépend de deux composants de temporisation (R et C).

La durée de l'impulsion RESET est  $t=1,1\ T=1,1\ RC$  elle est calculée de telle façon qu'elle assure une routine complète de reinitialisation (t=330MS).

Le schéma interne, et les circuits externes associés au monostable MC 1455 ainsi que les chronogrammes et son principe de fonctionnement sont donnés en annexe.

Une reinitialisation manuelle est fournie par la carte moniteur associé à la carte unité centrale.

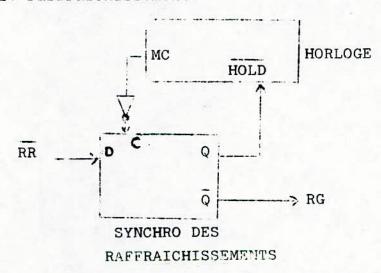

- I 33 Circuit de Raffraichissement Dynamique :

- a) Nécessité des raffraichissements :

L'utilisation des mémoires RAM Dynamique necessite un circuit de raffraichissement.

Les mémoires RAM dynamiques stockent des bits d'information comme des charges de condensateurs. Une capacité est nécessaire pour chaque bit, une opération de lecture décharge la capacité.

Une reecriture est donc nécessaire pour préserver le contenu de la RAM, mais les fuites dans les circuits MOS déchargent la RAM en quelques ms. Ainsi la charge doit être restaurée toutes les 2 ms : c'est le raffraichissement de la RAM.

Les RAM dynamiques sont en général utilisés pour des applications nécessitant des capacités mémoires importantes (plus de 8 K bytes) vu leur faible consommation.

#### b) Principe de fonctionnement :

La demande de raffraichissement est formulée à l'aide de la commande RR (Refresh request), RR est synchronisé avec le signal MC au moyen d'une bascule D, dont la sortie Q attaque l'horloge sur son entrée Hold.

Le raffraichissement n'ayant lieu que si les mémoires sont au repos, donc pendant Ø2 à l'état bas. si la demande de raffraichissement est prise en compte, la bascule D de synchro renvoie par l'intermédiaire de sa sortie Q un signal RG (Refresh Grant) autorisant ainsi le raffraichissement.

AUTORISATION DES RAFFRAICHISSEMENTS

RG

| RR<br>4C | 0 | 1 |           |

|----------|---|---|-----------|

| 0        | 0 | х |           |

| 1        | 1 | x | I minutes |

RG

#### II - ETUDE DU SYSTEME DE VISUALISATION DE LA CENTRALE :

La centrale de sécurité est dotée d'un terminal vidéo permettant la visualisation de l'état de chaque zone où sont placés les différents détecteurs.

La visualisation d'un texte sur écran est gérée par un processeur spécialisé (CRTC).

La mémoire RAM d'écran ne fait pas partie de la mémoire centrale. L'unité centrale se trouve ainsi dégagée des tâches de gestion de la visualisation.

#### II 1 <u>Composants de ce système</u> :

Le système de visualisation comporte :

- un clavier ASCII permettant de coder l'information devant être traitée et visualisé.

Il se subdivise en deux parties :

- a) Un générateur de code ASCII formant la partie électronique (Encodeur).

- b) Les touches du clavier ainsi qu'un bouton poussoir du type inverseur pour le Restart manuelle, un autre inverseur I lpour la sélection du mode de travail de la centrale (en local ou en Line), et enfin un interrupteur permettant de choisir deux vitesses de transmission (V1 ou V2), cet ensemble formant la partie mécanique du clavier.

- Une carte permettant d'établir la comptabilité entre les entrées/Sorties (E/S) du processeur et du périphérique (clavier - consôle de visualisation).

- Un écran TV avec une entrée vidéo.

L'unité de dialogue (cad le clavier + la carte de visualisation + écran TV) assure dans notre cas, l'échange d'onformations (conversation) entre l'opérateur et le microprocesseur.

#### II 2 Etude de la Carte de Visualisation :

Par la suite on expliquera comment se font ces échanges, pour le moment nous essayerons de mettre en évidence le rôle de chaque élément de la carte de visualisation. Celle-ci comporte :

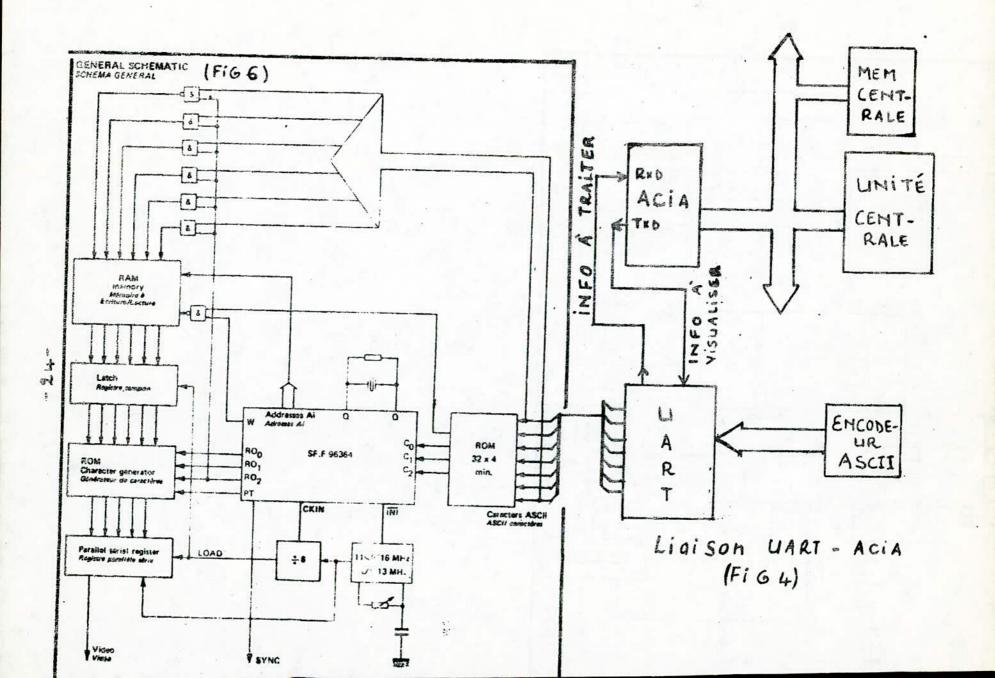

- A l'entrée un élément (UART : Universal Asynchronous Receiver Transmitter) permettant la conversion parallèle série des informations arrivant du clavier, pour être acheminées vers l'unité centrale (pour un éventuel traitement et chargement en mémoire centrale), et série parallèle des informations arrivant de l'unité centrale (transitant par ACIA) pour être visualisés sur écran TV. Un schéma fonctionnel est donné par fig. 4.

- Une EPROM de decodage (MCM 2708 de 1 K x 8 Bits).

Chaque caractère ASCII est codé sous forme de 4 Bits co, c1, c2, c3 représentant les 4 bits de poids faible du bus de données (Do = C0, D1 = C1, D2 = C2, D3 = C3) les 4 autres bits de poids fort étant à la masse.

Donc 128 bytes (octets) seulement parmis les 1024 disponibles sont utilisés vu le nombre de caractères ASCII à

coder, la combinaison des 4 bits (CO, C1 C2, C3) permet de reconnaitre les différentes touches du clavier comme étant :

- \* soit un caractère à visualiser

- \* soit un mouvement du curseur

- \* soit une information à ignorer

- Le CRTC (SFF 96364) circuit réalisant le rôle de contrôleur d'écran, ses fonctions sont les suivantes :

- \* Génération de la synchronisation TV (standard CCIR 625 lignes).

- \* Raffraichissement de l'écran.

- \* Gestion complète du curseur

- \* Balayage des lignes de caractère (par l'intermédiaire du compteur de visualisation intégré dans le CRTC).

- \* Commande de lecture et d'écriture par la sortie W (broche 17).

- \* Blanchissement de ligne ou de page (grâce à RO2 du compteur de visualisation).

- \* Affichage de 1024 caractères sur écran sous forme de 16 lignes de 64 caractères.

- \* Enchainement de plusieurs pages.

- Deux mémoires RAM pour le raffraichissement de l'écran (2114 de 1 K x 4 Bits). Elles permettent le stockage de 1024 caractères affichables sur l'écran.

Un circuit tampon ou LATCH (SN 74100) qui verrouille ou libère l'information presente à ses entrées suivant que le niveau de l'entrée horloge soit respectivement à 1 ou 0.

- Une EPROM (MC 2708): Formant le générateur de caractères. Pour un caractère du code ASCII présent sur les 7 Bits de poids fort du bus adresse de l'EPROM, les 3 Bits de poids faible sont attaqués par les sorties du compteur de visualisation (ROO, RO1, RO2) qui balayera les huit combinaisons. Donc un caractère du code ASCII occupera 8 positions mémoire (8 octets).

Ces 8 bytes génèrent les signaux nécessairement à la representation du caractère sur écran.

- Un registre à décalage (SN 74 165) permettant de serialiser l'information presente à son entrée (information issue du bus donnée de l'EPROM Générateur de caractères), afin de la transmettre à l'entrée vidéo du récepteur TV.

- Un Baud rate (14 411) permettant de sélecter la vitesse de transmission compatible avec le périphérique.

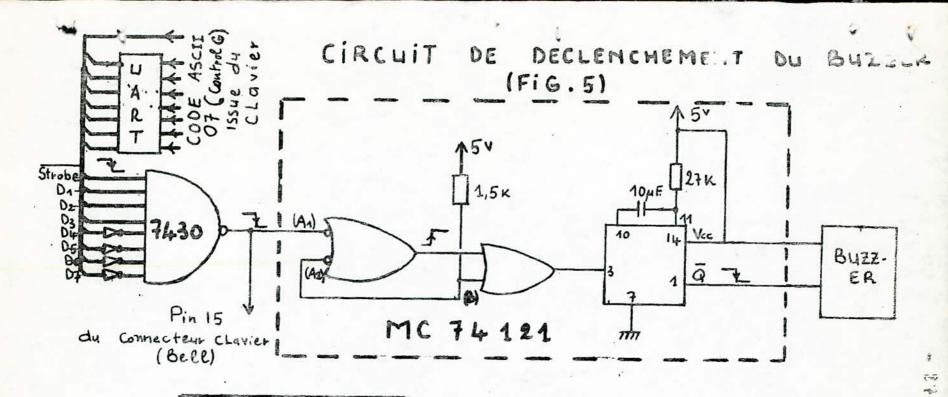

- Un circuit de déclenchement du buzzer :

- Ce circuit peut se déclencher de deux manières :

- \* soit par enfoncement d'une touche du clavier ne correspondant pas à un caractère hemadecimal, le code 07 est alors généré par l'unité centrale.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - Arramana     |                |   |   |    |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|---|---|----|--------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A <sub>1</sub> | A <sub>2</sub> | В | Q | Q  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0              | $\phi$         | 1 | 0 | 1  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | φ              | 0              | 1 | 0 | 1  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | φ              | φ              | 0 | 0 | 1  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1              | 1              | Φ | 0 | 1  |              |

| Commence of the Commence of th | 1              | 1              | 1 | П | U  |              |

| Description of the last                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | \              | 1              | 1 | Л | IJ |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1              | -              | 1 | П | J  |              |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0              | Φ              | 1 | n | ر  | and the same |

| and other party and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ø              | 0              | 1 | m | TI |              |

TABLE DE VERITÉ DU MC 74 121 1

\* soit en appuyant sur la touche correspondant au code 07 qui permet de déclencher le buzzer cad "control G". Le schéma de ce circuit est donné par la fig. 5, il utilise essentiellement une porte NAND à 8 entrées et un monostable SN 74 121 dont la table de vérité est donnée avec la fig. 5.

A l'état normal, la sortie de la porte NAND est à 1, quand le code 07 se présente à ses entrées, sa sortie bascule à 0. Le monostable se trouve alors dans la configuration A2 = 1, A1 , B = 1 sa sortie Q bascule alors à 0 actionnant ainsi le buzzer.

Le signal STROBE presene à l'une des entrées dela NAND, remet la sortie de celle-ci à 1 et arrête l'action du buzzer.

Un schéma synoptique de cette carte est donné par la fig 6.

#### II 3 Mode de Visualisation d'un texte sur l'écran :

A chaque action sur une touche de clavier un code caractère ASCII est générée sous forme d'une combinaison de 7 Bits parallèle validés par la ligne STROBE. Ce code passe dans l'UART qui permettra sa conversion parallèle - série et série - parallèle. En parallèle ce code entre dans l'EPROM qui le decodera en génerant en sortie 4 Bits CO, C1, C2, C3. Si ce code correspond à un caractère à visualiser (CO, C1, C2, C3 = 1, 1, 1, 1,), le bloc RAM sera sélecté en écriture permettant l'inscription de ce code à l'adresse générée par les lignes adresses du CRTC. Le passage de la

ligne W du CRTC à zéro (0), 4 \(\mu \sigma \) plus tard sélecte les RAM en lecture, d'ou sortie de l'information (code caractère ASCII).

Cette information passe dans le LATCH qui la liberera ou verouillera suivant le front du signal LOAD fourni par un compteur diviseur par 8.

L'information à la sortie du LATCH passe dans l'EPROM générateur de caractères, permettant la représentation de chaque caractère selon une matrice 5 x 7 (7 Lignes de 5 colonnes).

Les 5 Bits parralèle à la sortie de l'EPROM (un bit correspond à un point sur écran ) seront sérialisés par un registre à décalage à une fréquence de 6,5 MHZ (fourni par un oscillateur).

Chaque balayage d'une ligne TV présentera à l'écran les 5 points relatifs à tous les caractères de la ligne, au 2ème balayage, la prochaine rangée de points, et ceci jusqu'à visualiser les 64 caractères de la 1ère ligne d'écran.

L'information serialisée peut être produite sur deux (2) sorties

- QH = Video directe (caractère blanc sur fond noir)

- QH = vidéo inverse (caractère noir sur fond blanc).

Toute l'image necessite d'être raffraichie 50 fois/s (50 HZ) pour éviter le scintillement. Il est donc nécessaire de lire les 1624 positions mémoires du bloc RAM quelque soit leur contenu et les afficher sur **ecran**.

- \* cas du mouvement du curseur = (C3 = 0)

- L'entrée W des RAM est à 1 (sélectée en lecture)

- les 8 T 95 sont bloqués

CO, C1, C2 prennent différentes valeurs suivant la nature du mouvement du curseur. (voir table 1). Le CRTC agit directement sur le curseur sans autorisation d'écriture.

#### \* ordre d'effacement =

En mettant la ligne RO2 du compteur visu du CRTC à 0, on envoie un zéro sur les portes AND (7408) ce qui forcera la caractère noir dans les cases mémoires concernées.

#### II 4 Traitement de l'information avant visualisation :

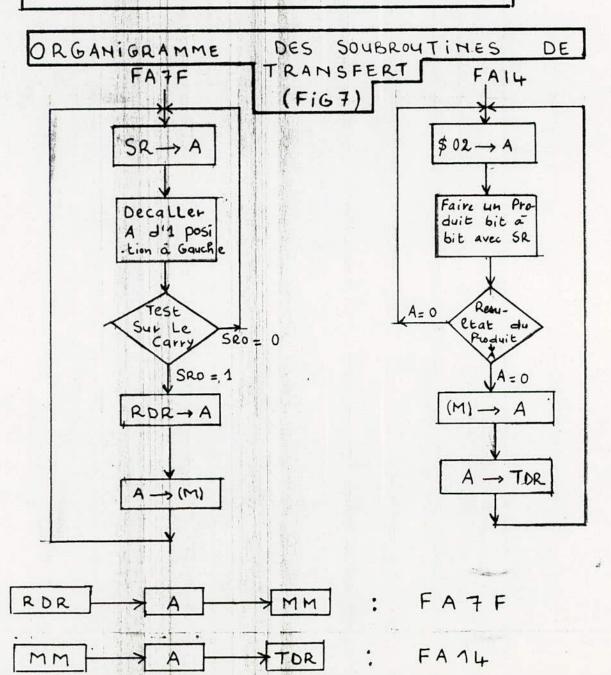

L'information entrant en parallèle dans l'UART et issue du clavier, est convertie en série. Cette information sera transférée en mémoire centrale pour traitement et reviendra à l'UART pour la visualisation grâce à l'ACIA et le moniteur de base résidant en EPROM, associé à la carte unité centrale.

La liaison entre l'UART et l'ACIA est bidirectionnelle en simultané (Full Duplex). Les informations transitent dans les deux sens simultanement. Le moniteur contient entre autre deux subroutines (FA 7 F et FA 14), FA 7 F permet le transfert vers la mémoire centrale des informations présentes dans le registre réception de l'ACIA.

FA 14 par contre permet le transfert des informations de la mémoire centrale vers le registre émission de l'ACIA (voir organigramme de la fig. 7).

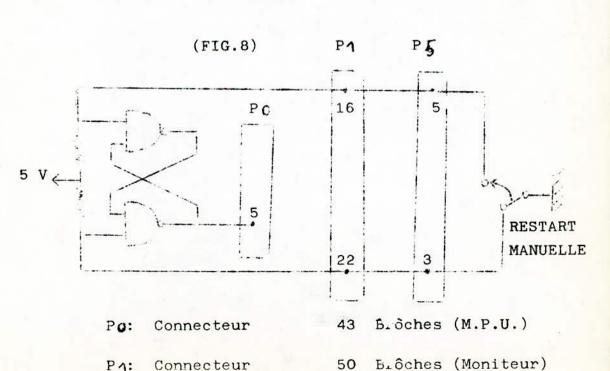

#### II 5 Circuit de reinitialisation manuelle:

Un Restart manuelle réalisé par un simple bouton poussoir du type inverseur au niveau du clavier permet le demarrage du système. Ce bouton poussoir est connecté à un dispositif antirebond permettant d'envoyer un niveau logique bas sur la ligne RESET. (voir fig. 8).

20

Brôches (Clavier).

PZ:

Connecteur

| TAB                                           | LE       | 1                          |                                                                                    |

|-----------------------------------------------|----------|----------------------------|------------------------------------------------------------------------------------|

|                                               | c2 c, c0 | Durée<br>d'exécution<br>ms |                                                                                    |

| Page erase and cursor frome (top-left)        | 0 0 0    | 132                        | Clfacer and de page avec retour ou curseur en                                      |

| End of line erase and cursor return (at left) | 0 0 1    | 8,3                        | Effacement de fin de ligne avec ritous du cui<br>seur à gauche                     |

| Line feed (cursor down)                       | 0 1 0    | 8,3                        | Deplacement du curseur d'une prisition en but                                      |

| *Inhibition of the character sent             | 0 1 1    | 8 3                        | * Innibleion du caracière en oye.                                                  |

| Cursor left (one position)                    | 1 0 0    | 8,3                        | Déplacement du curseur d'une position à geuc                                       |

| Erasure of cursor-line                        | 1 0 1    | 8,3                        | Effacement de la ligne rimiante du curseur                                         |

| Cursor up (one position)                      | 1 1 0    | 8,3                        | Diplocement du curseur d'une position en hau                                       |

| Normel character                              | 1 1 1    | 8,3                        | Caractère normal                                                                   |

|                                               |          |                            | In order to suppless parasite characts Destiné à supprimer les coractères perasite |

#### III UNITE DE STOCKAGE :

(disquette).

## III 1 Nécessité d'une unité de stockage :

NOtre centrale est conque pour un traitement en temps réel. Elle doit de ce fait être connectée "en ligne" avec les différentes zones.

Cependant, nous devons prévoir le cas ou l'opérateur au niveau de la centrale, qui doit prendre compte les états de chaque zone, au fur et à mesure de leur arrivée, est absent. Pour cela un traitement "Hors ligne" interviendra: - Les informations ne sont pas traitées immédiatement, mais stockées provisoirement sur un support intermédiaire

L'opérateur qui est "Hors ligne" prendra connaissance du message à son retour et demandera son traitement. Il est à remarquer que lorsque la centrale travaille "en ligne", l'enregistrement des informations peut être utile. En effet la mise en archive de tous les messages permettra des recherches ultérieures et des statistiques.

Cet enregistrement se fait sur disquette, car elle présente des avantages déterminants du point de vue de l'accés et de la rapidité, alliés à une grande capacité de stockage et à un coût très supportable.

Une touche du clavier (prévue au niveau de la centrale) permettra de connecter celle-ci "en ligne" ou "Hors ligne".

III 2 <u>Constitution de l'Unité de Stockage</u>: (Voir schéma bloc de la fig. 2).

## L 'unité de stockage comprend :

- 2 lecteurs de disques souples (ou drives) comportant une partie mécanique et une partie électronique.

- Une carte "Contrôleur disque" qui contient :

- \* L'EPROM E 800 (début d'adresse) contenant le "bootstrap" permettant de charger en mémoire centrale le programme de gestion du périphérique (Drive).

Ce programme appelé M DOS (Motorola Disk operating system) se trouve initialement sur disquette.

- \* Le circuit de récupération de données PLL qui permet de décoder les informations et de générer un signal d'horloge de synchronisation, par une séparation des données.

- \* Le SSDA (MC 6852): Interface entre le drive et l'unité centrale, il réalise la synchronisation des opérations de lecture et d'écriture, la serialisation des données écrites et la deserialisation des données lues.

- \*Le PIA (MC 6820) s'interfaçant avec le drive pour permettre à l'unité centrale de contrôler les fonctions du drive, et ainsi de la renseigner sur les états des éléments du drive.

\* Un bloc (MC 8506) permettant une bonne détection d'erreur et utilisant comme type code le CRC (code redondant cyclique).

## C H A P I T R E II : MODE D'ECHANGE D'INFORMATIONS :

#### ENTRE LA CENTRALE ET LES ZONES

## I 1 Rôle de la carte interface ACIA (MC 6850):

Chaque zone communiquant avec la centrale, comporte un "contrôleur de zone" qui traite les états de chaque détecteur avant de les faire converger.

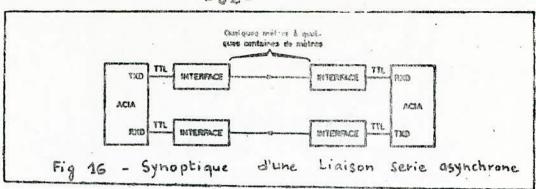

La distance entre la zone et la centrale pouvant aller de plusieurs dizaines de mètres à quelques centaines de mètres, une liaison série est toute indiqué pour l'acheminement des informations.

Une carte ACIA contenant autant d'ACIA que de zones à surveiller jouera le rôle d'interface entre la centrale et les "contrôleurs de zones".

Chaque zone communique avec la centrale par trois (3) lignes (emission, réception, commun.).

L'ACIA étant la pièce maitresse du mode d'échange, nous avons jugé utile de donner quelques détails sur le "ship" MC 6850.

# I 2 Rappels sur l'ACIA et la Norme RS 232 :

## I 21 MC 6850

L'ACTA est un circuit d'interface qui réalise la mise au format des données et la commande des communications série asynchrone. L'organisation interne de l'ACTA et les détails sur ses différents registres sont donnés en annexe.

Ce genre de liaison série, a été prévu initialement pour connecter entre eux deux équipements informatiques relativement éloignés (quelques mètres à plusieurs centaines de m), comme c'est le vas pour notre liaison centrale-"contrôleur de zone". Les entrées/sorties (E/S) de l'ACIA sont compatibles TTL, cet éloignement compromet à l'allure des signaux TTL échangés, en effet : un signal TTL est un signal rectangulaire dont les flance doivent être très raides, pour rester le moins longtemps possible dans la bande interdite (0,8 V - 2 V).

Une liaison longue présente une capacité parasite non négligeable (plusieurs centaines de PF). Un signal TTL, après un parcours suffisament long, dans de telles conditions arrive fortement déformé, ses flancs sont expenentiels et son amplitude est réduite.

Allure après un long parcour Pour s'affranchir de ces problèmes et conserver à la liaison série asynchrone son intérêt, on applique aux niveaux électriques échangés la norme RS 232 (ou V 24).

## I 22 Norme RS 232 (Voir schéma en annexe) :

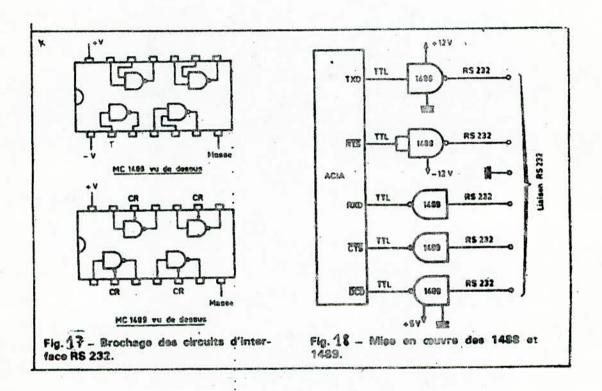

Les signaux TTL sortant de l'ACIA de la centrale passent dans unadaptateur de niveau (MC 1488) avant d'être envoyé sur le câble de liaison, les signaux arrivant sur le câble passent eux aussi, dans un adaptateur de niveau (MC 1489) pour être remis aux normes TTL et être appliqués à l'ACIA du "Contrôleur de zone".

Les niveaux sur la RS 232 sont définis comme suit :

- A l'emission le signal a une amplitude variant de

+ 15 V à 15 V, compte tenu des alimentations disponibles

la valeur généralement utilisé est de + 12 V à 12 V.

- A la réception, les circuits d'interface RS 232 reconnaissant comme niveau bas tout signal inférieur à 3 V et comme niveau haut tout signal supérieur à + 3 V.

Le courant maximum circulant dans la ligne est limité côté emission à 10 m A par les circuits d'interface.

La logique utilisée sur la ligne RS 232 est une logique négative c,a,d, qu'un niveau haut TTL correspond à un niveau bas RS 232 et réciproquement un niveau bas TTL correspond à un niveau haut RS 232. Cala signifie que les circuits d'interface RS 232 tant à l'émission qu'à la réception remplissent, en plus de leur fonction de conversion de niveau, la fonction d'inverseur.

Le brochage des circuits réalisant l'interface RS 232 (MC 1488 et MC 1489) et leur mise en oeuvre dans une liaison série asynchrone est donnée en annexe par les fig. 16, 17, 18 (voir annexe).

- Le MC 1488 est le circuit d'emission RS 232, il dispose de deux brôches d'alimentation qui peuvent admettrent jusqu'à + 15 V et à - 15 V.

Trois de ces portes disposent de deux (2) entrées, la 4ème porte n'ayant qu'une seule entrée.

- Le MC 1489 est le circuit de réception, il admet donc des signaux RS 232 pour les convertir en signaux TTL. IL dispose d'une seule alimentation + 5 V, ses entrées admettent des signaux qui peuvent aller de + 30 V à - 30 V d'amplitude, et ses seuils de basculement sont de + 1,5 V à - 1,5 V. Les portes qu'il contient sont des inversemes et disposent toutes d'une entrée dite "Contrôle de Reponse" (CR) qui n'est quasiment jamais utilisé (en l'air).

# I 3 Mode d'Echange d'informations :

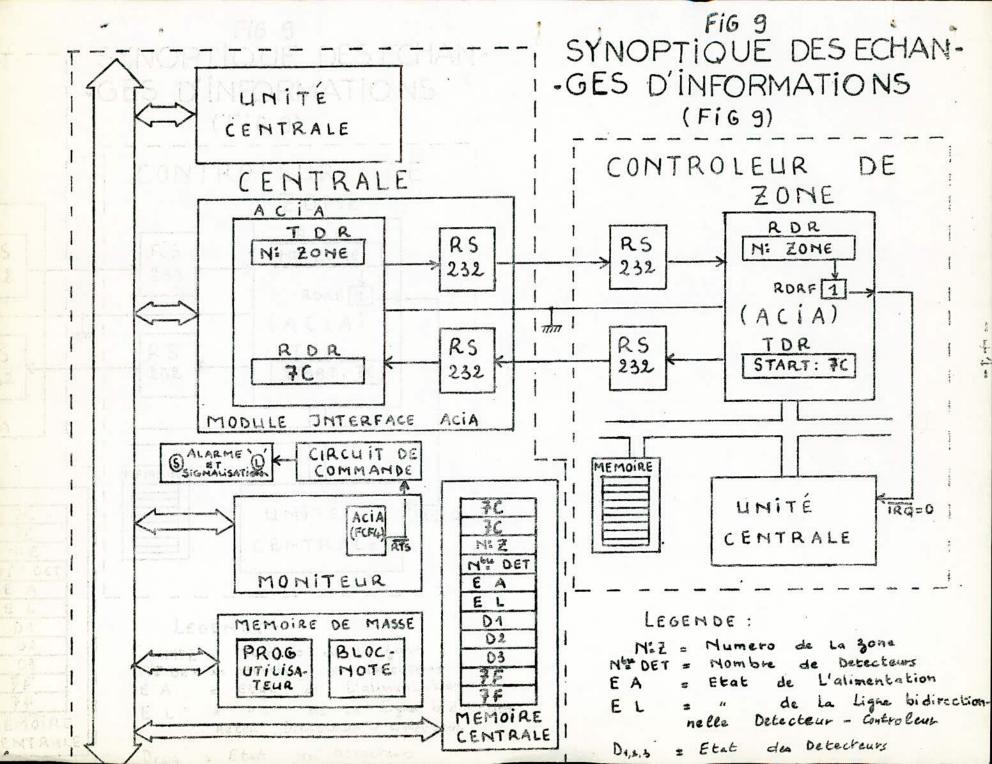

Une schématisation est donnée par la fig. 9 tout d'abord il faut préciser que dans notre étude on a prévu le contrôle de trois types de détecteurs (rayonnement température, humidité), cependant, une extension à d'autres types de détecteurs est toujours possible.

Ceci dit, notre centrale scrutera les différentes zones par mode d'interruption. Pour cela le numéro de la zone à contrôler sera placé dans le registre emission de l'ACIA (TDR) correspondant au niveau de la centrale.

Ce numéro sera alors envoyé au registre réception de l'ACIA du "Contrôleur de zone" (voir fig.9) correspondant et interrompt ce dernier ( c a d que l'ACIA du CZ ayant son registre réception plein mettra le bit STO du registre d'Etat (RDRF) à 1, ce qui déclenche une demande d'interruption). Le "Contrôleur de zone" termine l'exécution de l'instruction en cours avant de prendre en considération la demande d'interruption.

Après reconnaissance de celle-ci, le Contrôleur de zone executera une séquence d'interruption en lisant le vecteur d'interruption.

Après exécution de cette séquence, le "contrôleur de zone" commence le transfert vers la centrale de toutes mes informations qu'il a enregistré durant les cycles précédents.

Chaque fois qu'un transfert d'informations intervient, on est amené à résoudre différents problèmes susceptibles de survenir.

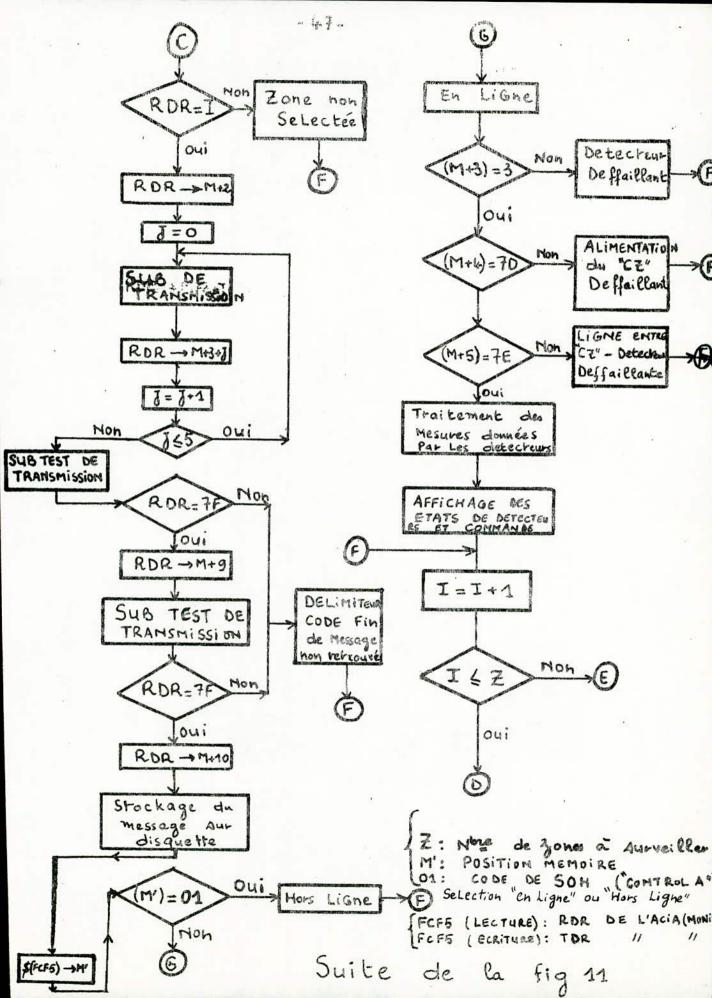

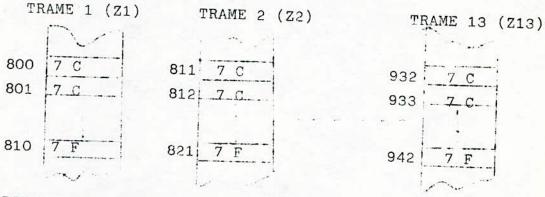

Pour cela on défini une trame composée de 11 bytes (octets) formant le message qui est défini comme suit :

- 1er octet : code delimiteur début de trame (7 C)

- 2ème octet : code delimiteur début de trame (7 C)

- 3ème octet : Donnera le numéro de la zone à surveiller ce qui permettra de vérifier que la zone demandée a bien été sélectée.

- 4ème octet : renseigne sur le nombre de détecteurs que contient la zone.

- 5ème octet : permet de contrôler l'état de l'alimentation du contrôleur de zone" (7 D).

- 6ème octet : renseigne sur l'état de la ligne de dialogue entre le "contrôleur de zone" et les détecteurs (7 E).

- 7ème , 8ème, 9ème octe $\hat{\mathbf{t}}$  : renseigne sur l'état des trois détecteurs choisis pour notre application . (D1 = R, D2 = T, D3 = H).

- 10ème octet : delimiteur code de fin de trame (7 F)

- 11ème octet : delimiteur code de fin de trame (7 F)

Pour les délimiteurs "code début ou fin de trame" on a utilisé deux bytes pour une question de sécurité, c a d'afin d'être sûr que l'information comprise entre les délimiteurs est bien conforme au message envoyé par le "contrôleur de zone". Donc le message utile sera constitué de 6 bytes, les 5 bytes restant de la trame sont occupés par les codes délimiteurs et per l'adresse désignée par centrale (N° de zone).

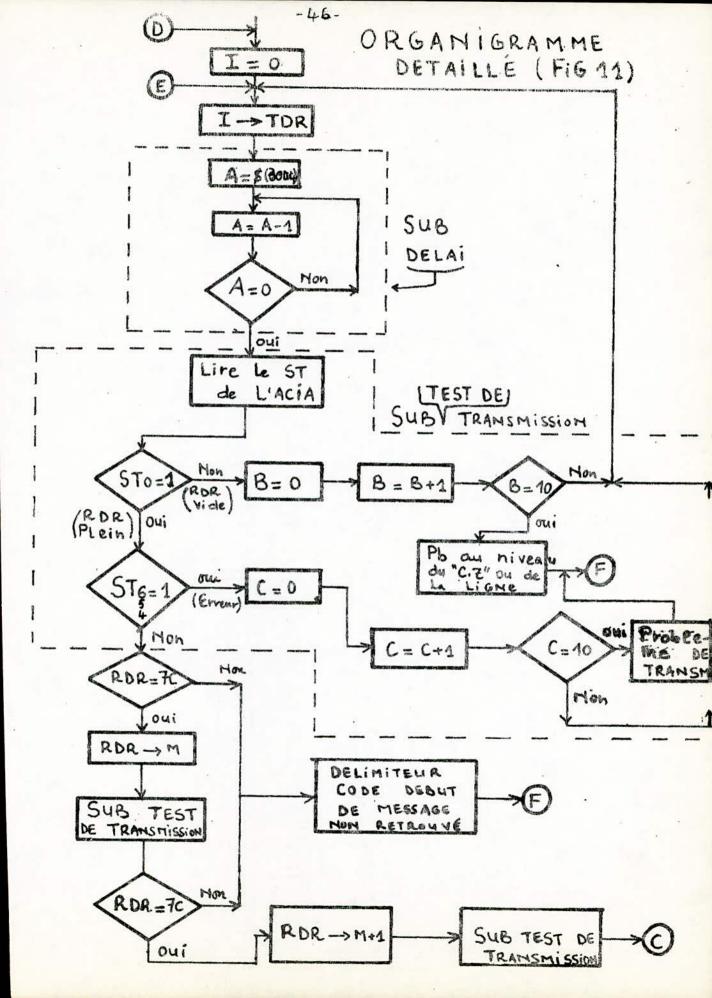

#### I 4 Détails sur le mode d'échange :

En envoyant au "CZ" une demande d'interruption, la centrale marque un temps d'attente laissant

ainsi le temps au "CZ" de lui transférer les informations

enregistrées. Si elle ne reçoit aucun message après le

délai autorisé, elle adressera la zone à nouveau. Après

un nombre défini de demande (10 fois par ex.), si la

centrale ne trouve toujours rien dans son registre, elle

concluera que la ligne qui la relie à la zone est coupée

ou que le "CZ" est défaillant et passe à la zone suivante :

Si un octet arrive dans le registre réception de l'ACIA de la centrale. Celle-ci vérifie que le byte du message et compatible à celui qui a été envoyé. Pour déceler les éventuelles erreurs de transmission, on utilise la méthode la plus simple qui consiste en un contrôle de parité.

Un bit de chaque octet sera réservé au bit de parité - si erreur, la centrale adressera à nouveau la zone pour retransmission du caractère erroné et ceci un certain nombre de fois (10 fois par ex.). Si après ces 10 demandes, l'erreur persiste toujours, elle concluera que la ligne n'est pas bonne et passera à la zone suivante. Si le caractère reçu est compatible avec celui qui a été envoyé, la centrale testera cet octet (s'il ne correspond pas au message utile) et l'enverra en memoire s'il est bon . elle reprendra alors le même travail avec le deuxième byte et ainsi de suite jusqu'au onzième. Le message sera stocké sur disquette puis suivant que la centrale soit connectée "en ligne" ou "hors ligne", suivra le traitement ou non de ce message. Traitement suivi de visualixation et de déclenchement de commande).

La centrale adressera ensuite la zone suivan suivante et fera le même travail qu'avec la première et ai ainsi jusqu'à la dernière zone. Une fois terminé avec cette dernière, elle reviendra à la première et la boule recommencera.

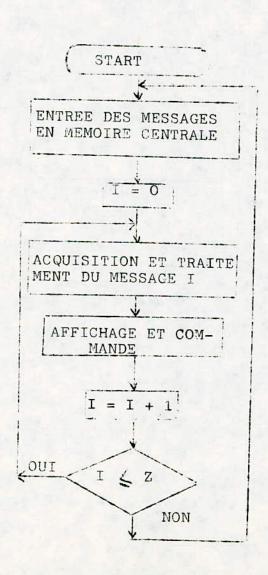

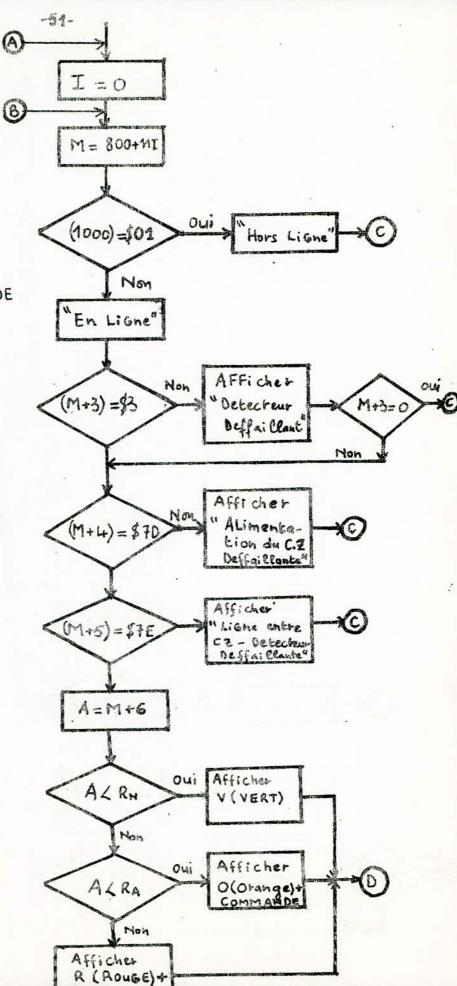

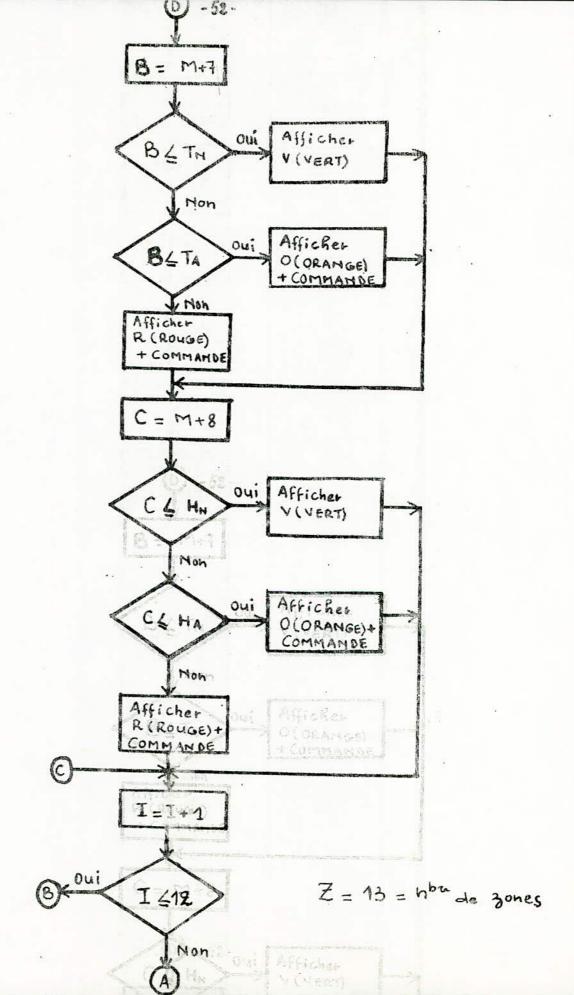

L'organigramme général est donné par la fig. 10, celui qui est détaillé par la fig. 11, et le programme est en annexe.

# II SIMULATION:

Les Contrôleurs de zone devant nous envoyés les informations de chaque détecteur, n'étant pas disponibles, nous ferons un programme simulant ces Contrôleurs.

Ainsi en mémoire centrale seront présents les différents messages (normalement envoyés par les C.Z à la centrale).

Après acquisition des messages, la centrale les traitera et agira en conséquence sur les commandes (Alarme - Signalisation).

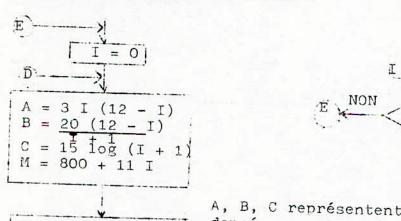

ORGANIGRAMME PRINCIPAL

Z = Nbre. de zone à contrôler

Z peut aller jusqu'à 128 (Codé sur 7 BITS).

Dans notre application on s'est limité à Z = 13

I = Numéro de la zone.

# A) ENTREES DES MESSAGES EN MEMOIRE CENTRALE :

On introduira en mémoire centrale 13 messages (cas de 13 zones), chaque message occupera 11 positions mémoires (11 Bytes).

# \* OCCUPATION MEMOIRE

# \* ORGANIGRAMME D'ENTREE DES DONNEES

| 7  | C               | M |   |    |

|----|-----------------|---|---|----|

| 7  | C               | M | + | 1  |

| Ι  |                 | M | + | 2  |

| 3  | >               | M | + | 3  |

| 7  | D>              | M | + | 4  |

| 7  | E               | M | + | 5  |

| A. | <del>&gt;</del> | M | + | 6  |

| В  | >               | M | + | 7  |

| C  | >               | M | + | 8  |

| 7  | F               | M | + | 9  |

| 7  | F ->            | M | + | 10 |

A, B, C représentent les mesures données par les détecteurs (R, T, H,). Ces mesures sont exprimées sous forme de fonctions mathématiques. Cette méthode nous permet de gagner en nombre d'instructions puisqu'une boucle fera le chargement de tous les messages en mémoire. Il faut préciser que le choix de ces fonctions est aléatoire, mais permet de balayer tous les cas possibles/(Etat normal, Admissible, dangereux).

# B) Acquisition et traitement du message :

Etant donné que nous ne recevons pas de message, il est inutile de faire les tests sur la transmission. Donc on ne peut pas conclure si un "CZ" est défaillant ou si la ligne est coupée ou mauvaise.

Nous avons dans cette partie simulation, à traiter uniquement le message utile (de la procédure de transmission ou trame que nous avons défini précedemment), sans avoir à nous préoccuper de la synchronisation caractère (reconnaissance du début et de la fin du message). Avant de faire ce traitement nous ferons un test nous signalant l'état " on line" ou "off line". Pour cela nous avons choisi une touche du clavier (contrôle A) de code (O1). Avant de quitter son poste l'observateur doit appuyer sur cette touche. Notre programme se chargera de transférer ce code dans une position mémoire (M').

Si (M') = 01 "off line" Si (M') ≠ 01 "on line"

# - Traitement des mesures données par les 3 détecteurs :

$\begin{pmatrix} & R = Rayonnement & 7 \text{ème OCTET} \\ & (& T = Température & 8 \text{ème OCTET} \\ & (& H = Humidité & 9 \text{ème OCTET} \end{pmatrix}$

Les mesures A, B, C données par chaque détecteur sera comparée à deux seuils (seuil normal et seuil admissible)

$(RN = 70 \text{ Rem } TN = 45^{\circ} \text{ HN} = 10\%$

(RA = 100 Rem TA = 55° HA = 40%

Si A  $\langle$  (seuil)  $\stackrel{\longrightarrow}{N}$  Etat normal (vert)

Si (seuil)  $\stackrel{\longrightarrow}{N}$  A  $\langle$  (seuil)  $\stackrel{\longrightarrow}{A}$  Etat admissible (orange)

Si A  $\stackrel{\longrightarrow}{N}$  (seuil)  $\stackrel{\longrightarrow}{A}$  Danger (Rouge).

- C) Visualisation et Commande :

- \* VISUALISATION :

L'Etat de chaque zone apparait par l'affichage d'un V (vert), O (orange), R (rouge), suivant le cas dans une case d'un tableau visualisé sur écran. (L'Etat de chaque zone dépendante des mesures fournies par les détecteurs).

Si l'alimentation du "CZ" ou la ligne qui le relie aux détecteurs est défaillante ou si des détecteurs fonctionnent mal, un affichage le mentionnera.

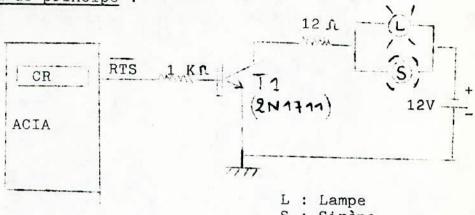

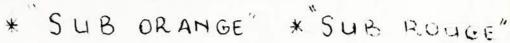

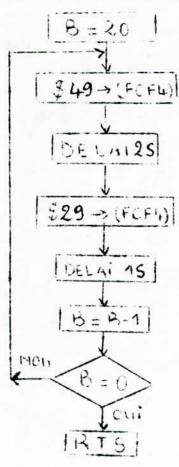

Commande (Sirène et Lampe Rouge) :

Un panneau placé au niveau de notre centrale comporte une sirène et une lampe rouge. Ceci permet une signalisation évidente d'un danger (pour le voyant rouge) et l'avertissement à distance (sirène).

Si un orange (0) ou un rouge (R) apparait dans une case quelconque du tableau, une subroutine permettra le déclenchement d'un circuit commandant cette sirène et cette lampe pendant un certain temps (DELAI).

- L'orange fera clignoter la lampe et actionnera la sirène par intermittance (attention : prévention d'un danger).

- le rouge fera fonctionner d'une manière continue la lampe et la sirène (DANGER).

Nous avons utilisé la ligne RTS de l'ACIA (associée au module CPU). Cette ligne servira à bloquer (RTS = 0) ou saturer (RTS = 1) un transistor T1.

Schéma de principe :

S: Sirène RL // RS = 8 JL

Par programmation du registre de contrôle de l'ACIA, on mettra à "1" ou à "0" la ligne RTS

\* (CR5, CR6) = (1,0) RTS = 0 \* (CR5, CR6) = (0,1) RTS = 1

- Le Baud rate est utilisé en diviseur par 1 6 (CRO, CR1) = (1,0).

- la transmission sefait par insertion d'un bit stop dans un mot de longueur 7 Bits (parité paire) : (CR2, CR3, CR4) = (0,1,0).

|              | CR7 | CR6 | CR5 | CR4 | CR3 | CR2 | CR1 | CR | 0   |   |   |

|--------------|-----|-----|-----|-----|-----|-----|-----|----|-----|---|---|

| <b>\$</b> 29 | 10  | , 0 | 1   | 0   | 1   | 0   | 0   | 1  | RTS | = | 0 |

| <b>\$</b> 49 | 0   | 1   | 0   | 0   | 1 , | 0   | 0   | 1  | RTS | = | 1 |

Le registre de contrôle se cet ACIA occupe la position mémoire FC F4.

FIG 12-B

ORGANIGRAMME DE

TRAITEMENT

DU MESSAGE

UTILE

Subroutines de déclenchement des commandes

\* DELAI 15 (TEMP1)

A = 10 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X - 1 X = X -

DELAI 25 (TEMP2)

même organigramme que

femp1 seulement il faut

charger L'ACCUMULATEUR

A avec 20 (ou \$14)

# // ONCLUSION

Arrivés au terme de ce semestre, on se rend compte que les nombreuses difficultés dans la conception d'un système de sécurité centralisé ne pourraient être résolues en si peu de temps.

Face à certaines de ces difficultés nous avons essayé de trouver une solution de compromis entre le Hard, Le Soft et Le Coût qu'elle apporte.

De plus ce système ainsi conçu peut évoluer par apport de certaines modifications ne remettant pas en cause son architecture (extension du système).

Ces modifications peuvent consister en l'adjonction d'une unité supplémentaire ou le changement d'une unité par un modèle plus rapide. Par exemple dans le domaine de la radioprotection, un analyseur multicanaux serait utile au niveau de la centrale puisqu'il permet de fournir un spectre d'énergie du rayonnement nucléaire.

Au niveau des programmes, une amélioration pourrait être apportée par un test approfondi et une analyse de tous les incidents.

Nous espérons que ces améliorations seraient apportées dans les années à venir et rendront notre système plus efficace dans le domaine de la sécurité.

#

# TABLE DE VERITÉ

| 5~  | Sa  | Pin 1 | Pin 15 |       |     | E1 04 | INP<br>UT | OUT- |                                   |

|-----|-----|-------|--------|-------|-----|-------|-----------|------|-----------------------------------|

| 1 0 |     |       | P      | 26    | 2   | L     | L         | L    | H=1<br>L=0                        |

|     | 1 0 | PZ    |        | F 000 | 500 | H     | *         | 2    | Z = Haute<br>impede<br>P = Transf |

Sw= Q RIW BA Sa = Q2 R/W

MC ST26 E1 = E2 = BSEM

- L'Interface Série Asynchrone ACIA (MC 6350) :

L'ACTA est en circuit d'interface entre l'unité centrale et un périphérique travaillant en mode série asynchrone.

L'ACIA est relié au système par les entrées de sélection (RS), d'activation ( $\emptyset$ 2), la ligne de lecture écriture ( $\mathbb{R}/\overline{\mathbb{W}}$ ), une ligne d'interruption ( $\overline{\mathbb{IRO}}$ ) et un bus données 8 Bits.

L'interface série est constitué côté périphérique, d'une entrée série (R x D) et d'une sortie série (T x D) avec horloges indépendantes et trois lignes de commande de périphérique/modem. (voir fig. 15).

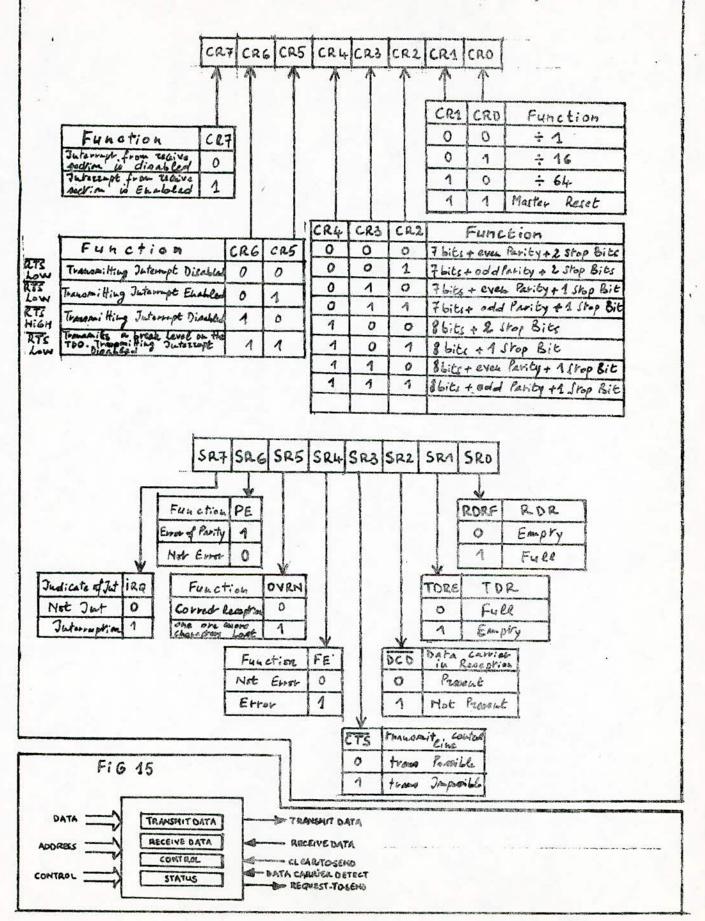

L'ACIA possède 4 registres accessibles au microprocesseur, deux en lecture, le registre d'Etat (SR) et le registre de données reçues (RDR), deux en écriture, le registre de contrôle (CR) et le registre données à transmettre (TDR). La ligne RS et l'état du signal R/W déterminent le registre sélecté comme le montre la fig. 19.

Un schéma fonctionnel et deux tables sur le contenu des registres sont donnés par la fig. 14 et les tables 2 et 3.

La confiruration fonctionnelle de l'ACIA est programmée (Via le bus données) pendant la mise à l'état initial du système. Le registre de commande (ou de contrôle) programmable permet d'indiquer la longueur des mots, le rapport de division d'horloge, la commande de transmission, la commande de réception et celle d'interruption. Un registre d'Etat permet d'observer l'état courant du transmetteur et du récepteur.

TABLES - DEFINITION OF ACIA REGISTER CONTENTS

|                               |                                          |                                         | Suffer Address                   |                                       |

|-------------------------------|------------------------------------------|-----------------------------------------|----------------------------------|---------------------------------------|

| Data<br>Bus<br>Line<br>Number | RS o RJW<br>Transmit<br>Onto<br>Register | RS o R/W<br>Receive<br>Data<br>Register | RS • EJW<br>Control<br>Register  | RS = R/W<br>Stebus<br>Rogister        |

|                               | (Write Only)                             | (Read Caly)                             | (Write Only)                     | (Read Only)                           |

| 0                             | Data Sit O°                              | Data Sibo                               | Counter Divide<br>Select (CRO)   | Receive Data Register Full (RDRF)     |

| 4                             | Data Git 1                               | Date St.1                               | Counter Divide<br>Sciece 2 (CA4) | Transmit Onto Register Empty (TO A.S) |

| 2                             | Data Sit 2                               | Daen Bit 2                              | Word Solack 4<br>(c.f.2)         | Onto Corrier Galace<br>(BCB)          |

| 3                             | Data Git 3                               | Data Bit3                               | Ward Select 2<br>(cma)           | Clear-to-Sand<br>(CVS)                |

| 4                             | Data Dit h                               | Date & t 4                              | Word Select 3<br>(CRA)           | Framing Error<br>(FE)                 |

| 5                             | Doba Bit 5                               | Data Sits                               | Transmia Combrot 4<br>(CAS)      | Asceives Oversum<br>(OVAM)            |