UNIVERSITÉ D'ALGER

ECOLE NATIONALE POLYTECHNIQUE

DEPARTEMENT ÉLECTRICITÉ

السكرية الرطنية للعلوم الهسدي السكرينية السكرينية ECOLE NATIONALE POLYTECHN OHE BIBLIOTHÈQUE

PROJET DE FIN D'ETUDES

TECHNOLOGIE

I LOCUE LE LALON ILLE

- ILONALE POLYTECHNIQUE

MIELMOTHREISE

PROPOSÉ PAR :

Mme G. MONDON

ETUDIÉ PAR : HAMEG L. Qu'il me soit permis d'exprimer tous mes remerciements et toute ma profonde gratitude à tous mes professeurs, ainsi qu'à Madame C. MONDON qui m'a vivement aidé dans l'élaboration de mon projet.

Je remercie également M.Ms. M. MAZOUNI et A. AMARA, pour lour aide précieuse.

#

|   | INTRODUCTION                                                                                                                                                                                  | page | 5  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|

| 1 | DEFINITION                                                                                                                                                                                    | page | 5  |

| 2 | CENERALITES                                                                                                                                                                                   | page | 6  |

|   | CHAPITRE I : Les mémoires Actuelles                                                                                                                                                           | page | 8  |

|   | I.1 LES MEMOIRES A TORES DE FERRITE.                                                                                                                                                          | page | 8  |

|   | <ul> <li>I.1.1. Le tore de ferrite.</li> <li>I.1.2 Ecriture et lecture d'une information.</li> <li>I.1.3 Ménoire à coïncidence.</li> <li>I.1.4 Autres types de némoires à ferrite.</li> </ul> |      |    |

|   | I.1.5 Conclusion.                                                                                                                                                                             |      | 4- |

|   | I.2 LES MEMOIRES A TAMBOURS MAGNETIQUES.  I.2.1 Conclusion                                                                                                                                    | page | 10 |

|   | 1.3 LES DISQUES MAGNETIQUES                                                                                                                                                                   | page | 11 |

|   | I.4 LA BANDE MAGNETIQUE                                                                                                                                                                       | page | 11 |

|   | I.5 Conclusion                                                                                                                                                                                | page |    |

|   | CHAPITRE II : Les Mémoires à CI M.O.S                                                                                                                                                         | page | 13 |

|   | II.1 LE TRANSISTOR M.O.S.                                                                                                                                                                     | page | 13 |

|   | II.2 CELLULES STATIQUES - CELLULES DYNAMIQUES.                                                                                                                                                | page | 19 |

| II.2.1. Fonctionnement en statique                |      |    |

|---------------------------------------------------|------|----|

| II.2.2 Fonctionnement en dynamique.               |      |    |

| II.2.3 La cellule M.O.S statique                  |      |    |

| II.2.4 La cellule M.O.S en dynamique.             |      |    |

| II.3 LES MEMOIRES VIVES                           | page | 26 |

| II.3.1 RAM statiques                              |      |    |

| II.3.2 R.A.M. dynamiques                          |      |    |

|                                                   |      |    |

| II.4. LES MEMOIRES MORTES                         | page | 37 |

| II.4.1 Les P.R.D.M.                               |      |    |

| II.4.2 Structure des R.O.M.                       |      |    |

| II.4.3 Les R.E.P.R.O.M.                           |      |    |

| II.5 LES MEMOIRES ASSOCIATIVES                    | page | 44 |

| II.6 R.A.M. A M.O.S. COMPLEMENTAIRES              | page | 45 |

| II.6.1 Les circuits C/M.O.S                       |      |    |

| II.6.2 Les cellules en C/M.O.S. de R.A.M.         |      |    |

| CHAPITRE III : LES PERSPECTIVES D'AVENIR          | page | 49 |

| III.1 ETAT ACTUEL ET AVENIR DES MEMOIRES A C.I    | page | 49 |

| III.2. LES MEMOIRES A SEMI-CONDUCTEURS AMORPHES.  | page | 51 |

| III.2.1.Les semi-conducteurs amorphes.            |      |    |

| III.2.2.Le commutateur amorphe.                   |      |    |

| III.2.3 Une mémoire à s-c amorphes, la R M M 256. |      |    |

| III.3. LES MEMOIRES A DECALAGE.                          | page   | 57      |

|----------------------------------------------------------|--------|---------|

| III.3.1. Mémoires C.C.D                                  | page   | 57      |

| III.3.2 Mémoires à bulles magnétiques                    | page   | 64.     |

| III.3.2.1 Théorie du ferromagnétisme                     |        |         |

| III.3.2.2. Obtention des bulles magnétiques              |        |         |

| III.3.2.3 Méthode de déplacement des bulles              |        |         |

| III.3.2.4 Méthodes de détection des bulles               |        |         |

| III.3.2.5 Mémoires à bulles magnétiques                  |        |         |

| III.4 MEMOIRES A SUPRACONDUCTEURS                        | page   | 74.     |

| III.4.1 LA supraconductivité                             |        |         |

| III.4.2 Etude d'une cellule supraconductrice.            |        |         |

| III.4.3 Réalisation des mémoires à supraconducteurs.     |        |         |

| III.4.4. Avantages et inconvenients des némoires à supra | condu  | cteurs. |

| III.5 MEMOIRES A HOLOGRAMMES                             | page   | 79      |

| III.5.1 Introduction                                     |        |         |

| III.5.2 Ménoires holographiques à materiaux magnéto-opt  | tiques | •       |

| III.5.3 Mémoires holographiques à nateriaux électro-opt  | tiques | •       |

| III.5.4 Mémoires holographiques à nateriaux photochrome  | es.    |         |

| III.5.5. Mémoires holographiques à films de bismuth.     |        |         |

| III.5.6 Mémoires holographiques à enregistrements them   | noplas | tiques  |

III.6 LES MEMOIRES A FILMS MAGNETIQUES MINCES

page 87

| III.6.1 Les films ma | gnétiques minces |

|----------------------|------------------|

|----------------------|------------------|

III.6.2 Fonctionnement d'une cellule de mémoire

III.6.3 Constitution d'une mémoire

III.6.4 Mémoires à fils.

| IV. CONCLUSION  | page | 95 |

|-----------------|------|----|

| * ANNEXE        | page | 96 |

| * BIBLIOGRAPHIE | page | 99 |

#### INTRODUCTION.

Les performances des ménoires d'ordinateurs entrent pour une très large part dans celles des systèmes informatiques et leur évolution semble être destinée à s'accentuer encore. Aussi, les perspectives des ménoires d'ordinateurs conditionnent l'évolution future des systèmes informatiques.

Notre étude porte sur une synthèse d'ordre technologique des ménoires. ce qui extrêmenent délicat pour un sujet aussi vaste et intéressant que celui des ménoires. C'est pourquoi, nous avons insisté sur l'étude des ménoires qui présentent un intérêt certain - du noins, nous le pensons- conne les ménoires à M.O.S. et celles. qui sont au stade de recherche. Quant aux autres ménoires ( tores de ferrites, disques magnétiques, tambours etc...), nous ne dirons que l'essentiel car elles sont encore utilisées à l'heure actuelle.

Le donaine d'étude des ménoires présente donc deux intérêts:

- INTERET D'ORDRE TECHNIQUE: recherche du type de ménoire et des caractéristique les plus importantes par rapport aux autres types.

- INTERET D'ORDRE ECONOMIQUE: s'il est un marché en pleine évolution c'est bien celui des mémoires, les débouchés sont nouveaux et importants: automatisme, télécommunications, enseignément programmé, traduction automatique, etc...

## ,1 DEFINITION:

La ménoire est un organe électronique capable de contenir, d'enregistrer et de restituer des informations à un organe de traitement lorsque celui-ci se manifeste en interrogeant la ménoire.

Les dispositifs utilisés sont à 2 états d'équilibre stable. Le suport de l'information sera donc une cellule binaire. Les phénoménes utilisés pour le stockage d'énergie sont:

- l'énergie magnétique

- l'énergie électrostatique

- l'énergie qui accompagne un changement d'état ( transfert d'énergie).

On distingue deux aspects essentiels du fonctionnement d'une ménoire : la lecture et l'écriture.

On dit qu'il y a écriture lorsque l'on enregistre des informations en mémoires et lecture lorsque l'on sort des informations précedemment enregistrées.

#### ,2 GENERALITES :

#### 1.2.1 CAPACITE :

Elle s'exprime par le nombre de bits qu'il est possible de stocker la capacité s'exprime par des puissances de 2 - L'unité de capacité est le K= 2<sup>10</sup>= 1024 bits (à peu près kilo-information).

#### .2.2. VOLATILITE:

On dit qu'une mémoire et volatile si l'information stockée risque d'être modifiée on perdre par défaut d'alimentation électrique et non volatile dans le cas contraire.

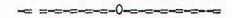

#### .2.3 TEMPS DE CYCLE

C'est le temps minimal qui s'écoule entr<sub>e</sub> 2 opérations successives de lecture on d'écriture. Il se décompose suivant le schéma:

- Temps d'accés: temps qui s'écoule entre l'arrivée de l'ordre et de la fin de l'execution de cet ordre. Ce temps varie de la ns à quelques secondes.

- Temps d'attente: temps qui s'écoule entre l'arrivée de l'ordre de lecture ou d'écriture et le moment où l'on trouve l'adresse indiquée.

## .2.4. les types de némoires:

- \*- les némoires statiques où le support de l'information est fixe: tous de fenites, transistors....

- \*- les mémoires dynamiques où le suport de l'information ou l'information sont en mouvement: tambours, ci (sircoits intégrés)

Les mémoires à propagation: les discontinuités physique se propagent de manière cyclique : ébranlements électromagnetiques, ebranlements soniques, cheminement de bulles magnétiques sous l'effet d'un champ mégnétique tournant.

## :2.5 LES MODES D'ACCES A UNE ADRESSE TROUVEE:

\*- accés séquentiel: les informations se présentent à la sortie dens un ordre préatabli c'est à dire qu'on peut avoir accés à l'adresse n + 1 qu'après avoir fait défilèr devant la tête de lecture toutes les positions de mémoires depuis 0 jusqu'à n.

- \*-accés aléatoire ou direct ou libre : ce temps d'accés est le même pour toutes les adresses.

- \*-accés cyclique: Dans les tambours et disques magné tiques un ensemble d'adresse repasse périodiquement et toujours dans le même ordre en face de la tête de lecture.

- \*- ACCES PAR BLOC: l'accés au début du bloc et aléatoire à vitesse noyenne mais la lecture est séquentielle et à grande vitesse.

## .2.6 UTILISATION DES MEMOIRES:

- \* Les mémbires de travail (strach-pad memoires) de très petites capacités et de grande vitesse Elles sont intégrées appelés mémoires toujours on mémoires bloc-notes à accés aléatoire dens l'unité de traitement leur capacité est 100 à 5000 éléments binaires et le temps d'accés de 20 à 500 ns.

- \*-La ménoire principale centrale: Elle dontient les programes et les données, elle est de grande capacité (10<sup>5</sup> à 10<sup>7</sup> éléments binaires) et de t<sub>e</sub>mps d'accés court (200 ns à 10 ns).

- \*-LES MEMOIRES SECONDAIRES ADRESSABLES: Elles forment une extension de la némoire principale- capacité de 10<sup>7</sup> à 10<sup>8</sup> éléments binaires et le temps d'accés très court (1 pas à 20 ns). Elles sont de coreception relativent récente- les solutions magnetique stat ques sont les seules disponible actuellement.

- \*- LES MEMOIRES FICHIERS ON MEMOIRES DE MASSE': De très grande capacité (108 e. b) et de temps d'accés très long très supérieur à le ms. Elles sont à accés sélèctif. On distingue: les tambours et disque à tête fixes (tps d'écés 5 à 20 mms). disque à tête mobiles souvent amovibles (tps d'éccés 50 à 100 ). mémoires à feuillets magnétique (200 à 600 ). Les rémoires magnetiques dynamique sont très utilisés: faible coût au bit, capacités importantes, vitesse de transfert de plusieurs méga caractère /1.

Les nécoires fichiers sont constitués par des bandes magnétiques à accés séquentiel.

## CHAPITRE I

## LES MEMOIRES ACTUELLES:

Nous le parlerons pas des mémoires à lignes de retard cour elles sont très peu utilisés vus leur enconbrement et la déformation du signal lorsque le retard devient considérable. A l'heure actuelle, les mémoires les plus répendues sont les mémoires à tors de fenite. Elles sont simple, de grande fiabilité, de temps d'accés très court (s), de prix de revient et de consommation relativement faibles.

#### I. 1 LES MEMOIRES A TORES DE FENITE

#### I. 1.1. LE TORE DE FENITE:

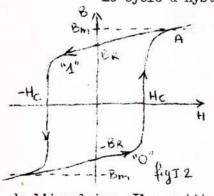

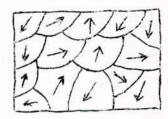

Les fénites sont des oxydes nixte de fer trivalent et d'im nétal divalent. Ils ont des propriétés magnetiques voisines de celles des corps ferromagnetiques, les fenites utilisés pour les ménoires sont à base de manganèse; ayant un champs coercitif assez faible et une réduction rémarente voisine de l'iriduction de saturation, ils ent donc un cycle d'hystérésis rectangulaire.

Un courant dans le fil aversant le tore de fenite crée dans l'espace un champ magnetique H qui produit une réduction magnetique B dans le tore ( fig II1).

Du fait de la taille et de la forme du tore, l'iriduction R est constante et ne dépend pas de la position on de l'inclinaison du fil à l'intérieur du tore.

# I. 1.2. : ECRITURE ET LECTURE D'UNE INFORMATION

Le cycle d'hystéresis et rectangulaire (fig II 2.):

Une impultion de courant positive crée un charps H positif qui fait déplacer le point de fonctionnement à droite au delà du point C. et vient se placer au point + BR- Une impulsion négative place le point de fonctionnement au point -BR- le tore se place donc dans une position ou dans l'autre suivant le signe de l'implulsion de courant. Il reste ensuite dans cette position jusqu'à nouvel ordre se xouvenant du signe

de l'impulsion. Il constitue donc une némoire unitaire. On adoptera la convertion suivante:

induction + BR pour l'information 1.

induction - BR pour l'information 0 -

la fig II 3 montre que pour écrire un 0, on envoie un courant I dans le fil avec un sens tel que le point de fonctionnement soit au point

. . .

de 0 1 calchere

lecture

lecture

bas du cycle d'hystérésis - Pour écrire un 1, on envoie une impulsion de courant de signe opposé.

Pour lire on envoie dans le fil d'écriture une impulsion I, dont le sens est choisi de façon à amener le point de repos

du tore au point haut du cycle à l'iriduction + Bn.Si le tore avait emmagasiné l'information 0, en grande variation d'iriduction - Br à + Bn donne une forte tension induite sur le fil de lecture.

Si le tore avait enmagasimé l'information 1, la faible variation d'induction + Br à + Bm donne une faible tension induite sur le fil de lecture.

En fin d'impulsion de lecture l'induction revient sur + Br quelle que soit à l'information lue. La lecture détruit donc l'information contenue dans le tore. Elle est destructive. Dans la mémoire, les tores sont groupés en mots - Toute la technique des mémoires à fenite consiste à mettre en oeuvre des organes de sélection écononiques permettant dé atteindre facilement le contenu du mot que l'on désire lire. Les némoires à fénite se clament suivant le mode de sélection utilisé.

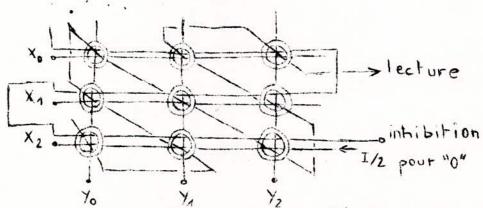

## I. 1 3 MEMOIRE A COINCIDENCE:

C'est le mode de réalisation le plus usuel. Chaque tore est traversé par 4 fils: fil X, fil y, fil d'inhilision, fil de lecture.

Supposons tous les tores dans l'état 0 (soit - Br ) Pour écrire 1 dans un tore déterniné, on envoie un courant +  $\frac{1}{2}$  ( I étant le courant nécessaire au basculement sur le fil X de la rangée où se trouve le tore choisi et un courant +  $\frac{1}{2}$  sur le fil Y de la colonne correspondante; seul le tore choisi subira le champ du courant I et passera à l'état.+  $\beta_r$  ( $\frac{1}{2}$   $\frac{1}{4}$   $\frac{1}{4}$ ).

Pour écrire 0, on envoie un courant  $-\frac{I}{2}$  sur le fil d'inbibition. Pour lire le tore, on fera passer -I/2 dans le fil X et -I/2 dans le fil Y, ce qui fera basculer le tore sélectionné en Br et donnera naissance à une impulsion sur le fil de lecture. Toute écriture doit être suivie soit d'une lecture soit d'une remise à Zéro (R à Z). La lecture est destructive lorsqu'elle se fait par R à Z de tous les tores.

C'est un grand inconvénient car on peut en avoir besoin par la suite. On prodédera à une réécriture après chaque lecture.

Le temps minimal entre 2 ordres de lectures successifs d'une même mémoire est de l'ordre de la icroseconde pour les mémoires de plus d'un millier de mots.

## I. 1.4. AUTRES TYPES DE PEROIRES A FERRITE

On utilise des plaques de ferrites percées de trous dans lesquels passent les fils de commande. Le courant passant dans les fils aimante les bords du trou qui acquiérent une aimantation rémanente dont le sens dépend dusens du courant. RCA fabrique actuellement de telles rémoires avec un temps de cycle de 0,31. Ces dispositifs sont rapides et évitent le câblage des tores.

## I. 1. 5 CONCLUSION:

Les mémoires de tores sont encore utilisées de façon systématique à cause de leur:

- très grande robustesse.

- encombrement réduit

- temps d'accés moyen faible et en constante diminution grâce aux progrés réalisés dans la fabrication des tores.

- Insensibilité relative aux variations de  $t_{\rm e}$ mpérature grâce aux progrés récents de la technologie.

- Les informations restent en émoire nême en cas de panne ou d'arrêt de la machine. Les inconvénients sont:

- Les courants de commande ont des valeurs élevées ( quelques centaines de ma par tore).

Il est impossible de remplacer un tore ddéféchieux dans une matrice et, en cas d'avarie d'un tore il faut éliminer la totalité de la matrice.

- un prix élevé dû aux difficultés de câblage.

# I.2 LES ÆMOIRES A TAMBOURS MAGNETIQUES.

Un tambour magnétique est constitué par un support cylindrique recouvert d'une couche d'oxydes magnétiques. Le tambour qui tourne à vitesse uniforme est divisé en un certain nombre de pistes; à chacune desquelles est affectée une tête de lecture-écriture. Chacune des têtes est un électro-ajmant comportant un entrefer très petit et disposé très près de la surface du tambour.

Pour écrire, on envoie une impulsion sur l'électro - aimant qui crée un

petit doublet magnétique sur la surface cylindrique; lorsque l'amplitude de l'impulsion est suffisante, la couche magnétique est saturée et le doublet persiste après supression du courant. Lorsque ce doublet repasse sous la têto de lecture, il induit dans l'électro- aimant une f.é.m qui pourra donner maissance à une impulsion si l'ampli de lecture est débloqué.

On notera que la lecture est non destructive et l'information non volatile.

## I.2.1 CONCLUSION:

Les tambours magnétiques sont utilisés comme mémoires secondaires de grandes capacité. En effet, la densité d'information est de l'ordre de 2 à 10 bits /mm de piste et l'on fait des tambours pouvant stocker jusqu'à 10<sup>8</sup> caractères. Le prix de revient du bit stocké est faible. En outre, la fiabilité est grande et le temps d'accés relativement court ( quelques ms).

## I. 3 . LES DISQUES MAGNETIQUES.

Ils sont obtenus en recouvrant les 2 faces d'un disque rigide (1 à 2 nm d'épaisseur, 40 à 120 cm de dianètre ) d'un enduit magnétique et empilés jusqu'à 50 disque/pile. La sisposition des têtes de lecture-écriture est variable. Pour une tête de lecture - écriture par pile, le positionnement est obtenu par voie pneumatique en deux temps:

- -Positionne ent en face du disque sélectionné.

- Positionnement sur la piste sélectionnée.

Une des mémoires à disques IBM comportait 50 disques à 1200 tours/nn sur un axe vertical commune chaque disque comportait 200 pistes pouvent stocker 600000 bits. Il y a une seule têt<sub>e</sub> de lecture - écriture et le temps d'attente est inférieur à 800 ms. D'autres ont une têt<sub>e</sub> de lecture-écriture par face de disque, ce qui réduit le temps d'accés (50 à 100 ms). Il exist<sub>e</sub> des mémoires à disques où la pile est intechangeable (dispacks I B h). Leur utilisation est très commade. Le dispack standard permet de stocker jusqu'à 8.106 caractères.

# I.4 LABANDE MAGNETIQUE:

La bande magnétique est réalisée avec un ruban de matière plastique (mylar) très résistant et recuvert d'une couche magnétique homogène comprenant des pistes.

La mise envitesse ( 1 à 5 m/s) pose des problèmes à cause des accélérations très importantes mises en jeu. Il exist $_{\rm e}$  2 solutions usuelles pour la réalisation:

- Utilisation de 2 bobines sur lesquelles est enroulée la bande, mais celle -ci présent<sub>e</sub> un "nou" important entre les bobines et le dispositi<sub>r</sub> de lecture-écriture.

- utilisation d'un carter plat dont les 2 faces sont exactement distantes

de la largeur de la bande et dons lequel elle repose librement; la bande ne peut guére dépasser quelques dizaines de nétres de longueur si elle forme une boucle sans fin, et une centaine de nétres dans le cas où les extrémités sont libres. la bande magnétique est le moyen de stockage le plus dense et le plus économique. En efact, la densité d'enregistrement est comprise entre 20 bits /m et 60 bits /m et la vitesse de transfert est de l'ordre de 800000 bits /s. Le temps d'attente est considérable, plusieurs dizaines de secondes. La bande magnétique n'est intéressante que lorsqu'il est possible de procéder à des enregistrements de grande longueur (enregistrement par blocs, tenue de fichier). Sa lecture est non destructive et l'écriture non volatile.

Dans le donaine de la gestion et du dépovillement statistique ou dans le donaine de la recherche automatique de l'information (bibliographie et documentation), le volume à stocker est gigantesque et l'emploi de la bande meg étique s'y prête bien. Actuellement, les bandes magnétiques tendent de plus en plus à remplacer les disques.

## I.5 CONCLUSION:

L'évolution des calculatrices met en évidence une tendance permanente à l'accroissement du volume de la mémoire.

- Les nénoires auxilliaires ( nénoires périphériques et de masse).

inexistantes sur les premières machines sont passées de la dizaine de nilliers de nots

à quelques nillions pour atteindre le nilliard de nots et plus.

#### CHAPITRE II:

## Les némoires à CI (Circuits Intégrés) nos

Jusq'en 1970, les némoires magnétiques ont dominé un marché dont l'Informatique et le calcul ont été les principaux clients. Avec les Mos, le marché des némoires commence de plus en plus à devenir important. Le prepier coup d'envoi fut donné en 1970 par la firme IBM en annonçant le 370/145 et L'IBM 3, doté de némoires à circuits Intégrés dont le rapport performances/ Prix est supérieur à celui des tores, pour plusieurs raisons, entre autres:

- La densité en bits- mémoires est plus élevée avec les circuits intégrés.

- La consonnation est faible : quelques micro-watts avec la MOS dynamique, alors qu'elle est de un milliwatt par tore.

- Le temps de cycle: 700 ns avec la MOS statique

200 400 ns avec la HOS dynamique

10 ns avec la logique non saturée

à mode de courant type MECL Motorola

500 à 1000 ns avec les tores.

Le prix du bit némoire est de plus en plus en baisse.

## III. 1 LE TRANSISTOR M.O.S.

Le transistors à effet de champ à grille isolée ou MOS (nétal -oxyde-semiconducteur ) se prête parfaitement à l'intégration. C'est ce que prouve son processus de fabrication, qui va tout d'abord être d'écrit.

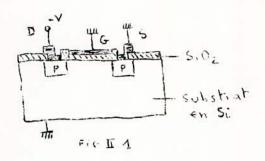

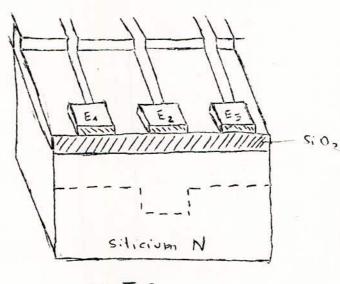

Soit un substrat de silicium de type N ( fig II . 1). On procéde à une oxydation, suivie par une première opération de photo gravure et par la diffusion d'une couche P qui constituera la source et le drain.

Puis la surface du substrat est réoxydée et l'on ouvre une fenêtre pour la nétallisation de l'électrode de commande, la grille (ougate).

La couche d'oxyde est alors attaquée pour être portée à l'épaisseur voulue, tandis qu'un autre masque permet de créer les fenêtres pour les connexions. Une métallisation en aluminium recouvre le tout, alors qu'une dernière opération de photogravure permet de ne laisser subsister cet aluminium que là où il est nécessaire.

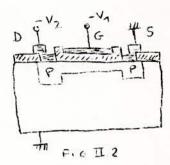

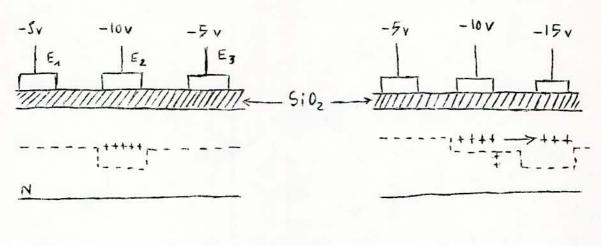

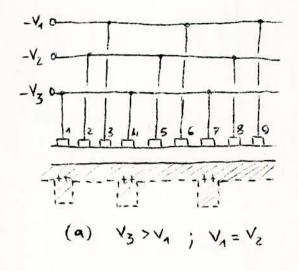

Nous venons de réaliser un M O S à canal P, à enrichissement. En effet l'application d'une tension négative à la grille donne naissance à un canal P, conne le nontre la fig II.. 2.

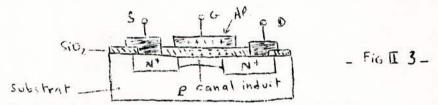

La grille étant portée au nême potentiel que la source, le transistor est bloqué, il ne devient conducteur que si la grille se trouve portée à un potentiel négatif au moins égal à une certaine tension de seuil Vt, Par rapport à la source. Aucune différence de principe ne se manifeste si l'on part d'un substrat de type P, si ce n'est qu'alors, c'est une tension positive qui doit être appliquée à la grille pour attirer les porteurs négatifs et crée un canal (fig II.5).

L'élement produit est du type à enrichissement, mais à canal N, cette fois.

Les circuits à MOS offrent un certain nombre d'avantages. Tout d'abord, on constate que la jonction entre substrat et drain ou source constitue, par construction, une diode Polarisée en inverse : avec les circuits intégrés (CI) à M.O.S il n'est pas nécessaire de prévoir des caissons d'isolement.

Ensuite, on a pu voir qu'une seule opération de diffusion suffisait pour réaliser le M.O.S, alors qu'il en faut quatre pour réaliser un transistor classique. D'autres part, Il n'est plus besoin d'apitaxie. Il en résulte que le prix de revient d'un circuit intégré à M.O.S est inférieur à celui d'un circuit intégré à transistors bipolaires. D'autre part, la densité d'élements peut être accurue, en particulier en raison de l'absence des cai sons d'isolement.

Le gain fourni par un M.O.S dépend de sa géonétrie et non des caractéristiques de diffusion ou de depage. D'autre part, le M.OS se présente avec ses avantages et ses inconvénients: forte impédance d'entrée- supérieure à 10<sup>10</sup> ohns -, faible dissipation, réponse en fréquence limitée par ses capacités.

Notons que, en principe, les zones de drain et de source peuvent être interverties, l'élément étant bidirectionnel. Cependant, par convention, on désigne par source la région P la moins négative, laquelle se trouve reliée au même potentiel que le substrat.

La polarisation négative appliquée à la grille a pour objet de repousser les électrons superficiels du substrat, juste en dessous de la nétallisation de grille, et d'attirer les porteurs positifs, donc d'enrichir cette région en trous, afin d'y créer un canal P. Une tension minimale de seuil Vt, est donc nécessaire pour obtenir ce résultat.

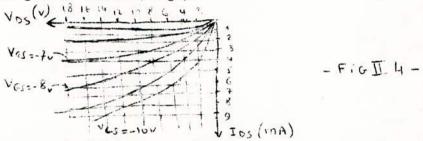

Un réseau typique de courbes donnant le courant drain-source (I ds) en fonction de la tension drain - source (V ds ) d'un H.O.S a été fig. II 4 pour différentes tensions grille-source (V gs).

Linéaires pour de faibles courants, ces courbes inrquent une très nette tendance à la saturation lorque uds augmente. Pratiquement, pour qu'un canal existe, il faut que:

$$Vgs - V_t = VDS$$

.

En valeurs absolues, en supposant que les polarités correstes sont respectées.

La saturation se manifeste pour :  $V_GS - V_t$  VDS , et le courant I D S est alors relativement indépendent de la tension VDS.

Dans la région linéaire, on a : VGS - VT VDS .

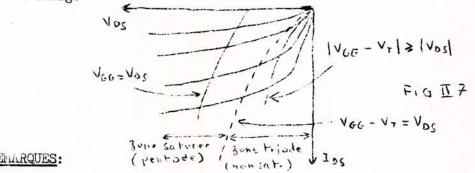

Le M.O.S peut servir de résistance de charge. Copendant, il convient de distinguer deux modes de fonctionnement:

# a) Régine saturé (Zone pentode):

Soit le schona de la fig II 5, lequel représente un 11.0.S

Avec, en série, une impédance de charge constituée par un second M.O.S. Si l'on appelle VGG la tension appliquée à la grille à la grille de T2, les conditions de saturation sont:

La méthode la plus simple, pour aboutir à ce résultat consiste à relier la grille de T2 à la tension négative d'alimentation VDD (fig II 6). A ce moment, en effet VGG= VDD et VGS = VDS.

Supposons alors que le courant de saturation de T1 soit largement supérieur à celui de TZ, et plaçons nous dans les conditions extrêmes. Si T1 est saturé, la tension de sortie est proche de la masse. Au contraire, si Tlest bloqué, son faible courant de fuite traverse également T2, produisant

> Une chute de tension égale à VT b) REGIME NON SATURE (Zone triode):

La condition de non saturation s'écrit: VGG- VT V DS et s'obtient en appliquant à la grille de T2 une tension plus négative que V DS d'une quantité égale ou supérieure à VT - si à ce moment, T1 est bloqué, on trouve pratiquement VDD à la sortie. En revanche, sit T1 est passant, la sortie est approximativement au niveau de la masse, En effet, la chute de la tension drain - source d'un M.O.S. non saturé est très faible.

Les courbes de la figure III. 7 contrent comment évoluent les caractéristique drain - source ducourant en fonction de la tension VDS, Pour un M.O.S utilisé en résistance de charge.

REMARQUES:

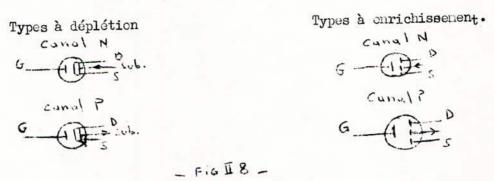

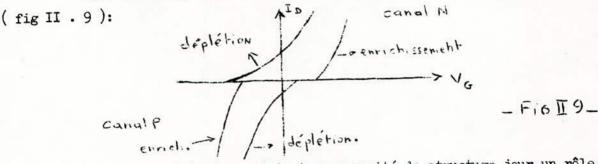

\* - On avu que la grille est l'électrode de commande. En effet, quand on applique une tension entre la source et le drain, le courant qui circule entre ces 2 électrodes est controlé par la tension appliquée sur lagrille. Le M O S présente alors une co nduction par trous ou par électrons. Les éléments qui utilisent des électrons come porteurs sont dénormés " à canal N " ceux qui autilisent des trous sont"à canal P ". ceux qui sont bloqués lorsque la tension grille- ource VGS est nulle sont du type à enrichissement et ceux qui sont passents en l'absence de polarisation de la grille sont du type à appauvrissement ou déplétion. Pour les besoins de la logique, nous utiliserons donc le MOS à enrichissement.

\*- La représentation symbolique d'un M 0 S n'a pas subi une normalisation.

Un mode de dessin, proposé per certains fabricants, est indiquéfix II-8.

Pour les 4 types de MOS on obtient les caractéristiques suivantes

\*- La capacité gate- substrat ou capacité de structure jour un rôle important dans le fonctionnement en " dynamique de l'élement (fig II.10):

L'opération de charge et de décharge de la capacité s'effectue par le MOS inverseur ou la charge de l'étage précédent. Lorsque l'inverseur est bloqué, le condensateur se charge par le MOS en charge de l'étage 1 de résistance R2 ( constante de temps R1 C).

Lorsque l'inverseur est saturé, la capacité se décharge p.r l'inverseur de l'étage 1, dont la résistance du canal Ron est à peu prés 10 fois plus faible que RL. La décharge est donc plus rapide que la charge.

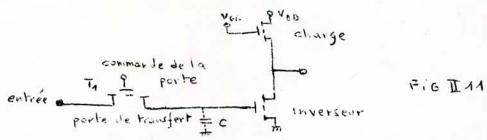

On utilise la capacité de structure pour nénoriser une information (fig II. 11):

Le MOS T<sub>1</sub> est utilisé come interrupteur. Il sert à charger C au niveau 1 ou 0, puis il est bloqué. La capacité de structure est isolée et conserve sa charge; celle-ci s'éliminera peu à peu par le courant de fuite source- drain de T1, mais la constante de temps est suffisamment importante pour qu'il n'y ait pas perte d'information.

#### AVANTAGES ET INCONVENIENTS EES MOS:

- a) Rappelons les avantages:

- les MOS sont plus faciles à intégrer.

- les caissons d'implement sont inutiles.

- la densité d'intégration est plus grande.

- la forte impédance d'entrée

- la faible consormation.

- le couplage direct est possible, ce qui permet de les utiliser conne interrupteurs, résistances de charges. et en éléments de ménoire.

- -Possibilité de concevoir des circuits à fonctions complexes.

- b) les inconvénients sont:

- les MOS sont très sensibles à la contamination aux impuretés et aux charges d'électricité statique.

- la limitation de la fréquence maximale de fonctionnement

- les tensions de seuil élevées

La dérive temporelle et thermique.

Ces inconvénients sont plus ou noins atténués par de nouvelles conceptions technologiques qui ont pour but de:

- diminuer la tension de seuil par l'implantation ionique.

- augmenter la rapidité par l'emploi des MOS

#### complémentaires

- diminuer les capacités d'entrée pour augmenter la rapidité (implantation ionique).

- agrandir les intervalles de température de fonctionnement.

## II.2 CELLULES STATIQUE- CELLULES DYNAMIQUES:

La tention d'alimentation VDS et la tension de comande VGS sont positives avec le canal N, négatives avec le canal P. Le principe de fonctionnement est identique pour les deux types. Avant d'aborder l'étude des cellules, il est interessant d'étudier les deux modes de fonctionnement du circuit inverseur en MOS à enri chissement.

## II.2.1. FONCTIONNEMENT EN STATIQUE:

Le circuit inverseur est le circuit de base de teutes les portes logiques "et-non". Corme on l'a vu, on le réalise avec un transistor MOS T<sup>2</sup> de grande résistance qui constitue la résistance de charge et d'un transistor MOS T<sup>1</sup> de faible résistance qui est l'élénent de commutation. On rappelle que le circuit a deux nodes de fonctionnement: régime saturé et régime non saturé.

Le niveau de sortie lorsqu'on applique un état 1 sur la grille  $T_1$  dépend de la géométrie des deux éléments  $T_1$  et  $T_2$ , de la tention d'alimentation et des tensions de commande sur les deux grilles.

## II.2.2. Fonctionnement en dynaHique:

Dans les circuits MOS la fréquence de coupure est de l'ordre de 1 GHz. Cependant, dans les circuits complexes, elle est beaucoup plus basse, parce qu'à chaque commutation, des capacités douvent être chargées et déchargées à travers des impédances qui atteignent souvent de grandes valeurs. Deux types de capacité dominent:

- La capacité entre la grille et le subtrat ou capacité de structure

- Les capacités d'interconnesions, formées par les interconnexions,

- l'oxyde épais et le sulstrat.

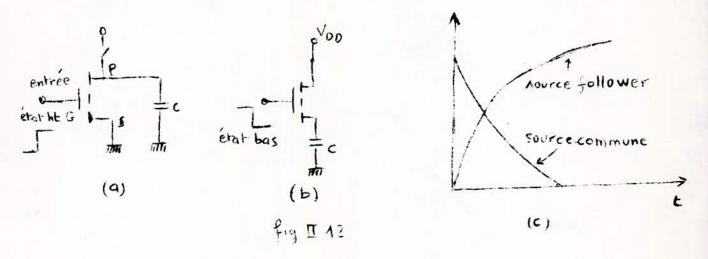

En dynamque, on trouve deux types de fonctionnement, le node source commune et le node source follower. Le node source commune est representé par la figure .II 12 a. Il est caractérisé par la décharge d'un condensateur à travers TR lorsqu'on applique un échelon sur son entrée. Plus la constante Rds. C sera petite et plus la décharge sera rapide. Le node source follower (fig.II 12 b) consiste en la charge de la capacité C à travers TR, Lorsqu'on applique un échelon de tension sur son entrée. Comme dans le cas prédédent, la réponse en temps dépend de la constante de temps RDS. C. Mais tandis qu'en node source commune, la tension VGS est constante, elle diminue au fur et à nesure que la capacité C se charge en node source follower, donc la résitance RDS et la constante de temps RDS. C augmente.

La réponse en temps (fig II.12 C) d'abord rapide sera lentit donc au fur et à mesure que la charge de c croît. D'autre part, la valeur finale de charge de la capacité est égale à VGS-VT.

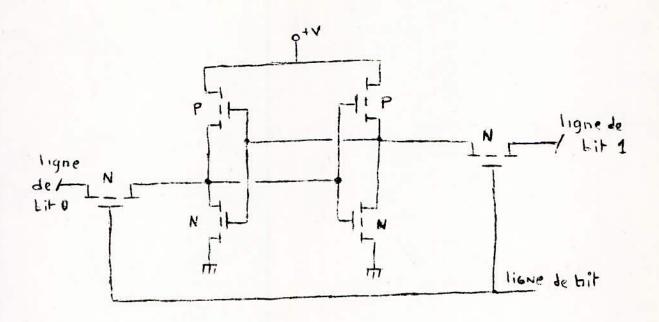

# II. 2.3. LA CELLULE MOS STATIQUE:

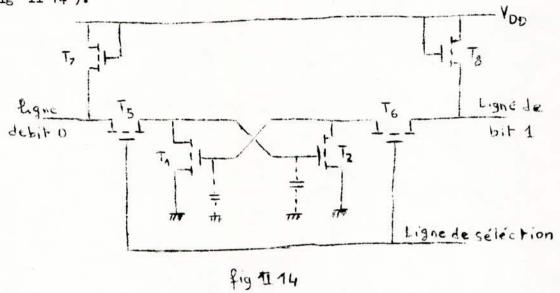

C'est un simple flip-flop doté de deux portes de transfert T5 et T6 et deux circuits inverseurs (fig II 13) dont l'entrée

de l'un est relié à la sortie de l'autre. T<sub>1</sub> et T<sub>2</sub> sont les transistors de commutation, T<sub>3</sub> et T<sub>4</sub> les transistors de charge. T<sub>5</sub> et T<sub>6</sub> sont des portes qui nettent la cellule en contact avec l'extérieur par l'intermédiaire de deux lignes debits.

Chaque ligne de bit véhicule une des deux informations binaires (  $\circ$  et 1) entr<sub>e</sub> l'extérieur et la cellule mémoire.

Si T<sub>5</sub> et T<sub>6</sub> sont fermées, la cellule est isolée et conserve en mémoire

2.1

l'information écrite. Dans ce cas, l'in des inverseurs est à l'état bas (le transistor de commutation est conducteur), l'autre est à l'état haut. L'inverseur à l'état bas dissipe de l'énergie tandisque l'inverseur à l'état haut laisse passer un très faible courant et ne consonne pratiquement aucune puissance.

Supposons qu'un " 1 " soit stocké en nénoire, c'est à dire que l'inverseur ( $T_1$ ,  $T_3$ ) soit à l'état haut et que l'inverseur ( $T_2$ ,  $T_4$  soit à l'état bas.

Pour lire la cellule, T<sub>5</sub> et T<sub>6</sub> sont rendus passants par l'intermédiaire d'une impulsion appliquée sur la ligne de sélection. Un courant s'écoule dans la ligne de bit 1 à travers T<sub>8</sub>, T<sub>6</sub> et T<sub>2</sub>. Aucun courant ne s'écoule dans la ligne de bit 0. La détection du courant sur la ligne de bit 1 caractérise donc l'état 1. La présence d'un 0 dans la cellule ménoire donnerait un courant sur la ligne de bit 0. La lecture est une opération rapide, qui ne subit aucun retard de la part de la cellule. Elle n'est pas destructive de l'information. L'opération d'écriture débute, comme celle de lecture, par l'ouverture des port<sub>e</sub>s T<sub>5</sub> et T<sub>6</sub>. La cellule ménoire est alors en relation avec les circuits d'écriture.

L'écriture d'information à l'intérieur de la cellule se fait en portant l'une des lignes de bit à l'état bas. Si la ligne de bit 1 est reliée à la masse, rien ne se produit, car la grille de T<sub>1</sub> est déjà à l'état bas. Si la ligne de bit 0 est à l'état bas, la cellule doit changer d'état.

Cette opération se déroule en deux temps:

- la capacité de grille  $C_2$  de  $T_2$  se décharge à travers  $T_5$  fonctionnant en source commune. Dès que la tension aux bornes de  $C_2$  est inférieure à la tension de seuil de  $T_2$ , ce dernier se bloque.

- La capacité de grille C<sub>1</sub> de T<sub>1</sub> se charge en node source follower à travers T6 et T8 ( Tu est une grande impédance et a peu d'inflûence). Lorsque la tension aux bornes de C<sub>1</sub> est supérieure à la tension de seuil de T<sub>1</sub>, T<sub>1</sub> so met à conduire. La charge de C<sub>1</sub> doit être suffisamment grande, pour que le transistor T<sub>1</sub> soit suffisamment conducteur et qu'il y ait un état bas à la sortie de l'inverseur (T<sub>1</sub>,T<sub>3</sub>).

Nous avons vu précedement que la charge d'une capacité en source follower est beaucoup plus longue que la décharge en source Commune. La séquence d'écriture dépend donc essentiellement de la charge de la capacité de l'un des trasistors de commutation. La durée de cette charge conditionne la durée des impulsions appliquées sur la ligne de sélection, car T5 et T6 doivent être passants pendant la durée de cette charge. Les performances d'écriture peuvent être anéliorées en augmentant les gains de T5 T6,T7, T8, donc en diminuant leurs résistances. Copendant il y a une

limite supérieure sur le gain de ces éléments. En effet, en lecture, la cellule peut être perturbée par un courant trop intense à travers le transistor de commu tation passant (T<sub>1</sub> ou T<sub>2</sub>) dont le drain monte à un potentiel supérieur au seuil du transistor de commutation bloqué. Ce dernier se net alors à conduire et peut perturber le contenu de l'information.

La réalisation d'une cellule à six éléments est un compronis entre plusieurs exigences. Elle est relativement complexe, car elle nécessite plusieurs types de transistors de commutation très conducteurs, des transistors de charge très résistifs et des portes suffissament conductrices pour que l'écriture soit suffisament rapide et la lecture non perturbée. De plus, elle occupe une surface relativement importante.

L'intégnation sur une pastille de ce type de cellule est donc assez limitée. A l'état de repos, lorsque la cellule n'est pas adressée, l'information est conservée en permanence. C'est le fonctionnement statique. Ce type de fonctionnement apporte de la souplesse à la logique, qui entoure la ménoire et permet de lire l'information stockée à n'importe quel noment. Cet avantage entrâine cependant une dissipation permanente de puissance dans la cellule.

## II.2.4. LA CELLULE M.O.S. EN DYNAMIQUE

En dynamique, la cellule à six éléments est complexe, difficile à réaliser et ne permet pas de tirer tous les avantages de la technologie MOS. Les inconvénients sont:

- dissipation de la cellule à l'état de repos.

- surface importante occupée par la cellule.

- cycle d'écriture long.

Dans la némoire à six éléments, l'information est co nservée sur l'une des capacités de grille  $C_1$  ou  $C_2$  des transistors de commutation (  $T_1$  ou  $T_2$  ), et le rôle des résitances de charge  $T_3$  et  $T_4$  est de compenser les courants de fuite qui ont tendance à décharger ces capacités. Les transistors  $T_3$  et  $T_4$  ont une grande résistance pour limiter la dissipation et occupent une grande surface.

Pour réduire la puissance dissipée à l'état de ropos, les transistors  $T_3$  et  $T_4$  peuvent être rendus passants périodiquement par des impulsions appliquées sur leur grille. En l'absence de ces impulsions,  $T_3$  et  $T_4$  sont bloqués, la consormation est négligeable. En présence de ces impulsions  $T_3$  et  $T_4$  sont passant et viennent recharger ou "rafraîchir les capacités des éléments actifs ( $T_4$  ou  $T_2$ ). Le cycle de lecture se déroule comme précéderment. Le cycle d'écriture ne peut avoir lieu

que si T3 et T4 sont passants. L'intervalle séparant deux impulsions est de quelques nillisecondes. Les cycles d'écriture ou de lecture ne sont pas affectés par l'opération de rafraîchissement. Ce type de fonctionnement où l'information est périodiquement regénerée, est appelé fonctionnement dynamique.

Les transistors T<sub>3</sub> et T<sub>4</sub> occupent une place importante et ne sont pas, en fait, nécessaires pour les cycles de lecture, d'écriture et de rafraîchissement. leur suppression permet de réduire substantiellement la taille de la cellule (fig II 14).

La régénération de l'information se fait au cours d'un cycle lecture. En appliquant une impulsion sur la ligne de sélection, T5 et T6 sont passants et se comportent comme des charges les éléments actifs T1 et T2. Un bistable est ainsi reconstitué et la capacité de grille qui contient l'information est rechargée par le courant qui s'écoule à travers la ligne de bit associé.

Le principe de fonctionnement de cette cellule est inentique à celui de de la cellule à six éléments. En dynamique, la consommation est légérement supérieure, puisque T5 et T6 sont des résistances moyennes. Les cycles d'écriture, de lecture et de rafraîchissement ne peuvent se dérouter que si T5 et T6 sont conducteurs, donc lorsqu'une impulsion est appliquée sur la ligne de not, cette contrainte nouvelle permet de diminuer la taille de la cellule.

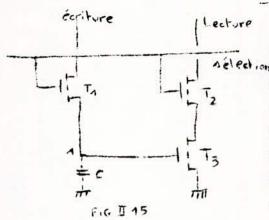

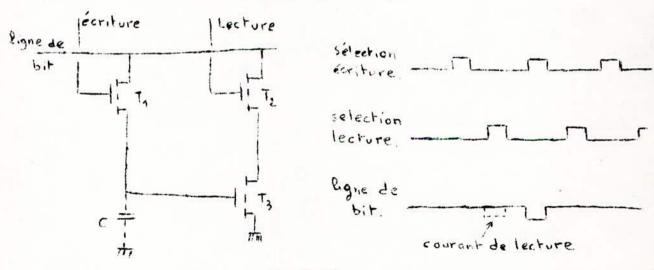

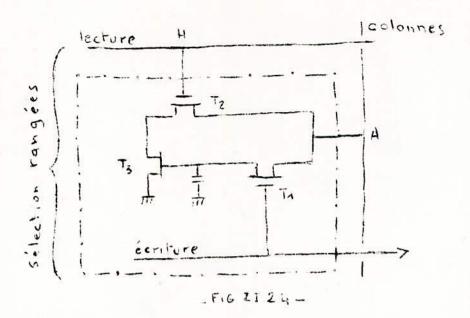

Dans le montage présédent, l'information est stockée dans une des capacités des transistors de commutation ( $T_1$  ou  $T_2$ ). Ceci est redondant; une seule suffit donc (fig II 15).

Cette cellule comprend: l'élément némoire proprenentdit, constitué par T3 et sa capacité de de grille et deux portes, T1 qui met en contact la cellule avec les circuits d'écriture et T2 qui transmet l'information carragasinée sur c vers les circuits de lecture. Le cycle de lecture s'obtient en activant T2 - Les éléments T2 et T3

forment une porte "ET." T3 est passant ou non suivant que l'information stockée est un 1 ou 0. La présence ou l'absence d'un courant sur la ligne de lecture déternine l'état de la cellule, donc l'information emagasinée.

T<sub>1</sub> et T<sub>2</sub> ant des tensions de seuil différentes. La tension de seuil de T<sub>1</sub> est supérieure à celle de T<sub>2</sub>, pour que le cycle de lecture ne déclenche pas simultanément un cycle d'écriture. Pour que le cycle de lecture ne déclenche pas sumultanément un cycle d'écriture. Pour tourner cette sujétion, on utilise deux lignes de sélection: d'écriture et de lecture (figII . 16).

F.G I 16

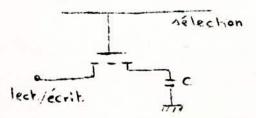

On voit ici que les ordres de sélection sont l'amplitude égale. Si l'on nénorise l'information dans une capacité de grille, la plus simple des cellules est celle de la figure II 17.

L'inscription s'effectue en portant la ligne bit au niveau voulu et en débloquant le transistor MOS à l'aide de la ligne sélection. La lecture est également assurée Par le déblocage du MOS, soit en appréciant la tension de charge C, soit en utilisant l'impulsion de décharge.

Ici, la lecture est destructive, et la charge stockée par c est redistribuée à la lecture aux capacités de la ligne bit; de plus, la vitesse d'écriture est limitée par la capacité de C sui doit être suffisament importante.

C'est cette formule qu'a choisi en 1971 General Instrument en annonçant une RAM de 2048 bits. La surface occupée par un point - némoire est de 0, 002 nm², la puce de silicium mesurant à peu près 3,5 x 3,5 nm, circuits de décodage et de logique compris.

Le temps d'accés en lecture serait inférieur à 250 ns, pour un cycle de moins de 400 ns ; la consonnation aux fréquences les plus élevées n'atteindrait que 300 mw.

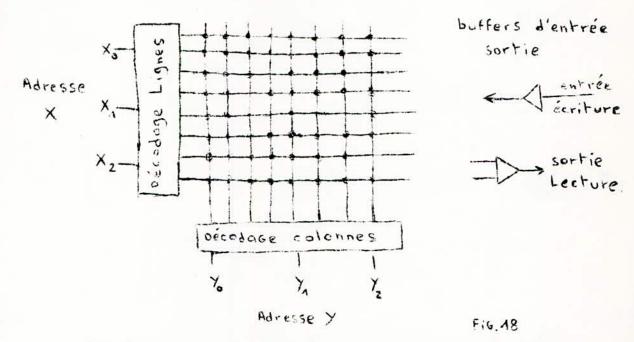

## II.3 MEMOIRES VIVES.

Elles sont encore appelées RAM (Random Access Memory) ou némoires à accés aléatoire ou à accés direct. La mémoire vive a MOS se présente sous forme de boîtier DIL à 14,16, 18, 24 broches ou plus. Elle est constituée par un ensemble de cellules élémentaires disposées en natrice, comprennant x rangées et y colonnes. Chaque cellule peut être écrite on lue. Elles sont toutes directment accessibles par adressage. L'adressage se fait en sélectionnant le numéro de la rangée et le numéro de la colonne de la cellule concernée. Le plus souvent, l'adresse est appliquée en code binaire sur le boîtier, la décodification étant en terme. La décodification des adresses sur la patille de la némoire vive a un certain nombre d'inconvénients. Les circuits de décodification augmente la surface de la pastille et la puissance dissipée. Ils sont faits avec des transistors MOS qui ont le désavantage d'être lents, donc d'autementer les temps d'écriture et de lecture. Par contre, l'incorporation de la décodification dininue le nombre d'interconnexions, permet l'utilisation de boîtier avec un nombre de broches réduit et donne peut-être une fiabilité plus grande.

La décodification à l'extérieur du boîtier par des cirquits bipolaires est souvent le noyen optimal pour beaucoup d'applications. La technologie bipolaire permet d'attaquer les lignes d'interconnexions à grande charge capacitive sous faible impédance, donc de dininuer les constantes de temps.

La lecture ou l'écriture d'une cellule ménoire se fait par l'intermédiaire d'amplificateurs dont la première qualité est de présenter une faible impédance. La technologie bipolaire est bien adapter à ce genre de circuits mais ne peut être intéreée sur la pastille ménoire. Par contre, la technologie MOS permet de fabriquer des amplificateurs de lecture et d'écritures d'impédance moyenne. L'intégration de derniers favorise la fiabilité de l'ensemble, mais se fait aux dépens de la rapidité. Les critéres de choix entre les ménoires entiérement décodées et celles qui ne le sont pas, dépendent essentiellement les performances qu'attend l'utilisateur. Les fabricants semblent vouloir de plus en plus s'orienter vers des circuits ménoires complétement décodes.

\* Rappelons que les nénoires vives sont des nénoires volatiles.

#### II.3.1 RAN STATIQ UES:

En statique, une RAM MOS recourt à des cellules fonctionnant en statique (paragrapheII .2.3.).

L'assemblage d'un certain nombre de cellules en un réseau déterminé, de 8 nots de 8 bits par exemple, mène à une némoire dont le synoptique de principe est do nné par la figure II 18

On y trouve les circuits de décodage d'adresse: dans ce cas, l'adresse est fournie sur 3 bits ; chaque point de croisement représente une cellule-ménoire. Les circuits d'écriture et de lecture sont été symbolisés.

# II.3.2 RAM DYNAMIQUE:

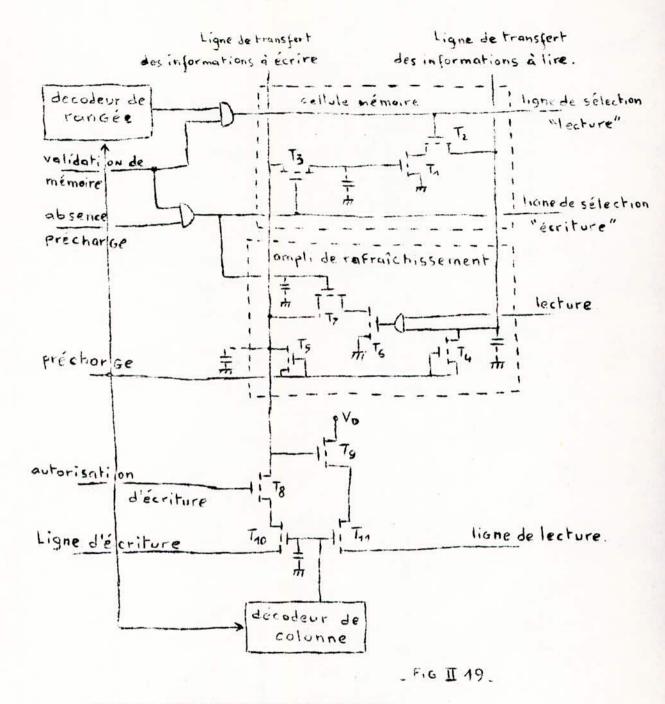

Les cellules utilisées sont dynamiques (voir paragraphe II. 2.4.). D'où une grande densité d'intégration, la vitesse est plus éluvée et la consonnation est relativement moindre.

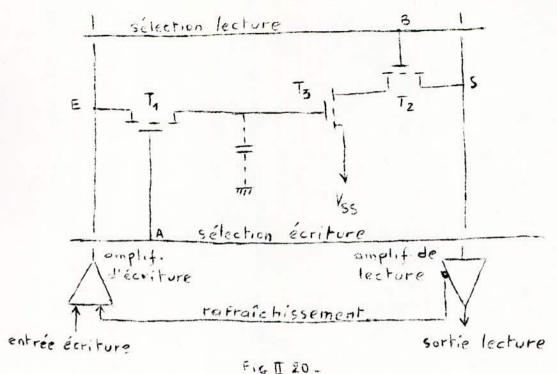

considérons un type de ménoire vive dynamique dont les cellule sont à 3 élèments (fig II 19).

Se déroulement des cycles de lecture et d'écriture est co nditionné par 3 rythmes: la précharge, la sélection de la mémoire et l'autorisation d'écriture;

## \* CYCLE DE RAFRAICHISSEMENT:

Le signal "validation de la mémoire " est appliqué. La ligne de sélection "Lecture " reçoit une impulsion qui rend conducteur T2 et provoque la décharge conditionnelle des lignes de transfert " Lecture". Les lignes dont la cellule contient un état haut sur C se déchargent à travers T1 tandis que les autres dont la cellule contient un état bas conservent leur état haut. Dès que les lignes de transfert "lecture" sont chargées, le signal "précharge" est supriné, provoquant

l'ouverture de T<sub>7</sub> et de T<sub>3</sub>. Les capacités des lignes de transfert "écriture", managées pendant la "précharge", ne se déchargent à travers T<sub>7</sub>et T<sub>6</sub> que si les lignes de transfert "lecture" associées sont à l'état haut. L'information stockée sur C est ainsi transmise sur la ligne de transfert "écriture" qui vient à travers T<sub>3</sub> régénérer C.

## \* - CYCLES DE LECTURE :

Les informations lues dans les cellules de la rangée sélectionnée sont transferrées sur les lignes d'écriture. Le décordeur de colonnes valide une ligne de transfert "écriture" en rendant conducteur T<sub>1</sub> et T<sub>11</sub>. Selon la charge emmagasinée . sur la capacité de cette ligne, T9 est passant ou non et un courant s'écoule ou non dans la ligne de lecture. A la fin du cycle, les informations stockées sur les lignes d'écriture sont réécrites dans les cellules de la rangée sélectionnée.

## \* - CYCLE D'ECRITURE :

Il débute par le rythme de "précharge" suivi du rythme de "Validation de la mémoire". La "précharge" permet de valider les décodeurs. "La validation de la mémoire " ouvre la porte T3 d'accès à la capacité de la cellule mémoire sélectionnée.

L'opération d'écriture est conditionnée par la séquence d'autorisation d'écriture qui ferme  $T_6$  et ouvre  $T_8$ , permettant ainsi d'acheminer à travers  $T_{10}$ ,  $T_8$  et  $T_3$  l'information à écrire.

# II.3.2.1 DEUX EXEMPLES DE RAM DYNAMIQUES.

# II.3. 1. 1 LA RAM DYNAMIQUE i 1103 INTEL.

La némoire i 1103, commercialisée depuis 1970 par INTEL CORP!, est rélisée suivant la technologie du gate au silicium. Une des caractéristiques de cette technologie est une densité très élevée le composants permettant, pour une configuration donnée de némoire, d'obtenir une réduction des prix en diminuant la surface de silicium nécessaire à la réalisation du circuit intégré.

D'autre part, la technique de ménorisation dynamique utilisée permet

d'obtenir des performances remarquables en ce qui concerne les temps d'accès, niveau d'intégration et dissipation:

- . temps d'accès: 300 ns

- ; niveau d'intégration: 1024 bits

- Dissipation : 8nw par bit au repos.

250 nw par bit en adressage.

La nénoire i 1103 est organisée en 1024 nots de 1 bit et se présente sous la forme d'un boîtier DIL à 18 terminaisons.

Elle utilise des cellules dynamiques (fig II20) à 5 élèments. L'information à enregistrer est appliquée à l'entrée E et une commande en A débloque le transistor MOS T1. La capacité de grille se charge au niveau 1 ou 0 de l'information à ménoriser, le transistor To restant bloqué. L'information est lue par l'application en B d'une commande qui débloque le transistor T2 . Auparavant, une tension de " précharge" avait chargé la capacité correspondant à la ligne omnibus à laquelle la sortie lecture s'est directe nent connectée. Selon le niveau 1 ou 0 de l'information mémorisée, le transistor T3 est passant ou bloqué et. dans le premier cas, décharge le ligne omnibus qui passe à la tension V SS. Le niveau de tension de la ligne ormibus est alors détecté par un amplificateur de lecture et peut être utilisé à la sortie de cet amplificateur de lecture. Le fonctionne ent de la cellule de base permet de mettre en évidence la particularité de la nénoire dynamique, à savoir la nécessité d'un rafraîchisse ent périodique de l'information. En effet, la capacité némoire de grille de T3 se décharge progressivement à travers les diverses impédances de fuite. Il est donc nécessaire de rétablir périodiquement le niveau de charge de cette capacité. Ce rafraîchissement est effectué autonatiquement par une opération de lecture. En effet , la sortic de l'amplificateur de lecture est reconnectée à l'entrée E de la cellule lue, tandis qu'une commande est appliquée en A.

Il y a donc dans ce cas, regénération autonatiquede l'information mémorisé.

14 11 20 -

La ménoire nécessite un rafraîchissement toutes les 2ns maximum.

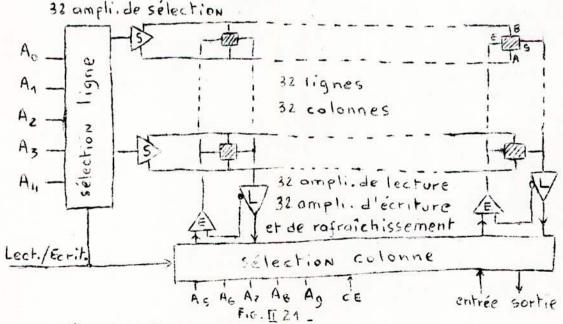

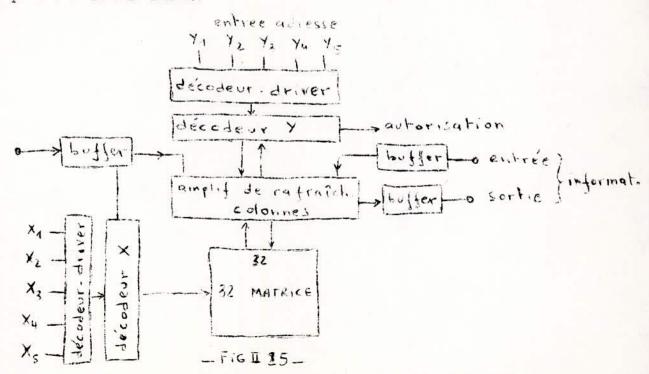

## \* STRUCTURE DE LA i 1103.

le synoptique de la rénoire est donné fig II 21. Les 1024 cellules ménoire sont organisées en une natrice à 32 lignes et 32 colonnes.

1) cycle de lecture:

Le décodage des 5 bits d'adresse de plus faible poids (Ao à A4) permet de sélectionner une ligne de 32 cellules do nt le contenu est lu par 32 amplificateurs de lecture. Cette co nfiguration permet de "rafraîchir" 32 cellules simultanément, à partir des 32 amplifacteurs de lecture. Le décodage des 5 bits de plus fort poids ( A5 à Ag) permet d'aiguiller sur une sortie unique l'information choisie sur les 32 lues initialement.

- 2)cycle d'écriture: L'information d'entrée est aiguillée par le décodage des bits de plus fort poids (A5 à Age) en direction d'un amplificateur d'écriture sur 32, l'écriture s'effectuant à l'intersection de la colonne correspondant à l'amplificateur d'écriture sélectionné et de la ligne sélectionnée et de la ligne sélectionnée par le décodage des 5 bits de plus faible poids (Ao à A4).

- 3) Rafraîchissement: Dans la mesure où un cycle de le cture entraîne le rafraîchissement automatique des informations contenues dans les 32 cellules d'une ligne, un rafraîchissement complet de la mémoire pourra être effectué simplement en 32 cycles de lecture permettant de sélectionner successivement toutes les lignes.

Il est à not<sub>e</sub>r que ces 32 cycles de lecture nécessaires au refraîchissement de la totalité de la mémoire correspondent aux 32 combinaisons binaires possibles des 5 bits d'adresse de plus faible poids, l'état des 5 bits d'adresse de plus fort poids étant indifférent durant le rafraîchissement.

La durée du cycle de lecture de la mémoire i 1103 étant de 580 ns, le rafraîchissement global de la mémoire s'effectue en 580 X 32 = 18,6 ms, ce qui représente moins de 1% du temps utile.

- 4) <u>Précharge</u>: Le signal de "précharge" dont le but est de précharger la capacité des lignes omnibus de lecture (lignes reliant toutes les sorties S des dispositifs) est commun à toutes les lignes de lecture de la ménoire.

- 5) <u>Cenable</u>: le signal " cenable" est une commande de validation supplémentaire qui permet, lors d'un assemblage de plusieurs boîtiers, de sélectionner un seul boîtier ou groupe de boîtiers. Ce signal est nécessaire pour permettre la connexion directe en " ou" des sorties de chacun des boîtiers, dans le cas, par exemple, d'un système comprenant plus de 1024 mots. Dans ce cas, le signal " cenable " bloque le transistor MOS de sortie des boîtiers non adressés.

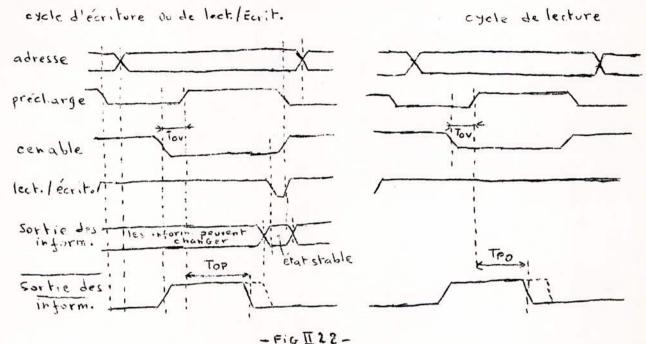

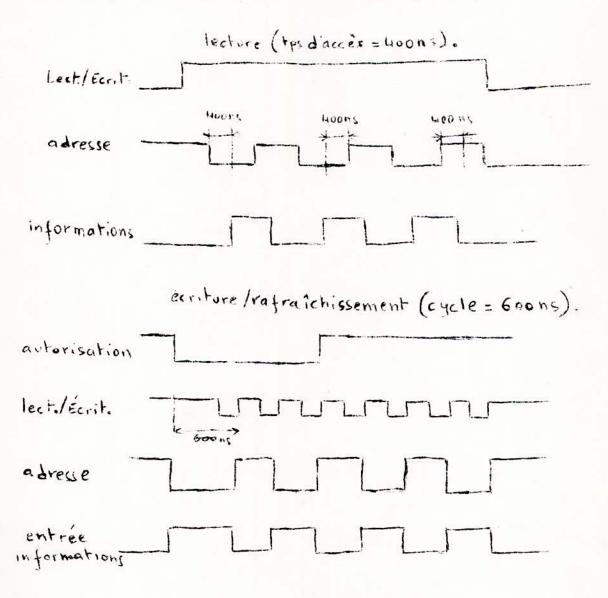

- 6) <u>Diagrame des temps:</u> Il est à noter que les cycles de rafraîchissement sont tout simplement des cycles de lecture. (fig. II 22).

## a) cycle de lecture:

Un cycle de lecture commence par le transition négative du signal " précharge ". Ce signal étant commun à toute la mémoire, le pré-chargement des lignes de sortie peut comencer avant stabilisation des adresses.

Pendant ce pré-chargement, les adresses sont stabilisées et, au bout du temps Tpc après transition du précharge ou TAC après stabilisation des adresses, intervient la transition du "cenable" qui valide la ménoire. Puis :

- Le signal de pré-chargement doit disparaître au bout du temps Tov après la transition de "cenable".

- -. L'information de sortie sera valide au bout du temps T po après Tov.

- Le signal " cenable" doit disparaître au bout du temps Tpov après Tov.

- \_ . Un no uveau cycle de lecture peut commencer après un temps Tcp de disparition de "cenable".

# b) Cycle de lecture écriture:

Le cycle de lecture écriture est identique au cycle de lecture jusqu'à la disparition du " précharge"; La lecture s'effectue de la manière au bout de temps Tpo après disparition du " précharge".

L'écriture peut s'effectuer au bout d'un temps Tpw après disparition du "précharge". L'écriture s'effectue par la transition négative du signal écriture lecture qui doit être maintenu négatif pendant le temps Twp, l'information d'entrée devant alors être stabilisée depuis un temps minimum Tdw avant la transition négative du signal d'écriture lecture.

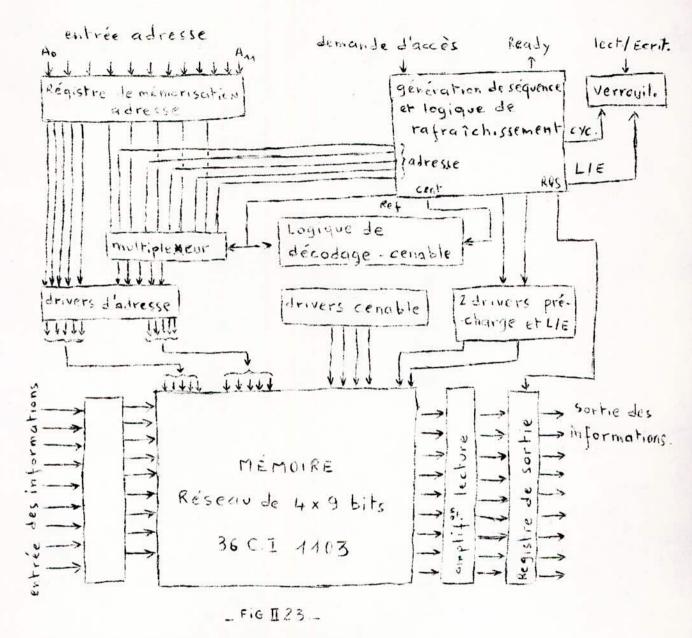

7) Réalisation d'une nénoire de 4096 nots de 9 bits (fig II 23).

# II. 3.2. 1.2 LA RAM DYNAMIQUE MK 4006 MOSTEK

c'est un autre type de RAM dynamique, très avancé, de 1024 mots de 1 bit. Elle ne serait guére différente, en principe, de la précédente si elle n'avait été réalisée per implantation ionique, et si elle ne comprenait des étages inverseurs avec charges MOS à déplétion. Rappelons que la charge à déplétion est conductrice en l'absence même de signal degrille, ce qui permet de gagner en temps de commutation. De ce fait, il n'est plus besoin de commande de précharge. La cellule de base de la MK 4006 emprend 3 éléments (fig II 25):

Chacune des 32 rangées de sélection des cellules (la mémoire est répartie en réseau de 32 colonnes et 32 rangées) dispose de deux lignes provenant de décodeux de rangées; toutes les lignes sont au Vss (subtrat) pour 31 rangées, mais sont négatives pour la rangée sélectionnée.

En position lecture, le noeud H est nétatif et rend conducteur  $T_2$ ; à l'écriture, c'est J qui, devenant nétatif, rend  $T_1$  conducteur. Le point A sert aussi bien à l'introduction qu'à l'extraction des informations binaires.

La figure II 2 donne le synoptique de la M K 4006 et la figure II. 2 61es séquences de fonctionnement:

Là encore, le rafraichissement n'occupe qu'environ 1% du tomps utile (32 cycles 0,65 Ms tous les 2000 Ms).

cette mémoire, comme la précédente et toutes les mémoire MOS plus généralement, peut être assemblée pour constituer des ensembles complexes. La MK 4006 seule consomme 50 Nw et sont temps d'accès est inférieur à 400 ps.

#### II. 4 LES MEHOIRES MORTES.

Appelées encore ROM (Read only-méory), ce sont des némoires à lecture seule. Une mémoire morte contient une série d'informations écrites en binaire. Ces informations, contrairement à ce qui se passe dans les récires vives, sont écrites pour une application donnée et ne sont généralement pas modifiables. Elles peuvent être ensuiste lues à volonté.

l'écriture des données est effectuée en cours de fabrication et n'est pas destructible. Les ROM constituent un donaine important d'application pour la technologie MOS. Elles sont utilisées dans les mémoires de contrôle, les transcodeurs, les générateurs de caractères, la programmation fixe. Dans un ordinateur, elles peuvent remplir le rôle de bloc de calcul et de bloc de commande (microprogramnation). Pour mémoriser l'information, on agit sur l'épaisseur de la couche d'oxyde, placée entre la grille et le subtrat. Si cette couche est fine, la tension de seuil du tramsistor MOS est faible ( stockage d'un 1 ). Si cette couche est épaisse, la tension de seuil est grande ( stockage d'un 0 ). la tension de seuil est donc proportionnelle à la couche d'oxyde. A l'extrême, la création d'une couche épaisse revient à suppriner le transistor M.O.S- En appliquant une impulsion sur la ligne de mot, le transistor MOS à faible tension de seuil conduit tandisque celui à tension de seuil élevée reste bloqué. L'état de conduction et de non conduction d'un transistor MOS en présence d'une impulsion appliquée sur sa grille permet d'identifier la donnée inscritre. La réponse en transitoire d'une telle cellule est rapide, puisque lorsqu'il y a conduction, elle se fait en mode source commune.

La distribution des 0 et des 1 se fait au moyen d'un seul masque pour une organisation déterminée au cours même de la réalisation du circuit intégré, on change le contenu de la mémoire par un simple changement de marque. Donn, l'élimination du cycle écriture permet de simplifier la cellule mémoire qui se réduit à 1 élément (fig II 27):

- F.6 1 27 -

En a) et b) la tension sur la ligne "Mot" doit être plus élevée que la tension às seuil du transistor pour le débloquer, mais cette ligne n'offre qu'une charge capacitive et l'immunité au bruit est bonne. En c), la tension plus besoin de tenir compte de la tension de seuil, mais l'isolement des lignes "Mot" et "bit "n'est plus assuré aussi parfaitement, et l'immunité au bruit est mauvaise. Fonctionnant en régime d'implulsions, les circuits en a) et b) sont du type dynamique, tandis que le c) est du type statique.

ordres de l'utilisateur; souvent, ce dernier préparera son programme sur carte perforée.

#### \* Remarques.

Les temps d'accés varient entre 300 ps et 800 ns pour une némoire complète; en 1970, le record semblait appartenir à Hughes airgraft, pionnier de l'implantation ionique, qui annonçait une R OM de 2048 bits recourant à cette technique et caractérisée par un temps d'accés de 100 ns.

La densité d'intégration peut, avec les ROM, être très élevée et dépasse plusieurs k bits. Hewlett packard fabriquait en 1971 des ROM DE 4096 bits à MOS, canal N, alors que des 9 K bits étaient annoncées par MONOLITHIC MEMORIES.

enfin, le prix du bit-mémoire qui étati de l'ordre de 0,05 F en 1971 par quantité pourrait largement diminuer dans les années à venir.

# II.4.2. ROM PROGRAMMABLES PAR L'UTILISATEUR ( PROM ):

Les PROM sont inscrites électriquement après la livraison des circuits intégrés et ce, par l'utilisateur. L'introduction des PROM rend l'emploi des rénoires mortes plus universel. La souplesse de la program ation est exceptionnelle et permet de travailler avec des circuits intégrés. en petites séries et même unitairement.

Les première PROM en MOS ont été annoncées en 1970 par solid state scientific. Les PROM sont surtout utilisées en nicroprogramation.

De nombreuses méthodes de réalisation ont été employées

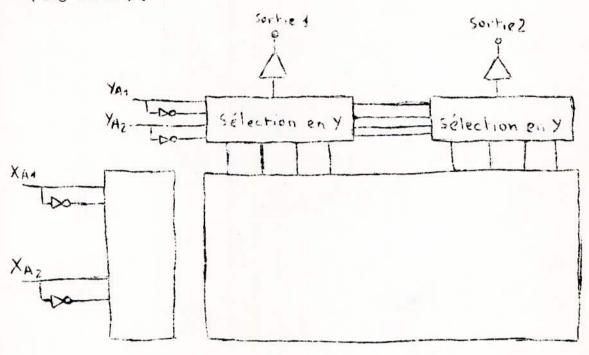

#### II.4.1 STRUCTURE DES ROM

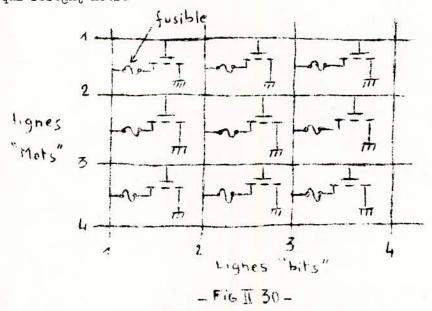

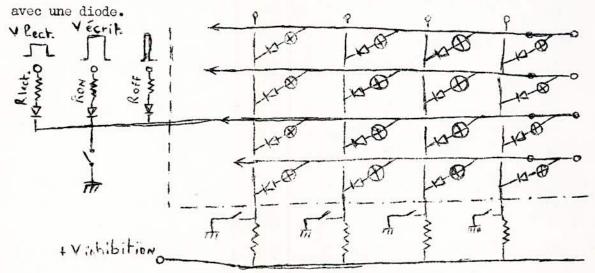

Une structure typique d'une ROM est representée par la figure suivante (fig II 28):

\_ FIG II 28 -

Il s'agit d'un réseau simple de 16 mots de 2 bits, d'où les MOS servant à enregistrer des zéros ont été exclus. On dispose d'un double circuit de sélection en Y parcequ'il s'agit de mots de 2 bits; la lecture s'effectue en appréciant le courant provenant de l'intersection X Y adressée. La distribution des 0 et des 1, c'est à dire la programmation de la mémoire, est assurée par le fabricant sur mais seules deux techniques semblent actuellement être largement diffusées:

- . La technique dite " à fusible".

- . La technique " par destruction de jonction".

# a) Principe du fusible:

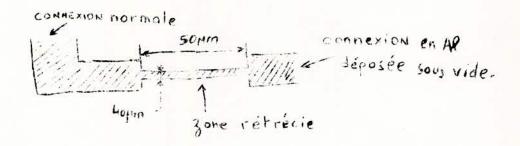

Dans ce type de technologie, la mémoire est construite de telle sorte que chaque ligne de bit est réunie à chaque ligne de met par une seule jonction polarisée dans le sens direct. En série se trouve un "fusible "constitué par une métallisation de surface fine et étroite (fig II 29).

- FIG 1 29 -

La programmation de ce type de mémoire est réalisée en faisant passer dans ce fusible un courant élevé qui le vaporise, créant ainsi le circuit ouvert recherché. considérons par exemple un réseau de 9 MOS (fig II 30). Le fusible étant intact, le MoS adressé fournirt le 0; le fusible étant détruit, le MOS fournir un 1.

La destruction du fusible est assurée par une rampe de courant de quelques dizaines de milliampéres. On s'arrange pour que le métal fondu ne se volatilise pas au hasard, mais se "rétracte" comme si le métal était absorbé par les bords qui restent nets.

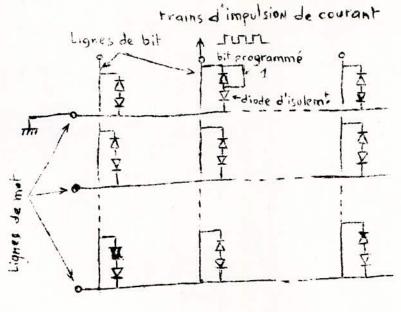

# b) METHODE PAR DESTRUCTION DE JONCTION.

Mise au point par intersil, cette méthode consiste à court-circuiter defaçon sélective des jonctions à semi- conducteur en appliquant des séries d'impulsions de courant (fig II 31).

FIG 1131

La mémoire est construite sous forme matricielle de N mots de n bits chacun. Chaque Ligne de mot est réunie à chaque ligne de bit par deux diodes tête - bêche correspondant à un circuit ouvert. Tout se passe comme si, à l'origine, les lignes de mot n'étaient pas réunies aux lignes de bit.

La programmation consiste à court- circuiter une des deux die des au niveau d'un bit préalablement choisi. Pour de faire, la ligne de mot correspondante est mise à la masse, tandisque sur la ligne de bit, on applique un train d'impulsions de courant. Celui - ci n'a aucun effet destructif sur la diede polarisée en inverse est amenée en régime d'avalanche. Si l'amplitude des impulsions est bien calibrée, leur effet est tel que l'en proveque une fusion locale de la jonction, mettant celle-ci en court -circuit. La ligne de bit et la ligne de mot correspondants sont maintenant réunies par une seule diede polarisée en sens sirect qui jour seulement le rôle de diede d'isolement.

La mémoire étant construite de telle sorte que, à l'origine, tous les bits soient à l'état 0, le bit ainsi programmé passe à l'état. 1

Les avantages présentés par la technique à destruction de jonction sont de deux ordres: la fiabilité ( il n 'ya plus de mátal vaporisé) et le prix.

\* En conclusion, les avantages des ROM programmables par l'utilisateur sont nombreux.

Pour le fabricant, ne pas réaliser la programation au cours de la fabrication lui permet de fabriquer un produit parfaitement standard; il en découle une réduction du prix de revient.

. Pour l'utilisateur, l'emploi des ROM programmables lui permet d'éviter les frais de masquage spécial nécessaires avec les ROM classiques. D'autre part il est possible d'obtenir en quelques minutes une mémoire programmé selon un nouveau code.

# II.4 3 LES PROM REPROGRAMABLES (REPROM)

Cette catégorie de PROM qui pourraient, éventuellement, être effacees puis reprogrammées, a été annoncée par INTEL avec la mémoire 2048 bits types 1601/1701, dans laquelle la mémorisation est assurée par avalanche.

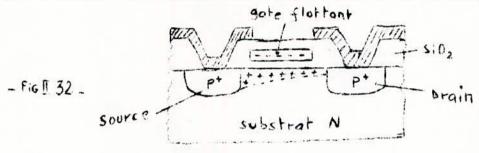

La technologie utilisée présente plusieurs particularités intéressantes qui sont, d'une part, le mode de rétention de l'information et, d'autre part, ses modes de lecture, d'écriture et d'effacement. Le support mémoire est constitué par le gate flottant d'un transistor MOS à canal P dont le schéma de structure est:

Il tire parti du fait qu'une charge électrique peut être stockée par un conducteur et retenue pendant plusieurs siècles par un diélectrique de faible conductibilité, sans l'aide d'aucune source de puissance extérieure. Le conducteur, matérialisé par le gate du transistor, est isolé du substrat par une épaisseur d'oxyde de silicium de 1000 Å, et de la surface externe par une couche d'oxyde de 1 micron.

### \* Lecture.

L'opération de lecture revient à détecter la présence de la charges électriques dans les gates des transistors constituant le not ménorisé que l'on désire sélectionné. Ceux-ci de part leur constitution, sont normalement bloqués en l'absence de charges négatives sur leur gate; ces zones drain-source contenant une majorité de trous, et la zone canal contenant une majorité d'electrons constituent, effet, une double jonction PN qui interdit le passage du courant dans un sens come dans l'autre.

Lorsqu'une charge nétative est placée dans le gate, celui-ci induit dans le canal une certaine quantité de trous et y crée, ainsi, une zone de conduction entre drain et source. Ainsi on est ranené à une structure de mémoire

conventionnelle. La valeur 1 donnée pour une absence de charge et la valeur 0 pour une présence de charge definissent l'atat de l'information enregistrée.

#### \* Ecriture.

L'opération d'écriture revient à implanter dans les gates flottants des transistors sélectionnés une quantité d'électrons suffisante pour les rendre conducteurs. ceux ci sont prélevés dans le substrat et l'énergie qui leur pernet de traverser : la barrière isolante les séparant du gate est obtenue par effet d'avalanche. l'enregistrement d'une information se fait par mise à zére sélective de certains bits. Cela simplique qu'ils soient tous, au préalable, entièrement mis à 1 ou, en d'autres termes, que la ménoire soit tatalement effacée.

Les informations peuvent être effacées en soumettant le cirquit intégré à à'ultra violet; ce rayonnement ionisant crée des paires électron trou qui déchargent les gates. Puis, on reprogramme la mémoire.

# II. 5 LES MEMOIRES ASSOCIATIVES ( CAM)

Dans les rénoires RAM et ROM, les informations sont rénorisées en des positions- nénoires précises, désignées par leur adresse. Ainsi, pour retrouver une information, on adresse une position de nénoire, il faut savoir précisement la quelle.

Dans les CAM ( co ntent adressable némory), l'information est retrouvée sans adresse, en tenant compte uniquement de son contenu. Ce principe s'avère extrêmement interessant dans les applications où l'on traite de liste d'informations souvent modifiées: on évite ainsi la recherche de l'adresse! En co ntre partie, on demande à la némoire d'assurer, en plus, des fonctions logiques quisqu'il lui faut procéder à des comparaisons partielles ou compètes de mots pour retrouver l'information, ce type de mémoire n'avait donné lieu à des réalisations commerciales qu'en 1970. Ses applications relévent du triage, de la reconnaissance des formes, de l'accés rapide à des tables ou des listes, et semblent encore à explorer pour l'essentiel.

# II. 6 RAM A MOS COMPLEMENTAIRES (C/ MOS):

# II.6. 1 LES CIRCUITS C/ MOS.

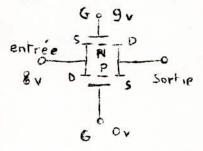

Un circuit MOS complémentaire comprend des transistors MOS à canal P et à canal N.

L'ossociation de ces deux types d'éléments permet d'éliminer les fonctionnements en source follower qui étaient un obstacle à la rapidité, et d'avoir des consennations faibles à l'état de repos.

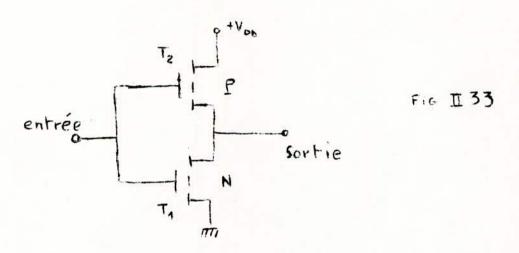

la fig II 33 représente un inverseur dans la technique MOS complémentaire. Lorsque l'état sur l'entrée est un niveau bas ( zéro volt ), le transistor MOS à canal N est bloqué, celui à canal P est conducteur; la sortie est à l'état haut.

Lorsque l'entrée est à l'état haut, l'inverse se produit et la sortie est à l'état bas. Le circuit se comporte donc comme un inverseur. En fonctionnement l'un des transistors MOS conduit, tandis que l'autre est bloqué. A l'état de repos les deux transistors sont bloqués. Il n'y a donc pas de courant (nis à part les courants de fuite) qui circule entre V DD et la masse. En transitoire, lorsque l'entrée passe d'un état bas à un état haut, la capacité de la sortie se décharge à travers T1 fonctionnant en source commune; lorsque l'entrée évolue d'un niveau haut à un niveau bas, le condonsateur de sortie se charge à travers T2, opérant en source commune. Le mode source follower est donc éliminé. De plus, les cont<sub>p</sub>aintes de gain sur les éléments de charge et de commutation dans les inverseurs classiques n'éxist<sub>e</sub>nt plus; En effet, l'état bas en sortie ne dépend que de la resistance source drain RDS de l'élement en commutation T1. Il n'est pas fonction, comme dans l'inverseur classique, du rapport des résistances source drain RDS du transistor MOS de charge et du transistor MOS de commutation.

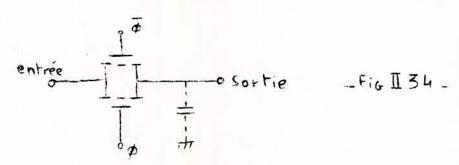

la fig II 34 montre une porte de transmission. Les deux transistors MOS sont

simultanément passants ou bloqués. Dans le cas où ils sont tous les deux conducteurs, il y en a toujours un qui opère dans le mode source commune, tandis que l'autre fonctionne en mode source follower est masqué.

Leur mise en parallèle fait que lemode source fallower est masqué.

Pour mieux comprendre l'avantage de  $\operatorname{cet}_{\operatorname{te}}$  por $\operatorname{te}_{\operatorname{e}}$  de  $\operatorname{transmission}$ , retenons donc que le fonctionnement en source follower existe, nais n'intorvient pas. supposons (fig II) que chaque transigtor MOS ait une tonsion de seuil de 2 volts et qu'un potentiel de o volt soit appliqué sur la grille de l'élement à canal P et une tension de + 9 volts sur la grille de l'élément à canal N. Applications sur l'entrée:

entrée S D HOS s'adaptent de manière à ôtro tous les deux conducteurs.

Sortie Celui à canal P, dont la différence de potentiel entre la conducteurs. l'entrée, est :

0-8= -8v, choist l'entrée comme source et fonctionne dans le mode source commune. Celui à canal N, dont la différence de potentiel entre la grille et l'entrée est 9 - 8 = 1 volt, ne peut être passant que s'il sélectionne la sortie comme source et, par conséquent, opère dans le mode source follower. comme dans II,  $T_1$  et  $T_2$  étant en parallèle, ce dernier mode est la première masque. Lorsque l'entrée est à zéro volt, c'est le contraire, To fonctionne en source follower et T1 en source commune;

# II 6.2 LES CELLULES EN C/ MOS DE RAM.

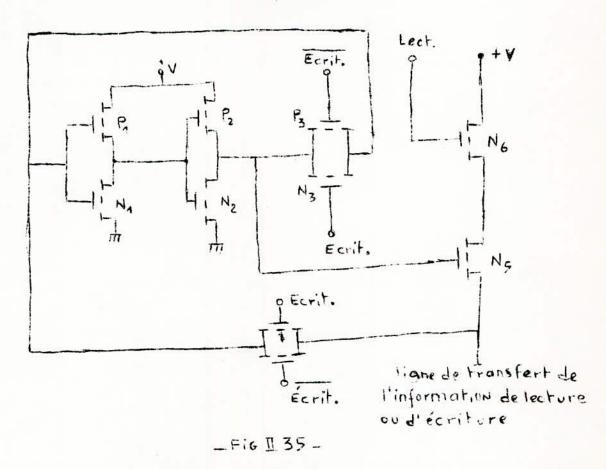

L'association des deux circuits précédents, inverseur et porte de transmission entechnologie MOS complémentaire, permet d'obtenir des cellules de nénoire vive très rapides, fonctionnant en statique. (fig II35 ).

A l'état de repos, la porte de transmission P3, N3 est passa te et permet le bouclage de la sortie de P2, N2 sur l'entrée de l'inversuur P1, N1 et P1, N1 et P2 et N2 forment alors un bistable, donc une cellule de mémoire vive classique. La porte P4, N4 est femmée. En lecture, la grille de N6 est portée à un potentiel positif et rend N6 passant.

N6 passant. Selon que l'information stockée sur la sortic P2, N2 est un 1 ou 0, N5 est conducteur ou bloqué. Si N5 est passant, un courant s'écoule à travers N5 et N6 en écriture, la polarité du siganl"écriture" est inversée, P3, N3 est bloqué et supprime de bouclage mentionné précédemment · P4, N4 conduit et envoie sur l'entrée P1 et N1 l'information véhiculée par la ligne de transfert d'information. Cette donnée se propage à travers P1 et N1; P2 N2, jusqu'à la sortie de P2, N2. A la fin du cycle écriture, le signal "écriture" revient à sont état initial et rétablit le circuit bistable.

La grande rapidité de cette cellule est obtenue au prix d'un circuit très complexe. On lui préfère la cellule suivante (fig II 36) qui est un peu noins rapide, mais plus simple.

\_FIG 1 36-

Le fonctionnement est similaire à la cellule à six éléments du paragraphe II 2.3. En pratique, une cellule en MOS complémentaire ne sonsonme que quelques nanawatts au repos. Cette consommation est deux à trois fois inférieure à celle de la cellule dynamique à trois éléments. Dans les deux cas cependant, la puissance dissipée par une cellule à l'état de repos est Baible et peut être fournie, si des besoins de non volatilité de l'information sont nécessaires, par des batteries.

#### CHAPITRE III :

### Les Perspectives d'Avenir

### DI 1 ETAT ACTUEL ET AVENIR DES MEMOIRES à C I :

Les mémoires à CI disponibles aujourd'hui utilisent surtout la technologie M O S qui comme on l'a déjà vu présente deux avantages majeurs pour les circuits complexes :

-La réalisation des circuits M O S se fait en un nombre d'opérations plus petit.

- La géométrie des composants permet des dimensions plus restreintes.

Dans une mémoire à CI, le coût du bit dépend essentiellement de la cellule mémoire et est donc pratiquement indépendant de la taille de la cellule. Des efforts considérables ont été faits pour des raisons techniques et économiques afin de développer des circuits de plus en plus complexes. Les raisons techniques sont les suivantes :

- La taille ou la densité

- L'amélioration de l'immunité aux parasites et aux réflexions

- Stabilité plus facile des circuits

- La fiabilité est plus grande.

Actuellement, on réalise des blocs-mémoires à CI. Ceci est caractéristique d'une évolution qui vise à répondre aux besoins d'un marché en croissance rapide. Ainsi, au lieu de laisser l'utilisateur affront seul la fabrication d'une mémoire avec des CI individuels, on lui fournit des sous-ensemble " prêts-à-l'emploi", directement enfichables.

Les circuits disponibles sont du type 1K et 2K. La sortie des circuits 4 K est déjà faite (MOTOROLA). Un 8 K a été produit expérimentalement chez I B M et, entre autres, les 16 K.

La technologie M O S est donc bon marché et se prête à une intégration de grande échelle.

D'un point de vue technique, la substitution des CI aux tores semble assurée. En ce qui concerne les temps d'accès, seules les mémoires à CI Progressent encore; s'agissant des capacités, les potentialites des CI sont superieures. Enfin, le prix des mémoires à CI deviendra inferieur à celui des mémoires tores vers 1975. On peut donc assurer que substitution sera complete dans les systèmes nouvellement concus dès avant 1980 (voir tableaux).

Temps d'accès des RAM

| ANNEE | Temps d'accès (ns |

|-------|-------------------|

| 1972  | 300               |

| 1975  | 150               |

| 1980  | 50 à 100          |

| 1985  | 20 à 100          |

Prix au bit (centimes)

| ANNEE | Prix   |

|-------|--------|

| 1972  | 4 à 12 |

| 1975  | 2 à 10 |

| 1980  | 1 à 8  |

| 1985  | 0,5    |

## DI . 2. LES MEMOIRES A SEMI- CONDUCTEURS AMORPHES.

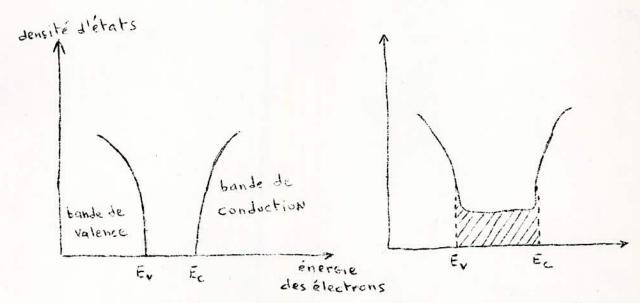

# 1 . 2.1 LES SEMI-CONDUCTEURS AMORPHES.

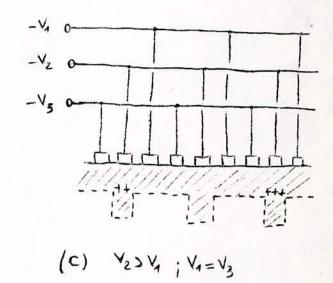

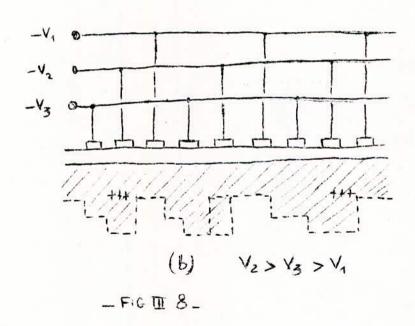

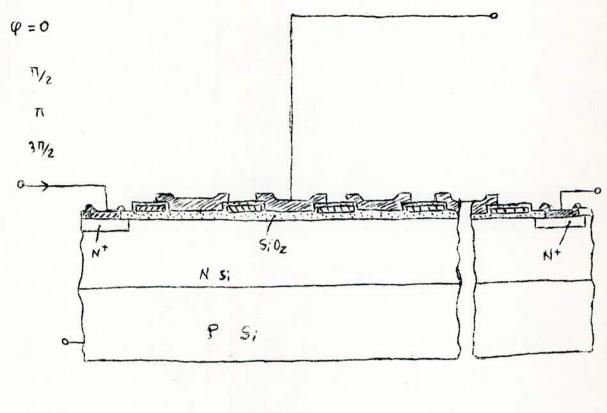

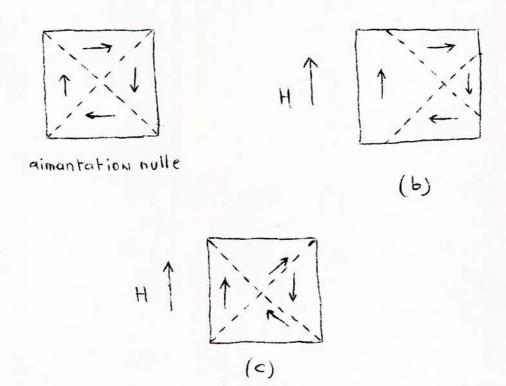

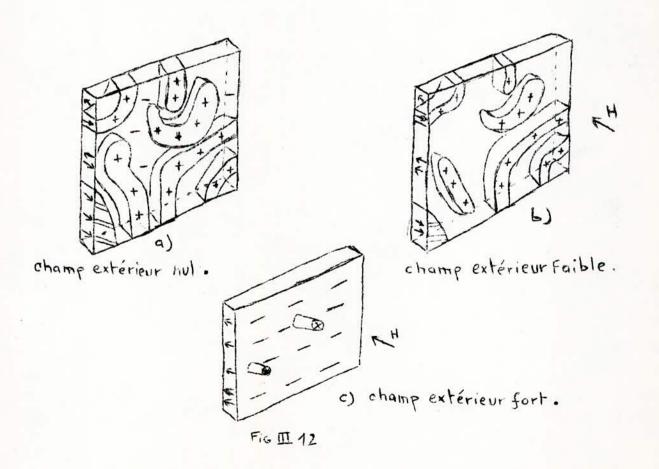

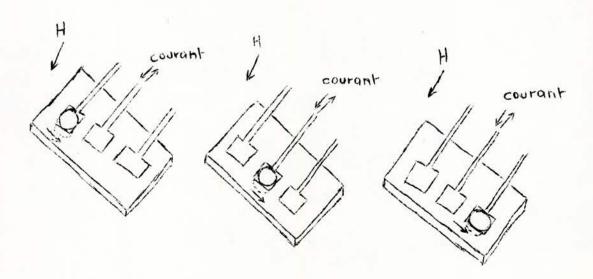

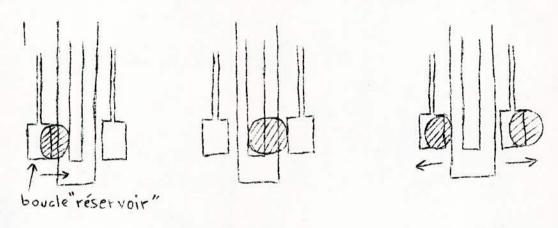

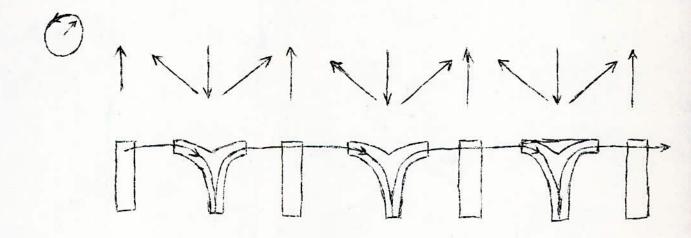

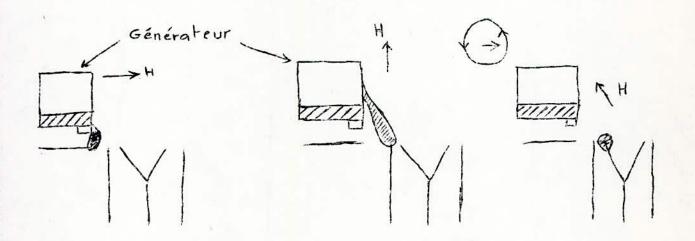

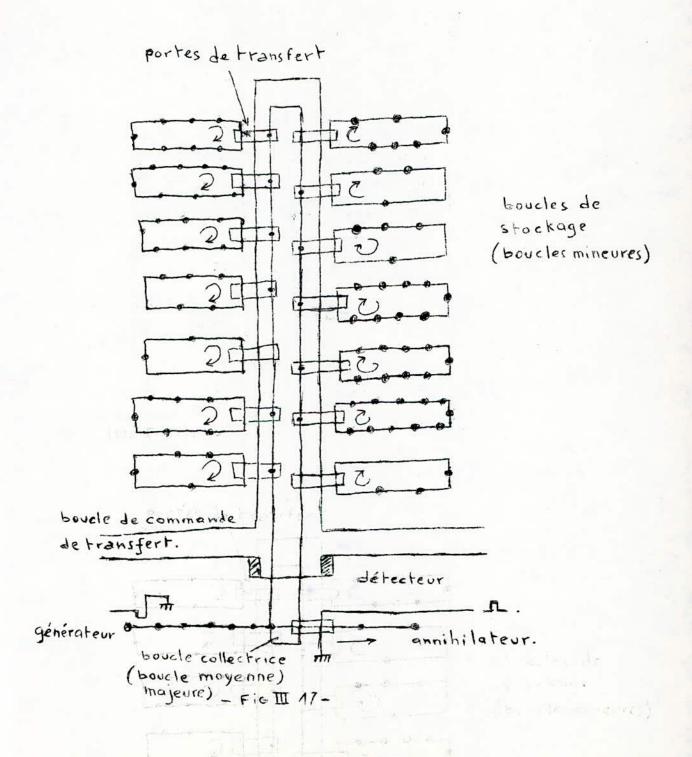

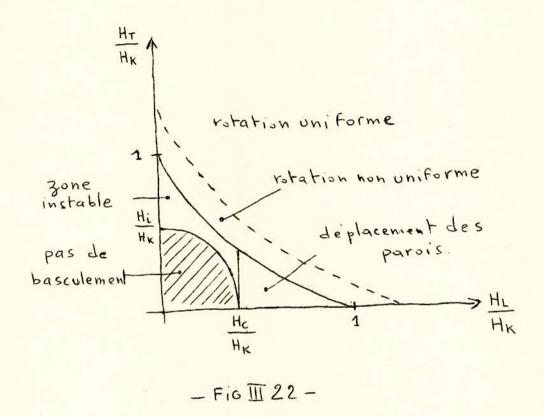

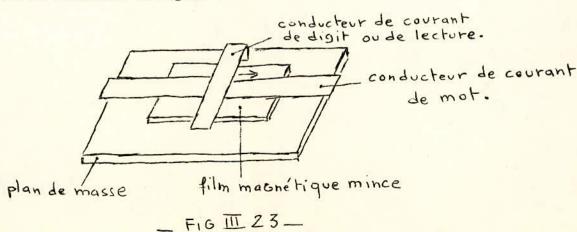

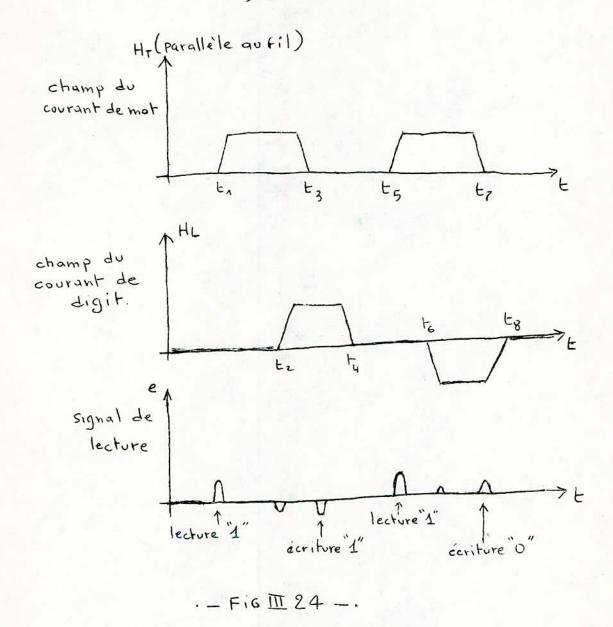

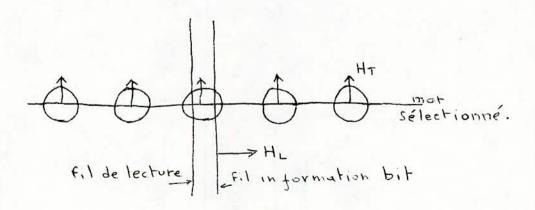

En 1968, le physicien américain S. R Ovshinski annonçait que des verres spéciaux, semi-conducteurs, présentaient des effets de commutation rapide et de mémoire. Ces effets portent, précisément, le nom de leur inventeur.